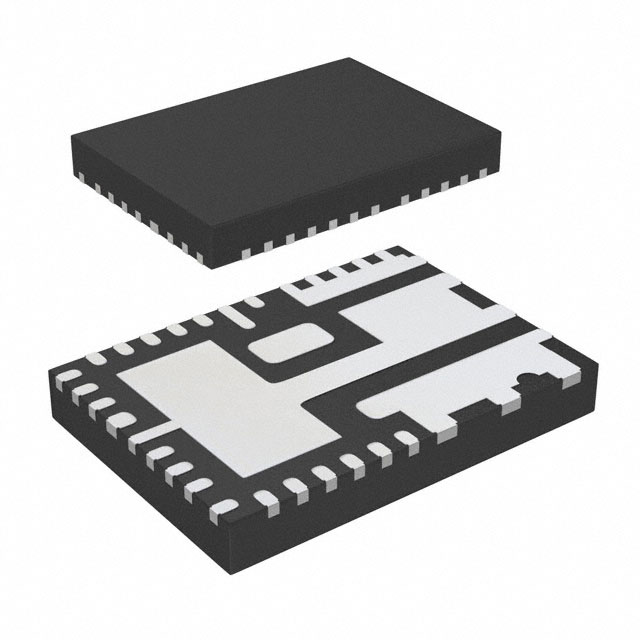

DCDC Converter

35A Highly Integrated SupIRBuck®

Single-Input Voltage, Synchronous

Buck Regulator

FEATURES

SupIRBuck

IR3846

DESCRIPTION

Single 5V to 21V application

Wide Input Voltage Range from 1.5V to 21V with

external Vcc

Output Voltage Range: 0.6V to 0.86*PVin

0.5% accurate Reference Voltage

Enhanced line/load regulation with Feed-Forward

Programmable Switching Frequency up to

1.5MHz

Internal Digital Soft-Start

Enable input with Voltage Monitoring Capability

Remote Sense Amplifier with True Differential

Voltage Sensing

Thermally compensated current limit and Hiccup

Mode Over Current Protection

Smart LDO to enhance efficiency

Vp for tracking applications and sequencing

Vref is available externally to enable margining

External synchronization with Smooth Clocking

Dedicated output voltage sensing for power good

indication and overvoltage protection which

remains active even when Enable is low.

Enhanced Pre-Bias Start up

Body Braking to improve transient

Integrated MOSFET drivers and Bootstrap diode

Thermal Shut Down

Post Package trimmed rising edge dead-time

Programmable Power Good Output with tracking

Small Size 5mm x 7mm PQFN

Operating Junction Temp: -40oC

VPG_low(upper)

1.5

2.5

3.5

µs

Vsns Rising,

0.4V < Vref < 1.2V

95

% Vref

Vsns Rising,

Vref < 0.1V

95

% Vp

1.28

ms

Vsns falling,

0.4V < Vref < 1.2V

90

% Vref

Vsns falling,

90

%Vp

Vsns rising

March 5, 2020

�IR3846

PARAMETER

SYMBOL

Power Good Low Lower

Threshold Falling delay

VPG_low(lower)_Dly

CONDITIONS

0.1V < Vref

Vsns <

VPG_low(lower)

MIN

TYP

MAX

UNIT

101

150

199

µs

0.5

V

PGood Voltage Low

PG (voltage)

IPGood = -5mA

Tracker Comparator

Upper Threshold

VPG(tracker_upper)

Vp Rising, Vref < 0.1V

0.4

V

Tracker Comparator

Lower Threshold

VPG(tracker_lower)

Vp Falling, Vref < 0.1V

0.3

V

Tracker Comparator

Delay

Tdelay(tracker)

Vp Rising, Vref < 0.1V

1.28

ms

Over Voltage Protection (OVP)

OVP Trip Threshold

OVP (trip)

OVP Fault Prop Delay

OVP (delay)

Vsns Rising,

0.45V < Vref < 1.2V

115

120

125

% Vref

Vsns Rising,

Vref < 0.1V

115

120

125

% Vp

Vsns rising

1.5

2.5

3.5

µs

OCSet=VCC, VCC =

6.8V, TJ = 25°C

41

44.4

48

A

OCSet=floating, VCC

= 6.8V, TJ = 25°C

32

35

38

A

OCSet=PGnd, VCC

=6.8V, TJ = 25°C

24

26.88

30

A

Over-Current Protection

OC Trip Current

ITRIP

Hiccup blanking time

Tblk_Hiccup

Note 4

20.48

ms

Thermal Shutdown

Note 4

145

°C

Hysteresis

Note 4

20

°C

Thermal Shutdown

Notes:

4. Guaranteed by design but not tested in production.

10

Rev 3.8

March 5, 2020

�IR3846

TYPICAL EFFICIENCY AND POWER LOSS CURVES

PVin = Vin = 12V, VCC = Internal LDO, Io=0-35A, Fs= 600kHz, Room Temperature, LFM=200. Note that the

losses of the inductor, input and output capacitors are also considered in the efficiency and power loss curves.

The table below shows the indicator used for each of the output voltages in the efficiency measurement.

VOUT (V)

1.2

1.8

3.3

5.0

11

LOUT (uH)

0.25

0.33

0.33

0.33

Rev 3.8

P/N

744309025 (Wurth Electronik)

744309033 (Wurth Electronik)

744309033 (Wurth Electronik)

744309033 (Wurth Electronik)

DCR (mΩ)

0.165

0.165

0.165

0.165

March 5, 2020

�IR3846

TYPICAL EFFICIENCY AND POWER LOSS CURVES

PVin = 12V, Vin = VCC = 5V, Io=0-35A, Fs= 600kHz, Room Temperature, LFM=200. Note that the losses of the

inductor, input and output capacitors are also considered in the efficiency and power loss curves. The table

below shows the indicator used for each of the output voltages in the efficiency measurement.

VOUT (V)

1.2

1.8

3.3

5.0

12

LOUT (uH)

0.25

0.33

0.33

0.33

Rev 3.8

P/N

744309025 (Wurth Electronik)

744309033 (Wurth Electronik)

744309033 (Wurth Electronik)

744309033 (Wurth Electronik)

DCR (mΩ)

0.165

0.165

0.165

0.165

March 5, 2020

�IR3846

TYPICAL EFFICIENCY AND POWER LOSS CURVES

PVin = Vin = VCC = 5V, Io=0-35A, Fs= 600kHz, Room Temperature, LFM=200. Note that the losses of the

inductor, input and output capacitors are also considered in the efficiency and power loss curves. The table

below shows the indicator used for each of the output voltages in the efficiency measurement.

VOUT (V)

1.0

1.2

13

LOUT (uH)

0.19

0.19

Rev 3.8

P/N

SL40307A-R19KHF (ITG)

SL40307A-R19KHF (ITG)

DCR (mΩ)

0.200

0.200

March 5, 2020

�IR3846

THERMAL DERATING CURVES

Measurements are done on IR3846 Evaluation board. PCB is a 6 layer board with 2 oz copper and FR4 material.

Vin=PVin=12V, Vout =1.2V, VCC=internal LDO (6.8V), Fs = 600kHz

Vin=PVin=12V, Vout =3.3V, VCC=internal LDO (6.8V), Fs = 600kHz

Note: International Rectifier Corporation specifies current rating of SupIRBuck devices conservatively. The

continuous current load capability might be higher than the rating of the device if input voltage is 12V typical and

switching frequency is below 600kHz. However, the maximum current is limited by the internal current limit and

designers need to consider enough guard bands between load current and minimum current limit to guarantee

that the device does not trip at steady state condition.

14

Rev 3.8

March 5, 2020

�IR3846

MOSFET RDSON VARIATION OVER TEMPERATURE

15

Rev 3.8

March 5, 2020

�IR3846

TYPICAL OPERATING CHARACTERISTICS (-40°C to +125°C)

16

Rev 3.8

March 5, 2020

�IR3846

TYPICAL OPERATING CHARACTERISTICS (-40°C to +125°C)

17

Rev 3.8

March 5, 2020

�IR3846

18

Rev 3.8

March 5, 2020

�IR3846

TYPICAL OPERATING CHARACTERISTICS (-40°C to +125°C)

OCset=VCC

OCset=Float

OCset=GND

OCset=VCC

OCset=Float

OCset=GND

OCset=VCC

OCset=Float

OCset=GND

19

Rev 3.8

March 5, 2020

�IR3846

THEORY OF OPERATION

DESCRIPTION

The IR3846 uses a PWM voltage mode control

scheme with external compensation to provide good

noise immunity and maximum flexibility in selecting

inductor values and capacitor types.

The switching frequency is programmable from

300kHz to 1.5MHz and provides the capability of

optimizing the design in terms of size and

performance.

IR3846 provides precisely regulated output voltage

programmed via two external resistors from 0.6V to

0.86*PVin.

The IR3846 operates with an internal bias supply

(LDO) which is connected to the VCC pin. This allows

operation with single supply. The bias voltage is

variable according to load condition. If the output load

current is less than half of the peak-to-peak inductor

current, a lower bias voltage, 4.4V, is used as the

internal gate drive voltage; otherwise, a higher

voltage, 6.8V, is used.

This feature helps the converter to reduce power

losses. The device can also be operated with an

external bias from 4.5V to 7.5V, allowing an extended

operating input voltage (PVin) range from 1.5V to 21V.

For using the internal LDO supply, the Vin pin should

be connected to PVin pin. If an external bias is used, it

should be connected to VCC pin and the Vin pin

should be shorted to VCC pin.

set thresholds. Normal operation resumes once VCC

and Enable rise above their thresholds.

The POR (Power On Ready) signal is generated when

all these signals reach the valid logic level (see

system block diagram). When the POR is asserted the

soft start sequence starts (see soft start section).

ENABLE

The Enable features another level of flexibility for

startup. The Enable has precise threshold which is

internally monitored by Under-Voltage Lockout

(UVLO) circuit. Therefore, the IR3846 will turn on only

when the voltage at the Enable pin exceeds this

threshold, typically, 1.2V.

If the input to the Enable pin is derived from the bus

voltage by a suitably programmed resistive divider, it

can be ensured that the IR3846 does not turn on until

the bus voltage reaches the desired level as shown in

Figure 4. Only after the bus voltage reaches or

exceeds this level and voltage at the Enable pin

exceeds its threshold, IR3846 will be enabled.

Therefore, in addition to being a logic input pin to

enable the IR3846, the Enable feature, with its precise

threshold, also allows the user to implement an

Under-Voltage Lockout for the bus voltage (PVin). It

can help prevent the IR3846 from regulating at low

PVin voltages that can cause excessive input current.

The device utilizes the on-resistance of the low side

MOSFET (synchronous Mosfet) as current sense

element. This method enhances the converter’s

efficiency and reduces cost by eliminating the need for

external current sense resistor.

IR3846 includes two low Rds(on) MOSFETs using IR’s

HEXFET technology. These are specifically designed

for high efficiency applications.

UNDER-VOLTAGE LOCKOUT AND POR

The under-voltage lockout circuit monitors the voltage

of VCC pin and the Enable input. It assures that the

MOSFET driver outputs remain in the off state

whenever either of these two signals drops below the

20

Rev 3.8

Figure 4: Normal Start up, device turns on when the

bus voltage reaches 10.2V

A resistor divider is used at EN pin from PVin to turn

on the device at 10.2V.

March 5, 2020

�IR3846

PVin=Vin

Vcc

Vp

> 1.0V

EN

> 1.2V

input. In this operating mode Vref is left floating.

Figure 6 shows the recommended startup sequence

for sequenced operation of IR3846 with Enable used

as logic input. Figure 7 shows the recommended

startup sequence for tracking operation of IR3846 with

Enable used as logic input. For this mode of

operation, Vref should be connected to LGND.

PRE-BIAS STARTUP

Intl_SS

Vo

Figure 5: Recommended startup for Normal operation

PVin=Vin

Vcc

Pre-bias can restrict the V_boot voltage and prevent

the IC from starting up properly. Knowing the Vboot

requirement, Vcc voltage (Vcc) and forward diode

(Vd) voltage the maximum pre-bias can be

determined. The power stage driver requires a

minimum of 3V Vboot during startup which translates

to a maximum pre-bias voltage of (Vcc – Vd –

Vboot)V.

Pre-Bias voltage Limit

< Vcc – Vd – Vboot

(1)

Vp

> 1.2V

EN

Intl_SS

Vo

Figure 6: Recommended startup for sequencing

operation (ratiometric or simultaneous)

PVin=Vin

Vcc

VDDQ

Vp

VDDQ/2

EN

> 1.2V

Vref

0V

Vcc

Vd

Vboot

Supply Rail (Internal LDO / External Supply)

Bootstrap diode forward voltage. [0.8V]

Required Vboot voltage at start up. [3V]

IR3846 implements asynchronous switching during

startup to help prevent oscillation and output

disturbance when starting up with a pre-biased output.

The regulator starts in an asynchronous fashion and

keeps the synchronous MOSFET (Sync FET) off until

the first gate signal for control MOSFET (Ctrl FET) is

generated. Figure 8 shows a typical Pre-Bias

condition at start up. The sync FET always starts with

a narrow pulse width (12.5% of a switching period)

and gradually increases its duty cycle with a step of

12.5% until it reaches the steady state value. The

number of these startup pulses for each step is 16

and it’s internally programmed. Figure 9 shows the

series of 16x8 startup pulses.

[V]

Vo

Vo

VTT Tracking

Pre-Bias

Figure 7: Recommended startup for memory tracking

operation (Vtt-DDR)

Figure 5 shows the recommended startup sequence

for the normal (non-tracking, non-sequencing)

operation of IR3846, when Enable is used as a logic

21

Rev 3.8

Voltage

[Time]

Figure 8: Pre-Bias startup

March 5, 2020

�IR3846

HDRv

...

12.5%

16

...

25%

...

LDRv

...

87.5%

...

...

The switching frequency can be programmed between

300kHz – 1500kHz by connecting an external resistor

from Rt pin to LGnd. Table 1 tabulates the oscillator

frequency versus Rt.

...

...

16

...

...

End of

PB

Figure 9: Pre-Bias startup pulses

SOFT-START

IR3846 has an internal digital soft-start to control the

output voltage rise and to limit the current surge at the

start-up. To ensure correct start-up, the soft-start

sequence initiates when the Enable and VCC rise

above their UVLO thresholds and generate the Power

On Ready (POR) signal. The internal soft-start

(Intl_SS) signal linearly rises with the rate of 0.4mV/µs

from 0V to 1.5V. Figure 10 shows the waveforms

during soft start. The normal Vout startup time is fixed,

and is equal to:

Tstart

0.75V 0.15V 1.5mS

0.4mV / S

Table 1: Switching Frequency(Fs) vs. External

Resistor(Rt)

Rt (KΩ)

80.6

60.4

48.7

39.2

34

29.4

26.1

23.2

21

19.1

17.4

16.2

15

(2)

During the soft start the over-current protection (OCP)

and over-voltage protection (OVP) is enabled to

protect the device for any short circuit or over voltage

condition.

Freq

(KHz)

300

400

500

600

700

800

900

1000

1100

1200

1300

1400

1500

SHUTDOWN

IR3846 can be shutdown by pulling the Enable pin

below its 1.0V threshold. During shutdown the high

side and the low side drivers are turned off.

OVER CURRENT PROTECTION

Figure 10: Theoretical operation waveforms during

soft-start (non tracking / non sequencing)

OPERATING FREQUENCY

22

Rev 3.8

The Over Current (OC) protection is performed by

sensing the inductor current through the RDS(on) of the

Synchronous MOSFET. This method enhances the

converter’s efficiency, reduces cost by eliminating a

current sense resistor and any layout related noise

issues. The Over Current (OC) limit can be set to one

of three possible settings by floating the OCset pin, by

pulling up the OCset pin to VCC, or pulling down the

OCset pin to PGnd. The current limit scheme in the

March 5, 2020

�IR3846

IR3846 uses an internal temperature compensated

current source to achieve an almost constant OC limit

over temperature.

Over Current Protection circuit senses the inductor

current flowing through the Synchronous MOSFET.

To help minimize false tripping due to noise and

transients, inductor current is sampled for about 30 nS

on the downward inductor current slope approximately

12.5% of the switching period before the inductor

current valley. However, if the Synchronous MOSFET

is on for less than 12.5% of the switching period, the

current is sampled approximately 40nS after the start

of the downward slope of the inductor current. When

the sampled current is higher than the OC Limit, an

OC event is detected.

Figure 11: Timing Diagram for Current Limit Hiccup

THERMAL SHUTDOWN

When an Over Current event is detected, the

converter enters hiccup mode.

Hiccup mode is

performed by latching the OC signal and pulling the

Intl_SS signal to ground for 20.48 mS (typ.). OC

signal clears after the completion of hiccup mode and

the converter attempts to return to the nominal output

voltage using a soft start sequence. The converter will

repeat hiccup mode and attempt to recover until the

overload or short circuit condition is removed.

Temperature sensing is provided inside IR3846. The

trip threshold is typically 145oC. When trip threshold is

exceeded, thermal shutdown turns off both MOSFETs

and resets the internal soft start.

Because the IR3846 uses valley current sensing, the

actual DC output current limit will be greater than OC

limit. The DC output current is approximately half of

peak to peak inductor ripple current above selected

OC limit. OC Limit, inductor value, input voltage,

output voltage and switching frequency are used to

calculate the DC output current limit for the converter.

Equation (2) to determine the approximate DC output

current limit.

REMOTE VOLTAGE SENSING

I OCP I LIMIT

IOCP

ILIMIT

Δi

i

2

= DC current limit hiccup point

= Current Limit Valley Point

= Inductor ripple current

(3)

Automatic restart is initiated when the sensed

temperature drops within the operating range. There

is a 20oC hysteresis in the thermal shutdown

threshold.

True differential remote sensing in the feedback loop

is critical to high current applications where the output

voltage across the load may differ from the output

voltage measured locally across an output capacitor

at the output inductor, and to applications that require

die voltage sensing.

The RS+ and RS- pins of the IR3846 form the inputs

to a remote sense differential amplifier (RSA) with

high speed, low input offset and low input bias current

which ensure accurate voltage sensing and fast

transient response in such applications.

The input range for the differential amplifier is limited

to 1.5V below the VCC rail. Note that IR3846

incorporates a smart LDO which switches the VCC rail

voltage depending on the loading. When determining

the input range assume the part is in light load and

using the lower VCC rail voltage.

There are two remote sense configurations that are

usually implemented. Figure 12 shows a general

remote sense (RS) configuration. This configuration

allows the RSA to monitor output voltages above

23

Rev 3.8

March 5, 2020

�IR3846

VCC. A resistor divider is placed in between the

output and the RSA to provide a lower input voltage to

the RSA inputs. Typically, the resistor divider is

calculated to provide VREF (0.6V) across the RSA

inputs which is then outputted to RSo. The input

impedance of the RSA is 63 KOhms typically and

should be accounted for when determining values for

the resistor divider. To account for the input

impedance, assume a 63 KOhm resistor in parallel to

the lower resistor in the divider network.

The

compensation is then designed for 0.6V to match the

RSo value.

Compensation

Low voltage applications can use the second remote

sense configuration. When the output voltage range

is within the RSA input specifications, no resistor

divider is needed in between the converter output and

RSA. The second configuration is shown in Figure

13. The RSA is used as a unity gain buffer and

compensation is determined normally.

Compensation

Figure 12: General Remote Sense Configuration

Figure 13: Remote Sense Configuration for Vout less

than VCC-1.5V

EXTERNAL SYNCHRONIZATION

IR3846 incorporates an internal phase lock loop (PLL)

circuit which enables synchronization of the internal

oscillator to an external clock. This function is

important to avoid sub-harmonic oscillations due to

beat frequency for embedded systems when multiple

24

Rev 3.8

point-of-load (POL) regulators are used. A multifunction pin, Rt/Sync, is used to connect the external

clock. If the external clock is present before the

converter turns on, Rt/Sync pin can be connected to

the external clock signal solely and no other resistor is

needed. If the external clock is applied after the

converter turns on, or the converter switching

frequency needs to toggle between the external clock

frequency and the internal free-running frequency, an

external resistor from Rt/Sync pin to LGnd is required

to set the free-running frequency.

When an external clock is applied to Rt/Sync pin after

the converter runs in steady state with its free-running

frequency, a transition from the free-running

frequency to the external clock frequency will happen.

This transition is to gradually make the actual

switching frequency equal to the external clock

frequency, no matter which one is higher. When the

external clock signal is removed from Rt/Sync pin, the

switching frequency is also changed to free-running

gradually. In order to minimize the impact from these

transitions to output voltage, a diode is recommended

to add between the external clock and Rt/Sync pin.

Figure 14 shows the timing diagram of these

transitions.

An internal circuit is used to change the PWM ramp

slope according to the clock frequency applied on

Rt/Sync pin. Even though the frequency of the

external synchronization clock can vary in a wide

range, the PLL circuit keeps the ramp amplitude

constant, requiring no adjustment of the loop

compensation. PVin variation also affects the ramp

amplitude, which will be discussed separately in FeedForward section.

Synchronize to the

external clock

Free Running

Frequency

Return to freerunning freq

...

SW

Gradually change

Gradually change

...

Fs1

SYNC

Fs1

Fs2

Figure 14: Timing Diagram for Synchronization

to the external clock (Fs1>Fs2 or Fs1

RE/RF >

RC/RD

RE/RF =

RC/RD

0.6V

0.6V

Simultaneous

Tracking

0V

Ratiometric

Tracking

0V

RE/RF >

RC/RD

The threshold is set differently in different operating

modes and the results of the comparison sets the

PGood signal. Figure 24, Figure 25 and Figure 26

show the timing diagram of the PGood signal at

different operating modes. Vsns signal is also used by

OVP comparator for detecting output over voltage

condition. PGood signal is low when Enable is low.

PGood pin should not exceed Vcc pin voltage. By

allowing PGood to exceed the VCC voltage, the

internal ESD structure will be back biased and the

PGood supply can partially drive the VCC rail. Due to

current being drawn through the PGood pull-up

resistor, the PGood voltage will reside in at an

undefined voltage level which may be translated as a

low or high level.

Damage is not expected when PGood is back biased,

but back biasing PGood is not recommended.

Vref

0.6V

0

VREF

This pin reflects the internal reference voltage which is

used by the error amplifier to set the output voltage. In

most operating conditions this pin is only connected to

an external bypass capacitor and it is left floating. A

minimum 100pF ceramic capacitor is required from

stability point of view. In tracking mode this pin should

be pulled to LGND. For margining applications, an

external voltage source is connected to Vref pin and

overrides the internal reference voltage. The external

voltage source should have a low internal resistance

(