FUJITSU SEMICONDUCTOR

DATA SHEET

DS705-00008-1v0-E

32-bit Microcontroller

CMOS

FR60 MB91460Q Series

MB91F469QA

■ DESCRIPTION

Differences versus MB91F469GB are marked in red color.

MB91460Q series is a line of general-purpose 32-bit RISC microcontrollers designed for embedded control

applications which require high-speed real-time processing, such as consumer devices and on-board vehicle

systems. This series uses the FR60 CPU, which is compatible with the FR family* of CPUs.

This series contains the LIN-USART and CAN controllers.

* : FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU Semiconductor Limited.

■ FEATURES

1. FR60 CPU core

•

•

•

•

•

•

•

•

•

32-bit RISC, load/store architecture, five-stage pipeline

16-bit fixed-length instructions (basic instructions)

Instruction execution speed: 1 instruction per cycle

Instructions including memory-to-memory transfer, bit manipulation, and barrel shift instructions: Instructions

suitable for embedded applications

Function entry/exit instructions and register data multi-load store instructions : Instructions supporting C

language

Register interlock function: Facilitating assembly-language coding

Built-in multiplier with instruction-level support

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

Interrupts (save PC/PS) : 6 cycles (16 priority levels)

Harvard architecture enabling program access and data access to be performed simultaneously

For the information for microcontroller supports, see the following web site.

This web site includes the "Customer Design Review Supplement" which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

Copyright©2010 FUJITSU SEMICONDUCTOR LIMITED All rights reserved

2010.09

�MB91460Q Series

• Instructions compatible with the FR family

2. Internal peripheral resources

• General-purpose ports : Maximum 205 ports

• DMAC (DMA Controller)

Maximum of 5 channels able to operate simultaneously (including 2 external channels).

3 transfer sources (external pin/internal peripheral/software)

Activation source can be selected using software

Addressing mode specifies full 32-bit addresses (increment/decrement/fixed)

Transfer mode (demand transfer/burst transfer/step transfer/block transfer)

Fly-by transfer support (between external I/O and memory)

Transfer data size selectable from 8/16/32-bit

Multi-byte transfer enabled (by software)

DMAC descriptor in I/O areas (200H to 240H, 1000H to 1024H)

• A/D converter (successive approximation type): 2 modules

ADC 0: 10-bit resolution: 32 channels

ADC 1: 10-bit resolution: 8 channels

Conversion time: minimum 1 µs

• External interrupt inputs : 32 channels

12 channels shared with CAN RX, LIN-USART SIN, I2C SDA or I2C SCL pins

16 channels shared with ADC input pins

• Bit search module (for REALOS)

Function to search from the MSB (most significant bit) for the position of the first “0”, “1”, or changed bit in a word

• LIN-USART (full duplex double buffer): 12 channels, 8 channels with FIFO

Clock synchronous/asynchronous selectable

Sync-break detection

Internal dedicated baud rate generator

LIN-USART 8-11 with asynchronous operation only

• I2C bus interface (supports 400 kbps): 3 channel

Master/slave transmission and reception

Arbitration function, clock synchronization function

• CAN controller (C-CAN): 3 channels

Maximum transfer speed: 1 Mbps

32 transmission/reception message buffers

• Sound generator : 1 channelTone frequency : PWM frequency divide-by-two (reload value + 1)

• Alarm comparator : 2 channelsMonitor external voltageGenerate an interrupt in case of voltage lower/higher

than the defined thresholds (reference voltage)

• 16-bit PPG timer : 16 channels

• 16-bit PFM timer : 1 channel

• 16-bit reload timer: 8 channels

• 16-bit free-run timer: 9 channels (1 channel each for ICU and OCU)

• Input capture: 10 channels (operates in conjunction with the free-run timer)

• Output compare: 8 channels (operates in conjunction with the free-run timer)

• Up/Down counter: 4 channels (4*8-bit or 2*16-bit)

• Watchdog timer

• Real-time clock

(Continued)

2

DS705-00008-1v0-E

�MB91460Q Series

(Continued)

• Low-power consumption modes : Sleep/stop mode function

• Supply Supervisor: Low voltage detection circuit for external VDD5 and internal 1.8V core voltage

• Clock supervisor

Monitors the sub-clock (32 kHz) and the main clock (4 MHz) , and switches to a recovery clock (CR oscillator,

etc.) when the oscillations stop.

• Clock modulator

• Clock monitor

• Sub-clock calibration

Corrects the real-time clock timer when operating with the 32 kHz or CR oscillator

• Main oscillator stabilization timer

Generates an interrupt in sub-clock mode after the stabilization wait time has elapsed on the 23-bit stabilization

wait time counter

• Sub-oscillator stabilization timer

Generates an interrupt in main clock mode after the stabilization wait time has elapsed on the 15-bit stabilization

wait time counter

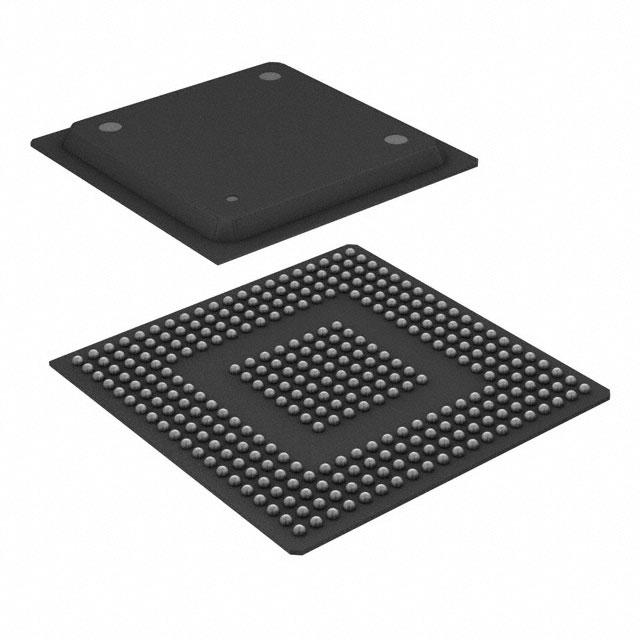

3. Package and technology

•

•

•

•

Package : 320-pin plastic BGA (BGA-320)

CMOS 0.18 µm technology

Power supply range 3 V to 5 V (1.8 V internal logic provided by a step-down voltage converter)

Operating temperature range: between − 40 °C and + 105 °C / +125 °C *1

1. For maximum ambient temperature TA(max), please refer to ORDERING INFORMATION on page 152.

DS705-00008-1v0-E

3

�MB91460Q Series

■ PRODUCT LINEUP

Feature

MB91F469QA

MB91V460A

MB91FV460B

Max. core frequency (CLKB)

80MHz

100MHz

100MHz at 1.9V 1

88MHz at 1.8V 2

Max. resource frequency (CLKP)

40MHz

50MHz

50MHz

Max. external bus freq. (CLKT)

40MHz

50MHz

50MHz

Max. CAN frequency (CLKCAN)

20MHz

50MHz

50MHz

Technology

0.35um

0.18µm

0.18µm

Emulation SRAM 32bit

read data

2112 KByte or external

emulation SRAM

2112 KByte

Flash Protection

no

yes

yes

Flash CRC calculation

no

yes

yes

D-RAM

64 KByte

64 KByte

64 KByte

ID-RAM

64 KByte

64 KByte

32 KByte

Flash-cache (F-cache)

16 KByte

16 KByte

16 KByte

External bus cache (I-cache)

4 KByte

4 KByte

4 KByte

Flash memory

Boot-ROM / BI-ROM

MMU/MPU

4 KByte fixed

MPU (16 ch)

3

16 KByte Boot Flash

MPU (16 ch)

3

4 KByte

MPU (8 ch) 3

DMA

5 ch

5 ch

5 ch

Software-Watchdog

yes

yes

yes

Hardware-Watchdog

(RC osc. based)

yes (disengageable)

yes (disengageable), can

be activated in SLEEP/

STOP

yes

Bit Search

yes

yes

yes

RTC

1 ch

1 ch

1 ch

Free Running Timer

8 ch

12 ch

9 ch

ICU

8 ch

10 ch

10 ch

OCU

8 ch

8 ch

8 ch

Reload Timer

8 ch

16 ch

8 ch

PPG 16-bit

16 ch

32 ch

16 ch

PFM 16-bit

1 ch

1 ch

1 ch

Sound Generator

1 ch

1 ch (old) + 1 ch (new)

1 ch

4 ch (8-bit) / 2 ch (16-bit)

4 ch (8-bit) / 2 ch (16-bit)

4 ch (8-bit) / 2 ch (16-bit)

6 ch (128msg)

6 ch (128msg)

3 ch (32msg)

4 ch + 4 ch FIFO + 8 ch

16 ch FIFO

4 ch + 4 ch FIFO + 4 ch

FIFO (asyncronous)

4 ch

8 ch

3 ch

Up/Down Counter (8/16-bit)

C_CAN

LIN-USART

I2C (400k)

4

Evaluation devices

DS705-00008-1v0-E

�MB91460Q Series

Feature

FR external bus

Evaluation devices

MB91V460A

MB91FV460B

MB91F469QA

yes (32bit addr, 32bit data, yes (32bit addr, 32bit data, yes (28bit addr, 32bit data,

8 chip selects)

8 chip selects)

8 chip selects)

External Interrupts

16 ch

32 ch

32 ch

NMI Interrupts

1 ch

1 ch

-

288 (23 non-multiplexed)

328 (24 non-multiplexed)

205

ADC (10 bit)

32 ch

32 ch + 22 ch

32 ch + 8 ch

Alarm Comparator

2 ch

2 ch

2 ch

Reset input (INITX)

yes

yes

yes

Hardware Standby Input (HSTX)

yes

yes

no

Clock Modulator

yes

yes

yes

Low power mode

yes

yes

yes

Supply Supervisor

yes

yes

yes

Clock Supervisor

yes

yes

yes

Main clock oscillator

4MHz

4MHz

4MHz

Sub clock oscillator

32kHz

32kHz

32kHz

RC Oscillator

100kHz

100kHz / 2MHz

100kHz / 2MHz

PLL

x 20

x 25

x 25

DSU4

yes

General IO ports

EDSU

yes (32 BP)

JTAG Boundary Scan

yes

3

yes (32 BP)

no

3

yes (16 BP) 3

no

no

yes

3V / 5V

3V / 5V / 1.8V

3V / 5V

Regulator

yes

no

yes

Power Consumption

n.a.

n.a.

16 ...100MHz)

RC Oscillator

Remarks

Typ

Main Oscillation

stabilisation time

ESD Protection

(Human body model)

Unit

Min

Power supply slew rate

Operating temperature

Value

0.6

ms

Vsurge

2

kV

fRC100kHz

50

100

200

kHz

fRC2MHz

1

2

4

MHz

Rdischarge = 1.5kΩ

Cdischarge = 100pF

VDDCORE ≥ 1.65V

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the

semiconductor device. All of the device’s electrical characteristics are warranted when the device is

operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation

outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on

the data sheet. Users considering application outside the listed conditions are advised to contact their

FUJITSU representatives beforehand.

VCC18C

VSS5

AVSS5

CS

104

DS705-00008-1v0-E

�MB91460Q Series

3. DC characteristics

Note: In the following tables, “VDD” means VDD35 for pins of ext. bus or VDD5 for other pins.

In the following tables, “VSS” means VSS5 for all pins.

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter Symbol

Pin name

Value

Min

Unit

Remarks

Typ

Max

⎯

VDD + 0.3

V

CMOS

hysteresis

input

⎯

VDD + 0.3

V

4.5 V ≤ VDD ≤ 5.5 V

⎯

VDD + 0.3

V

3 V ≤ VDD < 4.5 V

⎯

Port inputs if CMOS

Hysteresis 0.8/0.2 0.8 × VDD

input is selected

⎯

Port inputs if CMOS 0.7 × VDD

Hysteresis 0.7/0.3

0.74 × VDD

input is selected

⎯

AUTOMOTIVE

Hysteresis input is

selected

0.8 × VDD

⎯

VDD + 0.3

V

⎯

Port inputs if TTL

input is selected

2.0

⎯

VDD + 0.3

V

VIH

Input “H”

voltage

Condition

VIHR

INITX

⎯

0.8 × VDD

⎯

VDD + 0.3

V

INITX input pin

(CMOS

Hysteresis)

VIHM

MD_2 to

MD_0

⎯

VDD − 0.3

⎯

VDD + 0.3

V

Mode input pins

VIHX0S

X0, X0A

⎯

2.5

⎯

VDD + 0.3

V

External clock in

“Oscillation mode”

VIHX0F

X0

⎯

0.8 × VDD

⎯

VDD + 0.3

V

External clock in

“Fast Clock Input

mode”

⎯

Port inputs if CMOS

Hysteresis 0.8/0.2

input is selected

VSS − 0.3

⎯

0.2 × VDD

V

⎯

Port inputs if CMOS

Hysteresis 0.7/0.3

input is selected

VSS − 0.3

⎯

0.3 × VDD

V

VSS − 0.3

⎯

0.5 × VDD

V

4.5 V ≤ VDD ≤ 5.5 V

⎯

Port inputs if

AUTOMOTIVE

Hysteresis input is

selected

VSS − 0.3

⎯

0.46 × VDD

V

3 V ≤ VDD < 4.5 V

⎯

Port inputs if TTL

input is selected

VSS − 0.3

⎯

0.8

V

VIL

Input “L”

voltage

VILR

INITX

⎯

VSS − 0.3

⎯

0.2 × VDD

V

INITX input pin

(CMOS

Hysteresis)

VILM

MD_2 to

MD_0

⎯

VSS − 0.3

⎯

VSS + 0.3

V

Mode input pins

VILXDS

X0, X0A

⎯

VSS − 0.3

⎯

0.5

V

External clock in

“Oscillation mode”

DS705-00008-1v0-E

105

�MB91460Q Series

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter Symbol

Input “L”

voltage

Output “L“

voltage

Input leakage current

1.

106

Condition

X0

⎯

Value

Unit

Remarks

0.2 × VDD

V

External clock in

“Fast Clock Input

mode”

⎯

⎯

V

Driving strength

set to 2 mA

VDD − 0.5

⎯

⎯

V

Driving strength

set to 5 mA

I2C

3.0V ≤ VDD ≤ 5.5V,

outputs IOH = − 3mA

VDD − 0.5

⎯

⎯

V

VOL2

4.5V ≤ VDD ≤ 5.5V,

Normal IOH = + 2mA

outputs 3.0V ≤ VDD ≤ 4.5V,

IOH = + 1.6mA

⎯

⎯

0.4

V

Driving strength

set to 2 mA

VOL5

4.5V ≤ VDD ≤ 5.5V,

Normal IOH = + 5mA

outputs 3.0V ≤ VDD ≤ 4.5V,

IOH = + 3mA

⎯

⎯

0.4

V

Driving strength

set to 5 mA

VOL3

I2C

3.0V ≤ VDD ≤ 5.5V,

outputs IOH = + 3mA

⎯

⎯

0.4

V

−1

⎯

+1

IIL

3.0V ≤ VDD ≤ 5.5V

VSS5 < VI < VDD

Pnn_m TA=25 °C

*1

3.0V ≤ VDD ≤ 5.5V

VSS5 < VI < VDD

TA=TA(max)

Min

Typ

Max

VSS − 0.3

⎯

VOH2

4.5V ≤ VDD ≤ 5.5V,

Normal IOH = − 2mA

outputs 3.0V ≤ VDD ≤ 4.5V,

IOH = − 1.6mA

VDD − 0.5

VOH5

4.5V ≤ VDD ≤ 5.5V,

Normal IOH = − 5mA

outputs 3.0V ≤ VDD ≤ 4.5V,

IOH = − 3mA

VOH3

VILXDF

Output “H”

voltage

Pin

name

µA

−3

⎯

VSS5 < VI < VDD

+3

Pnn_m includes all GPIO pins. Analog (AN) channels and PullUp/PullDown are disabled.

DS705-00008-1v0-E

�MB91460Q Series

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

Analog input

leakage current

IAIN

Pull-up

resistance

RUP

Pnn_m *2

INITX

Pull-down

resistance

RDOWN

Pnn_m *3

Input

capacitance

CIN

ICC

Power

supply

current

ICCH

ANn *1

VDD5R

VDD5R

MB91

F469QAH

4.

5.

Unit

Remarks

Typ

Max

3.0V ≤ VDD ≤ 5.5V

TA=25 °C

−1

⎯

+1

µA

3.0V ≤ VDD ≤ 5.5V

TA=TA(max)

−3

⎯

+3

µA

3.0V ≤ VDD ≤ 3.6V

40

100

160

4.5V ≤ VDD ≤ 5.5V

25

50

100

3.0V ≤ VDD ≤ 3.6V

40

100

180

4.5V ≤ VDD ≤ 5.5V

25

50

100

-

5

15

pF

CLKB:

CLKP:

CLKT:

100 MHz

50 MHz

50 MHz

CLKCAN: 50 MHz

⎯

140

170

mA

TA = + 25 °C

⎯

50

210

µA

TA = + 105 °C

⎯

0.6

2.8

mA At stop mode *4

TA = + 125 °C

⎯

1.4

5.8

mA

TA = + 25 °C

⎯

120

560

µA

TA = + 105 °C

⎯

0.7

3.2

mA

TA = + 125 °C

⎯

1.5

7.2

mA

TA = + 25 °C

⎯

70

310

µA

TA = + 105 °C

⎯

0.65

3.0

TA = + 125 °C

⎯

1.45

6.0

RTC :

mA 100 kHz mode *4

*5

mA 32 kHz mode

AVSS5 < VI < AVCC5,

AVSS5 < VI < AVRH5

kΩ

kΩ

Code fetch from

Flash

RTC :

4 MHz mode *4

ILVE

VDD5

⎯

⎯

70

150

µA

External low voltage

detection

ILVI

VDD5R

⎯

⎯

50

100

µA

Internal low voltage

detection

⎯

⎯

250

500

µA

Main clock

(4 MHz)

⎯

⎯

20

40

µA

Sub clock

(32 kHz)

IOSC

3.

Value

Min

All except

VDD5, VDD5R,

f = 1 MHz

VSS5, AVCC5,

AVSS, AVRH5

MB91

F469QA,

1.

2.

Condition

VDD5

ANn includes all pins where AN channels are enabled.

Pnn_m includes all GPIO pins. The pull up resistors must be enabled by PPER/PPCR setting and

the pins must be in input direction.

Pnn_m includes all GPIO pins. The pull down resistors must be enabled by PPER/PPCR setting and

the pins must be in input direction.

Main regulator OFF, sub regulator set to 1.2V, Low voltage detection disabled.

Main regulator OFF, sub regulator set to 1.2V, Low voltage detection disabled, RC oscillator

disabled. Additional current consumption of Sub oscillator IOSC has to be taken into account.

DS705-00008-1v0-E

107

�MB91460Q Series

4. A/D converter characteristics

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol Pin name

Value

Min

Typ

Max

Unit

Remarks

Resolution

⎯

⎯

⎯

⎯

10

bit

Total error

⎯

⎯

−3

⎯

+3

LSB

Nonlinearity error

⎯

⎯

− 2.5

⎯

+ 2.5

LSB

Differential nonlinearity

error

⎯

⎯

− 1.9

⎯

+ 1.9

LSB

Zero reading voltage

VOT

ANn

AVRL −

1.5 LSB

AVRL +

0.5 LSB

AVRL +

2.5 LSB

V

Full scale reading voltage

VFST

ANn

AVRH −

3.5 LSB

AVRH −

1.5 LSB

AVRH +

0.5 LSB

V

0.6

⎯

t.b.d. 1

µs

4.5 V ≤ AVCC5 ≤

5.5 V

2.0

⎯

t.b.d. 1

µs

3.0 V ≤ AVCC5 ≤

4.5 V

0.4

⎯

⎯

µs

4.5 V ≤ AVCC5 ≤

5.5 V,

REXT < 2 kΩ

1.0

⎯

⎯

µs

3.0 V ≤ AVCC5 ≤

4.5 V,

REXT < 1 kΩ

1.0

⎯

⎯

µs

4.5 V ≤ AVCC5 ≤

5.5 V

3.0

⎯

⎯

µs

3.0 V ≤ AVCC5 ≤

4.5 V

⎯

⎯

11

pF

⎯

⎯

2.6

kΩ

4.5 V ≤ AVCC5 ≤

5.5 V

⎯

⎯

12.1

kΩ

3.0 V ≤ AVCC5 ≤

4.5 V

−1

⎯

+1

µA

TA = + 25 °C

−3

⎯

+3

µA

TA = TA(max)

Compare time

Sampling time

Conversion time

Input capacitance

Input resistance

Tcomp

Tsamp

Tconv

CIN

RIN

⎯

⎯

⎯

ANn

ANn

Analog input leakage

current

IAIN

ANn

Analog input voltage range

VAIN

ANn

AVRL

⎯

AVRH

V

Offset between input channels

⎯

ANn

⎯

⎯

4

LSB

1.

Paramater is under re-evaluation.

(Continued)

Note : The accuracy gets worse as AVRH - AVRL becomes smaller

108

DS705-00008-1v0-E

�MB91460Q Series

(Continued)

Parameter

Symbol Pin name

Value

Min

Typ

Max

Unit

Remarks

AVRH

AVRH5

0.75 ×

AVCC5

⎯

AVCC5

V

AVRL

AVSS5

AVSS5

⎯

AVCC5 ×

0.25

V

IA

AVCC5

⎯

2.5

5

mA

A/D Converter

active

IAH

AVCC5

⎯

⎯

5

µA

A/D Converter

not operated *1

IR

AVRH5

⎯

0.7

1

mA

A/D Converter

active

IRH

AVRH5

⎯

⎯

5

µA

A/D Converter

not operated *2

Reference voltage range

Power supply current

Reference voltage current

*1 : Supply current at AVCC5, if A/D converter and ALARM comparator are not operating,

(VDD5 = AVCC5 = AVRH = 5.0 V)

*2 : Input current at AVRH5, if A/D converter is not operating, (VDD5 = AVCC5 = AVRH = 5.0 V)

Sampling Time Calculation

Tsamp = ( 2.6 kOhm + REXT) × 11pF × 7; for 4.5V ≤ AVCC5 ≤ 5.5V

Tsamp = (12.1 kOhm + REXT) × 11pF × 7; for 3.0V ≤ AVCC5 ≤ 4.5V

Conversion Time Calculation

Tconv = Tsamp + Tcomp

Definition of A/D converter terms

• Resolution

Analog variation that is recognizable by the A/D converter.

• Nonlinearity error

Deviation between actual conversion characteristics and a straight line connecting the zero transition point

(00 0000 0000B ↔ 00 0000 0001B) and the full scale transition point (11 1111 1110B ↔ 11 1111 1111B).

• Differential nonlinearity error

Deviation of the input voltage from the ideal value that is required to change the output code by 1 LSB.

• Total error

This error indicates the difference between actual and theoretical values, including the zero transition error,

full scale transition error, and nonlinearity error.

DS705-00008-1v0-E

109

�MB91460Q Series

Total error

3FFH

3FEH

1.5 LSB’

Actual conversion

characteristics

Digital output

3FDH

{1 LSB’ (N − 1) + 0.5 LSB’}

004H

VNT

(measurement value)

003H

Actual conversion

characteristics

002H

Ideal characteristics

001H

0.5 LSB'

AVRH

AVSS5

Analog input

1LSB' (ideal value) = AVRH − AVSS5 [V]

1024

Total error of digital output N = VNT − {1 LSB' × (N − 1) + 0.5 LSB'}

1 LSB'

N : A/D converter digital output value

VOT' (ideal value) = AVSS5 + 0.5 LSB' [V]

VFST' (ideal value) = AVRH − 1.5 LSB' [V]

VNT : Voltage at which the digital output changes from (N + 1) H to NH

110

DS705-00008-1v0-E

�MB91460Q Series

Nonlinearity error

3FFH

Differential nonlinearity error

Actual conversion characteristics

Actual conversion characteristics

(N+1)H

3FEH

{1 LSB (N - 1) + VOT}

VFST

004H

VNT

(measurement value)

003H

002H

Ideal

characteristics

(measurement value)

Digital output

Digital output

3FDH

NH

(N-1)H

VFST

Actual conversion

characteristics

VNT

(measurement value)

Ideal characteristics

(N-2)H

001H

Actual conversion

characteristics

VTO (measurement value)

AVSS5

AVSS5

AVRH

Analog input

Nonlinearity error of digital output N =

VFST − VOT

1022

AVRH

Analog input

VNT − {1LSB × (N − 1) + VOT} [LSB]

1LSB

Differential nonlinearity error of digital output N =

1LSB =

(measurement value)

V (N + 1) T − VNT

1LSB

− 1 [LSB]

[V]

N

: A/D converter digital output value

VOT : Voltage at which the digital output changes from 000H to 001H.

VFST : Voltage at which the digital output changes from 3FEH to 3FFH.

DS705-00008-1v0-E

111

�MB91460Q Series

5. Alarm comparator characteristics

Parameter

Symbol

Pin name

Min

⎯

IA5ALMF

Power supply

current

Value

Typ

25

Max

40

Unit

Remarks

µA

Alarm comparator enabled in

fast mode (per

channel) *1

AVCC5

⎯

IA5ALMS

7

10

µA

Alarm comparator enabled in

normal mode

(per channel)

*1

IA5ALMH

⎯

⎯

5

µA

Alarm comparator disabled

−1

⎯

+1

µA

TA=25 °C

−3

⎯

+3

µA

TA=TA(max)

ALARM pin input current

IALIN

ALARM pin input voltage

range

VALIN

0

⎯

AVCC5

V

Alarm upper

limit

voltage

VIAH

AVCC5 × 0.78

− 3%

AVCC5 × 0.78

AVCC5 × 0.78

+ 3%

V

Alarm lower

limit

voltage

VIAL

AVCC5 × 0.36

− 5%

AVCC5 × 0.36

AVCC5 × 0.36

+ 5%

V

VIAHYS

50

⎯

250

mV

RIN

5

⎯

⎯

MΩ

tCOMPF

⎯

0.1

0.2

µs

Alarm hysteresis

voltage

Alarm input

resistance

ALARM_n

Comparion

time

tCOMPS

⎯

1

2

µs

Alarm comparator enabled in

fast mode *1

Alarm comparator enabled in

normal mode

*1

Note: *1 :

112

The fast Alarm Comparator mode is enabled by setting ACSR.MD=1

Setting ACSR.MD=0 sets the normal mode.

DS705-00008-1v0-E

�MB91460Q Series

6. FLASH memory program/erase characteristics

6.1.

MB91F469QA

(TA = 25oC, Vcc = 5.0V)

Parameter

Value

Unit

Remarks

2.0

s

Erasure programming time not

included

n*0.5

n*2.0

s

n is the number of Flash sector

of the device

6

100

µs

System overhead time not included

Min

Typ

Max

Sector erase time

-

0.5

Chip erase time

-

Word (16 or 32-bit width)

programming time

-

Programme/Erase cycle 10 000

cycle

Flash data retention time

year

20

*1

*1: This value was converted from the results of evaluating the reliability of the technology (using Arrhenius

equation to convert high temperature measurements into normalized value at 85oC)

DS705-00008-1v0-E

113

�MB91460Q Series

7. AC characteristics

7.1.

Clock timing

(VDD5 = 3.0 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Clock frequency

Symbol Pin name

fC

Value

Unit

Condition

16

MHz

Opposite phase external

supply or crystal

100

kHz

Min

Typ

Max

X0

X1

3.5

4

X0A

X1A

32

32.768

• Clock timing conditions

tC

Output pin

X0,

X1,

X0A,

X1A

0.8 VCC

0.2 VCC

PWH

114

PWL

DS705-00008-1v0-E

�MB91460Q Series

7.2.

Reset input ratings

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

INITX input time

(at power-on)

INITX input time

(other than the above)

Symbol

tINTL

Pin name

Condition

Value

Unit

Min

Max

10

⎯

ms

20

⎯

µs

⎯

INITX

tINTL

INITX

DS705-00008-1v0-E

0.2 VCC

115

�MB91460Q Series

7.3.

LIN-USART Timings at VDD5 = 3.0 to 5.5 V

• Conditions during AC measurements

• All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD5 = 3.0 V to 5.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = -40 °C to TA(max)

- Cl = 50 pF (load capacity value of pins when testing)

- VOL = 0.2 x VDD5

- VOH = 0.8 x VDD5

- EPILR = 0, PILR = 1 (Automotive Level == worst case)

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

Serial clock

cycle time

tSCYCI

SCKn

SCK ↓ → SOT

delay time

tSLOVI

SCKn

SOTn

SOT → SCK ↓

delay time

tOVSHI

SCKn

SOTn

Valid SIN →

SCK ↑ setup time

tIVSHI

SCKn

SINn

SCK ↑ → valid

SIN hold time

tSHIXI

Serial clock

“H” pulse width

Condition

VDD5 = 3.0 V to 4.5 V VDD5 = 4.5 V to 5.5 V

Unit

Min

Max

Min

Max

4 tCLKP

⎯

4 tCLKP

⎯

ns

− 30

30

− 20

20

ns

m×

tCLKP − 30*

⎯

m×

tCLKP − 20*

⎯

ns

tCLKP + 55

⎯

tCLKP + 45

⎯

ns

SCKn

SINn

0

⎯

0

⎯

ns

tSHSLE

SCKn

tCLKP + 10

⎯

tCLKP + 10

⎯

ns

Serial clock

“L” pulse width

tSLSHE

SCKn

tCLKP + 10

⎯

tCLKP + 10

⎯

ns

SCK ↓ → SOT

delay time

tSLOVE

SCKn

SOTn

⎯

2 tCLKP + 55

⎯

2 tCLKP + 45

ns

Valid SIN →

SCK ↑ setup time

tIVSHE

SCKn

SINn

10

⎯

10

⎯

ns

SCK ↑ → valid

SIN hold time

tSHIXE

SCKn

SINn

tCLKP + 10

⎯

tCLKP + 10

⎯

ns

SCK rising time

tFE

SCKn

⎯

20

⎯

20

ns

SCK falling time

tRE

SCKn

⎯

20

⎯

20

ns

Internal

clock

operation

(master

mode)

External

clock

operation

(slave

mode)

* : Parameter m depends on tSCYCI and can be calculated as :

• if tSCYCI = 2*k*tCLKP, then m = k, where k is an integer > 2

• if tSCYCI = (2*k + 1)*tCLKP, then m = k + 1, where k is an integer > 1

Notes :

116

• The above values are AC characteristics for CLK synchronous mode.

• tCLKP is the cycle time of the peripheral clock.

DS705-00008-1v0-E

�MB91460Q Series

• Internal clock mode (master mode)

tSCYCI

SCKn

for ESCR:SCES = 0

VOH

VOL

VOL

VOH

SCKn

for ESCR:SCES = 1

VOH

VOL

tSLOVI

tOVSHI

VOH

VOL

SOTn

tIVSHI

tSHIXI

VIH

VIL

SINn

VIH

VIL

• External clock mode (slave mode)

tSLSHE

SCKn

for ESCR:SCES = 0

VOH

SCKn

for ESCR:SCES = 1

VOL

tSHSLE

VOH

VOL

VOL

VOH

VOH

VOL

VOH

VOL

tRE

tFE

tSLOVE

SOTn

VOH

VOL

tIVSHE

SINn

DS705-00008-1v0-E

VIH

VIL

tSHIXE

VIH

VIL

117

�MB91460Q Series

7.4.

I2C AC Timings at VDD5 = 3.0 to 5.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 3 mA

- VDD5 = 3.0 V to 5.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = − 40 °C to TA(max)

- Cl = 50 pF

- VOL = 0.3 × VDD5

- VOH = 0.7 × VDD5

- EPILR = 0, PILR = 0 (CMOS Hysteresis 0.3 × VDD5/0.7 × VDD5)

Fast mode:

(VDD5 = 3.5 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

fSCL

Value

Unit

Min

Max

SCLn

0

400

kHz

tHD;STA

SCLn, SDAn

0.6

⎯

µs

LOW period of the SCL clock

tLOW

SCLn

1.3

⎯

µs

HIGH period of the SCL clock

tHIGH

SCLn

0.6

⎯

µs

Setup time for a repeated START

condition

tSU;STA

SCLn, SDAn

0.6

⎯

µs

Data hold time for I2C-bus devices

tHD;DAT

SCLn, SDAn

0

0.9

µs

Data setup time

tSU;DAT

SCLn SDAn

100

⎯

ns

Rise time of both SDA and SCL

signals

tr

SCLn, SDAn

20 + 0.1Cb

300

ns

Fall time of both SDA and SCL

signals

tf

SCLn, SDAn

20 + 0.1Cb

300

ns

Setup time for STOP condition

tSU;STO

SCLn, SDAn

0.6

⎯

µs

Bus free time between a STOP

and START condition

tBUF

SCLn, SDAn

1.3

⎯

µs

Capacitive load for each bus line

Cb

SCLn, SDAn

⎯

400

pF

Pulse width of spike suppressed

by input filter

tSP

SCLn, SDAn

0

(1..1.5) ×

tCLKP

ns

SCL clock frequency

Hold time (repeated) START

condition. After this period, the first

clock pulse is generated

Remark

*1

*1 The noise filter will suppress single spikes with a pulse width of 0ns and between (1 to 1.5) cycles

of peripheral clock, depending on the phase relationship between I2C signals (SDA, SCL) and peripheral clock.

Note: tCLKP is the cycle time of the peripheral clock.

118

DS705-00008-1v0-E

�DS705-00008-1v0-E

SCL

SDA

tHD;STA

tf

S

tr

tHD;DAT

tLOW

tHIGH

tSU;DAT

tSU;STA

Sr

tHD;STA

tSP

tr

P

tSU;STO

tBUF

S

tf

MB91460Q Series

119

�MB91460Q Series

7.5.

Free-run timer clock

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Input pulse width

Symbol

Pin name

Condition

tTIWH

tTIWL

CKn

⎯

Value

Min

Max

4tCLKP

⎯

Unit

ns

Note : tCLKP is the cycle time of the peripheral clock.

CKn

tTIWH

7.6.

tTIWL

Trigger input timing

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to TA(max))

Parameter

Input capture input trigger

A/D converter trigger

Symbol

Pin name

Condition

tINP

ICUn

tATGX

ATGX

Value

Unit

Min

Max

⎯

5tCLKP

⎯

ns

⎯

5tCLKP

⎯

ns

Note : tCLKP is the cycle time of the peripheral clock.

tATGX, tINP

ICUn,

ATGX

120

DS705-00008-1v0-E

�MB91460Q Series

7.7.

External Bus AC Timings at VDD35 = 4.5 to 5.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD35 = 4.5 V to 5.5 V, Iload = 5 mA

- VSS5 = 0 V

- TA = − 40 °C to TA(max)

- Cl = 50 pF

- VOL = 0.2 × VDD35

- VOH = 0.8 × VDD35

- EPILR = 0, PILR = 1 (Automotive Level = = worst case)

7.7.1.

Basic Timing

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to BAAX delay time

SYSCLK ↓ to Address valid delay time

Symbol

tCLCH

tCHCL

Pin name

Max

1/2 × tCLKT − 4

1/2 × tCLKT + 5

ns

1/2 × tCLKT − 5

1/2 × tCLKT + 4

ns

⎯

9

ns

⎯

8

ns

−2

8

ns

SYSCLK

ASX

⎯

8

ns

⎯

7

ns

SYSCLK

BAAX

⎯

5

ns

-2

⎯

ns

SYSCLK

A27 to A0

⎯

10

ns

SYSCLK

SYSCLK

CSXn

tCHCSL

tCLASL

tCLASH

tCLBAL

tCLBAH

tCLAV

Unit

Min

tCLCSL

tCLCSH

Value

Note : tCLKT is the cycle time of the external bus clock.

DS705-00008-1v0-E

121

�MB91460Q Series

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

tCLBAH

tCLBAL

BAAX

122

DS705-00008-1v0-E

�MB91460Q Series

7.7.2.

Synchronous/Asynchronous read access with external MCLKI input

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

tCHRL

Value

Unit

Min

Max

SYSCLK

RDX

−2

7

ns

tCHRH

MCLKI

RDX

10

20

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

20

⎯

ns

RDX ↑ to Data valid hold time

(external MCLKI input)

tRHDX

RDX

D31 to D0

0

⎯

ns

Data valid to MCLKI ↑ setup time

tDSCH

MCLKI

D31 to D0

1

⎯

ns

MCLKI ↑ to Data valid hold time

tCHDX

MCLKI

D31 to D0

3

⎯

ns

SYSCLK ↓ to WRXn (as byte enable)

delay time

tCLWRL

⎯

9

ns

−1

⎯

ns

⎯

9

ns

⎯

8

ns

SYSCLK ↑ /MCLKI ↑ to RDX delay

time

SYSCLK ↓ to CSXn delay time

tCLWRH

tCLCSL

tCLCSH

SYSCLK

WRXn

SYSCLK

CSXn

Note: The usage of the external feedback from MCLKO to MCLKI is not recommended.

DS705-00008-1v0-E

123

�MB91460Q Series

SYSCLK

MCLKI

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tDSCH

tRHDX

tCHDX

DATA IN

124

DS705-00008-1v0-E

�MB91460Q Series

7.7.3.

Synchronous/Asynchronous read access with internal MCLKO --> MCLKI feedback

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin name

tCHRL

SYSCLK

RDX

tCHRH

Value

Unit

Min

Max

−2

7

ns

−2

4

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

19

⎯

ns

RDX ↑ to Data valid hold time

(internal MCLKO → MCLKI

/MCLKI feedback)

tRHDX

RDX

D31 to D0

0

⎯

ns

⎯

9

ns

−1

⎯

ns

⎯

9

ns

⎯

8

ns

tCLWRL

SYSCLK ↓ to WRXn

(as byte enable) delay time

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

DS705-00008-1v0-E

125

�MB91460Q Series

7.7.4.

Synchronous write access - byte control type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to WEX delay time

Symbol

Pin name

tCLWL

SYSCLK

WEX

tCLWH

Value

Unit

Min

Max

⎯

8

ns

-2

⎯

ns

Data valid to WEX ↓ setup time

tDSWL

WEX

D31 to D0

−5

⎯

ns

WEX ↑ to Data valid hold time

tWHDH

WEX

D31 to D0

tCLKT − 10

⎯

ns

SYSCLK ↓ to WRXn (as byte enable)

delay time

tCLWRL

SYSCLK

WRXn

⎯

9

ns

−1

⎯

ns

⎯

9

ns

⎯

8

ns

SYSCLK ↓ to CSXn delay time

tCLWRH

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

126

DS705-00008-1v0-E

�MB91460Q Series

7.7.5.

Synchronous write access - no byte control type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to WRXn delay time

Symbol

Pin name

tCLWRL

SYSCLK

WRXn

tCLWRH

Value

Unit

Min

Max

⎯

9

ns

−1

⎯

ns

Data valid to WRXn ↓ setup time

tDSWRL

WRXn

D31 to D0

−6

⎯

ns

WRXn ↑ to Data valid hold time

tWRHDH

WRXn

D31 to D0

tCLKT − 10

⎯

ns

SYSCLK

CSXn

⎯

9

ns

⎯

8

ns

SYSCLK ↓ to CSXn delay time

tCLCSL

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

DS705-00008-1v0-E

127

�MB91460Q Series

7.7.6.

Asynchronous write access - byte control type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

WEX ↓ to WEX ↑ pulse width

tWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT − 6

⎯

ns

tDSWL

WEX

D31 to D0

1/2 × tCLKT − 9

⎯

ns

tWHDH

WEX

D31 to D0

1/2 × tCLKT − 7

⎯

ns

WEX

WRXn

⎯

1/2 × tCLKT + 2

ns

1/2 × tCLKT − 1

⎯

ns

⎯

1/2 × tCLKT - 1

ns

1/2 × tCLKT + 1

⎯

ns

tWRLWL

tWHWRH

tCLWL

WEX

CSXn

tWHCH

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

128

DS705-00008-1v0-E

�MB91460Q Series

7.7.7.

Asynchronous write access - no byte control type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

WRXn ↓ to WRXn ↑ pulse width

tWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT − 6

⎯

ns

tDSWRL

WRXn

D31 to D0

1/2 × tCLKT − 9

⎯

ns

tWRHDH

WRXn

D31 to D0

1/2 × tCLKT − 7

⎯

ns

WRXn

CSXn

⎯

1/2 × tCLKT − 1

ns

1/2 × tCLKT + 1

⎯

ns

tCLWRL

tWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

DS705-00008-1v0-E

129

�MB91460Q Series

7.7.8.

RDY waitcycle insertion

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

RDY setup time

tRDYS

RDY hold time

tRDYH

Value

Unit

Min

Max

SYSCLK

RDY

19

⎯

ns

SYSCLK

RDY

0

⎯

ns

SYSCLK

tRDYS

tRDYH

RDY

130

DS705-00008-1v0-E

�MB91460Q Series

7.7.9.

Bus hold timing

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to BGRNTX delay time

Symbol

Pin name

tCLBGL

tCLBGH

Bus HIZ to BGRNTX ↓

tAXBGL

BGRNTX ↑ to Bus drive

tBGHAV

Value

Unit

Min

Max

SYSCLK

BGRNTX

⎯

5

ns

⎯

5

ns

BGRNTX

MCLK*

A0 to An

RDX, ASX

WRXn,WEX

CSXn,BAAX

tCLKT + 2

⎯

ns

tCLKT + 1

⎯

ns

Note : BRQ must be kept High until the bus is granted (this is acknowledged by the falling edge of BGRNTX).

It must be kept High as long as the bus shall be hold.

After releasing the bus (BRQ set to Low) this is acknowledged by the rising edge of BGRNTX.

SYSCLK

BRQ

tCLBGL

tCLBGH

BGRNTX

tAXBGL

tBGHAV

ADDR, RDX, WRX,

WEX, CSXn, ASX,

MCLKE, MCLKI,

MCLKO, BAAX

DS705-00008-1v0-E

131

�MB91460Q Series

7.7.10. Clock relationships

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK to MCLKO

Symbol

Pin name

tCSHMH

SYSCLK

MCLKO

tCSLML

MCLKO ↓ to MCLKE (in sleep mode)

tCLML

MCLKO

MCLKE

tCLMH

Value

Unit

Min

Max

1

5

ns

0

2

ns

⎯

5

ns

−3

⎯

ns

SYSCLK

tCSHMH

tCSLML

MCLKO

tCLML

tCLMH

MCLKE (sleep)

132

DS705-00008-1v0-E

�MB91460Q Series

7.7.11. DMA transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to DACKX delay time

SYSCLK ↓ to DEOP delay time

Symbol

Pin name

tCLDAL

tCLDAH

tCLDEL

tCLDEH

Value

Unit

Min

Max

SYSCLK

DACKXn

⎯

8

ns

⎯

8

ns

SYSCLK

DEOPn

⎯

7

ns

⎯

9

ns

SYSCLK ↑ to DACKX delay time

(ADDR → CS delayed)

tCHDAL

SYSCLK

DACKXn

−1

8

ns

SYSCLK ↑ to DEOP delay time

(ADDR → CS delayed)

tCHDEL

SYSCLK

DEOPn

−1

8

ns

DREQ setup time

tDRQS

SYSCLK

DREQn

19

⎯

ns

DREQ hold time

tDRQH

SYSCLK

DREQn

0

⎯

ns

DEOTXn setup time

tDTXS

SYSCLK

DEOTXn

20

⎯

ns

DEOTXn hold time

tDTXH

SYSCLK

DEOTXn

0

⎯

ns

Note : DREQ and DEOTX must be applied for at least 5 × tCLKT to ensure that they are really sampled and evaluated.

Under best case conditions (DMA not busy) only setup and hold times are required.

DS705-00008-1v0-E

133

�MB91460Q Series

SYSCLK

tCLDAL

tCLDAH

tCLDEL

tCLDEH

DACKX

DEOP

tCHDAL

delayed DACKX

tCHDEL

delayed DEOP

tDRQS

tDRQH

tDTXS

tDTXH

DREQ

DEOTX

134

DS705-00008-1v0-E

�MB91460Q Series

7.7.12. DMA flyby transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↑ to IORDX delay time

Symbol

Pin name

tCHIRL

tCHIRH

tCHIWL

SYSCLK ↑ to IOWRX delay time

tCHIWH

Value

Unit

Min

Max

SYSCLK

IORDX

-2

8

ns

0

4

ns

SYSCLK

IOWRX

-2

8

ns

-1

3

ns

:

SYSCLK

tCHIRH

tCHIRL

IORDX

tCHIWH

tCHIWL

IOWRX

DS705-00008-1v0-E

135

�MB91460Q Series

7.8.

External Bus AC Timings at VDD35 = 3.0 to 4.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD35 = 3.0 V to 4.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = − 40 °C to TA(max)

- Cl = 50 pF

- VOL = 0.2 × VDD35

- VOH = 0.8 × VDD35

- EPILR = 0, PILR = 1 (Automotive Level = = worst case)

7.8.1.

Basic Timing

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to BAAX delay time

SYSCLK ↓ to Address valid delay

time

136

Symbol

tCLCH

tCHCL

Pin name

Max

1/2 × tCLKT − 1

1/2 × tCLKT + 3

ns

1/2 × tCLKT − 3

1/2 × tCLKT + 1

ns

⎯

9

ns

⎯

7

ns

−1

4

ns

SYSCLK

ASX

⎯

5

ns

⎯

6

ns

SYSCLK

BAAX

⎯

6

ns

0

⎯

ns

SYSCLK

A27 to A0

⎯

13

ns

SYSCLK

SYSCLK

CSXn

tCHCSL

tCLASL

tCLASH

tCLBAL

tCLBAH

tCLAV

Unit

Min

tCLCSL

tCLCSH

Value

DS705-00008-1v0-E

�MB91460Q Series

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

tCLBAH

tCLBAL

BAAX

DS705-00008-1v0-E

137

�MB91460Q Series

7.8.2.

Synchronous/Asynchronous read access with external MCLKI input

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

tCHRL

Value

Unit

Min

Max

SYSCLK

RDX

−1

3

ns

tCHRH

MCLKI

RDX

11

25

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

25

⎯

ns

RDX ↑ to Data valid hold time

(external MCLKI input)

tRHDX

RDX

D31 to D0

0

⎯

ns

Data valid to MCLKI ↑ setup time

tDSCH

MCLKI

D31 to D0

1

⎯

ns

MCLKI ↑ to Data valid hold time

tCHDX

MCLKI

D31 to D0

3

⎯

ns

SYSCLK ↓ to WRXn

(as byte enable) delay time

tCLWRL

⎯

5

ns

-1

⎯

ns

⎯

5

ns

⎯

6

ns

SYSCLK ↑/MCLKI ↑ to RDX

delay time

SYSCLK ↓ to CSXn delay time

tCLWRH

tCLCSL

tCLCSH

SYSCLK

WRXn

SYSCLK

CSXn

Note: The usage of the external feedback from MCLKO to MCLKI is not recommended.

138

DS705-00008-1v0-E

�MB91460Q Series

SYSCLK

MCLKI

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tDSCH

tRHDX

tCHDX

DATA IN

DS705-00008-1v0-E

139

�MB91460Q Series

7.8.3.

Synchronous/Asynchronous read access with internal MCLKO --> MCLKI feedback

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin name

tCHRL

SYSCLK

RDX

tCHRH

Value

Unit

Min

Max

−1

3

ns

−2

4

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

25

⎯

ns

RDX ↑ to Data valid hold time

(internal MCLKO → MCLKI /

/MCLKI feedback)

tRHDX

RDX

D31 to D0

0

⎯

ns

⎯

5

ns

-1

⎯

ns

⎯

5

ns

⎯

6

ns

tCLWRL

SYSCLK ↓ to WRXn

(as byte enable) delay time

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

tCLCSH

SYSCLK

WRXn

SYSCLK

CSXn

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

140

DS705-00008-1v0-E

�MB91460Q Series

7.8.4.

Synchronous write access - byte control type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to WEX delay time

Symbol

Pin name

tCLWL

SYSCLK

WEX

tCLWH

Value

Unit

Min

Max

⎯

5

ns

-1

⎯

ns

Data valid to WEX ↓ setup time

tDSWL

WEX

D31 to D0

− 11

⎯

ns

WEX ↑ to Data valid hold time

tWHDH

WEX

D31 to D0

tCLKT − 13

⎯

ns

SYSCLK ↓ to WRXn (as byte enable)

delay time

tCLWRL

SYSCLK

WRXn

⎯

5

ns

-1

⎯

ns

⎯

5

ns

⎯

6

ns

SYSCLK ↓ to CSXn delay time

tCLWRH

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

DS705-00008-1v0-E

141

�MB91460Q Series

7.8.5.

Synchronous write access - no byte control type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to WRXn delay time

Symbol

Pin name

tCLWRL

SYSCLK

WRXn

tCLWRH

Value

Unit

Min

Max

⎯

5

ns

-1

⎯

ns

Data valid to WRXn ↓ setup time

tDSWRL

WRXn

D31 to D0

− 11

⎯

ns

WRXn ↑ to Data valid hold time

tWRHDH

WRXn

D31 to D0

tCLKT − 13

⎯

ns

SYSCLK

CSXn

⎯

5

ns

⎯

6

ns

SYSCLK ↓ to CSXn delay time

tCLCSL

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

142

DS705-00008-1v0-E

�MB91460Q Series

7.8.6.

Asynchronous write access - byte control type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

WEX ↓ to WEX ↑ pulse width

tWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT − 4

⎯

ns

tDSWL

WEX

D31 to D0

1/2 × tCLKT − 12

⎯

ns

tWHDH

WEX

D31 to D0

1/2 × tCLKT − 11

⎯

ns

WEX

WRXn

⎯

1/2 × tCLKT + 1

ns

1/2 × tCLKT − 1

⎯

ns

⎯

1/2 × tCLKT − 1

ns

1/2 × tCLKT + 1

⎯

ns

tWRLWL

tWHWRH

tCLWL

WEX

CSXn

tWHCH

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

DS705-00008-1v0-E

143

�MB91460Q Series

7.8.7.

Asynchronous write access - no byte control type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

WRXn ↓ to WRXn ↑ pulse width

tWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT − 3

⎯

ns

tDSWRL

WRXn

D31 to D0

1/2 × tCLKT − 12

⎯

ns

tWRHDH

WRXn

D31 to D0

1/2 × tCLKT − 11

⎯

ns

WRXn

CSXn

⎯

1/2 × tCLKT − 1

ns

1/2 × tCLKT + 1

⎯

ns

tCLWRL

tWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

144

DS705-00008-1v0-E

�MB91460Q Series

7.8.8.

RDY waitcycle insertion

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

Symbol

Pin name

RDY setup time

tRDYS

RDY hold time

tRDYH

Value

Unit

Min

Max

SYSCLK

RDY

24

⎯

ns

SYSCLK

RDY

0

⎯

ns

SYSCLK

tRDYS

tRDYH

RDY

DS705-00008-1v0-E

145

�MB91460Q Series

7.8.9.

Bus hold timing

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to BGRNTX delay time

Symbol

Pin name

tCLBGL

tCLBGH

Bus HIZ to BGRNTX ↓

tAXBGL

BGRNTX ↑ to Bus drive

tBGHAV

Value

Unit

Min

Max

SYSCLK

BGRNTX

⎯

5

ns

⎯

6

ns

BGRNTX

MCLK*

A0 to An

RDX, ASX

WRXn,WEX

CSXn,BAAX

tCLKT + 2

⎯

ns

tCLKT - 2

⎯

ns

Note : BRQ must be kept High until the bus is granted (this is acknowledged by the falling edge of BGRNTX).

It must be kept High as long as the bus shall be hold.

After releasing the bus (BRQ set to Low) this is acknowledged by the rising edge of BGRNTX.

SYSCLK

BRQ

tCLBGL

tCLBGH

BGRNTX

tAXBGL

tBGHAV

ADDR, RDX, WRX,

WEX, CSXn, ASX,

MCLKE, MCLKI,

MCLKO, BAAX

146

DS705-00008-1v0-E

�MB91460Q Series

7.8.10. Clock relationships

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK to MCLKO

Symbol

Pin name

tCSHMH

tCSLML

tCLML

MCLKO ↓ to MCLKE

(in sleep mode)

tCLMH

Value

Unit

Min

Max

SYSCLK

MCLKO

1

5

ns

0

2

ns

MCLKO

MCLKE

⎯

4

ns

-3

⎯

ns

SYSCLK

tCSHMH

tCSLML

MCLKO

tCLML

tCLMH

MCLKE (sleep)

DS705-00008-1v0-E

147

�MB91460Q Series

7.8.11. DMA transfer

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max))

Parameter

SYSCLK ↓ to DACKX delay time

SYSCLK ↓ to DEOP delay time

Symbol

Pin name

tCLDAL

tCLDAH

tCLDEL

tCLDEH

Value

Unit

Min

Max

SYSCLK

DACKXn

⎯

9

ns

⎯

7

ns

SYSCLK

DEOPn

⎯

8

ns

⎯

7

ns

SYSCLK ↑ to DACKX delay time

(ADDR → CS delayed)

tCHDAL

SYSCLK

DACKXn

0

8

ns

SYSCLK ↑ to DEOP delay time

(ADDR → CS delayed)

tCHDEL

SYSCLK

DEOPn

−1

8

ns

DREQ setup time

tDRQS

SYSCLK

DREQn

25

⎯

ns

DREQ hold time

tDRQH

SYSCLK

DREQn

0

⎯

ns

DEOTXn setup time

tDTXS

SYSCLK

DEOTXn

26

⎯

ns

DEOTXn hold time

tDTXH

SYSCLK

DEOTXn

0

⎯

ns

Note : DREQ and DEOTX must be applied for at least 5 × tCLKT to ensure that they are really sampled and evaluated.

Under best case conditions (DMA not busy) only setup and hold times are required.

148

DS705-00008-1v0-E

�MB91460Q Series

SYSCLK

tCLDAL

tCLDAH

tCLDEL

tCLDEH

DACKX

DEOP

tCHDAL

delayed DACKX

tCHDEL

delayed DEOP

tDRQS

tDRQH

tDTXS

tDTXH

DREQ

DEOTX

DS705-00008-1v0-E

149

�MB91460Q Series

7.8.12. DMA flyby transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = −40 °C to TA(max)) :

Parameter

SYSCLK ↑ to IORDX delay time

Symbol

Pin name

tCHIRL

tCHIRH

tCHIWL

SYSCLK ↑ to IOWRX delay time

tCHIWH

Value

Unit

Min

Max

SYSCLK

IORDX

-1

6

ns

-2

3

ns

SYSCLK

IOWRX

0

5

ns

-2

3

ns

SYSCLK

tCHIRH

tCHIRL

IORDX

tCHIWH

tCHIWL

IOWRX

150

DS705-00008-1v0-E

�MB91460Q Series

DS705-00008-1v0-E

151

�MB91460Q Series

■ ORDERING INFORMATION

Part number

MB91F469QAPB-GSE1

MB91F469QAHPB-GSE1

152

Package

320-pin plastic BGA

(BGA-320P-M06)

Maximum ambient

temperature

TA(max)

+ 105 °C

+ 125 °C

Remarks

Lead-free package

DS705-00008-1v0-E

�MB91460Q Series

■ PACKAGE DIMENSION

×

Please check the latest package dimension at the following URL:

http://edevice.fujitsu.com/package/en-search/

×

�MB91460Q Series

■ REVISION HISTORY

1. Changes in Preceding Editions

154

Version

Date

Remark

2.0

2008-01-28

Initial version

2.1

2008-02-05

Pins 257 to 320 are GND.

2.2

2008-02-11

The CANs have only 32-message buffers

2.3

2008-02-15

Corrected product lineup: No NMI function,

updated disclaimer at the end

2.4

2008-02-21

ICU8,9: PFR must be 0, DDR recommended 0

2.5

2008-02-22

Corrected naming and size of Flash-cache (F-cache)

2.6

2008-04-30

- IO MAP: initial values for LVSEL + REGSEL corrected

- Pin 110: CK0 --> CK0/8 (added Free Run Timer 8)

- Flash memory operation modes: Added note about the

"flash access mode switching" incl. Boot ROM start address

- Flash parallel programming: wait times after power-on / INIT added

- External Bus AC spec: TAXBGL values corrected

- IO Map: removed INT Relocation control registers (was reservation only)

- INT Vector Table: Added resource numbers for INT16-23

- added chapter SPECIAL PORT / RESOURCE ASSIGNMENTS

2.7

2008-05-05

INT Vector Table: Added resource numbers for FRT8 and ICU8,9

2.8

2008-05-08

Updated the section about re-located interrupts (Ports 34+35)

2.9

2008-08-18

- Corrected I/O circuit type of P24_4 from A to C.

- SPECIAL PORT / RESOURCE ASSIGNMENTS: corrected the notes

that only digital inputs (no outputs) are disabled if an analog fnuction (ADC)

is enabled on this port.

- FLASH: Corrected a typo in the note about the

"flash access mode switching" incl. address in Boot ROM;

added section "Poweron Sequence in parallel programming mode"

- IO CIRCUIT TYPE: fixed typos in Remarks

- "Notes on PS register" updated

- IO Map: Initial values of PFR00 - PFR10 corrected (depend on MD=000)

- INT Vector Table: Added Resource number for ADC1 (RN=113);

corrected the footnotes

- Electrical Characteristics: removed the note that analog input/output

pins cannot accept +B signal input.

- DC Characteristics: Updated IIL and IAIN, updated ILVE and ILVI,

corrected values of Pull up/down resistances,

updated and re-ordered the table footnotes

- ADC Characteristics: fixed the typos regarding "nonlinearity error"

- fixed offset between input channels

2.10

2008-08-19

DC characteristics: updated the current consumption values ICC, ICCH

(target values based on MB91F469G)

2.11

2008-09-23

I/O MAP: Removed the notes about new INT disable feature,

added bookmarks inside IO MAP

Added note to IOS register (addr. 0xC03) "always write 1 to IOS[1]"

DS705-00008-1v0-E

�MB91460Q Series

Version

Date

Remark

PIN Definitions: Corrected pin 145 into P34_5

Flash Security Vector FSV2: Corrected typo in table header

2.12

2.13

2008-11-07

2009-01-09

Embedded Program/Data Memory (Flash):

Added section 7 “Notes About Flash Memory CRC Calculation”

(CLKB must be faster then the RC clock)

Block Diagram: Added External Bus Instruction Cache

Special Port/Resource Assignments: Corrected section

“The Additional External Interrupts” (PFR/EPFR/ADERH settings)

Special Port/Resource Assignments: Re-located External Interrupts:

Corrected that SDA2 is enabled by PFR24 (not by EPFR24)

IO Map: Added EPFR34, EPFR35 at address 0x00DE2, 0x00DE3

IO Map: Corrected the table header (address +0,+1,+2,+3)

DC characteristics: corrected the current consumption values ICC, ICCH

Page

26

107

Section

Changes in DS07-16614-1E

■ I/O CIRCUIT TYPES

Changed the table of Type I.

Pull-down resistor value: 50 kW approx. →

Pull-down resistor value: 50 kΩ approx.

■ ELECTRICAL CHARACTERISTICS

4. A/D converter characteristics

Changed the table of “Zero reading voltage”.

AVRL - 1.5 → AVRL - 1.5 LSB

AVRL + 0.5 → AVRL + 0.5 LSB

AVRL + 2.5 → AVRL + 2.5 LSB

LSB → V

Changed the table of “Full scale reading voltage”.

AVRH - 3.5 → AVRH - 3.5 LSB

AVRH - 1.5 → AVRH - 1.5 LSB

AVRH + 0.5 → AVRH + 0.5 LSB

LSB → V

DS705-00008-1v0-E

155

�MB91460Q Series

2. Changes in This Edition

Preceding edition DS07-16614-1E

Current edition DS705-00008-1v0-E

Page

Section

(2009-06-24)

(2010-09-03)

Changes

1

■ DESCRIPTION

Fujitsu Microelectronics → Fujitsu Semiconductor

3

■ DESCRIPTION

2. Internal peripheral resources

Renamed the Low Voltage detection → Supply Supervisor

3

■ DESCRIPTION

2. Internal peripheral resources

Removed the note about PHILIPS I2C license

3

■ DESCRIPTION

3. Package and technology

Changed Operating temperature range

upper limit from + 105 °C → + 105 °C / + 125 °C and

added footnote about TA(max)

4

■ PRODUCT LINEUP

Added MB91FV460B (the new EVA device), and removed lines which are irrelevant for MB91F469Q.

4

■ PRODUCT LINEUP

Software-Watchdog

Renamed "Watchdog timer" → "Software watchdog"

Renamed "Watchdog timer (RC osc. based)"

→ "Hardware-Watchdog (RC osc. based)"

5

■ PRODUCT LINEUP

Temperature Range (TA)

Changed the symbol of ambient temperature from "Ta"

into "TA", changed MB91F469Q upper limit from 105 °C

→ “TA(max)”

5

■ PRODUCT LINEUP

Power Consumption

Changed the value from < 1W → < 2W

33

■ HANDLING DEVICES

3. Power supply pins

Corrected typo "capacitator" → "capacitor"

39

■ CPU AND CONTROL UNIT

3. Programming model

3.1. Basic programming model

Corrected the name of program status register from

"RS" → "PS"

62,

64,

69

■ I/O MAP

TCDT0 [R/W] to TCDT8 [R/W]

Free Run Timer 0-8: Changed the TCDT register

initialization value from 0xXXXX → 0x0000 (by RST)

63

■ I/O MAP

LIN-USART (FIFO) 11

Corrected RDR00/TDR00 → RDR11/TDR11

72

■ I/O MAP

PFR01 to PFR10

Corrected the foot note number from 4 → 5

■ RECOMMENDED SETTINGS

1. PLL and Clockgear settings,

2. Clock Modulator settings

Added “Please refer to Absolute maximum ratings...”

94,

95

■ ELECTRICAL CHARACTERISTICS

1. Absolute maximum ratings

102

Permitted operating frequency MB91F469QA,

MB91F469QAH

Added these parameters, depending on device, TA and

regulator setting

■ ELECTRICAL CHARACTERISTICS

102 1. Absolute maximum ratings

Permitted power consumption *7

Added these parameters, depending on device and TA ,

added the attached footnotes on next page.

156

DS705-00008-1v0-E

�MB91460Q Series

Preceding edition DS07-16614-1E

Current edition DS705-00008-1v0-E

Page

Section

(2009-06-24)

(2010-09-03)

Changes

■ ELECTRICAL CHARACTERISTICS

104 2. Recommended operating conditions

Operating temperature

Changed maximum from +105 °C → TA(max) and added

remark

■ ELECTRICAL CHARACTERISTICS

104 2. Recommended operating conditions

Lock-up time PLL (4 MHz ->16 ...100MHz)

Corrected “Look-up time PLL” → “Lock-up time PLL”

105,

108,

112,

114,

■ ELECTRICAL CHARACTERISTICS

3. DC characteristics,

4. A/D converter characteristics,

5. Alarm comparator characteristics,

7. AC characteristics

Changed the condition on top of the tables from

TA = −40 °C to +105 °C → TA = −40 °C to TA(max)

Changed the symbol of ambient temperature

from "Ta" → "TA"

■ ELECTRICAL CHARACTERISTICS

3. DC characteristics

106, Input leakage current,

107 Analog input leakage current

Changed the condition from

TA = 105 °C → TA = TA(max)

■ ELECTRICAL CHARACTERISTICS

3. DC characteristics

107

Power supply current MB91 F469QA, MB91

F469QAH

Added MB91F469QAH,

added the IccH parameters for TA = 125 °C

■ ELECTRICAL CHARACTERISTICS

108 4. A/D converter characteristics

Compare time

Changed Tcomp max from 16,500 µs → "t.b.d."

because this parameter is under re-evaluation.

■ ELECTRICAL CHARACTERISTICS

115 7. AC characteristics

7.2. Reset input ratings

INITX input time (at power-on): Changed tINTL minimum

from 8 ms → 10 ms (same as the main oscillator stabilization time).

152 ■ ORDERING INFORMATION

Added product number MB91F469QAHPB-GSE1,

added table column defining the maximum ambient

temperature TA(max)

153 ■ PACKAGE DIMENSION

Corrected the text under the drawings

→ Please check the latest package dimension at the

following URL:

http://edevice.fujitsu.com/package/en-search/

■ REVISION HISTORY

154 1. Changes in Preceding Editions

156 2. Changes in This Edition

Changed the REVISION HISTORY arrangement

DS705-00008-1v0-E

157

�MB91460Q Series

■ MEMO AND DISCLAIMER

MEMO

158

DS705-00008-1v0-E

�MB91460Q Series

MEMO

DS705-00008-1v0-E

159

�MB91460Q Series

FUJITSU SEMICONDUCTOR LIMITED

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome,

Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858

http://jp.fujitsu.com/fsl/en/

For further information please contact:

North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC.

1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

Asia Pacific

FUJITSU SEMICONDUCTOR ASIA PTE. LTD.

151 Lorong Chuan,

#05-08 New Tech Park 556741 Singapore

Tel : +65-6281-0770 Fax : +65-6281-0220

http://www.fmal.fujitsu.com/

Europe

FUJITSU SEMICONDUCTOR EUROPE GmbH

Pittlerstrasse 47, 63225 Langen, Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122

http://emea.fujitsu.com/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD.

Rm. 3102, Bund Center, No.222 Yan An Road (E),

Shanghai 200002, China

Tel : +86-21-6146-3688 Fax : +86-21-6335-1605

http://cn.fujitsu.com/fmc/

Korea

FUJITSU SEMICONDUCTOR KOREA LTD.

206 Kosmo Tower Building, 1002 Daechi-Dong,

Gangnam-Gu, Seoul 135-280, Republic of Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

http://kr.fujitsu.com/fmk/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD.

10/F., World Commerce Centre, 11 Canton Road,

Tsimshatsui, Kowloon, Hong Kong

Tel : +852-2377-0226 Fax : +852-2376-3269

http://cn.fujitsu.com/fmc/en/

Specifications are subject to change without notice. For further information please contact each office.

All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose

of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does

not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating

the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use

or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any

third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right

by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or

other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without

limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured

as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect

to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in

nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in

weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures

by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations

of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Fujitsu Semiconductor Europe GmbH

160

DS705-00008-1v0-E

�MB91460Q Series

DS705-00008-1v0-E

161

�