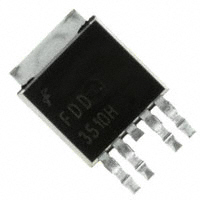

FDD3510H Dual N & P-Channel PowerTrench® MOSFET

April 2008

FDD3510H

Dual N & P-Channel PowerTrench® MOSFET

Features

Q1: N-Channel Max rDS(on) = 80mΩ at VGS = 10V, ID = 4.3A Max rDS(on) = 88mΩ at VGS = 6V, ID = 4.1A Q2: P-Channel Max rDS(on) = 190mΩ at VGS = -10V, ID = -2.8A Max rDS(on) = 224mΩ at VGS = -4.5V, ID = -2.6A 100% UIL Tested RoHS Compliant

N-Channel: 80V, 13.9A, 80mΩ P-Channel: -80V, -9.4A, 190mΩ General Description

These dual N and P-Channel enhancement mode Power MOSFETs are produced using Fairchild Semiconductor’s advanced PowerTrench® process that has been especially tailored to minimize on-state resistance and yet maintain superior switching performance.

Applications

Inverter H-Bridge

D1 D1/D2

D2

G1 G2 S2 G1 S1 Dual DPAK 4L S1 N-Channel

G2

S2 P-Channel

MOSFET Maximum Ratings TC = 25°C unless otherwise noted

Symbol VDS VGS ID Parameter Drain to Source Voltage Gate to Source Voltage Drain Current - Continuous - Continuous - Pulsed Power Dissipation for Single Operation PD EAS TJ, TSTG Single Pulse Avalanche Energy Operating and Storage Junction Temperature Range TC = 25°C (Note 1) TA = 25°C (Note 1a) TA = 25°C (Note 1b) (Note 3) 37 TC = 25°C TA = 25°C Q1 80 ±20 13.9 4.3 20 35 3.1 1.3 54 mJ °C -55 to +150 Q2 -80 ±20 -9.4 -2.8 -10 32 W A Units V V

Thermal Characteristics

RθJC RθJC Thermal Resistance, Junction to Case, Single Operation for Q1 Thermal Resistance, Junction to Case, Single Operation for Q2 (Note 1) (Note 1) 3.5 3.9 °C/W

Package Marking and Ordering Information

Device Marking FDD3510H Device FDD3510H Package TO-252-4L Reel Size 13” Tape Width 12mm Quantity 2500 units

©2008 Fairchild Semiconductor Corporation FDD3510H Rev.C

1

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Electrical Characteristics TJ = 25°C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Off Characteristics

BVDSS ∆BVDSS ∆TJ IDSS IGSS Drain to Source Breakdown Voltage Breakdown Voltage Temperature Coefficient Zero Gate Voltage Drain Current Gate to Source Leakage Current ID =250µA, VGS = 0V ID = -250µA, VGS = 0V ID = 250µA, referenced to 25°C ID = -250µA, referenced to 25°C VDS = 64V, VGS = 0V VDS = -64V, VGS = 0V VGS = ±20V, VDS = 0V Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 80 -80 84 -67 1 -1 ±100 ±100 V mV/°C µA nA nA

On Characteristics

VGS(th) ∆VGS(th) ∆TJ Gate to Source Threshold Voltage Gate to Source Threshold Voltage Temperature Coefficient VGS = VDS, ID = 250µA VGS = VDS, ID = -250µA ID = 250µA, referenced to 25°C ID = -250µA, referenced to 25°C VGS = 10V, ID = 4.3A VGS = 6.0V, ID = 4.1A VGS = 10V, ID = 4.3A, TJ = 125°C VGS = -10V, ID = -2.8A VGS = -4.5V, ID = -2.6A VGS = -10V, ID = -2.8A, TJ = 125°C VDD = 10V, ID = 4.3A VDD = -5V, ID = -2.8A Q1 Q2 Q1 Q2 Q1 2.0 -1.0 2.6 -1.6 -6.7 4.6 64 70 121 153 184 259 15 6.8 80 88 152 190 224 322 4.0 -3.0 V mV/°C

rDS(on)

Static Drain to Source On Resistance

mΩ

Q2 Q1 Q2

gFS

Forward Transconductance

S

Dynamic Characteristics

Ciss Coss Crss Rg Input Capacitance Output Capacitance Reverse Transfer Capacitance Gate Resistance Q1 VDS = 40V, VGS = 0V, f = 1MHZ Q2 VDS = -40V, VGS = 0V, f = 1MHZ Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 600 660 56 50 27 25 1.7 7.2 800 880 75 70 41 40 pF pF pF Ω

f = 1MHz

Switching Characteristics

td(on) tr td(off) tf Qg(TOT) Qgs Qgd Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Total Gate Charge Gate to Source Charge Gate to Drain “Miller” Charge Q2 VGS = -10V, VDD = -40V, ID = -2.8A Q1 VDD = 40V, ID = 4.3A, VGS = 10V, RGEN = 6Ω Q2 VDD = -40V, ID = -2.8A, VGS = -10V, RGEN = 6Ω Q1 VGS = 10V, VDD = 40V, ID = 4.3A Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 Q1 Q2 7 6 2 3 16 25 2 5 13 14 2.3 1.9 3.2 2.9 13 11 10 10 29 40 10 10 18 20 ns ns ns ns nC nC nC

FDD3510H Rev.C

2

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Electrical Characteristics TJ = 25°C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics

VSD trr Qrr

Notes: 1. RθJA is determined with the device mounted on a 1in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. RθJC is guaranteed by design while RθCA is determined by the user's board design.

Source to Drain Diode Forward Voltage Reverse Recovery Time Reverse Recovery Charge

VGS = 0V, IS = 2.6A VGS = 0V, IS = -2.6A Q1 IF = 4.3A, di/dt = 100A/s Q2 IF = -2.8A, di/dt = 100A/s

(Note 2) (Note 2)

Q1 Q2 Q1 Q2 Q1 Q2

0.8 -0.8 29 30 28 30

1.2 -1.2 46 48 45 48

V ns nC

Q1

a. 40°C/W when mounted on a 1 in2 pad of 2 oz copper

b. 96°C/W when mounted on a minimum pad of 2 oz copper

Scale 1 : 1 on letter size paper

Q2

a. 40°C/W when mounted on a 1 in2 pad of 2 oz copper

b. 96°C/W when mounted on a minimum pad of 2 oz copper

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty cycle < 2.0%. 3. Starting TJ = 25°C, N-ch: L = 3mH, IAS = 5A, VDD = 80V, VGS = 10V; P-ch: L = 3mH, IAS = -6A, VDD = -80V, VGS = -10V.

FDD3510H Rev.C

3

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

20

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE VGS = 10V ID, DRAIN CURRENT (A) VGS = 6V VGS = 4.5V

4.0 3.5 3.0

VGS = 4V VGS = 3.5V PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX

15

PULSE DURATION = Xµs DUTY CYCLE = X%MAX

2.5

VGS = 4.5V

10

VGS = 4V

2.0 1.5 1.0 0.5 0 5 10 15 20

ID, DRAIN CURRENT(A)

VGS = 6V

5

VGS = 3.5V

VGS = 10V

0 0 1 2 3 4

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 1. On Region Characteristics

Figure 2. Normalized On-Resistance vs Drain Current and Gate Voltage

300

SOURCE ON-RESISTANCE (mΩ)

2.2

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 -75

ID = 4.3A VGS = 10V

ID = 4.3A

PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX

rDS(on), DRAIN TO

200

TJ = 125oC

100

TJ = 25oC

-50

-25 0 25 50 75 100 125 150 TJ, JUNCTION TEMPERATURE (oC)

0 2 4 6 8 10

VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. Normalized On Resistance vs Junction Temperature

20

PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX IS, REVERSE DRAIN CURRENT (A)

Figure 4. On-Resistance vs Gate to Source Voltage

20 10

VGS = 0V

ID, DRAIN CURRENT (A)

15

VDS = 5V

1

TJ = 150oC

TJ = 25oC

10

TJ = 150oC TJ = 25oC

0.1

5

TJ = -55oC

0.01

TJ = -55oC

0 2 3 4 5 6

VGS, GATE TO SOURCE VOLTAGE (V)

0.001 0.0

0.2

0.4

0.6

0.8

1.0

1.2

VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics

Figure 6. Source to Drain Diode Forward Voltage vs Source Current

FDD3510H Rev.C

4

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

10

VGS, GATE TO SOURCE VOLTAGE(V) ID = 4.3A

1000

Ciss

CAPACITANCE (pF) VDD = 40V

8 6

VDD = 30V VDD = 50V

100

Coss

4 2 0 0 2 4 6 8 10 12 14

Qg, GATE CHARGE(nC)

f = 1MHz VGS = 0V

Crss

10 0.1

1

10

100

VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics

Figure 8. Capacitance vs Drain to Source Voltage

15

ID, DRAIN CURRENT (A)

5

IAS, AVALANCHE CURRENT(A)

4 12

VGS = 10V

3

TJ = 25oC

9

VGS = 6V

2

TJ = 125oC

6 3

RθJC = 3.5 C/W

o

1 0.01

0.1

1

10

0 25

50

75

100

o

125

150

tAV, TIME IN AVALANCHE(ms)

TC, CASE TEMPERATURE ( C)

Figure 9. Unclamped Inductive Switching Capability

50

P(PK), PEAK TRANSIENT POWER (W)

Figure 10. Maximum Continuous Drain Current vs Case Temperature

10

5

VGS = 10V

ID, DRAIN CURRENT (A)

10

100us

THIS AREA IS LIMITED BY rDS(on)

10

4

1

10

3

SINGLE PULSE RθJC = 3.5oC/W TC = 25oC

SINGLE PULSE TJ = MAX RATED RθJC = 3.5oC/W

1ms 10ms 100ms DC

10

2

0.1 0.05 0.5 1

TC = 25oC

10

VDS, DRAIN to SOURCE VOLTAGE (V)

100

10 -6 10

10

-5

10

-4

10

-3

10

-2

10

-1

1

t, PULSE WIDTH (sec)

Figure 11. Forward Bias Safe Operating Area

Figure 12. Single Pulse Maximum Power Dissipation

FDD3510H Rev.C

5

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

2

1

DUTY CYCLE-DESCENDING ORDER NORMALIZED THERMAL IMPEDANCE, ZθJC

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

t1 t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZθJC x RθJc + TC

0.01

SINGLE PULSE RθJC = 3.5 C/W

o

0.001 -6 10

10

-5

10

-4

10

-3

10

-2

10

-1

1

t, RECTANGULAR PULSE DURATION (sec)

Figure 13. Transient Thermal Response Curve

2

1

NORMALIZED THERMAL IMPEDANCE, ZθJA

DUTY CYCLE-DESCENDING ORDER

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

0.01

t1

SINGLE PULSE RθJA = 96 C/W

(Note 1b)

o

t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZθJA x RθJA + TA

-1

0.001 -4 10

10

-3

10

-2

10

1

10

100

1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 14. Transient Thermal Response Curve

FDD3510H Rev.C

6

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q2 P-Channel) TJ = 25°C unless otherwise noted

10

VGS = -10V -ID, DRAIN CURRENT (A) VGS = -4.5V VGS = -3.5V PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

2.5

VGS = -2.5V VGS = -3V

8 6 4

2.0

VGS = -3.5V

1.5

VGS = -4.5V

VGS = -3V

2

VGS = -2.5V

1.0

PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX VGS = -10V

0 0 1 2 3 4 5

-VDS, DRAIN TO SOURCE VOLTAGE (V)

0.5 0 2 4 6 -ID, DRAIN CURRENT(A) 8 10

Figure 15. On- Region Characteristics

Figure 16. Normalized on-Resistance vs Drain Current and Gate Voltage

600

SOURCE ON-RESISTANCE (mΩ)

2.0

NORMALIZED DRAIN TO SOURCE ON-RESISTANCE

1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 -75

ID = -2.8A VGS = -10V

ID = -2.8A

PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX

500 400 300 200

TJ = 25oC TJ = 125oC

rDS(on), DRAIN TO

-50

-25

0

25

50

75

100 125 150

100 2 4 6 8 10

-VGS, GATE TO SOURCE VOLTAGE (V)

TJ, JUNCTION TEMPERATURE (oC)

Figure 17. Normalized On-Resistance vs Junction Temperature

Figure 18. On-Resistance vs Gate to Source Voltage

10

PULSE DURATION = 80µs DUTY CYCLE = 0.5%MAX -ID, DRAIN CURRENT (A) -IS, REVERSE DRAIN CURRENT (A)

10

VGS = 0V

8

VDS = -5V

1

TJ = 150oC

6 4

TJ = 150oC

0.1

TJ = 25oC

2 0 1

0.01

TJ = -55oC

TJ = 25oC TJ = -55oC

2

3

4

5

0.001 0.0

0.2

0.4

0.6

0.8

1.0

1.2

-VGS, GATE TO SOURCE VOLTAGE (V)

-VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 19. Transfer Characteristics

Figure 20. Source to Drain Diode Forward Voltage vs Source Current

FDD3510H Rev.C

7

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q2 P-Channel)TJ = 25°C unless otherwise noted

10

-VGS, GATE TO SOURCE VOLTAGE(V) ID = -2.8A

1000

Ciss

CAPACITANCE (pF) VDD = -40V

8 6

VDD = -30V VDD = -50V

100

Coss

4 2 0 0 2 4 6 8 10 12 14 16

Qg, GATE CHARGE(nC)

f = 1MHz VGS = 0V

Crss

10 0.1

1

10

100

-VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 21. Gate Charge Characteristics

Figure 22. Capacitance vs Drain to Source Voltage

10

-ID, DRAIN CURRENT (A)

4

-IAS, AVALANCHE CURRENT(A)

3

TJ = 25oC

8

VGS = -10V

6

VGS = -4.5V

2

4 2

RθJC = 3.9 C/W

o

TJ = 125oC

1 0.1

1

tAV, TIME IN AVALANCHE(ms)

10

0 25

50

75

100

o

125

150

TC, CASE TEMPERATURE ( C)

Figure 23. Unclamped Inductive Switching Capability

20 10

-ID, DRAIN CURRENT (A)

Figure 24. Maximum Continuous Drain Current vs Case Temperature

20000

P(PK), PEAK TRANSIENT POWER (W)

10000

VGS = -10V

FOR TEMPERATURES ABOVE 25oC DERATE PEAK CURRENT AS FOLLOWS:

100us 1ms 10ms

SINGLE PULSE TJ = MAX RATED

1000

X – Tx o R 3.9 C/W I = I25θJC = ------------------125

SINGLE PULSE

1 THIS AREA IS

LIMITED BY rds(on)

TX = 25oC

100ms DC

100

0.1 0.05 1

RθJC = 3.9 C/W TC = 25oC

o

10

100

200

10 -6 10

10

-5

10

-4

10

-3

10

-2

10

-1

1

-VDS, DRAIN to SOURCE VOLTAGE (V)

t, PULSE WIDTH (s)

Figure 25. Forward Bias Safe Operating Area

Figure 26. Single Pulse Maximum Power Dissipation

FDD3510H Rev.C

8

www.fairchildsemi.com

�FDD3510H Dual N & P-Channel PowerTrench® MOSFET

Typical Characteristics (Q2 P-Channel)TJ = 25°C unless otherwise noted

2

1

NORMALIZED THERMAL IMPEDANCE, ZθJC

DUTY CYCLE-DESCENDING ORDER

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

t1 t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZθJC x RθJC + TC

0.01

SINGLE PULSE RθJC = 3.9 C/W

o

0.001 -6 10

10

-5

10

-4

10

-3

10

-2

10

-1

1

t, RECTANGULAR PULSE DURATION (s)

Figure 27. Transient Thermal Response Curve

2

1

NORMALIZED THERMAL IMPEDANCE, ZθJA

DUTY CYCLE-DESCENDING ORDER

0.1

D = 0.5 0.2 0.1 0.05 0.02 0.01

PDM

0.01

t1

SINGLE PULSE RθJA = 96 C/W

(Note 1b)

o

t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZθJA x RθJA + TA

-1

0.001 -4 10

10

-3

10

-2

10

1

10

100

1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 28. Transient Thermal Response Curve

FDD3510H Rev.C

9

www.fairchildsemi.com

�Preliminary Datasheet

FDD3510H Dual N & P-Channel PowerTrench® MOSFET

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidianries, and is not intended to be an exhaustive list of all such trademarks. ACEx® Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT™ CTL™ Current Transfer Logic™ EcoSPARK® EfficentMax™ EZSWITCH™ *

™

®

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT® FAST® FastvCore™ FlashWriter® *

FPS™ F-PFS™ FRFET® Global Power ResourceSM Green FPS™ Green FPS™ e-Series™ GTO™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MillerDrive™ MotionMax™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

®

tm

PDP-SPM™ Power-SPM™ PowerTrench® Programmable Active Droop™ QFET® QS™ Quiet Series™ RapidConfigure™ Saving our world 1mW at a time™ SmartMax™ SMART START™ SPM® STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SuperMOS™ ®

The Power Franchise®

tm

TinyBoost™ TinyBuck™ TinyLogic® TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ µSerDes™

UHC® Ultra FRFET™ UniFET™ VCX™ VisualMax™

* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Advance Information Product Status Formative or In Design Definition This datasheet contains the design specifications for product development. Specifications may change in any manner without notice. This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design. This datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.

Rev. I34

Preliminary

First Production

No Identification Needed Obsolete

Full Production Not In Production

FDD3510H Rev.C

10

www.fairchildsemi.com

�