FDZ1040L

Integrated Load Switch

Features

Description

Optimized for Low-Voltage Core ICs in Portable

Systems

Very Small Package Dimension: WLCSP

0.8 X 0.8 X 0.5 mm3

Current = 1.2 A, VIN max = 4 V

This device is particularly suited for compact power

management in portable applications needing 1 V to 4 V

input and 1.2 A output current capability. This load

switch integrated a level-shifting function that drives a Pchannel power MOSFET in a very small 0.8 X 0.8 X

0.5 mm3 WLCSP package.

Current = 2 A, VIN max = 4 V (Pulsed)

Applications

RDS(on) = 80 mΩ at VON = VIN = 4 V

RDS(on) = 85 mΩ at VON = VIN = 3.6 V

RDS(on) = 90 mΩ at VON = VIN = 3 V

Load Switch

Power Management in Portable Applications

RDS(on) = 110 mΩ at VON = 0.7 V, VIN = 1.6 V

RDS(on) = 309 mΩ at VON = 0.7 V, VIN = 1 V

RoHS Compliant

GND

VOUT

ON

Pin 1

VIN

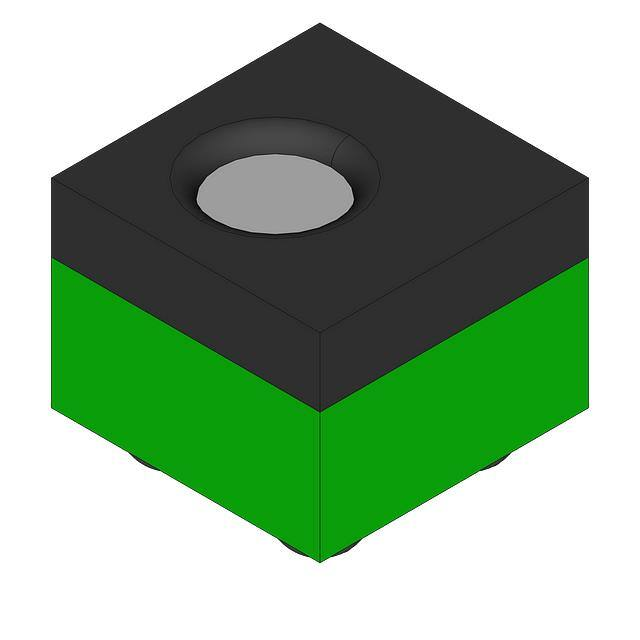

Figure 1.

Bottom View

Figure 2.

Top View

Ordering Information

Part

Number

Device

Mark

Ball

Pitch

Operating

Temperature Range

Switch

Package

Packing

Method

FDZ1040L

ZL

0.4 mm

-40 to 85°C

80 m, P-Channel

MOSFET

0.8 x 0.8 x

0.5 mm3 WLCSP

Tape & Reel

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

FDZ1040L — Integrated Load Switch

April 2013

�FDZ1040L — Integrated Load Switch

Typical Application

VIN

OFF ON

VOUT

ON

GND

Figure 3.

Typical Application

Block Diagram

Figure 4.

Internal Block Diagram

Top View (Bumps Down)

Figure 6.

Pin Configuration

Figure 5.

Bottom View (Bumps Up)

Pin Descriptions

Pin #

Name

A1

VIN

A2

VOUT

B1

ON

B2

GND

Description

Supply Input: Input to the load switch

Switch Output: Output of the load switch

ON/OFF Control Input, Active High

Ground

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

2

�Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol

VIN

Parameter

Voltage on VIN, VOUT, ON to GND

IOUT_C

IOUT-Load Current (Continuous)

IOUT_P

IOUT-Load Current (Pulsed)

Max.

Unit

-0.3

4.2

V

1.2

A

2

A

0.9

W

-40

85

°C

-65

150

°C

135

°C/W

(1a)

(1a)

PD

Power Dissipation at TA = 25°C

TA

Operating Temperature Range

TSTG

Min.

Storage Temperature

RΘJA

Thermal Resistance, Junction to Ambient

ESD

Electrostatic Discharge Capability

(1a)

Human Body Model, JESD22-A114

8

Charged Device Model, JESD22-C101

2

kV

Notes:

1. RΘJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal

reference is defined as the solder mounting surface of the drain pins. RΘJC is guaranteed by design, while RΘJA

is determined by the board design.

a.

2.

117°C/W when mounted on a

1-inch square pad of 2-oz copper.

b.

277°C/W when mounted on a

minimum pad of 2-oz copper.

Pulse test: pulse width < 300 µs; duty cycle < 2.0%.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol

Parameter

Min.

Max.

Unit

VIN

Voltage on VIN Pin

1

4

V

VON

Voltage on ON Pin

0.7

4.0

V

Operating Temperature Range

-40

85

°C

TA

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

3

FDZ1040L — Integrated Load Switch

Absolute Maximum Ratings

�TJ = 25°C unless otherwise noted.

Symbol

Parameter

VIN

Operation Voltage

VIL

ON Input Logic Low Voltage

VIH

ON Input Logic High Voltage

Test Conditions

Min. Typ.

Max.

Unit

4

V

1

1.6 V ≤ VIN ≤ 4 V

0.35

1 V ≤ VIN ≤ 1.6 V

0.25

1.6 V ≤ VIN ≤ 4 V

1.0

1 V ≤ VIN ≤ 1.6 V

0.7

V

V

IQ

Quiescent Current

VIN = VON = 1.8 V, VOUT = Float

1

μA

IQ(off)

Off Supply Current

VIN = 1.8 V, VON = GND, VOUT = Float

1

μA

ISD(off)

Off Switch Leakage Current

VIN = 1.8 V, VON = GND, VOUT = 0 V

100

nA

RPD

Output Discharge Pull-Down

Resistance

ION

ON Input Leakage

RDS(ON)

Static Drain-Source

On-Resistance

Ω

200

VON = VIN or GND

1

VON = VIN = 4 V, IOUT = 300 mA

48

80

VON = VIN = 3.6 V, IOUT = 300 mA

49

85

VON = VIN = 3 V, IOUT = 300 mA

51

90

VON = 0.7 V, VIN = 1.6 V, IOUT = 300 mA

70

110

VON = 0.7 V, VIN = 1 V, IOUT = 300 mA

142

309

VIN = 3.6 V, IOUT = 300 mA, TJ = 85°C

59

120

μA

mΩ

Switching Characteristics

Symbol

td(on)

tr

td(off)

tf

td(on)

tr

td(off)

tf

td(on)

tr

td(off)

tf

td(on)

tr

td(off)

tf

td(on)

tr

td(off)

tf

Parameter

Typical

Unit

Turn-On Delay

22

μs

Turn-On Rise Time

23

μs

127

μs

Turn-Off Fall Time

298

μs

Turn-On Delay

37

μs

35

μs

Turn-Off Delay

Turn-On Rise Time

Test Conditions

VIN = 1.6 V, VON = 0.7 V, CL = 1 μF, RL = 500 Ω

VIN = 1 V, VON = 1.8 V, CL = 1 μF, RL = 500 Ω

161

μs

Turn-Off Fall Time

544

μs

Turn-On Delay

20

μs

Turn-Off Delay

22

μs

136

μs

Turn-Off Fall Time

272

μs

Turn-On Delay

15

μs

Turn-On Rise Time

20

μs

168

μs

Turn-Off Fall Time

229

μs

Turn-On Delay

13

μs

19

μs

202

μs

214

μs

Turn-On Rise Time

Turn-Off Delay

Turn-Off Delay

Turn-On Rise Time

Turn-Off Delay

VIN = 1.8 V, VON = 1.8 V, CL = 1 μF, RL = 500 Ω

VIN = 2.5 V, VON = 1.8 V, CL = 1 μF, RL = 500 Ω

VIN = 3.3 V, VON = 1.8 V, CL = 1 μF, RL = 500 Ω

Turn-Off Fall Time

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

4

FDZ1040L — Integrated Load Switch

Electrical Characteristics

�FDZ1040L — Integrated Load Switch

Typical Performance Characteristics

Figure 7.

Shutdown Current vs. Temperature

Figure 8.

Shutdown Current vs. Supply Voltage

Figure 9.

Off Supply Current vs. Temperature

Figure 10.

Off Supply Current vs. Supply Voltage

Figure 11.

Quiescent Current vs. Temperature

Figure 12.

Quiescent Current vs. Supply Voltage

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

5

�FDZ1040L — Integrated Load Switch

Typical Performance Characteristics

Figure 13.

Figure 15.

RON vs. Temperature

Figure 14.

ON-Pin Threshold vs. VIN

Figure 16.

Figure 17. VOUT Turn-On and Turn-Off Delay

vs. Temperature at RL=500 Ω

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

RON vs. Supply Voltage

VOUT Rise and Fall Time vs. Temperature

at RL=500 Ω

Figure 18.

Forward Bias Safe Operation Area

www.fairchildsemi.com

6

�FDZ1040L — Integrated Load Switch

Typical Performance Characteristics

Figure 19.

Turn-On Response (VIN = 3.3 V, COUT=1 µF, RL=500 Ω)

Figure 20.

Turn-Off Response (VIN = 3.3 V, COUT=1 µF, RL=500 Ω)

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

7

�The FDZ1040L is a low-RDS(ON) P-channel load switch

packaged in space-saving 0.8x0.8 WLCSP.

of 1-4 V. The ON pin, an active HIGH TTL-compatible

input that supports input as low as 0.7 V, controls the

state of the switch.

The core of the device is a 80 mΩ P-channel MOSFET

capable of functioning over a wide input operating range

Applications Information

VIN

VIN = 1 -4 V

CIN

VOUT

ON

OFF ON

GND

Figure 21.

COUT

RL

Typical Application

Input Capacitor

Output Capacitor

To reduce device inrush current effect, a 0.1 µF ceramic

capacitor, CIN, is recommended close to the VIN pin. A

higher value of CIN can be used to further reduce the

voltage drop experienced as the switch is turned on into

a large capacitive load.

FDZ1040L works without an output capacitor. However,

if parasitic board inductance forces VOUT below GND

when switching off, a 0.1 µF capacitor, COUT, should be

placed between the VOUT and GND pins.

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

8

FDZ1040L — Integrated Load Switch

Functional Description

�FDZ1040L — Integrated Load Switch

Physical Dimensions

F

0.03 C

A

E

2X

0.40

B

Ø0.20

Cu Pad

A1

0.40

D

BALL A1

INDEX AREA

Ø0.30

Solder Mask

0.03 C

2X

TOP VIEW

RECOMMENDED LAND PATTERN

(NSMD PAD TYPE)

0.06 C

0.292±0.018

0.539

0.461

0.05 C

C

E

0.208±0.021

SEATING PLANE

SIDE VIEWS

D

NOTES:

A. NO JEDEC REGISTRATION APPLIES.

0.005

B. DIMENSIONS ARE IN MILLIMETERS.

C A B

Ø0.260±0.020

4X

0.40

B

A

0.40

C. DIMENSIONS AND TOLERANCE

PER ASME Y14.5M, 1994.

(Y)±0.018

D. DATUM C IS DEFINED BY THE SPHERICAL

CROWNS OF THE BALLS.

F

1 2

E. PACKAGE NOMINAL HEIGHT IS 500 MICRONS

±39 MICRONS (461-539 MICRONS).

(X)±0.018

F. FOR DIMENSIONS D, E, X, AND Y SEE

PRODUCT DATASHEET.

BOTTOM VIEW

G. DRAWING FILNAME: MKT-UC004AFrev1.

Figure 22.

4-Ball, WLCSP, 2 X 2 Array, 0.4 mm Pitch, 250 µm Ball

Product-Specific Dimensions

Product

D

E

X

Y

FDZ1040L

0.8 ±0.03 mm

0.8 ±0.03 mm

0.21 mm

0.21 mm

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the

warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

9

�FDZ1040L — Integrated Load Switch

© 2010 Fairchild Semiconductor Corporation

FDZ1040L • Rev. D1

www.fairchildsemi.com

10

�