FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

April 2009

FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without

Secondary Side Feedback Circuitry

Features

Linearly Decreasing PWM Frequency Green Mode Under Light-load and Zero-Load Conditions Constant Voltage (CV) and Constant Current (CC) around ±25% without Secondary Side Feedback Circuitry Precise Constant Voltage (CV) at ±5% by Secondary Side Feedback Circuitry Low Startup Current: 8μA Low Operating Current: 3.6mA Leading-Edge Blanking (LEB) Constant Power Limit Universal AC Input Range Synchronized Slope Compensation 140°C OTP Sensor with Hysteresis VDD Over-Voltage Clamping Cycle-by-Cycle Current Limiting Under-Voltage Lockout (UVLO) Fixed PWM Frequency with Hopping Gate Output Maximum Voltage Clamped at 17V

Description

This highly integrated PWM controller provides several features to enhance the performance of low-power flyback converters. To minimize standby power consumption, a proprietary green-mode function provides off-time modulation to linearly decrease the switching frequency under light-load and zero-load conditions. This green mode enables the power supply to meet international power conservation requirements. The supply voltage VDD is also used for feedback compensation, to regulate the output voltage without requiring a conventional TL431 and a photo-coupler. A typical output CV/CC characteristic is shown in Figure 1. Another advantage of the FSEZ2016 is that the typical startup current is only 8μA, while the typical operating current can be as low as 3.6mA. A large startup resistance can be used to achieve even higher power conversion efficiency. FSEZ2016 integrates frequency hopping function internally to reduce EMI emissions with minimum line filters. Also, built-in synchronized slope compensation maintains the stability of peak current-mode control. Proprietary internal compensation ensures constant output power limiting over a universal range of AC input voltages, from 90VAC to 264VAC. The FSEZ2016 provides many protection functions. Pulse-by-pulse current limiting ensures constant output current, even if a short circuit occurs. The internal protection circuit disables PWM output if VDD exceeds 22.7V. The gate output is clamped at 17V to protect the power MOS from over-voltage damage. The built-in over-temperature protection (OTP) function shuts down the controller at 140°C with a 30°C hysteresis.

Applications

General-purpose switching-mode power supplies and flyback power converters, such as: Battery Chargers for Cellular Phones, Cordless Phones, PDAs, Digital Cameras, Power Tools Power Adapters for Ink Jet Printers, Video Game Consoles, Portable Audio Players Open-Frame SMPS for TV/DVD Standby and Auxiliary Supplies, Home Appliances, Consumer Electronics Replacement for Linear Transformers and RCC SMPS PC 5V Standby Power

8 7 6 5 4 3 2

Vo

Maximum With Secondar y F eedback

Minimum Without Secondar y F eedback

Related Resources

AN-6081 — Low-Power Green-Mode EZSWITCH without Secondary Feedback

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

TM

1 0 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

Io

Figure 1.

Typical Output V-I Characteristic

www.fairchildsemi.com

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

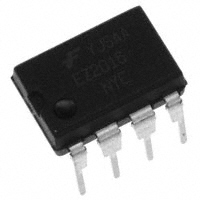

Ordering Information

Part Number

FSEZ2016NY

Operating Temperature Range

-40°C to +105°C

Eco Status

Green

Package

7-Lead, Dual Outline Package (DIP-7)

Packing Method

Tube

For Fairchild’s definition of Eco Status, please visit: http://www.fairchildsemi.com/company/green/rohs_green.html.

Application Diagram

Figure 2.

Typical Application

Internal Block Diagram

Figure 3.

Functional Block Diagram

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 2

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Marking Information

1’st line Z: Assembly plant code X: Year code Y: Week code TT: Die run code 3’rd line T: Package type (N=DIP) P: Y=Green package M: Manufacture flow code Figure 4. Top Mark

Pin Configuration

Figure 5.

Pin Assignments

Pin Definitions

Pin #

1 2 3 4 5 6 8

Name

SOURCE GND VDD FB NC NC DRAIN

Description

Power MOSFET source. This is the high-voltage power MOSFET source. Ground Power supply The FB pin provides feedback information to the internal PWM comparator. This feedback is used to control the duty cycle. When no feedback is provided, this pin is left open. No connection No connection Power MOSFET drain. This is the high-voltage power MOSFET drain.

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 3

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

Symbol

VDD VFB VSENSE PD θJA TJ TSTG TL ESD DC Supply Voltage

(1, 2)

Parameter

Input Voltage to FB Pin Input Voltage to Sense Pin Power Dissipation (TA=25°C) Thermal Resistance (Junction to Air) Operating Junction Temperature Storage Temperature Range Lead Temperature (Wave Soldering or IR, 10 Seconds) Electrostatic Discharge Capability Human Body Model (JEDEC:JESD22_A114) Charged Device Model (JEDEC:JESD22_C101)

Min.

-0.3 -0.3

Max.

30 7.0 7.0 1.2 98.7

Unit

V V V W °C/W °C °C °C KV KV

-40 -55

150 150 260 2 1

Notes: 1. All voltage values, except differential voltages, are given with respect to GND pin. 2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 4

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Electrical Characteristics

Unless otherwise noted, VDD=15V and TA=25°C.

Symbol VDD Section

VDD-OP VDD-ON VDD-OFF IDD-ST IDD-OP VDD-G-OFF

Parameter

Conditions

W ith Secondary Feedback Without Secondary Feedback

Min.

Typ.

Max. Units

20.0 22.7

Continuously Operation Voltage Turn-on Threshold Voltage Turn-off Threshold Voltage Startup Current Operating Supply Current VDD Low-threshold Voltage to Exit Green-off Mode Input-Voltage to Current-Sense Attenuation Input Impedance Open-Loop Voltage VDD Feedback Threshold Voltage

V V V μA mA V

16 7.5 VDD=VDD-ON – 0.1V CL=1nF

17 8.0 8 3.6 VDD-OFF +1.3

18 8.5 20 4.6

Feedback Input Section

AV ZFB VFB-OPEN VDD-FB 0.35 IFB=0.1mA to 0.2mA 4.5 FB is Open IFB=0.4mA 20.7 18.4 22.7 20.4 100 VDD=18V VSTHVA Current Limit Valley Threshold Voltage VDD=15V VDD=10V VDD=18V VSTHFL tLEB Current Limit Flat Threshold Voltage Leading-Edge Blanking Time VDD=15V VDD=10V 220 0.83 0.74 0.59 1.15 1.04 0.84 310 400 24.7 22.4 150 4.6 V/V kΩ V V V ns V V V V V V ns

Current-Sense Section

tPD Propagation Delay

Figure 6.

Saw Limit

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 5

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Electrical Characteristics (Continued)

Unless otherwise noted, VDD=15V and TA=25°C.

Symbol Oscillator Section

fOSC tHOP fOSC-G VFB-N VFB-G VFB-Z SG fDV fDT Frequency

Parameter

Center Frequency Hopping Range

Conditions

Min.

60 ±4.1 14.5 2.3

Typ.

65 ±4.7 4 17.0 2.6 VFB-N 0.75 1.4

Max.

70 ±5.3 19.5 2.9

Units

kHz ms KHz V V V

Hopping Period Green Mode Frequency Green Mode Entry FB Voltage Green Mode Ending FB Voltage Zero Duty Cycle FB Voltage Green Mode Modulation Slope Frequency Variation vs. VDD Deviation Frequency Variation vs. Temperature Deviation Maximum Duty Cycle Drain-Source Breakdown Voltage Breakdown Voltage Temperature Coefficient Maximum Continuous Drain-Source Diode Forward Current Maximum Pulsed Drain-Source Diode Forward Current Static Drain-Source On-Resistance ID=0.5A, VGS=10V VDS=600V, VGS=0V, TC=25°C VDS=480V, VGS=0V, TC=100°C VDS=300V, ID=1.1A, RG=25Ω ID=250μA, VGS=0V ID=250μA, Referenced to 25°C VDD=10 to 22V TA= -20 to 85°C 40

70

100 5

Hz/mV % %

1.5

5.0

Internal MOSFET Section

DCYMAX BVDSS ΔBVDSS/ΔTJ IS ISM RDS(ON) IDSS 69 600 0.6 1 4 9.3 11.5 5 10 7 21 13 27 VGS=0V, VDS=25V, fS=1MHz 130 19 140 110 24 52 36 64 170 25 74 79 % V V/°C A A Ω μA μA ns ns ns ns pF pF °C °C

Drain-Source Leakage Current

tD-ON tr tD-OFF tf CISS COSS TOTP

Turn-on Delay Time Rise Time Turn-off Delay Time Fall Time Input Capacitance Output Capacitance Protection Junction Temperature

Over Temperature Protection (OTP)

TOTP-RESTART Restart Junction Temperature

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 6

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Typical Performance Characteristics

17 8.4

16.8

8.2

16.6

V DD-OFF (V)

-40 -25 -10 5 20 35 50 65 80 95 110 125

V DD-ON (V)

8

16.4

7.8

16.2

7.6

16

7.4 -40 -25 -10 5 20 35 50 65 80 95 110 125

T emperature (℃ )

T emperature (℃ )

Figure 7.

Turn-on Threshold Voltage (VDD-ON) vs. Temperature

Figure 8.

Turn-off Threshold Voltage (VDD-OFF) vs. Temperature

14

3

12

2.8

10

IDD-OP (mA)

-40 -25 -10 5 20 35 50 65 80 95 110 125

IDD-ST (μ A)

2.6

8

2.4

6

2.2

4

2 -40 -25 -10 5 20 35 50 65 80 95 110 125

T emperature (℃ )

T emperature (℃ )

Figure 9.

Startup Current (IDD-ST) vs. Temperature

Figure 10. Operating Supply Current (IDD-OP) vs. Temperature

66 65

77 76

63 62 61 60 -40 -25 -10 5 20 35 50 65 80 95 110 125

DCY MAX (%)

fOSC (KHz)

64

75 74 73 72 71 -40 -25 -10 5 20 35 50 65 80 95 110 125

T emperature (℃ )

T emperature (℃ )

Figure 11. Center Frequency (fOSC) vs. Temperature

Figure 12. Maximum Duty Cycle (DCYMAX) vs. Temperature

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 7

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Typical Performance Characteristics (Continued)

3 2.2

2.8

2

V FB-G (V)

-40 -25 -10 5 20 35 50 65 80 95 110 125

V FB-N (V)

2.6

1.8

2.4

1.6

2.2

1.4

2

1.2 -40 -25 -10 5 20 35 50 65 80 95 110 125

T emperature (℃ )

T emperature (℃ )

Figure 13. Green-Mode Entry FB Voltage (VFB-N) vs. Temperature

380

Figure 14. Green-Mode Ending FB Voltage (VFB-G) vs. Temperature

800 750 700 650 600 550 500

360

tLEB (ns)

340

320

300

280 -40 -25 -10 5 20 35 50 65 80 95 110 125

BV DSS (V)

-40

-25

-10

5

20

35

50

65

80

95

110

125

T emperature (℃ )

T emperature (℃ )

Figure 15. Leading-Edge Blanking Time (tLEB) vs. Temperature

Figure 16. Drain-Source Breakdown Voltage (BVDSS) vs. Temperature

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 8

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Operation Description

FSEZ2016 devices integrate functions for low-power switch-mode power supplies. The following descriptions highlight the key features of the FSEZ2016.

Oscillator Operation

The oscillation frequency is fixed at 65KHz.

Startup Current

The required startup current is only 8μA. This allows a high-resistance, low-wattage startup resistor to supply the controller’s startup power. A 1.5MΩ/0.25W startup resistor can be used over a wide input range (100V240VAC) with very little power loss.

Leading-Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs at the sense-resistor. To avoid premature termination of the switching pulse, a 310ns leadingedge blanking time is built in. Conventional RC filtering is not necessary. During this blanking period, the current-limit comparator is disabled and cannot switch off the gate drive.

Operating Current

The operating current is normally 3.6mA, which results in higher efficiency and reduces the required VDD holdup capacitance. A 10μF/25V VDD hold-up capacitor can be used over a wide input range (90V-264VAC) with very little power loss.

Constant Output Power Limit

W hen the SENSE voltage across the sense resistor RS reaches the threshold voltage, the output GATE drive is turned off following a small propagation delay, tPD. This propagation delay introduces an additional current proportional to tPD•VIN/LP. The propagation delay is nearly constant, regardless of the input line voltage VIN. Higher input line voltages result in larger additional currents. Under high input-line voltages, the output power limit is higher than under low input-line voltages. Over a wide range of AC input voltages, the variation can be significant. To compensate for this, the threshold voltage is adjusted by adding a positive ramp (Vlimit_ramp). This ramp signal can vary from 0.74V to 1.04V and flattens out at 1.04V. A smaller threshold voltage forces the output GATE drive to terminate earlier, reducing total PWM turn-on time and making the output power equal to that of the low line input. This proprietary internal compensation feature ensures a constant output power limit over a wide range of AC input voltages (90V-264VAC).

Green-Mode Operation

The proprietary green-mode function provides off-time modulation to linearly decrease the switching frequency under light-load and zero-load conditions. The on-time is limited to provide better protection against brownouts and other abnormal conditions. Power supplies using the FSEZ2016 can meet international restrictions regarding standby power-consumption.

Constant Voltage (CV) and Constant Current (CC) without Feedback

The FSEZ2016 can tightly regulate the output voltage and provide over-current protection without requiring secondary-side feedback signals. For improved CV and CC accuracy, the transformer leakage inductance should be reduced as much as possible.

Under Voltage Lockout (UVLO)

The turn-on/turn-off thresholds are fixed internally at 17V and 8V. To enable the FSEZ2016 during startup, the hold-up capacitor must first be charged to 17V through the startup resistor. The hold-up capacitor continues to supply VDD before energy can be delivered from the auxiliary winding of the main transformer. VDD must not drop below 8V during this startup process. This UVLO hysteresis window ensures that the hold-up capacitor can adequately supply VDD during startup.

Over-Temperature Protection (OTP)

The FSEZ2016 has a built-in temperature-sensing circuit to shut down PWM output if the junction temperature exceeds 140°C. While PWM output is shut down, the VDD voltage gradually drops to the UVLO voltage. Some of the internal circuits are shut down, and VDD gradually starts increasing again. When VDD reaches 17V, all the internal circuits, including the temperature-sensing circuit, operate normally. If the junction temperature is still higher than 140°C, the PWM controller shuts down immediately. This situation continues until the temperature drops below 110°C. The PWM output is then turned back on. The temperature hysteresis window for the OTP circuit is 30°C.

Gate Output

The BiCMOS output stage is a fast totem-pole gate driver. Cross-conduction is avoided to minimize heat dissipation, increase efficiency, and enhance reliability. The output driver is clamped by an internal 17V Zener diode to protect the power MOSFET transistors against any harmful over-voltage gate signals.

VDD Over-Voltage Clamping

VDD over-voltage clamping is built in to prevent damage from over-voltage conditions. When VDD exceeds 22.7V, PWM output is shut down. Over-voltage conditions may be caused by an open photo-coupler loop or a short circuit in the output.

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 9

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Operation Description (Continued)

Slope Compensation

The sensed voltage across the current sense resistor is used for current mode control and pulse-by-pulse current limiting. The built-in slope compensation improves power supply stability. Furthermore, it prevents sub-harmonic oscillations that normally would occur because of peak current mode control. A positively sloped, synchronized ramp is activated with every switching cycle. The slope of the ramp is: 0.33 × Duty (1) Duty(max.)

Noise Immunity

Noise from the current sense or the control signal may cause significant pulse-width jitter, particularly in continuous-conduction mode. Slope compensation helps alleviate this problem. Good placement and layout practices should be followed. The designer should avoid long PCB traces and component leads. Compensation and filter components should be located near the FSEZ2016. Finally, increasing the power-MOS gate resistance is advised.

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 10

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Applications Information

Figure 17. Reference Circuit (without Secondary-Side Feedback)

BOM

Reference

C1 C2 C3 C4 C5 C6 C7 C9 C10 D1 D2 D3 D4 D5 D6 D7

Component

CC 4.7nF/1kV EC 4.7μF/400V 105°C EC 4.7μF/400V 105°C EC 10μF/50V 105°C CC 1nF/1kV EC 560μF/10V EC 560μF/10V Open CC 1nF Diode 1N4007 Diode 1N4007 Diode 1N4007 Diode 1N4007 Diode FR107 Diode FR102 Diode SB560 F1 L2 L3 L4

Reference

R 1Ω/1W

Component

Inductor 4.7μH Inductor 470μH Inductor 80μH R 750kΩ R 750kΩ R 100kΩ R 10Ω R 2.2Ω R 47Ω R 270Ω R 0Ω R 2kΩ Transformer EE-16 IC FSEZ2016

R1 R2 R3 R4 R5 R6 R7 R8 R9 T1 U1

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 11

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Applications Information (Continued)

Figure 18. Reference Circuit (with Secondary-Side Feedback)

BOM

Reference

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 D1 D2 D3 D4 D5 D6 D7 F1 L2

Component

CC 4.7nF/1kV EC 4.7μF/400V 105°C EC 4.7μF/400V 105°C EC 10μF/50V 105°C CC 1nF/1kV EC 560μF/10V EC 560μF/10V CC 2.2nF Open CC 1nF Diode 1N4007 Diode 1N4007 Diode 1N4007 Diode 1N4007 Diode FR107 Diode FR102 Diode SB560 R 1Ω/1W Inductor 4.7μH L3 L4

Reference

Inductor 80μH R 750kΩ R 750kΩ R 100kΩ R 10Ω R 2.2Ω R 47Ω R 270Ω R 0Ω R 2kΩ R 560Ω R 20kΩ R 20kΩ R 20kΩ

Component

Inductor 470μH

R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 T1 U1 U2 U3

Transformer EE-16 IC FSEZ2016 IC PC817 IC TL431

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 12

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

Physical Dimensions

7

PIN 1 INDICATOR

10.16 9.47

5

6.47 6.22

(0.675)

1

4

8.128 7.620 0.35 0.20

3.556 3.048

2.794 2.286

4.318 3.680

0.508 MIN 3.81 2.92 0.508 0.356

NOTES: A) THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION AA EXCEPT LEAD COUNT. B) ALL DIMENSIONS ARE IN MILLIMETERS. C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS. D) DIMENSION WITH TERMINALS CONSTRAINED PERPENDICULAR TO PRINTED CIRCUIT BOARD. E) DRAWING FILE NAME: MKT-N07CREV1

Figure 19. 7-Pin DIP-7 Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

D

1.78 1.14

(7.632) 9.271 7.870

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 13

�FSEZ2016 — Low-Power Green-Mode EZSWITCHTM without Secondary Side Feedback Circuitry

© 2008 Fairchild Semiconductor Corporation FSEZ2016 Rev. 1.0.0

www.fairchildsemi.com 14

�