SC1453

NOT RECOMMENDED FOR NEW DESIGN

150mA Ultra Low Dropout

Regulator with Low Noise Bypass

POWER MANAGEMENT

Description

Features

The SC1453 is a low dropout linear regulator that

operates from a +2.25V to +6.5V input range and

delivers up to 150mA. A PMOS pass transistor allows

the low 75µA supply current to remain independent of

load, making these devices ideal for battery operated

portable equipment such as cellular phones, cordless

phones and personal digital assistants.

“2982/5205” compatible pinout

Guaranteed 150 mA output current

2% output accuracy guaranteed over line, load and

temperature

Very small external components - designed to work

with ceramic capacitors

Low 26µVRMS output noise

(1.5V option, CIN = COUT = 1µF, CBYP = 10nF)

Very low supply current

Thermal overload protection

Reverse battery protection

Low power shutdown

Full industrial temperature range

Very low profile packaging available (1mm max. height)

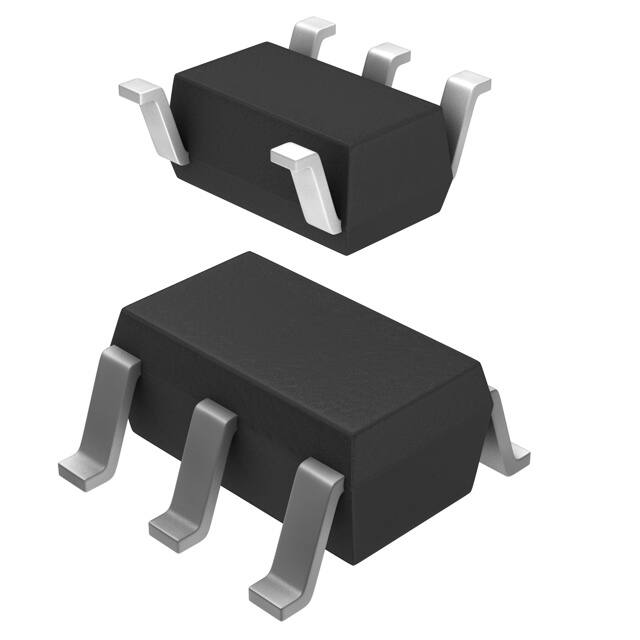

Surface mount packaging (5 pin SOT-23 and

TSOT-23)

Available in Lead-free packages, fully WEEE and RoHS

compliant

The SC1453 has a bandgap reference bypass pin for

very low noise operation - a 10nF (typ.) capacitor may be

connected between this pin and ground. Other features

include low powered shutdown, short circuit protection,

thermal shutdown protection and reverse battery

protection. The SC1453 comes in the tiny 5 lead SOT-23

package and the ultra-low profile 5 lead TSOT-23.

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

Applications

Battery Powered Systems

Cellular Telephones

Cordless Telephones

Personal Digital Assistants

Portable Instrumentation

Modems

PCMCIA cards

Typical Application Circuit

1

VIN

C1

1uF

3

U1

SC1453

IN

OUT

EN

GND BYP

2

Revision: April 21, 2008

5

VOUT

4

C3

1uF

C2

10nF

1

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified

in the Electrical Characteristics section is not implied.

Symbol

Maximum

Units

Input Supply Voltage

VIN

-0.6 to +7

V

Thermal Resistance Junction to Ambient

θJA

256

°C/W

Thermal Resistance Junction to Case

θJC

81

°C/W

Operating Ambient Temperature Range

TA

-40 to +85

°C

Operating Junction Temperature Range

TJ

-40 to +125

°C

Storage Temperature Range

TSTG

-65 to 150

°C

Lead Temperature (Soldering) 10 Sec.

TLEAD

300

°C

ESD Rating

ESD

2

kV

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

Parameter

Electrical Characteristics

Unless specified: VIN = VOUT + 1V, VEN = VIN, IOUT = 100µA, CIN = COUT = 1µF, TA = 25°C. Values in bold apply over full operating ambient temperature range.

Parameter

IN

Symbol

Supply Voltage Range

VIN

Supply Current

IQ

Conditions

Min

2.25

IOUT = 0mA to150mA

VIN = 6.5V, VEN = 0V

OUT

Output Voltage (1)

Line Regulation (1)(2)

VOUT

REG(LINE)

Typ

IOUT = 1mA

-1.5%

0mA ≤ IOUT ≤ 150mA, VOUT +1V ≤ VIN ≤ 5.5V

-2.0%

(VOUT(NOM) + 0.1V) ≤ VIN ≤ 5.5V, IOUT = 1mA

75

Max

Units

6.50

V

130

µA

160

0.1

1.0

µA

1.5

VOUT

+1.5%

V

+2.0%

2.5

10

mV

12

Load Regulation (1)

REG(LOAD)

IOUT = 0.1mA to 150mA

-3

-10

mV

-20

2008 Semtech Corp.

2

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Electrical Characteristics (Cont.)

Unless specified: VIN = VOUT + 1V, VEN = VIN, IOUT = 100µA, CIN = COUT = 1µF, TA = 25°C. Values in bold apply over full operating ambient temperature range.

Parameter

Symbol

Conditions

Min

Typ

Max

Units

OUT (Cont.)

Current Limit

ILIM

Dropout Voltage(1)(3)

VD

400

mA

IOUT = 1mA

1

IOUT = 50mA

50

mV

65

mV

75

IOUT = 100mA

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

100

Output Voltage Noise,

COUT = 100µF

Power Supply Rejection Ratio

BYP

Start-up Rise Time

EN

Enable Input Threshold

Enable Input Bias Current (4)

en

mV

155

IOUT = 150mA

Output Voltage Noise,

COUT = 1µF

125

150

190

mV

230

10Hz to 100kHz, IOUT = 1mA

CBYP = 10nF, VOUT = 1.5V

26

10Hz to 100kHz, IOUT = 1mA

CBYP = 10nF, VOUT = 3.3V

54

10Hz to 100kHz, IOUT = 1mA

CBYP = 10nF, VOUT = 1.5V

13

10Hz to 100kHz, IOUT = 1mA

CBYP = 10nF, VOUT = 3.3V

29

PSRR

f = 120Hz, CBYP = 10nF

61

dB

tr

CBYP = 10nF

1.3

ms

VIH

2.25V ≤ VIN ≤ 6.5V

VIL

2.25V ≤ VIN ≤ 6.5V

IEN

0V ≤ VEN ≤ VIN

en

µVRMS

µVRMS

1.6

V

0.4

-0.5

0

+0.5

µA

Over Temperature Protection

High Trip Level

Hysteresis

THI

150

°C

THYST

20

°C

Notes:

(1) Low duty cycle pulse testing with Kelvin connections required.

(2) VIN(MIN) = 2.25V.

(3) Defined as the input to output differential at which the output voltage drops 100mV below the value measured

at a differential of 1V. Not measurable on 1.5V and 1.8V parts due to minimum VIN constraints.

(4) Guaranteed by design.

2008 Semtech Corp.

3

www.semtech.com

�NOT RECOMMENDED FOR NEW DESIGN

SC1453

POWER MANAGEMENT

Pin Configuration

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

Top View

(SOT-23-5 & TSOT-23-5)

Pin Descriptions

Pin #

Pin Name

1

IN

2

GND

3

EN

4

BYP

5

OUT

2008 Semtech Corp.

Pin Function

Input pin.

Ground pin. Can be used for heatsinking if needed.

Active high enable pin. Connect to IN if not being used.

Reference bypass. Connect a 10nF capacitor (typical) between this pin and GND to reduce

output noise.

Regulator output, sourcing up to 150mA.

4

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Ordering Information

SOT-23-5

Voltage Option

(V)

Part Number

1.5

SC1453ITSK1.5TR

SC1453ISK-1.8TR

1.8

SC1453ITSK1.8TR

2.5

SC1453ISK-2.5TR

2.5

SC1453ITSK2.5TR

2.7

SC1453ISK-2.7TR

2.7

SC1453ITSK2.7TR

2.8

SC1453ISK-2.8TR

2.8

SC1453ITSK2.8TR

2.9

SC1453ISK-2.9TR

2.85

SC1453ITSK285TR

Voltage Option

(V)

Part Number

1.5

SC1453ISK-1.5TR

1.8

(1)

Lead-free

SOT-23-5 (1)(2)

P ackag e

TSOT-23-5

3.0

SC1453ISK-3.0TR

2.9

SC1453ITSK2.9TR

3.1

SC1453ISK-3.1TR

3.0

SC1453ITSK3.0TR

3.2

SC1453ISK-3.2TR

3.1

SC1453ITSK3.1TR

3.3

SC1453ISK-3.3TR

3.2

SC1453ITSK3.2TR

1.5

SC1453ISK1.5TRT

3.3

SC1453ITSK3.3TR

1.8

SC1453ISK18TRT

1.5

SC1453ITSK15TRT

2.5

SC1453ISK2.5TRT

1.8

SC1453ITSK18TRT

2.7

SC1453ISK2.7TRT

2.5

SC1453ITSK25TRT

2.8

SC1453ISK2.8TRT

2.7

SC1453ITSK27TRT

2.9

SC1453ISK2.9TRT

2.8

SC1453ITSK28TRT

3.0

SC1453ISK3.0TRT

2.85

SC1453TSK285TRT

3.1

SC1453ISK3.1TRT

2.9

SC1453ITSK29TRT

3.2

SC1453ISK3.2TRT

3.0

SC1453ITSK30TRT

3.3

SC1453ISK33TRT

3.1

SC1453ITSK31TRT

3.2

SC1453ITSK32TRT

3.3

SC1453ITSK33TRT

Specify

S C 1453E V B

Lead-free

TSOT-23-5 (1)(2)

Notes:

(1) Only available in tape and reel packaging. A reel

contains 3000 devices.

(2) Lead free packaging (ordered with suffix extension

“TRT”) is optional. Consult factory for availability. This

product is fully WEEE and RoHS compliant.

(3) Evaluation board for SC1453. Specify output voltage

option when ordering.

2008 Semtech Corp.

(1)

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

P ackag e

Evaluation

Board (3)

5

www.semtech.com

�NOT RECOMMENDED FOR NEW DESIGN

SC1453

POWER MANAGEMENT

Marking Information

Bottom Mark

x3XX

yyww

x = package (5 for SOT-23-5, T for TSOT-23-5)

3 = SC1453

XX = voltage option

(examples: 5331 for 3.1V option in SOT-23-5

yyww = Date code

(example: 0008 for week 8 of 2000)

Top Mark

Bottom Mark

BX00

yyww

For SC1453, 2.85V option:

X = L for SOT-23-5 and N for TSOT-23-5

yyww = Date code

(example: 0008 for week 8 of 2000)

Block Diagram

2008 Semtech Corp.

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

Top Mark

6

www.semtech.com

�NOT RECOMMENDED FOR NEW DESIGN

SC1453

POWER MANAGEMENT

Applications Information

Theory Of Operation

Component Selection - General

The SC1453 is intended for applications where very low

dropout voltage, low supply current and low output noise

are critical. It provides a very simple, low cost solution

that uses very little pcb real estate. Only three external

capacitors are required for operation (two if a low noise

output is not required).

Output capacitor - Semtech recommends a minimum

capacitance of 1µF at the output with an equivalent

series resistance (ESR) of < 1Ω over temperature. While

the SC1453 has been designed to be used with ceramic

capacitors, it does not have to be used with ceramic

capacitors, allowing the designer a choice. Increasing the

bulk capacitance will further reduce output noise and

improve the overall transient response.

The SC1453 contains a bandgap reference trimmed for

optimal temperature coefficient which is fed into the

inverting input of an error amplifier. The output voltage

of the regulator is divided down internally using a

resistor divider and compared to the bandgap voltage.

The error amplifier drives the gate of a low R DS(ON)

P-channel MOSFET pass device.

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

Input capacitor - Semtech recommends the use of a 1µF

ceramic capacitor at the input. This allows for the device

being some distance from any bulk capacitance on the

rail. Additionally, input droop due to load transients is

reduced, improving overall load transient response.

Bypass capacitor - Semtech recommends the use of a

10nF ceramic capacitor to bypass the bandgap

reference. Increasing this capacitor to 100nF will

further improve power supply rejection and overall

output noise. CBYP may be omitted if low noise operation

is not required.

An active high enable pin (EN) allows the regulator to be

shut down. Pulling this pin low causes the device to

enter a very low power shutdown mode, where it will draw

typically 0.1µA from the input supply.

A bypass pin (BYP) is provided to decouple the bandgap

reference to reduce output noise and also to improve

power supply rejection. This pin can be left open if low

noise operation is not required.

Thermal Considerations

The worst-case power dissipation for this part is given

by:

The regulator has its own current limit circuitry to

ensure that the output current will not damage the

device during output short, overload or start-up. The

current limit is guaranteed to be greater than 400mA to

allow fast charging of the output capacitor and high

initial currents for DSP initialization.

PD(MAX ) = (VIN(MAX) − VOUT(MIN) )• IOUT(MAX ) + VIN(MAX ) • IQ(MAX )

For all practical purposes, equation (1) can be reduced

to the following expression:

PD(MAX) = (VIN(MAX ) − VOUT(MIN) )• IOUT(MAX)

The SC1453 has a fast start-up circuit to speed up the

initial charging time of the bypass capacitor to enable

the output voltage to come up quicker (typically 1.3ms

with CBYP = 10nF).

(2)

Looking at a typical application, 3.3V to 2.8V at 150mA:

VIN(MAX) = 3.3 + 5% = 3.465V

VOUT(MIN) = 2.8V - 2% = 2.744V

IOUT = 150mA

TA = 85°C

The SC1453 includes thermal shutdown circuitry to turn

off the device if T J exceeds 150°C (typical), with the

device remaining off until TJ drops by 20°C (typical).

Reverse battery protection circuitry ensures that the

device cannot be damaged if the input supply is

accidentally reversed, limiting the reverse current to less

than 1.5mA.

2008 Semtech Corp.

(1)

7

www.semtech.com

�NOT RECOMMENDED FOR NEW DESIGN

SC1453

POWER MANAGEMENT

Applications Information (Cont.)

Inserting these values into equation (2) gives us:

Layout Considerations

PD(MAX ) = (3.465 − 2.744 ) • 0.150 = 108mW

While layout for linear devices is generally not as critical

as for a switching application, careful attention to detail

will ensure reliable operation.

Using this figure, we can calculate the maximum thermal

impedance allowable to maintain TJ ≤ 125°C:

θ JA (MAX ) =

(T

J(MAX )

− TA (MAX ) )

PD(MAX )

=

1) Attaching the part to a larger copper footprint will

enable better heat transfer from the device, especially

on PCBs where there are internal ground and power

planes.

(125 − 85) = 370°C / W

0.108

2) Place the input, output and bypass capacitors close

to the device for optimal transient response and device

behaviour.

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

With the standard SOT-23-5/TSOT-23-5 Land Pattern

shown at the end of this datasheet, and minimum trace

widths, the thermal impedance junction to ambient for

SC1453ISK is 256°C/W. Thus no additional heatsinking

is required for this example.

3) Connect all ground connections directly to the ground

plane. If there is no ground plane, connect to a common

local ground point before connecting to board ground.

The junction temperature can be reduced further (or

higher power dissipation can be allowed) by the use of

larger trace widths and connecting PCB copper to the

GND pin (pin 2), which connects directly to the device

substrate. Adding approximately one square inch of PCB

copper to pin 2 will reduce θ JA to approximately

130°C/W and T J(MAX) for the example above to

approximately 100°C for the SOT-23-5 package. The use

of multi layer boards with internal ground/power planes

will lower the junction temperature and improve overall

output voltage accuracy.

2008 Semtech Corp.

8

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Typical Characteristics

Quiescent Current vs. Junction Temperature

Off-State Quiescent Current

vs. Input Voltage

vs. Junction Temperature

200

120

IOUT = 150mA

VIN = 6.5V

VIN = 6.5V

VEN = 0V

175

100

150

IQ(OFF) (nA)

IQ (µA)

80

VIN = 3.8V

60

40

125

100

75

50

20

0

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

25

0

-50

-25

0

25

50

75

100

-50

125

-25

0

25

vs. Output Current

vs. Input Voltage Change

12

125

IOUT = 1mA

10

-0.10

IOUT = 50mA

-0.15

REGLINE (mV)

VOUT Deviation (%)

-0.05

100mA ≤ IOUT ≤ 150mA

-0.20

-0.25

8

VIN = VOUT + 1V to 6.5V

6

4

2

VIN = VOUT + 1V

-0.30

VIN = VOUT + 1V to 5.5V

0

-50

-25

0

25

50

75

100

125

-50

-25

0

TJ (°C)

25

50

75

100

125

TJ (°C)

Load Regulation vs.

Current Limit vs. Junction Temperature

Junction Temperature

vs. Input Voltage

0.90

VIN = VOUT + 1V

IOUT = 0.1mA to 150mA

0.85

8

0.80

7

0.75

6

0.70

ILIM (A)

REGLOAD (mV)

100

Line Regulation vs. Junction Temperature

IOUT = 1mA

9

75

Output Voltage vs. Junction Temperature

0.00

10

50

TJ (°C)

TJ (°C)

5

4

0.65

0.60

3

0.55

2

0.50

1

0.45

0

VIN = 6.5V

VIN = 3.8V

0.40

-50

-25

0

25

50

75

100

125

-50

TJ (°C)

2008 Semtech Corp.

-25

0

25

50

75

100

125

TJ (°C)

9

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Typical Characteristics (Cont.)

Dropout Voltage vs. Junction Temperature

Dropout Voltage vs. Output Current

vs. Output Current

vs. Junction Temperature

200

200

175

175

150

150

IOUT = 150mA

125

VD (mV)

VD (mV)

125

100

75

100

75

50

25

0

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

25

Top to bottom:

TJ = 125°C

TJ = 25°C

TJ = -40°C

50

IOUT = 50mA

0

-50

-25

0

25

50

75

100

125

0

25

50

75

TJ (°C)

100

125

Bypass Start-up Rise Time vs. Junction Temperature

Enable Input Threshold Voltage vs. Junction

vs. Input Voltage

Temperature vs. Input Voltage

1.8

1.7

1.6

CBYP = 10nF

1.6

VIN = 3.8V

1.4

VEN (V)

tr (ms)

1.5

1.3

1.2

1.4

VIH @ VIN = 6.5V

1.2

VIH @ VIN = 3.8V

1.0

VIL @ VIN = 6.5V

0.8

1.1

VIL @ VIN = 3.8V

VIN = 6.5V

1.0

0.6

0.9

0.8

0.4

-50

-25

0

25

50

75

100

125

-50

-25

0

25

TJ (°C)

5.0

4.5

50

75

Output Spectral Noise Density vs. Frequency

Junction Temperature

vs. Output Voltage, COUT = 1µF

VIN = VOUT + 1V

IOUT = 1mA

CIN = 1µF

CBYP = 10nF

TJ = 25°C

1

3.5

en (µV/√Hz)

3.0

2.5

2.0

1.5

0.1

0.01

1.0

0.5

0.0

-25

0

25

50

75

100

Top to bottom:

VOUT = 3.3V

VOUT = 3.0V

VOUT = 2.8V

VOUT = 2.5V

VOUT = 1.8V

VOUT = 1.5V

0.001

0.01

125

TJ (°C)

2008 Semtech Corp.

125

10

VIN = VEN = -6.5V

-50

100

TJ (°C)

Reverse Battery Protection vs.

4.0

I(REV BAT) (mA)

150

IOUT (mA)

0.1

1

10

100

1000

f (kHz)

10

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Typical Characteristics (Cont.)

Output Spectral Noise Density vs. Frequency

Output Spectral Noise Density vs. Frequency

vs. Output Voltage, COUT = 100µF

vs. Output Capacitance

10

10

VIN = VOUT + 1V

IOUT = 1mA

CIN = 1µF

CBYP = 10nF

TJ = 25°C

0.01

Top to bottom:

VOUT = 3.3V

VOUT = 3.0V

VOUT = 2.8V

VOUT = 2.5V

VOUT = 1.8V

VOUT = 1.5V

0.001

0.01

0.1

en (µV/√Hz)

0.1

1

0.1

0.01

VOUT = 1.5V

VIN = 2.5V

IOUT = 1mA

CBYP = 10nF

CIN = 1µF

TJ = 25°C

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

en (µV/√Hz)

1

Left to right:

COUT = 100µF

COUT = 44µF

COUT = 22µF

COUT = 10µF

COUT = 1µF

1

10

100

0.001

0.01

1000

0.1

1

f (kHz)

100

Output Spectral Noise Density vs. Frequency

Output Spectral Noise Density vs. Frequency

vs. Bypass Capacitance

vs. Output Current

10

VOUT = 1.5V

VIN = 2.5V

IOUT = 1mA

CIN = 1µF

COUT = 1µF

TJ = 25°C

0.001

0.01

0.1

0.1

0.01

1

10

100

Top to bottom:

IOUT = 150mA

IOUT = 100mA

IOUT = 50mA

IOUT = 1mA

1

en (µV/√Hz)

en (µV/√Hz)

0.1

0.01

VOUT = 1.5V

VIN = 2.5V

CIN = 1µF

CBYP = 10nF

COUT = 1µF

TJ = 25°C

0.001

0.01

1000

0.1

f (kHz)

1

10

100

Power Supply Rejection Ratio vs. Frequency

vs. Output Voltage, CBYP = 10nF

vs. Output Voltage, CBYP = 100nF

80

70

70

60

60

50

50

40

20

10

VIN = VOUT + 1V

CIN = COUT = 1µF

CBYP = 10nF

IOUT = 1mA

TJ = 25°C

0

0.01

0.1

PSRR (dB)

80

Top to bottom:

VOUT = 1.5V

VOUT = 1.8V

VOUT = 2.5V

VOUT = 2.8V

VOUT = 3.0V

VOUT = 3.3V

1

30

20

10

10

100

VIN = VOUT + 1V

CIN = COUT = 1µF

CBYP = 100nF

IOUT = 1mA

TJ = 25°C

0

0.01

1000

f (kHz)

2008 Semtech Corp.

40

0.1

1000

f (kHz)

Power Supply Rejection Ratio vs. Frequency

30

1000

10

CBYP = 1nF

CBYP = 10nF

CBYP = 100nF

CBYP = 1µF

1

PSRR (dB)

10

f (kHz)

Top to bottom:

VOUT = 1.5V

VOUT = 2.5V

VOUT = 1.8V

VOUT = 2.8V

VOUT = 3.0V

VOUT = 3.3V

1

10

100

1000

f (kHz)

11

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Evaluation Board Schematic

J1

RIPPLE MON

J2

IN MON

J3

1

U1

J4

5

OUT

R1

IN

C1

C2

R4

3

EN

EN

J12

GND

J13

GND

C5

IQ MON

J14

GND

C4

R2

R3

OUT MON

J6

J7

FLG

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

1

2

3

J11

GND

C3

1

2

J8

EN

4

BYP

GND

2

J5

J10

GND

SC1453

IN

J9

LOAD DRV

J15

GND

J16

1

2

3

LOAD DRV EN

Q1

1

2

3

4

S

S

S

G

D

D

D

D

8

7

6

5

Si4410

Evaluation Board Bill of Materials

Quantity

2

Reference

Part/Description

Vendor

Notes

C 1, C 4

Not placed

C 2, C 3

1µF ceramic

Murata

C5

10nF ceramic

Various

J1

BNC socket

Various

VOUT ripple monitor

J2 - J4

Test pin

Various

Red

J5

Test pin

Various

White

1

J6

Header, 2 pin

Various

1

J7

Not placed

2

J8 , J1 6

Header, 3 pin

Various

1

J9

Test pin

Various

Orange

6

J1 0 - J1 5

Test pin

Various

Black (J14 not placed)

1

Q1

S i 4410

Vishay

2

R1, R2

Not placed

1

R3

See next page

Various

1

R4

10kΩ, 1/10W

Various

1

U1

SC1453ISK-X.X or

SC1453ITSK-XX

Semtech

2

1

1

3

1

2008 Semtech Corp.

12

GRM42-6X7R105K10

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

POWER MANAGEMENT

Evaluation Board Gerber Plots

Top Copper

Bottom Copper

Top Silk Screen

2008 Semtech Corp.

13

Output Voltage Option (V)

R3 Value/Siz e

1.5

10Ω/0.5W

1.8

12Ω/0.5W

2.5

16Ω/0.5W

2.6

16Ω/0.5W

2.7

18Ω/0.5W

2.8

18Ω/0.5W

2.85

18Ω/0.5W

2.9

18Ω/0.5W

3.0

20Ω/0.5W

3.1

20Ω/0.5W

3.2

22Ω/0.5W

3.3

22Ω/0.5W

www.semtech.com

�SC1453

NOT RECOMMENDED FOR NEW DESIGN

POWER MANAGEMENT

Outline Drawing - SOT-23-5

DIMENSIONS

INCHES

MILLIMETERS

DIM

MIN NOM MAX MIN NOM MAX

A

e1

2X E/2

D

A

A1

A2

b

c

D

E1

E

e

e1

L

L1

N

01

aaa

bbb

ccc

N

EI

1

E

2

ccc C

2X N/2 TIPS

e

B

-

.045

-

.057

.006

.051

.020

.009

.118

.069

.114

.063

.110 BSC

.037 BSC

.075 BSC

.012 .018 .024

(.024)

5

0°

10°

.004

.008

.008

0.90

0.00

.90

0.25

0.08

2.80

1.50

aaa C

A2

-

1.15

-

1.45

0.15

1.30

0.50

0.22

3.00

1.75

2.90

1.60

2.80 BSC

0.95 BSC

1.90 BSC

0.30 0.45 0.60

(0.60)

5

0°

10°

0.10

0.20

0.20

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

D

.035

.000

.035

.010

.003

.110

.060

A

SEATING PLANE

A1

C

H

bxN

bbb

C A-B D

GAGE

PLANE

0.25

L

c

01

(L1)

SEE DETAIL

A

DETAIL

A

SIDE VIEW

NOTES:

1.

CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS

OR GATE BURRS.

Land Pattern - SOT-23-5

X

DIM

(C)

G

Z

Y

P

DIMENSIONS

MILLIMETERS

INCHES

(.098)

.055

.037

.024

.043

.141

C

G

P

X

Y

Z

(2.50)

1.40

0.95

0.60

1.10

3.60

NOTES:

1.

2008 Semtech Corp.

THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

14

www.semtech.com

�NOT RECOMMENDED FOR NEW DESIGN

SC1453

POWER MANAGEMENT

Outline Drawing - TSOT-23-5

DIM

A

e1

A

A1

A2

b

c

D

E1

E

e

e1

L

L1

N

01

aaa

bbb

ccc

D

N

2X E/2

E1

1

E

2

ccc C

2X N/2 TIPS

e

B

D

aaa C

A2

-

.000

.028

.012

.003

.110

.060

-

.039

.004

.035

.020

.008

.118

.067

.114

.063

.110 BSC

.037 BSC

.075 BSC

.012 .018 .024

(.024)

5

8°

0°

.004

.008

.010

-

0.00

0.70

0.30

0.08

2.80

1.50

-

1.00

0.10

0.90

0.50

0.20

3.00

1.70

2.90

1.60

2.80 BSC

0.95 BSC

1.90 BSC

0.30 0.45 0.60

(0.60)

5

0°

8°

0.10

0.20

0.25

A

H

N

O

FO T R

R EC

N O

EW M

M

D EN

ES D

IG ED

N

SEATING

PLANE

DIMENSIONS

INCHES

MILLIMETERS

MIN NOM MAX MIN NOM MAX

A1

C

bxN

bbb

c

GAGE

PLANE

C A-B D

0.25

L

01

(L1)

DETAIL

SEE DETAIL

A

A

SIDE VIEW

NOTES:

1.

CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS

OR GATE BURRS.

4. REFERENCE JEDEC STD MO-193, VARIATION AB.

Land Pattern - TSOT-23-5

X

DIM

(C)

G

Z

Y

P

C

G

P

X

Y

Z

DIMENSIONS

MILLIMETERS

INCHES

(.087)

.031

.037

.024

.055

.141

(2.20)

0.80

0.95

0.60

1.40

3.60

NOTES:

1.

THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

Contact Information

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805)498-2111 FAX (805)498-3804

2008 Semtech Corp.

15

www.semtech.com

�