物料型号:

- IS42S16400J

- IS45S16400J

器件简介:

- ISSI的64Mb同步动态随机存取存储器(SDRAM)是一种高速CMOS动态随机存取存储器,设计用于在3.3V的内存系统中运行,包含67,108,864位。内部配置为具有同步接口的四银行DRAM。每个16,777,216位的银行组织为4,096行x 256列x 16位。

引脚分配:

- 数据I/O引脚(DQ0至DQ15):用于数据输入和输出。

- 行地址输入(A0至A11):与读写命令一起选择内存阵列中的一个位置。

- 银行选择地址(BA0, BA1):定义要应用活动、读写或预充电命令的银行。

- 系统时钟输入(CLK):设备的主时钟输入。

- 时钟使能(CKE):确定是否使能CLK输入。

- 芯片选择(CS):确定是否在设备内启用命令输入。

- 行地址脉冲命令(RAS)、列地址脉冲命令(CAS)、写使能(WE):与CAS和WE一起形成设备命令。

参数特性:

- 时钟频率:200、166、143、133 MHz。

- CAS延迟:可编程CAS延迟(2、3时钟)。

- 突发长度:可编程突发长度(1、2、4、8、全页)。

- 突发序列:顺序/交错。

- 自刷新模式:自动刷新(CBR)。

功能详解:

- 同步动态随机存取存储器具有自动刷新模式和节能的掉电模式。所有信号都在时钟信号CLK的正边沿注册。所有输入和输出都与LVTTL兼容。

- 具有在高数据速率下同步突发数据的能力,具有自动列地址生成能力,能够在突发访问期间随机更改列地址。

应用信息:

- 适用于需要高速数据传输和高密度存储的应用。

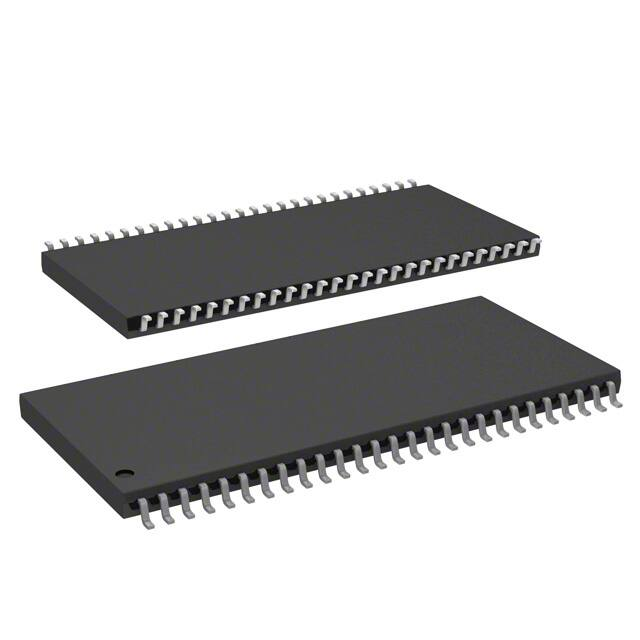

封装信息:

- 54引脚TSOP II、54球TF-BGA(8mm x 8mm)、60球TF-BGA(10.1mm x 6.4mm)。