ispXPGA® Device Datasheet

June 2010

Select Devices Discontinued!

Product Change Notifications (PCNs) have been issued to discontinue select devices in

this data sheet.

The original datasheet pages have not been modified and do not reflect those changes.

Please refer to the table below for reference PCN and current product status.

Product Line

LFX125B

LFX125C

LFX200B

LFX200C

Ordering Part Number

LFX125B-03F256C

LFX125B-03FN256C

LFX125B-04F256C

LFX125B-04FN256C

LFX125B-05F256C

LFX125B-05FN256C

LFX125B-03F516C

LFX125B-04F516C

LFX125B-05F516C

LFX125C-03F256C

LFX125C-03FN256C

LFX125C-04F256C

LFX125C-04FN256C

LFX125C-03F516C

LFX125C-04F516C

LFX200B-03F256C

LFX200B-03FN256C

LFX200B-04F256C

LFX200B-04FN256C

LFX200B-05F256C

LFX200B-05FN256C

LFX200B-03F516C

LFX200B-04F516C

LFX200B-05F516C

LFX200C-03F256C

LFX200C-03FN256C

LFX200C-04F256C

LFX200C-04FN256C

LFX200C-03F516C

LFX200C-04F516C

Product Status

Reference PCN

Discontinued

PCN#09-10

Discontinued

PCN#09-10

Active / Orderable

Discontinued

PCN#09-10

Discontinued

PCN#09-10

5555 N.E. Moore Ct. z Hillsboro, Oregon 97124-6421 z Phone (503) 268-8000 z FAX (503) 268-8347

Internet: http://www.latticesemi.com

�Product Line

LFX500B

LFX500C

LFX1200B

LFX1200C

LFX125EB

LFX125EC

Ordering Part Number

LFX500B-03F516C

LFX500B-04F516C

LFX500B-05F516C

LFX500B-03F900C

LFX500B-03FN900C

LFX500B-04F900C

LFX500B-04FN900C

LFX500B-05F900C

LFX500B-05FN900C

LFX500C-03F516C

LFX500C-04F516C

LFX500C-03F900C

LFX500C-03FN900C

LFX500C-04F900C

LFX500C-04FN900C

LFX1200B-03FE680C

LFX1200B-04FE680C

LFX1200B-05FE680C

LFX1200B-03F900C

LFX1200B-04F900C

LFX1200B-05F900C

LFX1200C-03FE680C

LFX1200C-04FE680C

LFX1200C-03F900C

LFX1200C-04F900C

LFX125EB-03F256C

LFX125EB-03FN256C

LFX125EB-04F256C

LFX125EB-04FN256C

LFX125EB-05F256C

LFX125EB-05FN256C

LFX125EB-03F256I

LFX125EB-03FN256I

LFX125EB-04F256I

LFX125EB-04FN256I

LFX125EB-03F516C

LFX125EB-04F516C

LFX125EB-05F516C

LFX125EB-03F516I

LFX125EB-04F516I

LFX125EC-03F256C

LFX125EC-03FN256C

LFX125EC-04F256C

LFX125EC-04FN256C

LFX125EC-03F256I

LFX125EC-03FN256I

Product Status

Reference PCN

Discontinued

PCN#09-10

Discontinued

PCN#09-10

Discontinued

PCN#03A-10

Discontinued

PCN#03A-10

Active / Orderable

Discontinued

PCN#09-10

Discontinued

PCN#09-10

5555 N.E. Moore Ct. z Hillsboro, Oregon 97124-6421 z Phone (503) 268-8000 z FAX (503) 268-8347

Internet: http://www.latticesemi.com

�Product Line

LFX125EC

(Cont’d)

LFX200EB

LFX200EC

LFX500EB

LFX500EC

Ordering Part Number

LFX125EC-03F516C

LFX125EC-04F516C

LFX125EC-03F516I

LFX200EB-03F256C

LFX200EB-03FN256C

LFX200EB-04F256C

LFX200EB-04FN256C

LFX200EB-05F256C

LFX200EB-05FN256C

LFX200EB-03F256I

LFX200EB-03FN256I

LFX200EB-04F256I

LFX200EB-04FN256I

LFX200EB-03F516C

LFX200EB-04F516C

LFX200EB-05F516C

LFX200EB-03F516I

LFX200EB-04F516I

LFX200EC-03F256C

LFX200EC-03FN256C

LFX200EC-04F256C

LFX200EC-04FN256C

LFX200EC-03F256I

LFX200EC-03FN256I

LFX200EC-03F516C

LFX200EC-04F516C

LFX200EC-03F516I

LFX500EB-03F516C

LFX500EB-04F516C

LFX500EB-05F516C

LFX500EB-03F516I

LFX500EB-04F516I

LFX500EB-03F900C

LFX500EB-03FN900C

LFX500EB-04F900C

LFX500EB-04FN900C

LFX500EB-05F900C

LFX500EB-05FN900C

LFX500EB-03F900I

LFX500EB-03FN900I

LFX500EB-04F900I

LFX500EB-04FN900I

LFX500EC-03F516C

LFX500EC-04F516C

LFX500EC-03F516I

Product Status

Reference PCN

Discontinued

PCN#09-10

Active / Orderable

Discontinued

PCN#09-10

Discontinued

PCN#09-10

Discontinued

PCN#09-10

Discontinued

PCN#09-10

5555 N.E. Moore Ct. z Hillsboro, Oregon 97124-6421 z Phone (503) 268-8000 z FAX (503) 268-8347

Internet: http://www.latticesemi.com

�Product Line

LFX500EC

(Cont’d)

LFX1200EB

LFX1200EC

Ordering Part Number

LFX500EC-03F900C

LFX500EC-03FN900C

LFX500EC-04F900C

LFX500EC-04FN900C

LFX500EC-03F900I

LFX500EC-03FN900I

LFX1200EB-03FE680C

LFX1200EB-04FE680C

LFX1200EB-05FE680C

LFX1200EB-03FE680I

LFX1200EB-04FE680I

LFX1200EB-03F900C

LFX1200EB-04F900C

LFX1200EB-05F900C

LFX1200EB-03F900I

LFX1200EB-04F900I

LFX1200EC-03FE680C

LFX1200EC-04FE680C

LFX1200EC-03FE680I

LFX1200EC-03F900C

LFX1200EC-04F900C

LFX1200EC-03F900I

Product Status

Reference PCN

Discontinued

PCN#09-10

Discontinued

PCN#03A-10

Discontinued

PCN#03A-10

5555 N.E. Moore Ct. z Hillsboro, Oregon 97124-6421 z Phone (503) 268-8000 z FAX (503) 268-8347

Internet: http://www.latticesemi.com

�ispXPGA Family

®

Includes

High,

Performance

Low-Cost

“E-Series”

February 2010

Non-volatile, Infinitely Reconfigurable

Data Sheet DS1026

• Microprocessor configuration interface

• Program E2CMOS while operating from SRAM

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

• Instant-on - Powers up in microseconds via

on-chip E2CMOS® based memory

• No external configuration memory

• Excellent design security, no bit stream to intercept

• Reconfigure SRAM based logic in milliseconds

Eight sysCLOCK™ Phase Locked Loops

(PLLs) for Clock Management

•

•

•

•

•

High Logic Density for System-level

Integration

•

•

•

•

139K to 1.25M functional gates

160 to 496 I/O

1.8V, 2.5V, and 3.3V VCC operation

Up to 414Kb sysMEM™ embedded memory

True PLL technology

10MHz to 320MHz operation

Clock multiplication and division

Phase adjustment

Shift clocks in 250ps steps

sysIO™ for High System Performance

• High speed memory support through SSTL and

HSTL

• Advanced buses supported through PCI, GTL+,

LVDS, BLVDS, and LVPECL

• Standard logic supported through LVTTL,

LVCMOS 3.3, 2.5 and 1.8

• 5V tolerant I/O for LVCMOS 3.3 and LVTTL

interfaces

• Programmable drive strength for series termination

• Programmable bus maintenance

High Performance Programmable Function

Unit (PFU)

• Four LUT-4 per PFU supports wide and narrow

functions

• Dual flip-flops per LUT-4 for extensive pipelining

• Dedicated logic for adders, multipliers, multiplexers, and counters

Flexible Memory Resources

• Multiple sysMEM Embedded RAM Blocks

– Single port, Dual port, and FIFO operation

• 64-bit distributed memory in each PFU

– Single port, Double port, FIFO, and Shift

Register operation

Two Options Available

• High-performance sysHSI (standard part number)

• Low-cost, no sysHSI (“E-Series”)

sysHSI™ Capability for Ultra Fast Serial

Communications

Flexible Programming, Reconfiguration,

and Testing

• Up to 800Mbps performance

• Up to 20 channels per device

• Built in Clock Data Recovery (CDR) and

Serialization and De-serialization (SERDES)

• Supports IEEE 1532 and 1149.1

Table 1. ispXPGA Family Selection Guide

Functional Gates

ispXPGA 125/E

ispXPGA 200/E

ispXPGA 500/E

ispXPGA 1200/E3

139K

210K

476K

1.25M

PFUs

484

676

1764

3844

LUT-4s

1936

2704

7056

15376

Logic FFs

3.8K

5.4K

14.1K

30.7K

sysMEM Memory

92K

111K

184K

414K

Distributed Memory

30K

43K

112K

246K

20

24

40

90

EBR

1

sysHSI Channels

User I/O

Packaging

4

8

12

20

160/176

160/208

336

496

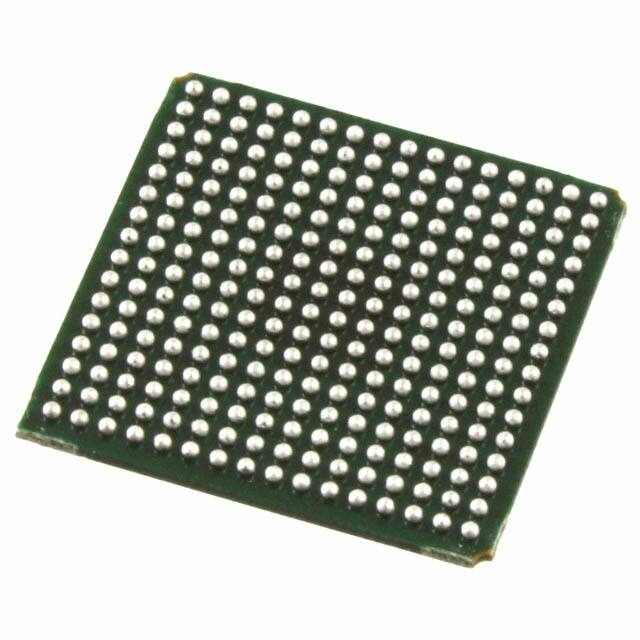

256 fpBGA

516 fpBGA2

256 fpBGA

516 fpBGA2

516 fpBGA2

900 fpBGA

680 fpSBGA

900 fpBGA

1. “E-Series” does not support sysHSI.

2. FH516 package was converted to F516 via PCN #09A-08.

3. Discontinued via PCN #03A-10.

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

1

DS1026_15.0

�Lattice Semiconductor

ispXPGA Family Data Sheet

ispXPGA Family Overview

The ispXPGA family of devices provides the ideal vehicle for the creation of high-performance logic designs that

are both non-volatile and infinitely re-programmable. Other FPGA solutions force a compromise, being either reprogrammable or non-volatile. This family couples this capability with a mainstream architecture containing the features required for today’s system-level design.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA family is available in two options. The standard device supports sysHSI capability for ultra fast serial

communications while the lower-cost “E-Series” supports the same high-performance FPGA fabric without the sysHSI Block.

Electrically Erasable CMOS (E2CMOS) memory cells provide the ispXPGA family with non-volatile capability.

These allow logic to be functional microseconds after power is applied, allowing easy interfacing in many applications. This capability also means that expensive external configuration memories are not required and that designs

can be secured from unauthorized read back. Internal SRAM cells allow the device to be infinitely reconfigured if

desired. Both the SRAM and E2CMOS cells can be programmed and verified through the IEEE 1532 industry standard. Additionally, the SRAM cells can be configured and read-back through the sysCONFIG™ peripheral port.

The family spans the density and I/O range required for the majority of today’s logic designs, 139K to 1.25M functional gates and 160 to 496 I/O. The devices are available for operation from 1.8V, 2.5V, and 3.3V power supplies,

providing easy integration into the overall system.

System-level design needs are met through the incorporation of sysMEM dual-port memory blocks, sysIO

advanced I/O support, and sysCLOCK Phase Locked Loops (PLLs). High-speed serial communications are supported through multiple sysHSI blocks, which provide clock data recovery (CDR) and serialization/de-serialization

(SERDES).

The ispLEVER™ design tool from Lattice allows easy implementation of designs using the ispXPGA product. Synthesis library support is available for major logic synthesis tools. The ispLEVER tool takes the output from these

common synthesis packages and place and routes the design in the ispXPGA product. The tool supports floor

planning and the management of other constraints within the device. The tool also provides outputs to common

timing analysis tools for timing analysis.

To increase designer productivity, Lattice provides a variety of pre-designed modules referred to as IP cores for the

ispXPGA product. These IP cores allow designers to concentrate on the unique portions of their design while using

pre-designed blocks to implement standard functions such as bus interfaces, standard communication interfaces,

and memory controllers.

Through the use of advanced technology and innovative architecture the ispXPGA FPGA devices provide designers with excellent speed performance. Although design dependent, many typical designs can run at over 150MHz.

Certain designs can run at over 300MHz. Table 2 details the performance of several building blocks commonly

used by logic designers.

Table 2. ispXPGA Speed Performance for Typical Building Blocks

Function

Performance

8:1 Asynch MUX

150 MHz

1:32 Asynch Demultiplexer

125 MHz

8 x 8 2-LL Pipelined Multiplier

225 MHz

32-bit Up/Down Counter

290 MHz

32-bit Shift Register

360 MHz

2

�Lattice Semiconductor

ispXPGA Family Data Sheet

Architecture Overview

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA architecture is a symmetrical architecture consisting of an array of Programmable Function Units

(PFUs) enclosed by Input Output Groups (PICs) with columns of sysMEM Embedded Block RAMs (EBRs) distributed throughout the array. Figure 1 illustrates the ispXPGA architecture. Each PIC has two corresponding sysIO

blocks, each of which includes one input and output buffer. On two sides of the device, between the PICs and the

sysIO blocks, there are sysHSI High-Speed Interface blocks. The symmetrical architecture allows designers to easily implement their designs, since any logic function can be placed in any section of the device.

The PFUs contain the basic building blocks to create logic, memory, arithmetic, and register functions. They are

optimized for speed and flexibility allowing complex designs to be implemented quickly and efficiently.

The PICs interface the PFUs and EBRs to the external pins of the device. They allow the signals to be registered

quickly to minimize setup times for high-speed designs. They also allow connections directly to the different logic

elements for fast access to combinatorial functions.

The sysMEM EBRs are large, fast memory elements that can be configured as RAM, ROM, FIFO, and other storage types. They are designed to facilitate both single and dual-port memory for high-speed applications.

These three components of the architecture are interconnected via a high-speed, flexible routing array. The routing

array consists of Variable Length Interconnect (VLI) lines between the PICs, PFUs, and EBRs. There is additional

routing available to the PFU for feedback and direct routing of signals to adjacent PFUs or PICs.

The sysIO blocks consist of configurable input and output buffers connected directly to the PICs. These buffers can

be configured to interface with 16 different I/O standards. This allows the ispXPGA to interface with other devices

without the need for external transceivers.

The sysHSI blocks provide the necessary components to allow the ispXPGA device to transfer data at up to

800Mbps using the LVDS standard. These components include serializing, de-serializing, and clock data recovery

(CDR) logic.

The sysCLOCK blocks provide clock multiplication/division, clock distribution, delay compensation, and increased

performance through the use of PLL circuitry that manipulates the global clocks. There is one sysCLOCK block for

each global clock tree in the device.

3

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 1. ispXPGA Block Diagram

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

PFU

PIC

sysMEM Block

sysCLOCK PLL

sysHSI Block

sysIO Buffer

Programmable Function Unit

The Programmable Function Unit (PFU) is the basic building block of the ispXPGA architecture. The PFUs are

arranged in rows and columns in the device with PFU (1,1) referring to (row 1, column 1). Each PFU consists of

four Configurable Logic Elements (CLEs), four Configurable Sequential Elements (CSEs), and a Wide Logic Generator (WLG). By utilizing these components, the PFU can implement a variety of functions. Table 3 lists some of

the function capabilities of the PFU.

There are 57 inputs to each PFU and nine outputs. The PFU uses 20 inputs for logic, and 37 inputs drive the control logic from which six control signals are derived for the PFU.

Table 3. Function Capability of ispXPGA PFU

Function

Capability

Look-up table

LUT-4, LUT-5, LUT-6

Wide logic functions

Up to 20 input logic functions

Multiplexing

2:1, 4:1, 8:1

Arithmetic logic

Dedicated carry chain and booth multiplication logic

Single-port RAM

16X1, 16X2, 16X4, 32X1, 32X2, 64X1

Double-port RAM

16X1, 16X2, 32X1

Shift register

8-bit shift registers (up to 32-bit shift capability)

4

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 2. ispXPGA PFU

COUT(r,c)

OE

OE

PFUCLK0

PFUCLK1

CEB0

CEB1

SR

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Control

Logic

WLGW0

S3

SYNC/ASYNC

CCG

IN

WIN2

WIN3

CLK/LE

CE

WLGW1

D

S

R

SEL0

XIN3

LUT-4

CCG

SEL0

IN

XIN2

XIN3

SEL1

SEL1

4C

YIN0

YIN2

LUT-4

COUT

LUT-4 SUM

S1

WLGY0

SYNC/ASYNC

CLE2

IN

YIN2

YIN3

WLGY1

4D

CLE3

ZIN2

LUT-4

WLGZ0

CCG

ZIN3

IN

ZIN2

ZIN3

SEL3

SEL3

CIN(r,c) from

COUT(r-1,c)

5

CLK/LE

CLK/LE

CE

CE

DD

SS

RR

S0

SYNC/ASYNC

ZIN1

Y0

QQ

Y1

Q

CLK/LE

CE

SEL2

COUT

LUT-4 SUM

DD

SS

RR

D

S

R

SEL2

ZIN0

X1

Q

CLK/LE

CE

CCG

YIN3

D

S

R

X0

QQ

CLK/LE

CLK/LE

CE

CE

WLGX1

SYNC/ASYNC

YIN1

DD

SS

RR

S2

Wide Logic Generator

CLE1

XIN2

WLGX0

4B

COUT

LUT-4 SUM

SYNC/ASYNC

XIN1

W1

Q

CLK/LE

CE

SEL0

XIN0

W0

Q

CSE1

CLE0

WIN2

WIN3

D

S

R

CSE2

LUT-4

COUT

LUT-4 SUM

WLGZ1

CLK/LE

CLK/LE

CE

CE

D

S

R

Z0

QQ

Q

CLK/LE

CE

CSE3

WIN1

CSE0

COUT

4A

WIN0

Z1

�Lattice Semiconductor

ispXPGA Family Data Sheet

Configurable Logic Element

The CLE is made up of a four-input Look-up Table (LUT-4), a Carry Chain Generator (CCG), and a two-input AND

gate. The LUT-4 creates various combinatorial and memory elements, the CCG creates a single one-bit full adder,

and the two-input AND gate can expand the CCG to incorporate Booth Multiplier capability by feeding the output of

the AND gate to one of the inputs of the CCG.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Of the five inputs that feed each CLE, two are dedicated inputs into each LUT-4 and the remaining three take on

varying functionality. The third and fourth inputs can be used as either inputs to the LUT-4 or as a Feed-Thru to the

CSE via the WLG. The fifth input can be a data port when the LUT is configured as Distributed Memory, a select

line for multiplexer operation, or a Feed-Thru directly to the CSE via the WLG (Figure 2).

Look-Up Table – Combinatorial Mode

In combinatorial mode, the LUT-4 can implement any logic function up to four inputs. By using the carry chain and

the WLG, each LUT-4 can be combined to form the enhanced functions listed in Table 3.

Look-Up Table – Distributed Memory Mode

In the distributed memory mode, the LUT functions as a memory element. The inputs to the LUT function as

Address and Data. Each PFU is capable of implementing up to 64 SRAM bits. Both single and double port RAM

can be performed in the PFU (Table 3). Furthermore, the distributed memory can be configured as either synchronous or asynchronous memory. Figure 3 illustrates the LUT while in distributed memory mode. When using any

LUT in the PFU in memory mode, the Set/Reset signal will be used for Write Enable (WE(SR)) and the CLK0 signal

will be used as the clock for synchronous read and write.

Figure 3. LUT in Distributed Memory Mode

PFUCLK0

CEB0

WE (SR)

ADDR[0] (IN0)

ADDR[1] (IN1)

ADDR[2] (IN2)

LUT-4

DOUT (4A)

ADDR[3] (IN3)

DIN (SEL)

Look-Up Table – Shift Register Mode

In the shift register mode, the LUT functions as a 1-bit to 8-bit shift register. This means that each PFU can implement up to four 8-bit shift registers or any cascaded combination. Figure 4 illustrates the LUT when configured in

shift register mode.

6

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 4. LUT in Shift Register Mode

PFUCLK0

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

CEB0

SEL (SHIFTIN)

LUT-4

SHIFTOUT (4A)

Carry Chain Generator

The Carry Chain Generator is useful for implementing high-speed arithmetic functions. The CCG consists of a twoinput XOR gate whose carryout can be cascaded with the input of the adjacent CCG. As shown in Figure 5, the

carryin signal feeds CLE3 of the PFU and is propagated through CLE2 and CLE1 before reaching CLE0. The sum

output of the CCG can be fed to the CSE through the WLG. The carryout must propagate to CLE0 for use outside

the PFU. The carryout from the PFU can feed the W0 input of CSE0. The CCG also helps to effectively implement

wider functions by using its logic elements to expand the capabilities of the LUT-4.

Figure 5. Carry Chain Generator

COUT(r,c)

COUT to

CSE0

CLE0

SUM3

CLE1

SUM2

CLE2

SUM1

CLE3

SUM0

A

B

COUT

SUM

CIN

CIN from

Routing

COUT(r+1,c)

Wide Logic Generator

The WLG contains the logic necessary to implement wide gate functions. This is made up of a set of multiplexers

that are located between the CLE and the CSE. The WLG helps in enhancing the wide gating capability of the PFU.

The outputs of each CLE can be cascaded in the WLG to build wide gating functions. Wide multiplexing functions

are also possible with a similar use of the WLG. Figure 6 illustrates the WLG.

7

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 6. ispXPGA Wide Logic Generator

COUT

WIN2

WIN3

4A

S3

SEL0

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

WLGW0

WLGW1

4B

XIN2

XIN3

WLGX0

S2

SEL1

WLGX1

SEL3

4C

SEL2

4D

YIN2

YIN3

S1

WLGY0

WLGY1

ZIN2

ZIN3

WLGZ0

S0

WLGZ1

Configurable Sequential Element

There are two registers in each CSE for a total of eight registers in each PFU. This high register count assists in

implementing efficient pipelined applications with no utilization penalty. Each register can be configured as a latch

or D type flip-flop with either synchronous or asynchronous set or reset. Figure 2 shows the signals that feed the

register’s D inputs. Feed-through signals in the architecture ensure that registers are efficiently utilized even if the

accompanying LUT is occupied.

Control Logic

The control signals available to the registers in a PFU are Clock, Clock Enable, and Set/Reset. Figure 7 shows the

various options available to generate the clock signal. As can be seen, the clock signal is the output of a 12:1 MUX

with true and compliment versions available from the 12:1 MUX. Each CSE can chose whether it uses the true or

complement form of the clock. Figure 8 shows the Set/Reset selection for each PFU in the ispXPGA. A common

8

�Lattice Semiconductor

ispXPGA Family Data Sheet

Set/Reset signal controls all the registers for each PFU. This common Set/Reset signal is composed of the logical

OR term of the Global Set/Reset signal (GSR) and the selected signal from routing. The polarity of this signal is not

controllable inside the PFU. The polarity of the Global Set/Reset signal (GSR) is programmable. Figure 9 shows

the Clock Enable and Output Enable selection for each PFU.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Figure 7. Clock Selection per PFU

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

PFUCLK0

PFUCLK1

From routing

4

Figure 8. Set/Reset Selection per PFU

8

From routing

Set/Reset

GSR

Figure 9. Clock Enable and Output Enable Selection per PFU

8

From routing

CEB0

8

CEB1

From routing

OE

Programmable Input/Output Cell

The Programmable Input/Output Cell (PIC) is an essential part of the symmetrical architecture of the ispXPGA

Family. The PICs interface the PFUs and EBRs to the sysIO and sysHSI blocks of the device.

Each PIC contains two Programmable Input/Outputs (PIOs) with a total of 21 inputs and 10 outputs. There are 18

inputs from routing, two inputs from the sysIO buffers, and the Global Set/Reset signal. Four outputs of the PIC

connect to routing and two outputs are available as Output Enables for the tri-statable Long Lines. The remaining

four outputs feed the sysIO buffers directly (one output enable and one output to each). Each PIC associated with a

sysHSI block has four additional inputs and six additional outputs to support the sysHSI blocks. The four additional

inputs come from the sysHSI block associated with the PIC. The four of the six additional outputs come from the

PIC outputs and feed the sysHSI block, while the remaining two outputs feed routing. Figure 10 shows the block

diagram of the PIC with the sysHSI block inputs and outputs.

9

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 10. ispXPGA PIC

GSR

sysIO

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

9

2

From routing

PIO0

To routing

2

From sysHSI block

2

To sysHSI block

Only for PICs

associated with

sysHSI blocks

To routing

Only for PICs

associated with

sysHSI blocks

PIC

2

To routing

From sysHSI block

2

To sysHSI block

9

2

To routing

PIO1

From routing

sysIO

OE1 OE0

Programmable Input/Output

The PIO is the building block of a PIC. The PIO has a total of 11 inputs and five outputs. Nine of the 11 inputs are

generated from routing. The inputs from routing are the PIO Input (IN), Feed-Thru (FT), Clock (CLK), Input Clock

Enable (ICE), Input Set/Reset (ISR), Output Clock Enable (OCEN), Output Set/Reset (OSR), PIO Output Enable

(OEN), and PIO Input Enable (IEN). The remaining inputs are the sysIO input buffer signal and the Global Set/

Reset signal. Three of the five outputs (OUT0, OUT1, and OE) feed routing. The last two outputs feed the sysIO

buffer directly as the output and output enable of the sysIO output buffer.

PIOs associated with sysHSI blocks contain two additional inputs and outputs to support the sysHSI block. The two

inputs come from the sysHSI block associated with the PIO, and the two outputs feed the sysHSI block. One of the

inputs routes directly through the PIO to routing, while the other is multiplexed with the Feed-Thru, register bypass,

and Q output of the register to form the OUT1 output of the PIO. The outputs to the sysHSI block are the same signals as the outputs which feed the sysIO buffers (sysIO Output and sysIO Output Enable).

Each PIO has an input register, an output register, and an output enable register as shown in Figure 11. The input

register path of the PIO has a ‘delay’ option, which slows the data-flow. A two-input OR function of the Global Set/

Reset (GSR) and Set/Reset (ISR or OSR) signals creates the set/reset term for the respective registers. Each PIO

has two pairs of set/reset and clock enable signals. One is exclusive to the input register, whereas the other is common for both the output and output enable registers. The clock (CLK) is common to all registers in a PIO, and the

polarity of the clock is controllable. The input, output, and the output enable registers can be configured as a latch

or D-type flip-flop. Each PIO is capable of generating an output enable signal, which in turn becomes a PIC output.

10

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 11. ispXPGA PIO

Only for PIOs associated with sysHSI Blocks

From sysHSI block

From sysHSI block

To Routing

Feed-through (FT)

OUT0

D

Q

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

From sysIO Input

Clock (CLK)

Input Clock Enable (ICEN)

Delay

OUT1

CLK/LE

CE

S R

Input Set/Reset (ISR)

Global Set/Reset(GSR)

To sysIO

Output

PIO Input (IN)

D

Q

To sysHSI

block

CLK/LE

Output Clock Enable (OCEN)

CE

S R

Output Set/Reset (OSR)

PIO Output Enable(OEN)

Only for PIOs

Associated with

sysHSI Blocks

To sysHSI

block

D

Q

To sysIO

Output

Enable

CLK/LE

CE

S R

OE

PIO Input Enable (IEN)

VLI Routing Resources

The ispXPGA architecture contains a Variable-Length-Interconnect (VLI) routing technology connecting the PFUs,

PICs, and EBRs in the device. There are four types of routing resources, Global Lines, Long Lines, General Interconnect, and Local Lines forming the global routing structure. This allows a signal to be routed to any element in

the device with the optimal delay.

The Global Lines consist of global clock lines and a global set/reset line. These lines are routed to all elements in

the device. They are specifically designed for high speed, predictable timing regardless of fan-out. The global clock

lines can also be used as dedicated inputs.

The Long Lines consist of Horizontal and Vertical Long Lines (HLL and VLL). The VLL and HLL are tri-statable

lines spanning the entire device. These lines allow fast routing for high fan-out nets and general-purpose functions.

The General Interconnect consists of Double and Deca Lines. The Double Lines connect up to three elements (two

plus the driving element), while the Deca Lines connect up to eleven elements (ten plus the driving element).

The Local Lines are extremely fast routing paths consisting of Feedback and Direct Connect Lines. The Feedback

Lines are internal routing paths from the PFU outputs to the PFU inputs. The Direct Connect Lines connect all adjacent elements.

The Common Interface Block (CIB) provides the link between the logic element (PFU, PIC, or EBR) and the VLI

Routing resources. The CIB is a switch matrix that can be programmed to connect virtually any routing resource to

any input or output of the logic element.

11

�Lattice Semiconductor

ispXPGA Family Data Sheet

Memory

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA architecture provides a large amount of resources for memory intensive applications. Embedded

Block RAMs (EBRs) are available to complement the Distributed Memory that is configured in the PFUs (see LookUp Table -Distributed Memory Mode in the PFU section above). Each memory element can be configured as RAM

or ROM. Additionally, the internal logic of the device can be used to configure the memory elements as FIFO and

other storage types. These EBRs are referred to as sysMEM blocks. Refer to Table 1 for memory resources per

device.

sysMEM Blocks

The sysMEM blocks are organized in columns distributed throughout the device. Each EBR contains 4.6K bits of

dual-port RAM with dedicated control, address, and data lines for each port. Each column of sysMEM blocks has

dedicated address and control lines that can be used by each block separately or cascaded to form larger memory

elements. The memory cells are symmetrical and contain two sets of identical control signals. Each port has a

read/write clock, clock enable, write enable, and output enable. Figure 12 illustrates the sysMEM block.

The ispXPGA memory block can operate as single-port or dual-port RAM. Supported configurations are:

•

•

•

•

512 x 9 bits single-port

256 x 18 bits single-port

512 x 9 bits dual-port

256 x18 bits dual-port

(8 bits data / 1 bit parity)

(16 bits data / 2 bits parity)

(8 bits data / 1 bit parity)

(16 bits data / 2 bits parity)

The data widths of “9” and “18” are ideal for applications where parity is necessary. This allows 9 data bits, 8 data

bits plus a parity bit, 18 data bits, or 16 data bits plus two parity bits. The logic for generating and checking the parity must be customized separately.

Figure 12. sysMEM Block Diagram

ADDRA

ADDRB

DATAA

DATAB

CLKA

CLKB

sysMEM Block

CEA

CE B

WEA

WEB

OEA

OEB

Read and Write Operations

The ispXPGA EBR has fully synchronous read and write operations as well as an asynchronous read operation.

These operations allow several different types of memory to be implemented in the device.

Synchronous Read: The Clock Enable (CE) and Write Enable (WE) signals control the synchronous read operation. When the CE signal is low, the clock is enabled. When the WE signal is low the read operation begins. Once

the address (ADDR) is present, a rising clock edge (or falling edge depending on polarity) causes the stored data

to be available on the DATA port. Figure 13 illustrates the synchronous read timing.

12

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 13. EBR Synchronous Read Timing Diagram

tEBCPW

CLK

tEBCES

tEBCEH

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

CE

tEBWES

WE

tEBWEH

OE

DATA

tEBOEDIS

Invalid Data

tEBCO

tEBWEDIS

Valid Data

tEBADDS

ADDR

tEBOEEN

tEBWEEN

Valid Data

tEBADDH

Synchronous Write: The WE signal controls the synchronous write operation. When the WE signal is high, the

write operation begins. Once the address and data are present and the Output Enable (OE) is active, a rising clock

edge (or falling edge depending on polarity) causes the data to be stored into the EBR. Figure 14 illustrates the

synchronous write timing.

Figure 14. EBR Synchronous Write Timing Diagram

CLK

tEBPW

tEBWES

WE

tEBWEH

tEBDATAH

DATA

tEBDATAS

tEBADDH

ADDR

WRITE

tEBADDS

WRITE

Asynchronous Read: The WE signal controls the asynchronous read operation. When the WE signal is low, the

read operation begins. Shortly after the address is present, the stored data is available on the DATA port. Figure 15

illustrates the asynchronous read timing. For more information about the EBR, refer to TN1028 ispXPGA Memory

Usage Guidelines.

Figure 15. EBR Asynchronous Read Timing Diagram

WE

OE

tEBOEDIS

Invalid Data

DATA0

DATA

ADDR

ADDR0

tEBOEEN

tEBWEEN

tEBWEDIS

DATA1

tEBARAD_H

DATA1

ADDR1

tEBARADO

13

ADDR2

�Lattice Semiconductor

ispXPGA Family Data Sheet

sysCLOCK PLL Description

The sysCLOCK PLL circuitry consists of Phase-Lock Loops (PLLs) and the various dividers, reset, and feedback

signals associated with the PLLs. This feature gives the user the ability to synthesize clock frequencies and generate multiple clock signals for routing within the device. Furthermore, it can generate clock signals that are aligned

either at the board level or the device level.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA devices provide up to eight PLLs. Each PLL receives its input clock from its associated global clock

pin, and its output is routed to the associated global clock net. For example, PLL0 receives its clock input from the

GCLK0 global clock pin and provides output to the CLK0 global clock net. The PLL also has the ability to output a

secondary clock that is a division of the primary clock output. When using the secondary clock, the secondary

clock will be routed to the neighboring global clock net. For example, PLL0 will drive its primary clock output on the

CLK0 global clock net and its secondary clock output will drive the CLK1 global clock net. Additionally, each PLL

has a set of PLL_RST, PLL_FBK, and PLL_LOCK signals. The PLL_RST signal can be generated through routing

or a dedicated dual-function I/O pin. The PLL_FBK signal can be generated through a dedicated dual-function I/O

pin or internally from the Global Clock net associated with the PLL. The PLL_LOCK signal feeds routing directly

from the sysCLOCK PLL circuit. Figure 17 illustrates how the PLL_RST and PLL_FBK signals are generated.

Each PLL has four dividers associated with it, M, N, V, and K. The M divider is used to divide the clock signal,

while the N divider is used to multiply the clock signal. The V divider allows the VCO frequency to operate at

higher frequencies than the clock output, thereby increasing the frequency range. The K divider is only used when

a secondary clock output is needed. This divider divides the primary clock output and feeds to the adjacent global

clock net. Different combinations of these dividers allow the user to synthesize clock frequencies. Figure 16 shows

the ispXPGA PLL block diagram.

The PLL also has a delay feature that allows the output clock to be advanced or delayed to improve set-up and

clock-to-out times for better performance. This operates by inserting delay on the input or feedback lines of the

PLL. For more information on the PLL, please refer to TN1003, sysCLOCK PLL Usage and Design Guidelines.

Figure 16. ispXPGA PLL Block Diagram

PLL_LOCK

CLK_OUT

GCLK_IN

Input Clock

(M) Divider

÷ 1 to 32

Programmable

+Delay

--------------------

Post-scalar

(V) Divider

÷

1, 2, 4, 8,

16, 32

PLL (n)

Programmable

-Delay

Clock Net

PLL_RST

Clock (K)

Divider

÷

2, 4, 8,

16, 32

To Adjacent_PLL

From

Adjacent_PLL

Feedback

Divider (N)

X 1 to 32

PLL_FBK

14

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 17. ispXPGA PLL_RST and PLL_FBK Generation

I/O/PLL_RST

To PLL

From Routing

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

I/O/PLL_FBK

To PLL

From Clock Net

Clock Routing

The Global Clock Lines (GCLK) have two sources, their dedicated pins and the sysCLOCK circuit. Figure 18 illustrates the generation of the Global Clock Lines.

Figure 18. Global Clock Line Generation

From Routing

GCLK0

GCLK7

CLK_OUT0

PLL0

CLK0

CLK7

SEC_OUT0

CLK_OUT7

PLL7

SEC_OUT7

From Routing

GCLK1

GCLK6

CLK_OUT1

PLL1

CLK1

CLK6

SEC_OUT1

CLK_OUT6

PLL6

SEC_OUT6

From Routing

GCLK2

GCLK5

CLK_OUT2

PLL2

CLK2

CLK5

SEC_OUT2

CLK_OUT5

PLL5

SEC_OUT5

From Routing

GCLK3

GCLK4

CLK_OUT3

PLL3

CLK3

SEC_OUT3

CLK4

CLK_OUT4

PLL4

SEC_OUT4

sysIO Capability

All the ispXPGA devices have eight sysIO banks, where each bank is capable of supporting multiple I/O standards.

Each sysIO bank has its own I/O supply voltage (VCCO) and reference voltage (VREF) resources allowing each

bank complete independence from the others. Each I/O is individually configurable based on the bank’s VCCO and

VREF settings. In addition, each I/O has configurable drive strength, weak pull-up, weak pull-down, or a bus-keeper

latch. Table 4 lists the number of I/Os supported per bank in each of the ispXPGA devices. In addition, 5V tolerant

inputs are specified within an I/O bank that is connected to VCCO of 3.0V to 3.6V for LVCMOS 3.3, LVTTL and PCI

interfaces.

Table 5 lists the sysIO standards with the typical values for VCCO, VREF and VTT.

The TOE, JTAG TAP pins, PROGRAM, CFG0 and DONE pins of the ispXPGA device are the only pins that do not

have the sysIO capabilities. The TOE and CFG0 pins operate off the VCC of the device, supporting only the LVCMOS standard corresponding to the device supply voltage. The TAP pins have a separate supply voltage (VCCJ),

which determines the LVCMOS standard corresponding to that supply voltage.

There are three classes of I/O interface standards that are implemented in the ispXPGA devices. The first is the unterminated, single-ended interface. It includes the 3.3V LVTTL standard along with the 1.8V, 2.5V, and 3.3V LVCMOS interface standards. Additionally, PCI and AGP-1X are subsets of this type of interface.

15

�Lattice Semiconductor

ispXPGA Family Data Sheet

The second type of interface implemented is the terminated, single-ended interface standard. This group of interfaces includes different versions of SSTL and HSTL interfaces along with CTT, and GTL+. Usage of these particular I/O interfaces requires an additional VREF signal. At the system level a termination voltage, VTT, is also required.

Typically an output will be terminated to VTT at the receiving end of the transmission line it is driving.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The third type of interface standards are the differential standards LVDS, BLVDS, and LVPECL. The differential

standards require two I/O pins to create the differential pair. The logic level is determined by the difference in the

two signals. Table 6 lists how these interface standards are implemented in the ispXPGA devices.

For more information on sysIO capability, refer to TN1000, sysIO Usage Guidelines for Lattice Devices.

Figure 19. sysIO Banks per Device

VCCO6

I/O 0

I/O N

I/O 0

Bank 6

VREF0

GND

I/O N

VCCO5

Bank 5

Bank 0

VCCO0

VREF6

GND

VCCO7

VREF7

GND

I/O N

Bank 7

I/O 0

VREF5

GND

I/O N

I/O 0

I/O 0

I/O N

VREF1

GND

I/O N

VCCO4

Bank 4

Bank 1

VCCO1

Bank 2

VREF4

GND

I/O 0

Bank 3

I/O N

I/O 0

I/O N

I/O 0

VCCO3

VREF3

GND

VCCO2

VREF2

GND

Table 4. Number of I/Os per Bank

Device

Max. Number of I/Os per Bank (N)

XPGA 1200

62

XPGA 500

42

XPGA 200

26

XPGA 125

22

16

�Lattice Semiconductor

ispXPGA Family Data Sheet

Table 5. ispXPGA Supported I/O Standards

VCCO

VREF

VTT

LVTTL

3.3V

N/A

N/A

LVCMOS-3.3

3.3V

N/A

N/A

LVCMOS-2.5

2.5V

N/A

N/A

LVCMOS-1.8

1.8V

N/A

N/A

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

sysIO Standard

PCI

3.3V

N/A

N/A

AGP-1X

3.3V

N/A

N/A

SSTL3, Class I, II

3.3V

1.5V

1.5V

SSTL2, Class I, II

2.5V

1.25V

1.25V

HSTL, Class I

1.5V

0.75V

0.75V

HSTL, Class III

1.5V

0.9V

1.5V

GTL+

N/A

1.0V

1.5V

LVPECL

3.3V

N/A

N/A

LVDS

2.5V

N/A

N/A

BLVDS

2.5V

N/A

N/A

1

1. VCCO must be 2.5V for high speed serial operations (sysHSI block).

Table 6. Differential Interface Standard Support1

sysIO Buffer Not Using sysHSI Block

LVDS

BLVDS

LVPECL

sysIO Buffer Using sysHSI Block

Driver

Supported with external resistor network

Receiver

Supported with standard termination

Supported with standard termination

Driver

Supported with external resistor network

Not supported

Receiver

Supported (may need termination)

Supported (may need termination)

Driver

Supported with external resistor network

Not supported

Receiver

Supported with termination

Supported with termination

1. For more information, refer to TN1000, sysIO Usage Guidelines for Lattice Devices.

17

Supported

�Lattice Semiconductor

ispXPGA Family Data Sheet

High Speed Serial Interface Block (sysHSI Block)1

The High Speed Serial Interface (sysHSI) allows high speed serial data transfer over a pair of LVDS I/O. The

ispXPGA devices have multiple sysHSI blocks.

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Each sysHSI block has two SERDES blocks which contain two main sub-blocks, Transmitter (with a serializer) and

Receiver (with a deserializer) including Clock/Data Recovery Circuit (CDR). Each SERDES can be used as a full

duplex channel. The two SERDES in sysHSI blocks share a common clock and must operate at the same nominal

frequency. Figure 20 shows the sysHSI block.

Device features support two data coding modes: 10B/12B and 8B/10B (for use with other encoding schemes, see

Lattice’s sysHSI technical notes). The encoding and decoding of the 10B/12B standard are performed within the

sysHSI block. For the 8B/10B standard, the symbol boundaries are aligned internally but the encoding and decoding are performed outside the sysHSI block.

Each SERDES block receives a single high speed serial data input stream (with embedded clock) from an input,

and provide a low speed 10-bit wide data stream and a recovered clock to the device. For transmitting, SERDES

converts a 10-bit wide low-speed data stream to a single high-speed data stream with embedded clock for output.

Additionally, multiple sysHSI blocks can be grouped together to form a source synchronous interface of 1-10 channels.

For more information on the SERDES/CDR, refer to TN1020, sysHSI Usage Guidelines.

Figure 20. sysHSI Block Diagram

SOUT

SERDES(HSI#A)

Serializer

SIN

10

TXD

10

RXD

RECCLK

From PICs

To PICs

To PICs

Deserializer and Clock/Data Recovery

SYDT

sysIO

Shared Source

Synchronous Pins Drive

Multiple sysHSI blocks

CDRRST

CAL

SS_CLKOUT

CSLOCK

CSPLL

REFCLK

SS_CLKIN

CDRRST

SYDT

To PICs

From PICs

From PICs

To PICs

From Global

Clock Tree

From PICs

To PICs

Deserializer and Clock/Data Recovery

SIN

RECCLK

10

SOUT

Serializer

SERDES(HSI#B)

1.

“E-Series” does not support sysHSI.

18

10

RXD

TXD

To PICs

To PICs

From PICs

�Lattice Semiconductor

ispXPGA Family Data Sheet

Configuration and Programming

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA family of devices takes a unique approach to FPGA configuration memory. It contains two types of

memory, Static RAM and non-volatile E2CMOS cells. The static RAM is used to control the functionality of the

device during normal operation and the E2CMOS memory cells are used to load the SRAM. The E2CMOS memory

module can be thought of as the hard drive for the ispXPGA configuration and the SRAM as the working configuration memory. There is a one-to-one relationship between SRAM memory and the E2CMOS cells. The SRAM can

be configured either from the E2CMOS memory or from an external source, as shown in Figure 21.

Figure 21 shows the different ports and modes that are used in the configuration and programming of the ispXPGA

devices. There are two possible ports that can be used for configuration of the SRAM memory: the ISP port which

supports the IEEE 1149.1 Test Access Port (TAP) Std., accommodates bit-wide configuration. The sysCONFIG

port allows byte-wide configuration of the SRAM configuration memory. When programming the E2CMOS memory,

only the 1149.1 TAP can be used.

Configuration and programming done through the 1149.1 Test Access Port (TAP) supports both the IEEE Std.

1149.1 Boundary Scan TAP specification and the IEEE Std. 1532 In-System Configuration specification. To configure or program the device using the 1149.1 TAP the device must be in the ISP mode. To configure the SRAM memory using the sysCONFIG Port, the device must be in the sysCONFIG mode. Upon power-up, the device’s SRAM

memory can be configured either from the E2CMOS memory or from an external source through the sysCONFIG

mode. Additionally, the SRAM can be re-configured from the E2CMOS memory by executing a “REFRESH.” See

TN1026, ispXP Configuration Usage Guidelines, for more in depth information on the different programming

modes, timing and wake-up.

Figure 21. ispXP Block Diagram

ISP 1149.1 TAP Port

sysCONFIG Peripheral Port

Port

ISP

BACKGND

1532

sysCONFIG

Mode

Configuration

in milliseconds

Programming

in seconds

Power-up

E2CMOS

Memory Space

Refresh

SRAM

Memory Space

Download in

microseconds

Memory Space

Supports IEEE 1149.1 Boundary Scan Testability

All ispXPGA devices have boundary scan cells and supports the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic

notes. Internal boundary scan registers are linked internally, allowing test data to be shifted in and loaded directly

onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be

linked into a board-level serial scan path for more board level testing.

Security Scheme

A programmable security scheme is provided on the ispXPGA devices as a deterrent to unauthorized copying of

the array configuration patterns. Once programmed, the security scheme prevents read-back of the programmed

19

�Lattice Semiconductor

ispXPGA Family Data Sheet

pattern by a device programmer, securing proprietary designs from competitors. The entire device must be erased

in order to erase the security scheme.

Density Shifting

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

The ispXPGA family has been designed to ensure that different density devices in the same package have the

same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from

lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted

for a high-density device to a lower density device. However, the exact details of the final resource utilization will

impact the likely success in each case.

Temperature Sensing Diode

The built-in temperature-sensing diodes allow junction temperature to be measured during device operation. A pair

of pins (DXp and DXn) are dedicated for monitoring device junction temperature. The measurement is done by

forcing 10 µA and 100 µA current in the forward direction, and then measuring the resulting voltage. The voltage

decreases with increasing temperature at approximately 1.64 mV/°C. A typical device with a 85°C junction temperature will measure approximately 593 mV.

The temperature-sensing diode works for the entire operating range as shown in Figure 22 - Sensing Diode Voltage-Temperature Relationship. Refer to the Lattice Thermal Management document for thermal coefficients. Also

refer to TN1043, Power Estimation in ispXPGA Devices.

Figure 22. Sensing Diode Voltage-Temperature Relationship

0.85

0.80

100 uA

10 uA

0.75

Voltage

0.70

0.65

0.60

0.55

0.50

-50

-25

0

25

50

75

Junction Temperature (°C)

20

100

125

�Lattice Semiconductor

ispXPGA Family Data Sheet

Absolute Maximum Ratings1, 2, 3

1.8V

2.5V/3.3V

Supply Voltage (VCC) . . . . . . . . . . . . . . . . . . . . . . -0.5 to 2.5V . . . . . . . . . .-0.5 to 5.5V

PLL Supply Voltage (VCCP) . . . . . . . . . . . . . . . . . -0.5 to 2.5V . . . . . . . . . .-0.5 to 5.5V

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Output Supply Voltage (VCCO) . . . . . . . . . . . . . . . -0.5 to 4.5V . . . . . . . . . .-0.5 to 4.5V

IEEE 1149.1 TAP Supply Voltage (VCCJ) . . . . . . . -0.5 to 4.5V . . . . . . . . . .-0.5 to 4.5V

Input Voltage Applied4, 5 . . . . . . . . . . . . . . . . . . . . -0.5 to 5.5V . . . . . . . . . .-0.5 to 5.5V

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . -65 to 150C. . . . . . . . . -65 to 150C

Junction Temperature (TJ) with Power Applied . . -55 to 150C. . . . . . . . . -55 to 150C

1. Stress above those listed under the “Absolute Maximum Ratings” may cause permanent damage to the device. Functional

operation of the device at these or any other conditions above those indicated in the operational sections of this specification

is not implied (while programming, following the programming specifications).

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2V to (VIH (MAX) + 2) volts not to exceed 6V is permitted for a duration of 3.6V is allowed.

Recommended Operating Conditions

Symbol

VCC

Min

Max

Units

Supply Voltage for 1.8V device1

Parameter

1.65

1.95

V

Supply Voltage for 2.5V device

2.3

2.7

V

Supply Voltage for 3.3V device

3.0

3.6

V

1.65

1.95

V

2.3

2.7

V

Supply Voltage for PLL and sysHSI blocks, 1.8V devices

VCCP

VCCJ

1

Supply Voltage for PLL and sysHSI blocks, 2.5V devices

Supply Voltage for PLL and sysHSI blocks, 3.3V devices

3.0

3.6

V

Supply Voltage for IEEE 1149.1 Test Access Port for LVCMOS 1.8V

1.65

1.95

V

Supply Voltage for IEEE 1149.1 Test Access Port for LVCMOS 2.5V

2.3

2.7

V

Supply Voltage for IEEE 1149.1 Test Access Port for LVCMOS 3.3V

3.0

3.6

V

TJ (COM)

Junction Temperature Commercial Operation

TJ (IND)

Junction Temperature Industrial Operation

0

85

C

-40

105

C

Min

Max

Units

1,000

—

Cycles

1. sysHSI specification is valid for VCC and VCCP = 1.7V to 1.9V.

E2CMOS Erase Reprogram Specifications

Parameter

Erase/Reprogram Cycle1

1. Valid over commercial temperature range.

Hot Socketing Characteristics1, 2, 3, 4

Symbol

IDK

Parameter

Condition

Input or Tristated I/O Leakage Current 0 ð VIN ð 3.0V

Min

Typ

Max

Units

—

+/-50

+/-800

A

1. Insensitive to sequence of VCC and VCCO when VCCO ð 1.0V. For VCCO > 1.0V, VCC min must be present. However, assumes monotonic

rise/fall rates for VCC and VCCO, provided (VIN - VCCO) ð 3.6V.

2. LVTTL, LVCMOS only.

3. 0 < VCC ð VCC (MAX), 0 < VCCO ð VCCO (MAX).

4. IDK is additive to IPU, IPD or IBH. Device defaults to pull-up until non-volatile cells are active.

21

�Lattice Semiconductor

ispXPGA Family Data Sheet

DC Electrical Characteristics

Over Recommended Operating Conditions

Symbol

IIL, IIH1

Parameter

Input or I/O Low Leakage

Min

Typ

Max

Units

0 ð VIN < (VCCO - 0.2V)

Condition

—

—

10

A

—

300

A

—

IIH2

3.6V < VIN ð 5.5V and

3.0V ð VCCO ð 3.6V

—

—

3

mA

IPU

I/O Active Pull-up Current

0 ð VIN ð 0.7 VCCO

-30

—

-150

A

IPD

I/O Active Pull-down Current

VIL (MAX) ð VIN ð VIH (MAX)

30

—

150

A

IBHLS

Bus Hold Low Sustaining Current VIN = VIL (MAX)

30

—

—

A

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

(VCCO - 0.2V) ð VIN ð 3.6V

Input High Leakage Current

IBHHS

Bus Hold High Sustaining Current VIN = 0.7 VCCO

-30

—

—

A

IBHLO

Bus Hold Low Overdrive Current

—

—

150

A

IBHHO

Bus Hold High Overdrive Current 0 ð VIN ð VIH (MAX)

—

—

-150

A

VBHT

Bus Hold Trip Points

VCCO * 0.35

—

VCCO * 0.65

V

C1

I/O Capacitance3

C2

Clock Capacitance3

C3

Global Input Capacitance3

0 ð VIN ð VIH (MAX)

VCCO = 3.3V, 2.5V, 1.8V

—

VCC = 1.8V, VIO = 0 to VIH (MAX)

—

VCCO = 3.3V, 2.5V, 1.8V

—

VCC = 1.8V, VIO = 0 to VIH (MAX)

—

VCCO = 3.3V, 2.5V, 1.8V

—

VCC = 1.8V, VIO = 0 to VIH (MAX)

—

8

8

6

—

—

—

—

—

—

pf

pf

pf

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not

measured with the output driver active. Bus maintenance circuits are disabled.

2. 5V tolerant inputs and I/Os should be placed in banks where 3.0V ð VCCO ð 3.6V. The JTAG and sysCONFIG ports are not included for the

5V tolerant interface.

3. TA = 25C, f = 1.0MHz.

22

�Lattice Semiconductor

ispXPGA Family Data Sheet

Supply Current

Over Recommended Operating Conditions

Symbol

Parameter

Device

Condition

Typ.

Max.

Units

—

60

—

mA

VCC = 2.5V

—

60

—

mA

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

LFX125

Min.

VCC = 3.3V

LFX200

ICC1, 2

Standby Core Operating Power Supply Current

LFX500

LFX1200

ICCO3

ICCP4

ICCJ5

Standby Output Power Supply Current

Standby PLL Operating Supply Current

Standby IEEE 1149.1 TAP Power Supply Current

VCC = 1.8V

—

40

—

mA

VCC = 3.3V

—

70

—

mA

VCC = 2.5V

—

70

—

mA

VCC = 1.8V

—

50

—

mA

VCC = 3.3V

—

120

—

mA

VCC = 2.5V

—

120

—

mA

VCC = 1.8V

—

100

—

mA

VCC = 3.3V

—

220

—

mA

VCC = 2.5V

—

220

—

mA

VCC = 1.8V

—

200

—

mA

VCCO = 3.3V

—

2.0

—

mA

VCCO = 2.5V

—

2.0

—

mA

VCCO = 1.8V

—

2.0

—

mA

VCCO = 1.5V

—

2.0

—

mA

VCCP = 3.3V

—

17.0

—

mA

VCCP = 2.5V

—

17.0

—

mA

VCCP = 1.8V

—

15.0

—

mA

VCCJ = 3.3V

—

2.0

—

mA

VCCJ = 2.5V

—

1.5

—

mA

VCCJ = 1.8V

—

1.0

—

mA

1. TA = 25°C, frequency = 1.0 MHz, device configured with 16-bit counters.

2. ICC varies with specific device configuration and operating frequency. For more accurate power calculation, see TN1043, Power Estimation

in ispXPGA Devices.

3. TA = 25°C, per bank, no DC load, frequency = 0 MHz.

4. TA = 25°C, per PLL, frequency = 10 MHz.

5. TA = 25°C

23

�Lattice Semiconductor

ispXPGA Family Data Sheet

sysIO Recommended Operating Conditions

VCCO (V)1

VREF (V)

Standard

Min.

Typ.

Max.

Min.

Typ.

Max.

LVCMOS 3.3

3.0

3.3

3.6

-

-

-

LVCMOS 2.5

2.3

2.5

2.7

-

-

-

2

1.65

1.8

1.95

-

-

-

LVTTL

3.0

3.3

3.6

-

-

-

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

LVCMOS 1.8

PCI 3.3

3.0

3.3

3.6

-

-

-

AGP-1X

3.15

3.3

3.45

-

-

-

SSTL 2

2.3

2.5

2.7

1.15

1.25

1.35

SSTL 3

3.0

3.3

3.6

1.3

1.5

1.7

CTT 3.3

3.0

3.3

3.6

1.35

1.5

1.65

CTT 2.5

2.3

2.5

2.7

1.35

1.5

1.65

HSTL Class I

1.4

1.5

1.6

0.68

0.75

0.9

HSTL Class III

1.4

1.5

1.6

-

0.9

-

GTL+

-

-

-

0.882

1.0

1.122

LVDS

2.3

2.5

2.7

-

-

-

LVPECL

3.0

3.3

3.6

-

-

-

BLVDS

2.3

2.5

2.7

-

-

-

1. Inputs independent of VCCO.

2. Design tool default setting.

24

�Lattice Semiconductor

ispXPGA Family Data Sheet

sysIO DC Electrical Characteristics

Over Recommended Operating Conditions

VIH

VIL

Standard

Max. (V)

Min. (V)

Max. (V)

-0.3

0.8

2.0

5.5

VOL

Max. (V)

VOH

Min. (V)

0.4

VCCO - 0.4

IOL (mA)

IOH (mA)

20, 16, 12, -20, -16,-12,

8, 5.33, 4 -8, -5.33, -4

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

LVCMOS 3.3

Min. (V)

LVCMOS 2.5

-0.3

0.7

0.68

LVCMOS 1.81

-0.3

LVTTL

-0.3

PCI 3.3

-0.3

AGP-1X

-0.3

1.7

3

1.07

0.2

VCCO - 0.2

0.1

-0.1

0.4

VCCO - 0.4

16, 12, 8,

5.33, 4

-16, -12, -8,

-5.33, -4

0.2

VCCO - 0.2

0.1

-0.1

0.4

VCCO - 0.4

12, 81, 5.33,

4

-12, -81,

-5.33, -4

0.2

VCCO - 0.2

0.1

-0.1

0.4

VCCO - 0.4

4

-4

0.2

VCCO - 0.2

0.1

-0.1

5.5

0.1 VCCO

0.9 VCCO

1.5

-0.5

3.6

0.1 VCCO

0.9 VCCO

1.5

-0.5

3.6

3

0.35VCC

0.65VCC

0.8

2.0

1.083

1.53

0.3VCCO

0.5 VCCO

1.083

1.53

0.3 VCCO

0.5 VCCO

3.6

5.5

SSTL 3 Class I

-0.3

VREF - 0.2

VREF + 0.2

3.6

0.7

VCCO - 1.1

8

-8

SSTL 3 Class II

-0.3

VREF - 0.2

VREF + 0.2

3.6

0.5

VCCO - 0.9

16

-16

SSTL 2 Class I

-0.3

VREF - 0.18 VREF + 0.18

3.6

0.54

VCCO - 0.62

7.6

-7.6

SSTL 2 Class II

-0.3

VREF - 0.18 VREF + 0.18

3.6

0.35

VCCO - 0.43

15.2

-15.2

CTT 3.3

-0.3

VREF - 0.2

VREF + 0.2

3.6

VREF - 0.4

VREF + 0.4

8

-8

CTT 2.5

-0.3

VREF - 0.2

VREF + 0.2

3.6

VREF - 0.4

VREF + 0.4

8

-8

HSTL Class I

-0.3

VREF - 0.1

VREF + 0.1

3.6

0.4

VCCO - 0.4

8

-8

HSTL Class III

-0.3

VREF - 0.1

VREF + 0.1

3.6

0.4

VCCO - 0.4

24

-8

GTL+

-0.3

VREF - 0.2

VREF + 0.2

3.6

0.6

N/A

36

N/A

1. Design tool default setting.

2. The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the

I/O bank, as shown in the logic signals connection table, shall not exceed n*8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank

3. Applicable for ispXPGA B devices.

25

�Lattice Semiconductor

ispXPGA Family Data Sheet

sysIO Differential Standards DC Electrical Characteristics1

Parameter

Description

Test Conditions

Min.

Typ.

Max.

LVDS2

VINP, VINM

Input voltage

VTHD

Differential input threshold

0.2V ð VCM ð 1.8V

0V

—

2.4V

+/-100mV

—

—

—

—

+/-10uA

Input current

Power on

Output High Voltage for VOP or VOM

RT = 100 Ohm

—

1.38V

1.60V

VOL

Output Low Voltage for VOP or VOM

RT = 100 Ohm

0.9V

1.03V

—

VOD

Output Voltage Differential

|VOP - VOM|, RT = 100 ohm

250mV

350mV

450mV

VOD

Change in VOD between high and low

—

—

50mV

VOS

Output Voltage Offset

1.125V

1.25V

1.375V

VOS

Change in VOS between H and L

—

—

50mV

IOSD

Output short circuit current

—

—

24mA

0V

—

2.4V

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

IIN

VOH

|VOP + VOM|/2, RT = 100 ohm

VOD = 0V Driver outputs

shorted

BLVDS1

VINP, VINM

Input voltage

VTHD

Differential input threshold

0.2V ð VCM ð 1.8V

+/-100mV

—

—

IIN

Input current

Power on

—

—

+/-10uA

VOH

Output High Voltage for VOP or VOM

RT = 27

—

1.4V

1.80V

VOL

Output Low Voltage for VOP or VOM

RT = 27

0.95V

1.1V

—

VOD

Output Voltage Differential

|VOP - VOM|, RT = 27

240mV

300mV

460mV

VOD

Change in VOD Between H and L

VOS

Output Voltage Offset

VOS

Change in VOS Between H and L

IOSD

Output Short Circuit Current

27mV

|VOP + VOM| /2, RT = 27

1.1V

1.3V

1.5V

27mV

VOD = 0. Driver Outputs

Shorted.

36mA

65mA

1. Refer to TN1000, sysIO Usage Guidelines for Lattice Devices.

2. VOP and VOM are the two outputs of the LVDS/BLVDS output buffer.

LVPECL1

DC

Parameter

Parameter Description

Min.

VCCO

Max.

Min.

3.0

Max.

Min.

3.3

Max.

Units

3.6

V

VIH

Input Voltage High

1.49

2.72

1.49

2.72

1.49

2.72

V

VIL

Input Voltage Low

0.86

2.125

0.86

2.125

0.86

2.125

V

VOH

Output Voltage High

1.8

2.11

1.92

2.28

2.13

2.41

V

VOL

Output Voltage Low

0.96

1.27

1.06

1.43

1.3

1.57

V

VDIFF2

Differential Input threshold

0.3

—

0.3

—

0.3

—

V

1. These values are valid at the output of the source termination pack as shown above with 100-ohm differential load only (see Figure 23).

The VOH levels are 200mV below the standard LVPECL levels and are compatible with devices tolerant of the lower common mode ranges.

2. Valid for 0.2 ð VCM ð 1.8V.

26

�Lattice Semiconductor

ispXPGA Family Data Sheet

Figure 23. LVPECL Driver with Three Resistor Pack

ispXPLD Emulated

LVPECL Buffer

1/4 of Bourns P/N

CAT 16-PC4F12

A

Zo

to LVPECL

differential

receiver

RD

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

RT=100

Rs

Rs

Zo

ispXPGA 125B/C & ispXPGA 125EB/EC External Switching Characteristics

Over Recommended Operating Conditions

-51

Parameter

Description

Conditions

PIO Output Register

-4

-3

Min.

Max.

Min.

Max.

Min.

Max. Units

—

5.3

—

5.7

—

6.6

ns

tCO

Global Clock Input to

Output

tS

Global Clock Input Setup

PIO Input Register without input

delay

-1.9

—

-1.8

—

-1.5

—

ns

tH

Global Clock Input Hold

PIO Input Register without input

delay

2.7

—

2.9

—

3.3

—

ns

tSINDLY

Global Clock Input Setup

PIO Input Register with input delay

3.1

—

3.3

—

3.8

—

ns

tHINDLY

Global Clock Input Hold

PIO Input Register with input delay

0.0

—

0.0

—

0.0

—

tCOPLL

Global Clock Input to

Output

PIO Output Register using PLL

without delay

—

3.6

—

3.9

—

4.5

ns

tSPLL

Global Clock Input Setup

PIO Input Register without input

delay using PLL without delay

0

—

0.1

—

0.3

—

ns

tHPLL

Global Clock Input Hold

PIO Input Register without input

delay using PLL without delay

0.9

—

1.0

—

1.2

—

ns

tSINDLYPLL Global Clock Input Setup

PIO Input Register with input delay

using PLL without delay

5.1

—

5.5

—

6.3

—

ns

tHINDLYPLL Global Clock Input Hold

PIO Input Register with input delay

using PLL without delay

-3.0

—

-2.8

—

-2.4

—

ns

1. Only available for ispXPGA 125B and ispXPGA 125EB (2.5V/3.3V) devices.

27

Timing v.0.3

�Lattice Semiconductor

ispXPGA Family Data Sheet

ispXPGA 125B/C & ispXPGA 125EB/EC PFU Timing Parameters

Over Recommended Operating Conditions

-51

Parameter

Min.

Description

-4

Max.

Min.

-3

Max.

Min.

Max.

Units

SE

L

D E

IS C

C T

O D

N E

TI VI

N C

U E

ED S

Functional Delays

LUTs

tLUT4

4-Input LUT Delay

—

0.41

—

0.44

—

0.51

ns

tLUT5

5-Input LUT Delay

—

0.73

—

0.79

—

0.91

ns

tLUT6

6-Input LUT Delay

—

0.86

—

0.93

—

1.07

ns

—

-0.62

—

-0.53

—

ns

Shift Register (LUT)

tLSR_S

Shift Register Setup Time

-0.64

tLSR_H

Shift Register Hold Time

0.61

—

0.63

—

0.72

—

ns

tLSR_CO

Shift Register Clock to Output Delay

—

0.70

—

0.75

—

0.86

ns

MC (Macro Cell) Carry In to MC Carry Out Delay (Ripple)

—

0.08

—

0.09

—

0.10

ns

Arithmetic Functions

tLCTHRUR

tLCTHRUL

2

MC Carry In to MC Carry Out Delay (Look Ahead)

—

0.05

—

0.05

—

0.06

ns

tLSTHRU

MC Sum In to MC Sum Out Delay

—

0.42

—

0.45

—

0.52

ns

tLSINCOUT

MC Sum In to MC Carry Out Delay

—

0.29

—

0.31

—

0.36

ns

tLCINSOUTR

MC Carry In to MC Sum Out Delay (Ripple)

—

0.36

—

0.39

—

0.45

ns

tLCINSOUTL

MC Carry In to MC Sum Out Delay (Look Ahead)

—

0.26

—

0.28

—

0.32

ns

PFU Feed-Thru Delay

—

0.15

—

0.16

—

0.18

ns

Feed-thru

tLFT

Distributed RAM

tLRAM_CO

Clock to RAM Output

—

1.24

—

1.33

—

1.53

ns

tLRAMAD_S

Address Setup Time

-0.41

—

-0.40

—

-0.34

—

ns

tLRAMD_S

Data Setup Time

0.21

—

0.22

—

0.25

—

ns

tLRAMWE_S

Write Enable Setup Time

0.45

—

0.46

—

0.53

—

ns

tLRAMAD_H

Address Hold Time

0.58

—

0.60

—

0.69

—

ns

tLRAMD_H

Data Hold Time

0.11

—

0.11

—

0.13

—

ns

tLRAMWE_H

Write Enable Hold Time

0.12

—

0.12

—

0.14

—

ns

tLRAMCPW

Clock Pulse Width (High or Low)

2.91

—

3.00

—

3.45

—

ns

tLRAMADO

Address to Output Delay

—

0.86

—

0.93

—

1.07

ns

—

0.58

—

0.62

—

0.71

ns

Register/Latch Delays

Registers

tL_CO

Register Clock to Output Delay

tL_S

Register Setup Time (Data before Clock)

0.14

—

0.14

—

0.16

—

ns

tL_H

Register Hold Time (Data after Clock)

-0.12

—

-0.12

—

-0.10

—

ns

tLCE_S

Register Clock Enable Setup Time

-0.11

—

-0.11

—

-0.09

—

ns

tLCE_H

Register Clock Enable Hold Time

0.11

—

0.11

—

0.13

—

ns

—

0.09

—

0.10

—

0.12

ns

Latches

tL_GO

Latch Gate to Output Delay

tLL_S

Latch Setup Time

0.14

—

0.14

—

0.16

—

ns

tLL_H

Latch Hold Time

-0.12

—

-0.12

—

-0.10

—

ns

tLLPD