LTC6902

Multiphase Oscillator

with Spread Spectrum

Frequency Modulation

U

FEATURES

■

■

■

■

■

■

■

■

■

■

■

■

2-, 3- or 4-Phase Outputs

Optional Spread Spectrum Frequency Modulation

for Improved EMC Performance

5kHz to 20MHz Frequency Range

One External Resistor Sets the Frequency

One External Resistor Sets Percent Frequency

Spreading

400µA Typical Supply Current, VS = 3V, 1MHz

Frequency Error ≤1.5% Max, 5kHz to 10MHz

(TA = 25°C)

Frequency Error ≤ 2% Max, 5kHz to 10MHz

(TA = 0°C to 70°C)

±40ppm/°C Temperature Stability

Fast Start-Up Time: 50µs to 1.5ms

100Ω CMOS Output Driver

Operates from a Single 2.7V to 5.5V Supply

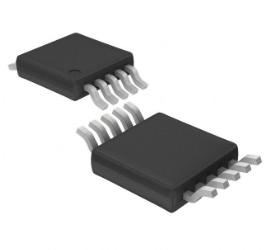

Available in 10-Lead MS Package

U

APPLICATIO S

■

■

■

■

Switching Power Supply Clock Reference

Portable and Battery-Powered Equipment

PDAs

Cell Phones

Clocking Switched Capacitor Filters

The LTC6902’s master oscillator is controlled by the RSET

resistor and has a range of 100kHz and 20MHz. In order

to accommodate a wider output frequency range, a programmable divider (divide by 1, 10 or 100) is included.

The integrated programmable multiphase circuit provides either 2-, 3- or 4-phase waveforms.

The LTC6902’s SSFM capability modulates the oscillator’s

frequency by a pseudorandom noise (PRN) signal to

spread the oscillator’s energy over a wide frequency band.

This spreading decreases the peak electromagnetic radiation level and improves electromagnetic compatibility

(EMC) performance. The amount of frequency spreading

is programmable by a single additional external resistor

(RMOD) and is disabled by grounding the MOD pin.

, LTC and LT are registered trademarks of Linear Technology Corporation.

U

■

The LTC®6902 is a precision, low power and easy-to-use

oscillator that provides multiphase outputs in a small

package. The oscillator frequency is set by a single external resistor (RSET). The LTC6902 also provides an optional

spread spectrum frequency modulation (SSFM) capability

that can be activated and controlled by an additional

external resistor (RMOD).

TYPICAL APPLICATIO

Output Frequency Spectrum With and Without SSFM

500kHz, 4-Phase Clock with 20% Frequency Spreading

5V

0.1µF

RMOD 10k

RSET 10k

LTC6902

OPEN

V+

SET

DIV

MOD

PH

GND

OUT1 OUT4

OUT4

OUT2 OUT3

OUT3

OUT2

6902 TA01

OUT1

0

RELATIVE AMPLITUDE (dBm)

■

DESCRIPTIO

OUTPUT

SPECTRUM

WITH SSFM

DISABLED

–20

OUTPUT

SPECTRUM

WITH 20%

SPREADING

–40

–60

–80

–100

400

550

450

500

FREQUENCY (kHz)

600

6902 TA02

6902f

1

�LTC6902

W W

W

AXI U

U

ABSOLUTE

RATI GS

U

U

W

PACKAGE/ORDER I FOR ATIO

(Note 1)

Supply Voltage (V +) to GND ........................– 0.3V to 6V

Voltage On Any Pin

(Referred to GND) ......................... – 0.3V to (V + + 0.3V)

Operating Temperature Range (Note 9)

LTC6902C .......................................... – 40°C to 85°C

LTC6902I ............................................ – 40°C to 85°C

Specified Temperature Range (Note 10)

LTC6902C .......................................... – 40°C to 85°C

LTC6902I ............................................ – 40°C to 85°C

Storage Temperature Range ................. – 65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

ORDER

PART NUMBER

TOP VIEW

V+

DIV

PH

OUT1

OUT2

1

2

3

4

5

10

9

8

7

6

SET

MOD

GND

OUT4

OUT3

LTC6902CMS

LTC6902IMS

MS PACKAGE

10-LEAD PLASTIC MSOP

MS PART MARKING

TJMAX = 150°C, θJA = 250°C/W

LTK2

LTK3

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. V+ = 2.7V to 5.5V, RL= 5k, CL = 5pF, Pin 3 (PH) = 0V (2-phase, M = 1)

unless otherwise specified. Pin 9 (MOD) is at 0V unless otherwise specified. RSET is defined as a resistor connected from the SET pin

to the V+ pin. RMOD is defined as a resistor connected from the MOD pin to the V+ pin.

SYMBOL

∆fOUT

PARAMETER

CONDITIONS

Frequency Accuracy (Notes 2, 3)

V+ = 5V

V+ = 2.7V

5kHz ≤ fOUT ≤ 10MHz

1kHz ≤ fOUT ≤ 5kHz

10MHz ≤ fOUT ≤ 20MHz

5kHz ≤ fOUT ≤ 10MHz, LTC6902C

5kHz < fOUT ≤ 10MHz, LTC6902I

5kHz ≤ fOUT ≤ 10MHz

1kHz ≤ fOUT ≤ 5kHz

5kHz ≤ fOUT ≤ 10MHz, LTC6902C

5kHz ≤ fOUT ≤ 10MHz, LTC6902I

MIN

●

●

●

TYP

MAX

UNITS

±0.5

±2.0

±3.0

±1.5

%

%

%

%

%

±0.5

±2.0

●

●

RSET

Frequency Setting Resistor Range

∆fOUT < 1.5%, V + = 5V

∆fOUT < 1.5%, V + = 2.7V

●

●

∆fOUT/∆T

Frequency Drift Over Temperature

(Note 3)

RSET = 63.2k

●

±0.004

∆fOUT/∆V

Frequency Drift Over Supply (Note 3) V+ = 2.7V to 5V, RSET = 63.2k

●

0.04

Timing Jitter (Note 4)

20

20

20k ≤ RSET ≤ 400k

Pin 2 = V + (N = 100)

Pin 2 = Open (N = 10)

Pin 2 = 0V (N = 1)

Long-Term Stability of

Output Frequency

Duty Cycle (Note 5)

±4.0

±2.0

±2.5

±1.5

±2.0

±2.5

%

%

%

%

400

400

kΩ

kΩ

%/°C

0.12

%/V

0.1

0.2

0.6

%

%

%

300

ppm/√kHr

Pin 2 = V + or Open (N = 100 or 10)

Pin 3 = 0V (2-Phase, M = 1)

Pin 3 = Open (3-Phase, M = 3)

Pin 3 = V + (4-Phase, M = 4)

●

●

●

49.0

32.3

49.0

50.0

33.3

50.0

51.0

34.3

51.0

%

%

%

Pin 2 = 0V (N = 1)

Pin 3 = 0V (2-Phase, M = 1)

Pin 3 = Open (3-Phase, M = 3)

Pin 3 = V + (4-Phase, M = 4)

●

●

●

45.0

32.3

49.0

50.0

33.3

50.0

55.0

34.3

51.0

%

%

%

6902f

2

�LTC6902

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at TA = 25°C. V+ = 2.7V to 5.5V, RL= 5k, CL = 5pF, Pin 3 (PH) = 0V (2-phase, M = 1)

unless otherwise specified. Pin 9 (MOD) is at 0V unless otherwise specified. RSET is defined as a resistor connected from the SET pin

to the V+ pin. RMOD is defined as a resistor connected from the MOD pin to the V+ pin.

SYMBOL

PARAMETER

V+

Operating Supply Range

IS

Power Supply Current

CONDITIONS

MIN

●

RSET = 400k, RL = ∞, Pin 2 = V + (N = 100), fOUT = 5kHz

V + = 5V

2.7

●

●

2.35

1.40

3.50

1.80

mA

mA

RSET = 400k, RL = ∞, Pin 2 = V + (N = 100), RMOD = 800k

V + = 5V

●

●

V + = 2.7V

0.45

0.34

0.63

0.50

mA

mA

RSET = 20k, RL = ∞, Pin 2 = 0V (N = 1), RMOD = 40k

V + = 5V

V + = 2.7V

2.50

1.40

3.60

1.90

mA

mA

●

●

● V+ – 0.4

VIL_DIV

Low Level DIV Input Voltage

●

VIL_PH

Low Level PH Input Voltage

IPH

VOH

VOL

tr

tf

PH Input Currrent (Note 6)

Pin 2 = V +,

V+

= 5V

Pin 2 = 0V, V + = 5V

Low Level Output Voltage (Note 6)

(OUT1, OUT2, OUT3, OUT4)

Output Rise Time (Note 7)

(OUT1, OUT2, OUT3, OUT4)

Output Fall Time (Note 7)

(OUT1, OUT2, OUT3, OUT4)

Spread Spectrum Frequency

Modulation Spreading Percentage

(Downspread from Maximum

Frequency)

Percent = 100 • (fMAX – fMIN)/fMAX

(Note 8)

●

●

–4

V

2

–2

0.4

V

4

µA

µA

● V+ – 0.4

V

●

Pin 3 = V+, V+ = 5V

Pin 3 = 0V, V+ = 5V

High Level Output Voltage (Note 6)

(OUT1, OUT2, OUT3, OUT4)

V

mA

mA

High Level DIV Input Voltage

High Level PH Input Voltage

5.5

0.55

0.50

VIH_DIV

VIH_PH

UNITS

0.35

0.32

RSET = 20k, RL = ∞, Pin 2 = 0V (N = 1), fOUT = 10MHz

V + = 5V

V + = 2.7V

DIV Input Current (Note 6)

MAX

●

●

V + = 2.7V

IDIV

TYP

●

●

–4

2

–2

0.4

V

4

µA

µA

V + = 5V

IOH = – 1mA

IOH = – 4mA

●

●

4.75

4.40

4.90

4.70

V

V

V + = 2.7V

IOH = – 1mA

IOH = – 4mA

●

●

2.35

1.85

2.6

2.2

V

V

V + = 5V

IOL = 1mA

IOL = 4mA

●

●

0.05

0.20

0.15

0.40

V

V

V + = 2.7V

IOL = 1mA

IOL = 4mA

●

●

0.1

0.4

0.3

0.7

V

V

V + = 5V

Pin 2 = V+ or Open (N = 100 or N = 10)

Pin 2 = 0V (N = 1)

14

7

ns

ns

V + = 2.7V

Pin 2 = V+ or Open (N = 100 or N = 10)

Pin 2 = 0V (N = 1)

19

11

ns

ns

V + = 5V

Pin 2 = V+ or Open (N = 100 or N = 10)

Pin 2 = 0V (N = 1)

13

6

ns

ns

V + = 2.7V

Pin 2 = V+ or Open (N = 100 or N = 10)

Pin 2 = 0V (N = 1)

19

10

ns

ns

V + = 5V, N = 10, RSET = 20k, RMOD = 10k

V + = 5V, N = 10, RSET = 20k, RMOD = 40k

V + = 2.7V, N = 10, RSET = 20k, RMOD = 10k

V + = 2.7V, N = 10, RSET = 20k, RMOD = 40k

●

●

●

●

35

7.5

35

7.5

40

10

40

10

45.0

12.5

45.0

12.5

%

%

%

%

6902f

3

�LTC6902

ELECTRICAL CHARACTERISTICS

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

Note 2: Frequencies near 100kHz and 1MHz may be generated using two

different values of RSET (see Applications Information). For these

frequencies, the error is specified under the following assumption:

20k < RSET ≤ 400k for 5kHz ≤ fOUT ≤ 10MHz.

Note 3: Frequency accuracy is defined as the deviation from the fOUT

equation.

Note 4: Jitter is the ratio of the peak-to-peak distribution of the period to

the mean of the period. This specification is based on characterization and

is not 100% tested.

Note 5: Guaranteed by 5V test.

Note 6: To conform with the Logic IC Standard convention, current out of

a pin is arbitrarily given as a negative value.

Note 7: Output rise and fall times are measured between the 10% and the

90% power supply levels with no output loading. These specifications are

based on characterization.

Note 8: fMAX is defined as the highest frequency excursion and is equal to

the fOUT frequency set by the RSET resistor. fMIN is the lowest frequency

excursion.

Note 9: The LTC6902CMS and LTC6902IMS are guaranteed functional

over the operating temperature range of –40°C to 85°C.

Note 10: The LTC6902CMS is guaranteed to meet 0°C to 70°C specifications and are designed, characterized and expected to meet the specified

performance from –40°C to 85°C but is not tested or QA sampled at these

temperatures. The LTC6902IMS is guaranteed to meet specified performance from –40°C to 85°C.

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Frequency Variation Over

Temperature

Frequency Variation vs RSET

4

1.00

TA = 25°C

GUARANTEED LIMITS APPLY OVER

20kΩ ≤ RSET ≤ 400kΩ

2

0.75

VARIATION (%)

0

–1

0.9

0.8

0.50

TYPICAL HIGH

1

1.0

RSET = 63.4k

÷1 OR ÷10 OR ÷100

TYPICAL LOW

0.25

0

TYPICAL

LOW

–0.25

–2

÷1, VA = 5V

0.7

TYPICAL

HIGH

JITTER (%P-P)

3

VARIATION (%)

Peak-to-Peak Jitter vs Output

Frequency (M = 1, 2-Phase Mode)

0.6

÷1, VA = 3V

0.5

0.4

0.3

–0.50

÷10

0.2

–3

–0.75

–4

1k

10k

100k

RSET (Ω)

–1.00

–40

1M

÷100

0.1

–20

0

20

40

60

TEMPERATURE (°C)

6902 G01

0

80

1k

10k

100k

1M

OUTPUT FREQUENCY (Hz)

6902 G02

Supply Current vs Output

Frequency [SSFM Disabled,

2-Phase Mode (M = 1)]

10M

6902 G03

Output Resistance

vs Supply Voltage

3.5

140

TA = 25°C

OUTPUT RESISTANCE (Ω)

SUPPLY CURRENT (mA)

3.0

2.5

÷1, 5V

2.0

÷10, 5V

1.5

÷100, 5V

1.0

0.5

0

÷100, 3V ÷10, 3V

1k

120

OUTPUT SOURCING CURRENT

100

80

60

÷1, 3V

10k

100k

1M

OUTPUT FREQUENCY (Hz)

OUTPUT SINKING CURRENT

10M

6902 G04

40

2.5

3.0

3.5 4.0 4.5

5.0

SUPPLY VOLTAGE (V)

5.5

6.0

6902 G05

6902f

4

�LTC6902

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Output Operating at 10MHz,

VS = 3V

Output Operating at 20MHz,

VS = 5V

V + = 5V, RSET = 10k, CL = 10pF

V + = 3V, RSET = 20k, CL = 10pF

1V/DIV

1V/DIV

0V

0V

69012 G06

12.5ns/DIV

25ns/DIV

69012 G07

U

QUICK DESIG GUIDE

V+

RMOD

0.1µF

RSET

SET

DIV

DIV

MOD

PH

PH

GND

10MHz 20kΩ

•

; 5kHz ≤ fOUT ≤ 20MHz

N • M RSET

R

Spreading Percentage = 20 • SET

RMOD

fOUT =

LTC6902

V+

OUT1 OUT4

OUT4

OUT2 OUT3

OUT3

OUT2

6902 F01

OUT1

Figure 1. Typical Application with Design Equation

Step 1. Select Multiphase Mode, Setting M

DIVIDER SETTING

By selecting the multiphase mode, a division parameter M

is also chosen:

N=1

Connect DIV Pin to GND

2MHz to 20MHz

N = 10

Leave DIV Open

200kHz to 2MHz

N = 100

Connect DIV Pin to V+

2-Phase: Connect PH Pin to GND

3-Phase: Leave PH Open

4-Phase: Connect PH Pin to V+

M=1

M=3

M=4

Step 2. Choosing Programmable Divider Setting N

A. For applications using spread spectrum frequency

modulation (SSFM) or applications that are constant frequency where low clock jitter is the primary specification:

FREQUENCY RANGE (fOUT • M)

< 200kHz

Note: The frequency range numbers are for a 5V supply where a 20MHz

output is the maximum frequency supported. For low supply applications

(2.7V ≤ V+ ≤ 4V), the maximum rated output frequency is 10MHz and all

of the above numbers should be halved.

B. For constant frequency applications where frequency

accuracy is the primary specification:

DIVIDER SETTING

N=1

Connect DIV Pin to GND

N = 10

Leave DIV Open

N = 100

Connect DIV Pin to V+

FREQUENCY RANGE (fOUT • M)

> 500kHz*

50kHz to 500kHz

< 50kHz

*The maximum frequency (fOUT • M) is 20MHz for 5V applications and is

10MHz for low supply applications (2.7V ≤ V+ ≤ 4V).

6902f

5

�LTC6902

U

QUICK DESIG GUIDE

Step 3. Calculating the RSET Resistor Value

Step 4. Calculating the RMOD Resistor Value

The RSET resistor, the multiphase mode and the divider

setting set the output frequency (fOUT) for constant frequency applications. For SSFM applications, the maximum frequency excursion (fMAX) is equal to fOUT.

(Note: For constant frequency applications RMOD is not

required. Disable SSFM by connecting the MOD pin to

GND)

10MHz

R SET = 20kΩ •

N • M • fOUT

100 DIV Pin = V +

N = 10 DIV Pin = Open

1 DIV Pin = 0 V

4

M = 3

1

(4 - Phase Output) PH Pin = V +

(3 - Phase Output) PH Pin = Open

(2 - Phase Output) PH Pin = 0 V

RMOD = 20 •

RSET

Spreading Percentage

where the Spreading Percentage is defined by the

following:

Spreading Percentage = 100 •

fMAX – fMIN

fMAX

where fMAX is the highest frequency excursion (set by the

RSET value calculated in Step 3) and fMIN is the lowest

frequency excursion.

Example

For a 4-phase, 250kHz clock with 40% spreading:

Connect PH Pin to V+ → Selects 4-Phase Mode, M = 4

Leave DIV Pin Open → N = 10

RSET = 20k → Sets fOUT = fMAX = 250kHz

RMOD = 10k → Sets Spreading to 40%

U

U

U

PI FU CTIO S

V+ (Pin 1): Supply Voltage ( 2.7V ≤ V+ ≤ 5.5V). The supply

should be kept free from noise and ripple. It should be

bypassed directly to a ground plane with a 0.1µF capacitor

placed as close to the pin as possible.

DIV (Pin 2): Divider Setting Input. This three-state input

selects among three divider settings determining the value

of N in the frequency equation. Pin 2 should be tied to GND

for the ÷1 setting, the highest frequency range. Floating

Pin 2, leaving it open, divides the master oscillator by 10.

Tie Pin 2 to V+ for the ÷100 setting, the lowest frequency

range. To detect a floating DIV pin, the LTC6902 places the

pin at the midsupply point with active circuitry. Therefore,

driving the DIV pin high requires sourcing approximately

2µA. Similarly, driving the DIV pin low requires sinking

2µA. When the DIV pin is floated, it should be bypassed by

a 1nF capacitor to GND or it should be surrounded by a

ground shield to prevent excessive coupling from other

PCB traces.

PH (Pin 3): Phase Setting Input. This three-state input

selects among three multiphase options. This sets the

outputs to produce 2-phase, 3-phase or 4-phase signals.

It also sets the value of M in the frequency equation. Pin 3

should be tied to GND for the 2-phase setting. This is the

highest frequency range with M set to 1. Floating Pin 3,

leaving it open, selects the 3-phase setting. This also sets

M to 3. Tie Pin 3 to V+ for the 4-phase setting. This is the

lowest frequency range as M is set to 4. To detect a floating

PH pin, the LTC6902 places the pin at the midsupply point

with active circuitry. Therefore, driving the PH pin high

requires sourcing approximately 2µA. Similarly, driving

the PH pin low requires sinking 2µA. When the PH pin is

floated, it should be bypassed by a 1nF capacitor to GND

6902f

6

�LTC6902

U

U

U

PI FU CTIO S

or it should be surrounded by a ground shield to prevent

excessive coupling from other PCB traces.

OUT1, OUT2, OUT3, OUT4 (Pins 4, 5, 6 and 7): Oscillator

Outputs. These pins can drive 5kΩ and/or 10pF loads.

Larger loads may cause inaccuracies due to supply bounce

at high frequencies.

GND (Pin 8): Ground. Should be tied to a ground plane for

best performance.

SET (Pin 10): Frequency Setting Resistor Input. The value

of the resistor (RSET) connected between Pin 10 and V+

determines the oscillator frequency. The voltage on this

pin is held at approximately 1.13V below the V+ voltage.

For best performance, use a precision metal film resistor

with a value between 10k and 2M and limit the capacitance

on this pin to less than 10pF.

MOD (Pin 9): Spread Spectrum Frequency Modulation

Setting Resistor Input. The value of the resistor (RMOD)

connected between Pin 9 and V+ determines the amount

of frequency modulation. The output frequency is always

modulated down from the frequency set by the RSET resistor. For best performance, use a precision metal film resistor with a value between 10k and 2M and limit the

capacitance on this pin to less than 10pF. The voltage on

this pin is not static. Limiting the capacitance on this pin

is important for the part to perform properly. To disable

the modulation, connect this pin to GND. Grounding the

MOD pin disables the modulation and shuts down the

modulation circuitry to save power. Leaving the pin open

to disable the modulation is not recommended. While

leaving the pin open, RMOD ≈ ∞, gives the mathematical

result of 0% modulation, the open pin is susceptible to

external noise coupling that can effect frequency accuracy.

W

BLOCK DIAGRA

2

V + – VSET = 1.1V ±25%

V

1

+

MASTER OSCILLATOR

ISET

10

IMOD

SET

ISET

RMOD

–

+

–

G=1

IMASTER

fMASTER = 10MHz • 20kΩ • +

(V – VSET)

VBIAS

ISET

9

PH

+

PROGRAMMABLE

DIVIDER ÷N

(N = 1, 10 OR 100)

IMASTER

MULTIPHASE

CIRCUIT

SELECTS BETWEEN

MULTIPHASE

OPTIONS AND ÷M

2-PHASE (M = 1)

3-PHASE (M = 3)

4-PHASE (M = 4)

OUT1

OUT2

OUT3

OUT4

4

5

6

7

MOD

IMOD

–

IMOD

+

RSET

3

DIV

VSET

REF

MULTIPLYING

DAC

7

9-BIT PRBS

GENERATOR

÷ 3200

CURRENT MIRROR

8 GND

6902 BD

6902f

7

�LTC6902

U

THEORY OF OPERATIO

As shown in the Block Diagram, the LTC6902’s master

oscillator is controlled by the ratio of the voltage between

the V+ and SET pins (V+ – VSET) and the current entering

the master oscillator, IMASTER. When the spread spectrum

frequency modulation (SSFM) is disabled, IMASTER is

strictly determined by the V+ – VSET voltage and the ISET

current. When SSFM is enabled, the current IMOD (modulation current) is subtracted from the ISET current to

determine the IMASTER current value. Here the IMASTER

current is maximally at ISET but more often than not it is

less than ISET by a value determined by the IMOD value. In

this way the frequency of the master oscillator is modulated to produce a frequency that is always less than or

equal to the frequency set by the ISET current.

The voltage on the SET pin is forced to approximately 1.1V

below V+ by the PMOS transistor and its gate bias voltage.

This voltage is accurate to ±8% at a particular input

current and supply voltage (see Figure 2). The RSET

resistor, connected between the V+ and SET pins, locks

together the (V+ – VSET) voltage and the current ISET. This

allows the parts to attain excellent frequency accuracy

regardless of the precision of the SET pin voltage. The

LTC6902 is optimized for use with RSET resistors between

10k and 2M. This corresponds to master oscillator frequencies between 100kHz and 20MHz. Additionally, the

MOD pin’s voltage tracks the SET pin’s voltage. The RMOD

resistor connected between the V+ and MOD pins similarly

locks together the MOD pin voltage variation and the IMOD

current to once more yield excellent accuracy.

1.4

1.3

VRES = V + – VSET

V + = 5V

1.2

V + = 3V

1.1

1.0

0.9

0.8

0.1

1

10

IRES (µA)

100

The master oscillator’s output is connected to the programmable divider. The output of the programmable

divider is then connected to the multiphase circuit with its

four outputs directly connected to output drivers. The final

output frequency is determined by the RSET resistor value,

the programmable divider setting and the multiphase

mode selected. The formula for setting the output frequency, fOUT, is below:

fOUT =

10MHz 20kΩ

•

N • M RSET

where:

100 DIV Pin = V +

N = 10 DIV Pin = Open

1 DIV Pin = 0 V

4

M = 3

1

(4 - Phase Output) PH Pin = V +

(3 - Phase Output) PH Pin = Open

(2 - Phase Output) PH Pin = 0 V

When the spread spectrum frequency modulation (SSFM)

is disabled, the frequency fOUT is the final output frequency. When SSFM is enabled, fOUT is the maximum

output frequency with the RMOD resistor value determining the minimum output frequency.

The programmable divider divides the master oscillator

signal by 1, 10 or 100. The divide-by value is determined

by the state of the DIV input (Pin 2). Tie DIV to GND or drive

it below 0.5V to select ÷1. This is the highest frequency

range, with the master output frequency passed directly to

the multiphase circuit. The DIV pin may be floated or

driven to midsupply to select ÷10, the intermediate frequency range. The lowest frequency range, ÷100, is selected by tying DIV to V+ or driving it to within 0.4V of V+.

Figure 3 shows the relationship between RSET, divider

setting and output frequency, including the overlapping

frequency ranges near 100kHz and 1MHz.

1000

69012 F02

Figure 2. V + – VSET Variation with IRES

The multiphase circuit generates outputs that are either

2-, 3- or 4-phase waveforms. To generate the 3- and

4-phase output signals, the output from the programmable

6902f

8

�LTC6902

U

THEORY OF OPERATIO

divider goes through further division. In addition to further division, the duty cycle of the output depends on the

multiphase mode selected. Figure 4 shows the waveform

at each output for 2-, 3- and 4-phase modes.

2-Phase Mode

In 2-phase mode, all outputs are nominally 50% duty

cycle. OUT1 and OUT2 are 180 degrees out of phase.

Stated differently, OUT2 is OUT1 inverted. However, OUT2

10000

RSET (kΩ)

1000

÷100

÷10

3-Phase Mode

÷1

100

10

1

1k

is not simply OUT1 routed through a standard logic

inverter. This would lead to substantial delay for OUT2’s

transitions from OUT1’s transitions. OUT1 and OUT2 are

created by a delay matched inverting circuit. Apart from

the basic inversion, the delay matching is determined by

analog circuit parameters. With this type of design, OUT1

and OUT2 transitions are typically within 100ps. OUT3 and

OUT4 are replications of OUT1 and OUT2 respectively.

Since the two phases are generated via delay matched

inverters, there is not any further division and the parameter M in the frequency setting equation is 1 (M = 1).

10k

100k

1M

10M

DESIRED OUTPUT FREQUENCY (Hz)

100M

69012 F03

Figure 3. RSET vs Desired Output Frequency

(PH = GND, 2-Phase, M = 1)

In 3-phase mode, OUT1, OUT2 and OUT3 are active and all

three outputs have a 33.3% duty cycle. OUT4 is not active

and is at a logic low state. The three active outputs are all

120 degrees out of phase. OUT2 lags OUT1 by 120 degrees

and OUT3 lags OUT2 by 120 degrees. The signals are

generated by a shift register. The output frequency is the

programmable divider’s output further divided 3 (M = 3).

4-Phase Mode

In 4-phase mode, all outputs have a 50% duty cycle. The

outputs are all 90 degrees out of phase. OUT2 lags OUT1

2-PHASE, PH = GND

M=1

DUTY CYCLE = 50%

OUT1

OUT2

OUT3

OUT4

3-PHASE, PH = OPEN

M=3

DUTY CYCLE = 33%

(OUT4 = LOGIC LOW)

OUT1

OUT2

OUT3

OUT4

4-PHASE, PH = V +

M=4

DUTY CYCLE = 50%

OUT1

OUT2

OUT3

OUT4

69012 F04

Figure 4. Mulitphase Output Waveforms

6902f

9

�LTC6902

U

THEORY OF OPERATIO

by 90 degrees, OUT3 lags OUT2 by 90 degrees and OUT4

lags OUT3 by 90 degrees. The signals are generated by

flip-flops. The output frequency is the programmable

divider’s output further divided 4 (M = 4).

The multiphase mode is determined by the state of the PH

input (Pin 3). Tie the PH pin to GND or drive it below 0.5V

to select the 2-phase mode. The PH pin may be floated or

driven to midsupply to select the 3-phase mode. The

4-phase mode is selected by tying the PH pin to V+ or

driving it to within 0.4V of V+.

The CMOS output drivers have an ON resistance that is

typically less than 100Ω. In the ÷1 (high frequency) mode,

the rise and fall times are typically 7ns with a 5V supply and

11ns with a 3V supply. These transition times maintain a

clean square wave at 10MHz (20MHz at 5V supply). In the

÷10 and ÷100 modes, where the output frequency is much

lower, slew rate control circuitry in the output driver increases the rise/fall times to typically 14ns for a 5V supply

and 19ns for a 3V supply. The reduced slew rate lowers EMI

(electromagnetic interference) and supply bounce.

Spread Spectrum Frequency Modulation

The LTC6902 provides the additional feature of spread

spectrum frequency modulation (SSFM). The oscillator’s

frequency is modulated by a pseudorandom noise (PRN)

signal to spread the oscillator’s energy over a wide frequency band. This spreading decreases the peak electromagnetic radiation levels and improves electromagnetic

compatibility (EMC) performance.

The amount of frequency spreading is determined by the

external resistor RMOD and the voltage between the V+ and

MOD pins (V+ – VMOD). Unlike the stationary SET pin

voltage (VSET), the MOD pin voltage (VMOD) is a dynamic

signal generated by a multiplying digital to analog converter (MDAC) referenced to VSET. Referencing to VSET

negates errors due to variations of the VSET voltage and

locks the two voltages together. The VMOD voltage is the

VSET voltage scaled by one fifth and multiplied by the

digital code sent to the MDAC from the pseudorandom

binary sequence (PRBS) generator. VMOD varies in a

pseudorandom noise-like manner. The (V+ – VMOD) voltage is 0V minimum and maximally one fifth (20%) of

(V+ – VSET).

Referencing VMOD to VSET allows the ratio of RSET to

RMOD to determine the amount of frequency spreading.

Consider the case when RSET is equal to RMOD. Here,

when the (V+ – VMOD) voltage is at its minimum of 0V,

IMOD = 0A, IMASTER = ISET and the master oscillator is at

its maximum frequency (fMAX) which is the fOUT frequency set by the RSET resistor. Furthermore, when the

(V+ – VMOD) voltage is at its maximum of 20% of (V+ –

VSET), IMOD = 0.2 • ISET, IMASTER = 0.8 • ISET and the

master oscillator is at its minimum frequency (fMIN)

which is 80% of the fOSC frequency set by the RSET

resistor. The general formula for the amount of frequency

spreading is below:

Frequency Spreading (in %) = 20 •

RSET

RMOD

where frequency spreading is defined as:

Frequency Spreading (in %) = 100 •

fMAX – fMIN

fMAX

The design procedure is to first choose the RSET resistor

value to set fMAX (fOUT) and then choose the RMOD resistor

value to set the amount of frequency spreading desired.

Note that the frequency is always modulated to a lower

value. This is often referred to as a down spread signal.

To disable the SSFM, connect the MOD pin to ground.

Grounding the MOD pin disables the modulation and shuts

down the modulation circuitry. While leaving the MOD pin

open, RMOD = ∞, gives a frequency spreading of 0%, this

is not a good method of disabling the modulation. The

open pin is susceptible to external noise coupling that can

affect the output frequency accuracy. Grounding the MOD

pin is the best way to disable the SSFM.

As stated previously the modulating waveform is a pseudorandom noise-like waveform. The pseudorandom signal

is generated by a linear feedback shift register that is 9 bits

long. The pseudorandom sequence will repeat every 512

(29) shift register clock cycles. The bottom seven bits of the

shift register are sent in parallel to the MDAC which produces the VMOD voltage. Being a digitally generated signal,

the output is not a perfectly smooth waveform but consists

of 128 (27) discrete steps that change every shift register

6902f

10

�LTC6902

U

THEORY OF OPERATIO

clock cycle. Note that the shift register clock is the master

oscillator’s output divided by 3200. This results in a somewhat slow moving modulating signal where each step is

separated in time by 3200/fMASTER seconds and the pseudorandom sequence repeats every (512 • 3200)/fMASTER

seconds.

The servo loop in the LTC6902 cannot respond instantaneously to each step due to its limited bandwidth. The

VMOD voltage steps are converted to frequency steps by

the servo loop. The servo loop has a bandwidth of about

25kHz that limits the frequency change rate and softens

corners of the waveform. This is beneficial when the

LTC6902 is used to clock switching regulators as will be

discussed in the Applications Information section. Figure␣ 5 illustrates the how the output frequency varies over

time.

fMAX

FREQUENCY

128 STEPS

fMIN

τSTEP

TIME

τREPEAT

τSTEP = 3200 τREPEAT = 3200 • 512

fMASTER

fMASTER

69012 F05

Figure 5

U

W

U U

APPLICATIO S I FOR ATIO

SELECTING THE DIVIDER SETTING AND RSET VALUE

The LTC6902’s master oscillator has a frequency range

spanning 0.1MHz to 20MHz. However, accuracy may

suffer if the master oscillator is operated at greater than

10MHz with a supply voltage lower than 4V. A programmable divider extends the frequency range to greater than

three decades. Additional frequency division may occur

depending on the multiphase mode selected. The

multiphase mode and the parameter M are generally

dependent on the application’s requirement and usually

do not offer any additional design flexibility.

The LTC6902’s master oscillator covers a 200:1 range

while the programmable divider has 10:1 steps (1, 10,

100). This wide frequency range coupled with the part’s

programmable divider yields at least two solutions for any

desired output frequency (the exception being the highest

output frequencies that cannot be divided down). Choosing the best divider setting and the correct RSET resistor

value depends on the application.

For spread spectrum frequency modulated (SSFM) applications, choose the highest divider setting. This forces the

master oscillator to run at its highest frequency. The

pseudorandom signal generator is clocked by the master

oscillator, not the output, and the faster the signal moves

the greater the improvement in EMC performance. For

most applications the multiphase mode is determined by

the specific application’s need. For these applications, the

parameter M is predetermined and fixed. Table 1 lists the

recommended output (fOUT) frequency range for each

divider setting when using SSFM.

6902f

11

�LTC6902

U

W

U U

APPLICATIO S I FOR ATIO

Table 1. Recommended Frequency Range vs Programmable

Divider Setting for SSFM Applications or for Low Jitter Constant

Frequency Applications

DIVIDER SETTING

N=1

FREQUENCY RANGE (fOUT • M)

DIV (Pin 2) = GND

2MHz to 20MHz

N = 10

DIV (Pin 2) = Open

200kHz to 2MHz

N = 100

DIV (Pin 2) = V+

< 200kHz

Note: The frequency range numbers are for a 5V supply where a 20MHz

output is the maximum frequency supported. For low supply applications

(2.7V ≤ V+ ≤ 4V), the maximum rated output frequency is 10MHz and all

of the above numbers should be halved.

For constant frequency applications, where SSFM is disabled, the best operating position depends on which

parameter is most important in the application. For the

lowest clock jitter it is best to set the divider to its highest

setting as done above. The divider reduces the master

oscillator’s jitter. The higher the division number the

greater the reduction in the master oscillator’s jitter. For

the best frequency accuracy it is best to run the programmable divider at its lowest setting, and thus, the master

oscillator runs at a lower frequency. The lower master

oscillator frequencies are more accurate and use less

power. To determine a tradeoff between frequency accuracy and jitter consult the Typical Performance Characteristics curves. Table 2 lists the recommended output frequency range for each divider setting for continuous

frequency applications where frequency accuracy is the

primary specification.

Table 2. Recommended Frequency Range vs Programmable

Divider Setting for Best Frequency Accuracy, Constant Frequency

Applications (SSFM disabled)

DIVIDER SETTING

FREQUENCY RANGE (fOUT • M)

N=1

DIV (Pin 2) = GND

> 500kHz*

N = 10

DIV (Pin 2) = Open

50kHz to 500kHz

N = 100

DIV (Pin 2) = V+

< 50kHz

*The maximum frequency (fOUT • M) is 20MHz for 5V applications and is

10MHz for low supply applications (2.7V ≤ V+ ≤ 4V).

For some applications, the multiphase circuit is also useful

in forcing the master oscillator to run at a higher or lower

frequency. If the application requires a single clock source,

the multiphase circuit can be set in whatever mode gives

the highest or lowest divider number (M) and thus the

highest or lowest master oscillator frequency. Additionally, if the application requires just two phases, the 4-phase

mode can be selected with only the OUT1 and OUT3

outputs are used (or alternatively the OUT2 and OUT4

outputs).

For instance, a 500kHz, 2-phase clock can be obtained in

four different ways. Table 3 lists the possible solutions.

For an SSFM application, the preferred solution for best

EMC performance is the last alternative where the master

oscillator is at 20MHz. For a constant frequency application, the preferred solution is the first alternative with the

master oscillator at 500kHz.

Table 3. Four Possible Ways to Obtain a 500kHz, 2-Phase Clock

RSET

N

MULTIPHASE MODE

M

fMASTER

OUTPUTS

400k

1

2

1

500kHz

OUT1, OUT2

100k

1

4

4

2MHz

OUT1, OUT3

40k

10

2

1

5MHz

OUT1, OUT2

10k

10

4

4

20MHz

OUT1, OUT3

After choosing the proper divider setting, determine the

correct frequency-setting resistor. Because of the linear

correspondence between oscillation period and resistance, a simple equation relates resistance with frequency.

4

100

10MHz

RSET = 20k •

, N = 10 M = 3

M • N • fOUT

1

1

(RSETMIN = 10k, RSETMAX = 2M)

Any resistor, RSET, tolerance adds to the inaccuracy of the

oscillator, fOUT.

SETTING THE SPREAD SPECTRUM MODULATION

SPREADING PERCENTAGE WITH THE LTC6902

Setting the spread spectrum modulation percentage on

the LTC6902 is very simple and straightforward. Since the

spreading is ratiometric, in percentage, the programmable divider and multiphase mode selection have no

influence on the spreading percentage. In general, for

greatest EMC improvement, each application should apply

as much spreading as possible. The amount of spreading

that any particular application can tolerate is dependent on

the specific nature of that application. Once the RSET

resistor value is calculated to set fMAX and the desired

6902f

12

�LTC6902

U

W

U U

APPLICATIO S I FOR ATIO

spreading is determined, the RMOD value is calculated

using the simple equation below:

RMOD = 20 •

RSET

Spreading Percentage

The only limitations for this formula are in the RMOD value

range and the spreading percentage range. The range of

the RMOD resistor value is the same as that for RSET

ranging from 10k to 400k. The LTC6902 is tested and

specified for spreading of 10% and 40%. These are

practical limits that would apply to many systems but they

are not the actual limits of the part. The lower end limit is

set by internal offsets and mismatches. At lower spreading

percentages, these mismatches become more significant

and the error from the calculated, desired spreading

increases. A practical lower end limit would be about 5%

spreading. At the higher end internal mismatching becomes less significant, however other factors come into

play and a theoretical limit approaching 100% (fMIN approaching zero) cannot be reliably achieved. A practical

upper limit would be about 80% spreading.

To disable the SSFM, connect the MOD pin to ground.

Grounding the MOD pin disables the modulation and shuts

down the modulation circuitry. While leaving the MOD pin

open, RMOD = ∞, gives a frequency spreading of 0%, this

is not a good method of disabling the modulation. The

open pin is susceptible to external noise coupling that can

affect the output frequency accuracy. Grounding the MOD

pin is the best way to disable the SSFM.

DRIVING LOGIC CIRCUITS

The outputs of the LTC6902 are suitable for driving

general digital logic circuits. The CMOS output drivers

have an ON resistance that is typically less than 100Ω and

are very similar in performance to HCMOS logic outputs.

However, the form of frequency spreading used in the

LTC6902 may not be suitable for many logic designs.

Many logic designs have fairly tight timing and cycle-tocycle jitter requirements. These systems often benefit

from a spread spectrum clocking system where the frequency is slowly and linearly modulated by a triangular

waveform, not a pseudorandom waveform. This type of

frequency spreading maintains a minimal difference in the

timing from one clock edge to the next adjacent clock edge

(cycle-to-cycle jitter). The LTC6902 uses a pseudorandom

modulating signal where the frequency transitions have

been slowed and the corners rounded by a 25kHz lowpass

filter. This filtered modulating signal may be acceptable for

many logic systems but the cycle-to-cycle jitter issues

must be considered carefully.

DRIVING SWITCHING REGULATORS

The LTC6902 is designed primarily to provide an accurate

and stable clock for switching regulator systems, especially those systems with multiple switching regulators

where all of the regulators are interleaved and are run at the

same frequency. This lowers the input capacitor requirements and prevents beat notes formed by mixing numerous clock frequencies and their harmonics. The multiphase

outputs have CMOS drivers with an ON resistance that is

typically less than 100Ω and are very similar in performance to HCMOS logic outputs. This is suitable for

directly driving most switching regulators and switching

controllers. Linear Technology has a broad line of fully

integrated switching regulators and switching regulator

controllers designed for synchronization to an external

clock. All of these parts have one pin assigned for external

clock input. The nomenclature varies depending on the

part’s family history. SYNC, PLLIN, SYNC/MODE, SHDN,

EXTCLK, FCB and S/S (shorthand for SYNC/SHDN) are

examples of clock input pin names used with Linear

Technology ICs. The exact operating details depend on the

switching regulator in use, but generally switching is

synchronized to the rising edge of the clock. Since the

LTC6902’s master oscillator is passed through inverters

or flip-flops to generate its multiphase outputs, coincident

rising edges (or falling edges) cannot occur. This is true

even when the LTC6902 is used with a high percentage of

spreading.

For the best EMC performance, the LTC6902 should be

run with SSFM enabled and the master oscillator at its

highest frequency. The pseudorandom modulation signal

6902f

13

�LTC6902

U

W

U U

APPLICATIO S I FOR ATIO

generator is driven by the master oscillator frequency, not

the output frequency. This gives some design flexibility in

the choice of the RSET and the programmable divider

setting. When making the choice, usually the faster master oscillator is the better choice. This is especially true

when the main goal is to lower peak radiated or conducted

signal levels measured during regulatory agency testing.

Regulatory testing is done with strictly specified bandwidths and conditions. Modulating faster than the test

bandwidth or as close to the bandwidth as possible gives

the lowest readings. The optimal modulating rate is not as

straightforward when the goal is to lower radiated signal

levels interfering with other circuitry in the system. The

modulation rate will have to be evaluated with the specific

system conditions to determine the optimal rate. Depending on the specific frequency synchronization method a

switching regulator employs, the modulation rate must

be within the synchronization capability of the regulator.

Many switching regulators use a phase-locked loop (PLL)

for synchronization. For these parts, the PLL loop filter

should be designed to have sufficient capture range and

bandwidth.

Even when running the LTC6902 at the maximum modulation rate, the frequency hopping transitions are slowed

by the part’s servo loop. The frequency transitions are

slowed by a 25kHz lowpass. This is an important feature

when driving a switching regulator. The switching regulator is itself a servo loop with a bandwidth typically on the

order of 1/10, but can vary from 1/50 to 1/2 of the

operating frequency. When the input clock frequency’s

transition is within the bandwidth of the switching regulator, the regulator’s output stays in regulation. If the transition is too sharp, beyond the bandwidth of the switching

regulator, the regulator’s output will experience a sharp

jump and then settle back into regulation. If the bandwidth

of the switching regulator is sufficiently high, beyond

25kHz, then there will not be any regulation issues.

One aspect of the output voltage that will change is the

output ripple voltage. Every switching regulator has some

output ripple at the clock frequency. For most switching

regulator designs with fixed MOSFETs, fixed inductor,

fixed capacitors, the amount of ripple will vary some with

the regulator’s operating frequency (the main exception

being hysteresis architecture regulators). An increase in

frequency results in lower ripple and a frequency decrease

gives more ripple. This is true for static frequencies or

dynamic frequency modulated systems. If the modulating

signal was a triangle wave, the regulator’s output would

have a ripple that is amplitude modulated by the triangle

wave. This repetitive signal on the power supply could

cause system problems by mixing with other desired

signals and giving a distorted output. Depending on the

inductor design and triangle wave frequency, it may even

result in an audible noise. The LTC6902 uses a pseudorandom noise-like modulating signal. This results in the

regulator’s output ripple being modulated by the wideband

pseudorandom noise-like signal. On an oscilloscope, it

looks essentially noise-like of even amplitude. The signal

is broadband and any mixing issues are minimized. Additionally, the pseudorandom signal repeats at such a low

rate that it is well below the audible range.

The LTC6902 directly drives many switching regulators.

The LTC6902 with the spread spectrum frequency modulation results in improved EMC performance. If the bandwidth of the switching regulator is sufficient, not a difficult

requirement in most cases, the regulator’s regulation,

efficiency and load response are maintained while peak

electromagnetic radiation (or conduction) is reduced.

Output ripple may be somewhat increased, but its behavior is very much like noise and its system impact is benign.

6902f

14

�LTC6902

U

W

U U

APPLICATIO S I FOR ATIO

POWER SUPPLY SENSITIVITY

Figure 6 shows the output frequency sensitivity to power

supply voltage at several different temperatures. The

LTC6902 has a guaranteed voltage coefficient of 0.1%/V

but, as Figure 6 shows, the typical supply sensitivity is

twice as low.

START-UP TIME

The start-up time and settling time to within 1% of the final

value can be estimated by tSTART ≅ RSET(3.7µs/kΩ) +

10µs. Note the start-up time depends on RSET and is

Jitter

The Peak-to-Peak Jitter vs Output Frequency graph, in the

Typical Performance Characteristics section, shows the

typical clock jitter as a function of oscillator frequency and

power supply voltage. The capacitance from the SET pin,

(Pin 3), to ground must be less than 10pF. If this requirement is not met, the jitter will increase.

70

RSET = 63.2k

PIN 4 = FLOATING (÷10)

0.10

25°C

–40°C

0.05

TA = 25°C

V+ = 5V

60

FREQUENCY ERROR (%)

FREQUENCY DEVIATION (%)

0.15

independent from the setting of the divider pin. For instance with RSET = 100k, the LTC6902 will settle with 1%

of its 200kHz final value (N = 10) in approximately 380µs.

Figure 7 shows start-up times for various RSET resistors.

85°C

0

50

40

30

20

400k

10

63.2k

0

–0.05

–10

2.5

3.0

3.5

4.0

4.5

SUPPLY VOLTAGE (V)

5.0

5.5

20k

0

200

400

800

600

TIME AFTER POWER APPLIED (µs)

69012 F07

69012 F06

Figure 6. Supply Sensitivity

1000

Figure 7. Start-Up Time

6902f

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

15

�LTC6902

U

PACKAGE DESCRIPTIO

MS Package

10-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1661)

0.889 ± 0.127

(.035 ± .005)

5.23

(.206)

MIN

3.2 – 3.45

(.126 – .136)

3.00 ± 0.102

(.118 ± .004)

(NOTE 3)

0.50

0.305 ± 0.038

(.0197)

(.0120 ± .0015)

BSC

TYP

RECOMMENDED SOLDER PAD LAYOUT

0.254

(.010)

10 9 8 7 6

3.00 ± 0.102

(.118 ± .004)

NOTE 4

4.90 ± 0.15

(1.93 ± .006)

DETAIL “A”

0.497 ± 0.076

(.0196 ± .003)

REF

0° – 6° TYP

GAUGE PLANE

1 2 3 4 5

0.53 ± 0.01

(.021 ± .006)

1.10

(.043)

MAX

DETAIL “A”

0.86

(.034)

REF

0.18

(.007)

SEATING

PLANE

0.17 – 0.27

(.007 – .011)

TYP

0.50

(.0197)

NOTE:

BSC

1. DIMENSIONS IN MILLIMETER/(INCH)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

0.13 ± 0.076

(.005 ± .003)

MSOP (MS) 0802

RELATED PARTS

PART NUMBER

DESCRIPTION

COMMENTS

TM

LTC1799

1kHz to 30MHz ThinSOT Oscillator

Single Output, Higher Frequency Operation

LTC6900

1kHz to 20MHz ThinSOT Oscillator

Single Output, Lower Power

ThinSOT is a trademark of Linear Technology Corporation.

6902f

16

Linear Technology Corporation

LT/TP 0103 2K • PRINTED IN USA

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

LINEAR TECHNOLOGY CORPORATION 2003

�