32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

Parallel NOR Flash Embedded Memory

JR28F032M29EWXX; PZ28F032M29EWXX; JS28F064M29EWXX

PC28F064M29EWXX; JR28F064M29EWXX; PZ28F064M29EWXX

JS28F128M29EWXX; PC28F128M29EWXX; RC28F128M29EWXX

Features

• VPP/WP# pin protection

– VPPH voltage on V PP to accelerate programming

performance

– Protects highest/lowest block (H/L uniform) or

top/bottom two blocks (T/B boot)

• Software protection

– Volatile protection

– Nonvolatile protection

– Password protection

– Password access

• Extended memory block

– 128-word (256-byte) block for permanent secure

identification

– Program or lock implemented at the factory or by

the customer

• Low-power consumption: Standby mode

• JESD47H-compliant

– 100,000 minimum ERASE cycles per block

– Data retention: 20 years (TYP)

• 65nm single-bit cell process technology

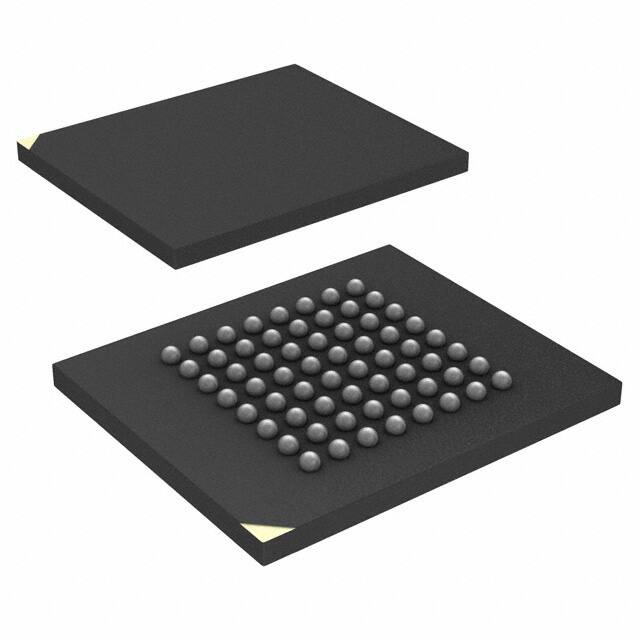

• Packages (JEDEC-standard)

– 56-pin TSOP (128Mb, 64Mb)

– 48-pin TSOP (64Mb, 32Mb)

– 64-ball FBGA (128Mb, 64Mb)

– 48-ball BGA (64Mb, 32Mb)

• Green packages available

– RoHS-compliant

– Halogen-free

• Operating temperature

– Ambient: –40°C to +85°C

• Supply voltage

– VCC = 2.7–3.6V (program, erase, read)

– VCCQ = 1.65–3.6V (I/O buffers)

• Asynchronous random or page read

– Page size: 8 words or 16 bytes

– Page access: 25ns

– Random access (VCCQ = 2.7–3.6V): 60ns (BGA);

70ns (TSOP)

• Buffer program: 256-word MAX program buffer

• Program time

– 0.56µs per byte (1.8 MB/s TYP when using 256word buffer size in buffer program without V PPH)

– 0.31µs per byte (3.2 MB/s TYP when using 256word buffer size in buffer program with V PPH)

• Memory organization

– 32Mb: 64 main blocks, 64KB each, or eight 8KB

boot blocks (top or bottom) and 63 main blocks,

64KB each

– 64Mb: 128 main blocks, 64KB each, or eight 8KB

boot blocks (top or bottom) and 127 main blocks,

64 KB each

– 128Mb: 128 main blocks, 128KB each

• Program/erase controller

– Embedded byte/word program algorithms

• Program/erase suspend and resume capability

– READ operation on another block during a PROGRAM SUSPEND operation

– READ or PROGRAM operation on one block during an ERASE SUSPEND operation on another

block

• BLANK CHECK operation to verify an erased block

• Unlock bypass, block erase, chip erase, and write to

buffer capability

– Fast buffered/batch programming

– Fast block and chip erase

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

Part Numbering Information

This product is available with the prelocked extended memory block. Devices are shipped from the factory with

memory content bits erased to 1. For a list of available options, such as packages or high/low protection, or for

further information, contact your Micron sales representative.

Table 1: Part Number Information

Part Number

Category

Package

Category Details

JS = 56-pin TSOP, 14mm x 20mm, lead-free, halogen-free, RoHS-compliant

PC = 64-ball Fortified BGA, 11mm x 13mm, lead-free, halogen-free, RoHS-compliant

RC = 64-ball Fortified BGA, 11mm x 13mm, leaded

JR = 48-pin TSOP, 12mm x 20mm, lead-free, halogen-free, RoHS-compliant

PZ = 48-ball BGA, 6mm x 8mm, lead-free, halogen-free, RoHS-compliant

Product designator

28F = Parallel NOR interface

Density

128 = 128Mb

064 = 64Mb

032 = 32Mb

Device type

M29EW = Embedded Flash memory (3V core, page read)

Device function

H = Highest block protected by VPP/WP#; uniform block

L = Lowest block protected by VPP/WP#; uniform block

B = Bottom boot; bottom two blocks protected by VPP/WP#

T = Top boot; top two blocks protected by VPP/WP#

Features

A/B/F/X or an asterisk (*) = Combination of features, including packing media, security features,

and specific customer request information

Valid M29EW Part Number Combinations

Table 2: Standard Part Numbers by Density, Medium, and Package

Density

Medium

Package

JS

32Mb

Tray

–

PC

RC

–

–

JR

PZ

JR28F032M29EWHA PZ28F032M29EWHA

JR28F032M29EWLA PZ28F032M29EWLA

JR28F032M29EWBA PZ28F032M29EWBA

JR28F032M29EWTA PZ28F032M29EWTA

Tape

and

reel

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

–

–

–

JR28F032M29EWBB PZ28F032M29EWBB

JR28F032M29EWTB

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

Table 2: Standard Part Numbers by Density, Medium, and Package (Continued)

Density

Medium

Package

64Mb

JS

PC

RC

Tray JS28F064M29EWHA PC28F064M29EWHA

JS28F064M29EWLA

–

PZ

JR28F064M29EWHA PZ28F064M29EWHA

PC28F064M29EWLA

JR28F064M29EWLA PZ28F064M29EWLA

JS28F064M29EWBA PC28F064M29EWBA

JR28F064M29EWBA PZ28F064M29EWBA

JS28F064M29EWTA

JR28F064M29EWTA PZ28F064M29EWTA

PC28F064M29EWTA

Tape JS28F064M29EWLB

and

reel

128Mb Tray

JR

–

–

JR28F064M29EWHB PZ28F064M29EWBB

JR28F064M29EWLB

JR28F064M29EWTB

JS28F128M29EWHF

PC28F128M29EWHF RC28F128M29EWHF

JS28F128M29EWLA

PC28F128M29EWLA RC28F128M29EWLA

Tape

and

reel

–

–

–

–

–

–

–

Table 3: Part Numbers with Security Features by Density, Medium, and Package

Package

Density

Medium

PC

PZ

64Mb

Tray

PC28F064M29EWHX

PZ28F064M29EWHX

PC28F064M29EWLX

PZ28F064M29EWLX

PC28F064M29EWBX

PZ28F064M29EWBX

PC28F064M29EWTX

PZ28F064M29EWTX

Tape and Reel

PC28F064M29EWTY

–

Tray

PC28F128M29EWHX

–

128Mb

PC28F128M29EWLX

Tape and Reel

Note:

–

–

1. This data sheet covers only standard parts. For security parts, contact your local Micron sales representative.

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

Contents

General Description ......................................................................................................................................... 8

Signal Assignments ........................................................................................................................................... 9

Signal Descriptions ......................................................................................................................................... 13

Memory Organization .................................................................................................................................... 14

Memory Configuration ............................................................................................................................... 14

Memory Map – 32Mb ................................................................................................................................. 15

Memory Map – 64Mb ................................................................................................................................. 17

Memory Map – 128Mb ................................................................................................................................ 19

Bus Operations ............................................................................................................................................... 20

Read .......................................................................................................................................................... 20

Write .......................................................................................................................................................... 20

Standby ..................................................................................................................................................... 20

Output Disable ........................................................................................................................................... 21

Reset .......................................................................................................................................................... 21

Registers ........................................................................................................................................................ 22

Status Register ............................................................................................................................................ 22

Lock Register .............................................................................................................................................. 27

Standard Command Definitions – Address-Data Cycles .................................................................................... 29

READ and AUTO SELECT Operations .............................................................................................................. 32

READ/RESET Command ............................................................................................................................ 32

READ CFI Command .................................................................................................................................. 32

AUTO SELECT Command ........................................................................................................................... 32

Bypass Operations .......................................................................................................................................... 34

UNLOCK BYPASS Command ...................................................................................................................... 34

UNLOCK BYPASS RESET Command ............................................................................................................ 35

Program Operations ....................................................................................................................................... 35

PROGRAM Command ................................................................................................................................ 35

UNLOCK BYPASS PROGRAM Command ..................................................................................................... 36

DOUBLE BYTE/WORD PROGRAM Command ............................................................................................. 36

QUADRUPLE BYTE/WORD PROGRAM Command ...................................................................................... 36

OCTUPLE BYTE PROGRAM Command ....................................................................................................... 37

WRITE TO BUFFER PROGRAM Command .................................................................................................. 37

UNLOCK BYPASS WRITE TO BUFFER PROGRAM Command ....................................................................... 39

ENHANCED WRITE TO BUFFER PROGRAM Command ............................................................................... 40

UNLOCK BYPASS ENHANCED WRITE TO BUFFER PROGRAM Command ................................................... 40

WRITE TO BUFFER PROGRAM CONFIRM Command .................................................................................. 41

ENHANCED WRITE TO BUFFER PROGRAM CONFIRM Command .............................................................. 41

BUFFERED PROGRAM ABORT AND RESET Command ................................................................................ 41

PROGRAM SUSPEND Command ................................................................................................................ 41

PROGRAM RESUME Command .................................................................................................................. 42

Erase Operations ............................................................................................................................................ 42

CHIP ERASE Command .............................................................................................................................. 42

UNLOCK BYPASS CHIP ERASE Command ................................................................................................... 42

BLOCK ERASE Command ........................................................................................................................... 43

UNLOCK BYPASS BLOCK ERASE Command ................................................................................................ 43

ERASE SUSPEND Command ....................................................................................................................... 44

ERASE RESUME Command ........................................................................................................................ 44

BLANK CHECK Operation .............................................................................................................................. 45

BLANK CHECK Commands ........................................................................................................................ 45

Block Protection Command Definitions – Address-Data Cycles ........................................................................ 46

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

Protection Operations ....................................................................................................................................

LOCK REGISTER Commands ......................................................................................................................

PASSWORD PROTECTION Commands .......................................................................................................

NONVOLATILE PROTECTION Commands ..................................................................................................

NONVOLATILE PROTECTION BIT LOCK BIT Commands ............................................................................

VOLATILE PROTECTION Commands ..........................................................................................................

EXTENDED MEMORY BLOCK Commands ..................................................................................................

EXIT PROTECTION Command ....................................................................................................................

Device Protection ...........................................................................................................................................

Hardware Protection ..................................................................................................................................

Software Protection ....................................................................................................................................

Volatile Protection Mode .............................................................................................................................

Nonvolatile Protection Mode ......................................................................................................................

Password Protection Mode ..........................................................................................................................

Password Access .........................................................................................................................................

Common Flash Interface ................................................................................................................................

Power-Up and Reset Characteristics ................................................................................................................

Absolute Ratings and Operating Conditions .....................................................................................................

DC Characteristics ..........................................................................................................................................

Read AC Characteristics ..................................................................................................................................

Write AC Characteristics .................................................................................................................................

Accelerated Program, Data Polling/Toggle AC Characteristics ...........................................................................

Electrical Specifications – Program/Erase Characteristics .................................................................................

Package Dimensions .......................................................................................................................................

Revision History .............................................................................................................................................

Rev. B – 11/12 .............................................................................................................................................

Rev. A – 08/12 .............................................................................................................................................

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

5

49

49

49

49

52

52

52

53

54

54

54

55

55

56

56

58

63

65

67

69

73

80

82

83

87

87

87

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

List of Figures

Figure 1: Logic Diagram ................................................................................................................................... 8

Figure 2: 56-Pin TSOP (Top View) .................................................................................................................... 9

Figure 3: 48-Pin TSOP (Top View) .................................................................................................................. 10

Figure 4: 48-Ball BGA (Top and Bottom Views) ............................................................................................... 11

Figure 5: 64-Ball Fortified BGA (Top and Bottom Views) .................................................................................. 12

Figure 6: Data Polling Flowchart .................................................................................................................... 24

Figure 7: Toggle Bit Flowchart ........................................................................................................................ 25

Figure 8: Status Register Polling Flowchart ..................................................................................................... 26

Figure 9: Lock Register Program Flowchart ..................................................................................................... 28

Figure 10: Boundary Condition of Program Buffer Size .................................................................................... 38

Figure 11: WRITE TO BUFFER PROGRAM Flowchart ...................................................................................... 39

Figure 12: Program/Erase Nonvolatile Protection Bit Algorithm ...................................................................... 51

Figure 13: Software Protection Scheme .......................................................................................................... 56

Figure 14: Power-Up Timing .......................................................................................................................... 63

Figure 15: Reset AC Timing – No PROGRAM/ERASE Operation in Progress ...................................................... 64

Figure 16: Reset AC Timing During PROGRAM/ERASE Operation .................................................................... 64

Figure 17: AC Measurement Load Circuit ....................................................................................................... 66

Figure 18: AC Measurement I/O Waveform ..................................................................................................... 66

Figure 19: Random Read AC Timing (8-Bit Mode) ........................................................................................... 71

Figure 20: Random Read AC Timing (16-Bit Mode) ......................................................................................... 71

Figure 21: BYTE# Transition Read AC Timing .................................................................................................. 72

Figure 22: Page Read AC Timing (16-Bit Mode) ............................................................................................... 72

Figure 23: WE#-Controlled Program AC Timing (8-Bit Mode) .......................................................................... 74

Figure 24: WE#-Controlled Program AC Timing (16-Bit Mode) ......................................................................... 75

Figure 25: CE#-Controlled Program AC Timing (8-Bit Mode) ........................................................................... 77

Figure 26: CE#-Controlled Program AC Timing (16-Bit Mode) ......................................................................... 78

Figure 27: Chip/Block Erase AC Timing (8-Bit Mode) ...................................................................................... 79

Figure 28: Accelerated Program AC Timing ..................................................................................................... 80

Figure 29: Data Polling AC Timing .................................................................................................................. 80

Figure 30: Toggle/Alternative Toggle Bit Polling AC Timing (8-Bit Mode) .......................................................... 81

Figure 31: 56-Pin TSOP – 14mm x 20mm ........................................................................................................ 83

Figure 32: 48-Pin TSOP – 12mm x 20mm ........................................................................................................ 84

Figure 33: 48-Ball BGA – 6mm x 8mm ............................................................................................................. 85

Figure 34: 64-Ball Fortified BGA – 11mm x 13mm ........................................................................................... 86

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Features

List of Tables

Table 1: Part Number Information ................................................................................................................... 2

Table 2: Standard Part Numbers by Density, Medium, and Package ................................................................... 2

Table 3: Part Numbers with Security Features by Density, Medium, and Package ................................................ 3

Table 4: Signal Descriptions ........................................................................................................................... 13

Table 5: 32Mb Memory Map – x8 Top and Bottom Boot [70:0] ......................................................................... 15

Table 6: 32Mb Memory Map – x16 Top and Bottom Boot [70:0] ........................................................................ 15

Table 7: 32Mb Memory Map – x8/x16 Uniform Blocks [63:0] ............................................................................ 16

Table 8: 64Mb Memory Map – x8 Top and Bottom Boot [134:0] ........................................................................ 17

Table 9: 64Mb Memory Map – x16 Top and Bottom Boot [134:0] ...................................................................... 17

Table 10: 64Mb Memory Map – x8/x16 Uniform Blocks [127:0] ........................................................................ 18

Table 11: 128Mb Memory Map – x8/x16 Uniform Blocks [127:0] ...................................................................... 19

Table 12: Bus Operations ............................................................................................................................... 20

Table 13: Status Register Bit Definitions ......................................................................................................... 22

Table 14: Operations and Corresponding Bit Settings ...................................................................................... 23

Table 15: Lock Register Bit Definitions ............................................................................................................ 27

Table 16: Standard Command Definitions – Address-Data Cycles, 8-Bit and 16-Bit ........................................... 29

Table 17: Read Electronic Signature ............................................................................................................... 33

Table 18: Block Protection ............................................................................................................................. 34

Table 19: Block Protection Command Definitions – Address-Data Cycles, 8-Bit and 16-Bit ................................ 46

Table 20: Extended Memory Block Address and Data ...................................................................................... 52

Table 21: V PP/WP# Functions ......................................................................................................................... 54

Table 22: Query Structure Overview ............................................................................................................... 58

Table 23: CFI Query Identification String ........................................................................................................ 58

Table 24: CFI Query System Interface Information .......................................................................................... 59

Table 25: Device Geometry Definition ............................................................................................................ 59

Table 26: Erase Block Region Information ....................................................................................................... 60

Table 27: Primary Algorithm-Specific Extended Query Table ........................................................................... 61

Table 28: Power-Up Specifications ................................................................................................................. 63

Table 29: Reset AC Specifications ................................................................................................................... 64

Table 30: Absolute Maximum/Minimum Ratings ............................................................................................ 65

Table 31: Operating Conditions ...................................................................................................................... 65

Table 32: Input/Output Capacitance .............................................................................................................. 66

Table 33: DC Current Characteristics .............................................................................................................. 67

Table 34: DC Voltage Characteristics .............................................................................................................. 68

Table 35: Read AC Characteristics .................................................................................................................. 69

Table 36: WE#-Controlled Write AC Characteristics ......................................................................................... 73

Table 37: CE#-Controlled Write AC Characteristics ......................................................................................... 76

Table 38: Accelerated Program and Data Polling/Data Toggle AC Characteristics .............................................. 80

Table 39: Program/Erase Characteristics ........................................................................................................ 82

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

General Description

General Description

The M29EW is an asynchronous, parallel NOR Flash memory device manufactured on

65nm single-bit cell (SBC) technology. READ, ERASE, and PROGRAM operations are

performed using a single low-voltage supply. Upon power-up, the device defaults to

read array mode.

The main memory array is divided into uniform blocks that can be erased independently so that valid data can be preserved while old data is purged. PROGRAM and ERASE

commands are written to the command interface of the memory. An on-chip program/

erase controller simplifies the process of programming or erasing the memory by taking

care of all special operations required to update the memory contents. The end of a

PROGRAM or ERASE operation can be detected and any error condition can be identified. The command set required to control the device is consistent with JEDEC standards.

CE#, OE#, and WE# control the bus operation of the device and enable a simple connection to most microprocessors, often without additional logic.

The M29EW supports asynchronous random read and page read from all blocks of the

array. It also features an internal program buffer that improves throughput by programming 256 words via one command sequence. The device contains a 128-word extended

memory block which overlaps addresses with array block 0. The user can program this

additional space and then protect it to permanently secure the contents. The device also features different levels of hardware and software protection to secure blocks from

unwanted modification.

Refer to TN-13-30, System Design Considerations with Micron Flash Memory, for details on system design and V CC and V CCQ signals.

Figure 1: Logic Diagram

VCC

VCCQ

VPP/WP#

15

A[MAX:0]

DQ[14:0]

DQ15/A-1

WE#

CE#

RY/BY#

OE#

RST#

BYTE#

VSS

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Signal Assignments

Signal Assignments

Figure 2: 56-Pin TSOP (Top View)

RFU

A22

A15

A14

A13

A12

A11

A10

A9

A8

A19

A20

WE#

RST#

A21

VPP/WP#

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

RFU

RFU

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Notes:

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

1.

2.

3.

4.

RFU

RFU

A16

BYTE#

VSS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

VCC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

VSS

CE#

A0

RFU

VCCQ

A-1 is the least significant address bit in x8 mode.

A21 is valid for 64Mb and above; otherwise, it is RFU.

A22 is valid for 128Mb and above; otherwise, it is RFU.

RFU = Reserved for future use.

9

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Signal Assignments

Figure 3: 48-Pin TSOP (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

A15

A14

A13

A12

A11

A10

A9

A8

A19

A20

WE#

RST#

A21

VPP/WP#

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

Notes:

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1.

2.

3.

4.

A16

BYTE#

VSS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

VCC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

VSS

CE#

A0

A-1 is the least significant address bit in x8 mode.

A21 is valid for 64Mb and above; otherwise, it is RFU.

For 48-Pin, there is no VCCQ pin, VCC also supply IO, it can only be 2.7V-3.6V

RFU = Reserved for future use.

10

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Signal Assignments

Figure 4: 48-Ball BGA (Top and Bottom Views)

3

2

1

4

5

6

6

5

A9

A13

A13

A9

4

3

2

1

A

A

A7 RY/BY# WE#

A3

WE# RY/BY# A7

A3

B

B

A4

A17 VPP/WP#RST#

A8

A12

A12

A8

RST# VPP/WP# A17

A4

A2

A6

A21

A10

A14

A14

A10

A21

A6

A2

C

C

A18

A18

D

D

A5

A1

A20

A19

A11

A15

A15

A11

A19

A20

A5

A1

E

E

D0

D2

D5

D7

CE#

D8

D10

D12

D14 BYTE#

D7

D5

D2

D0

A0

BYTE# D14

D12

D10

D8

CE#

A16

A16

A0

F

F

G

G

OE#

D9

D11

VCC

D13 D15/A-1

VSS

D1

D3

D4

D6

D15/A-1 D13

VCC

D11

D9

OE#

D4

D3

D1

VSS

H

H

VSS

VSS

BGA

Top view – ball side down

Notes:

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

1.

2.

3.

4.

D6

BGA

Bottom view – ball side up

A-1 is the least significant address bit in x8 mode.

A21 is valid for 64Mb and above; otherwise, it is RFU.

For 48-Pin, there is no VCCQ pin, VCC also supply IO, it can only be 2.7V-3.6V

RFU = Reserved for future use.

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Signal Assignments

Figure 5: 64-Ball Fortified BGA (Top and Bottom Views)

1

2

3

4

5

6

7

8

8

7

6

4

5

3

2

1

A

A

RFU

A3

A7 RY/BY# WE#

A9

A13

RFU

RFU

A13

A9

WE# RY/BY# A7

A3

RFU

B

B

RFU

A4

A17 VPP/WP# RST#

A8

A12

A22

A22

A12

A8

RST# VPP/WP# A17

A4

RFU

C

C

RFU

A2

A6

A18

A21

A10

A14

RFU

RFU

A14

A10

A21

A18

A6

A2

RFU

D

D

RFU

A1

A5

A20

A19

A11

A15 VCCQ

RFU

A0

D0

D2

D5

D7

A16

VCCQ CE#

D8

D10

D12

RFU

OE#

D9

D11

RFU

VSS

D1

D3

VCCQ A15

A11

A19

A20

A5

A1

RFU

D7

D5

D2

D0

A0

RFU

D14 BYTE# RFU

RFU BYTE# D14

D12

D10

D8

CE# VCCQ

VCC

D13 D15/A-1 RFU

RFU D15/A-1 D13

VCC

D11

D9

OE#

RFU

D4

D6

RFU

D4

D3

D1

VSS

RFU

E

E

VSS

VSS

A16

F

F

G

G

H

H

VSS

RFU

Fortified BGA

Top view – ball side down

Notes:

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

1.

2.

3.

4.

VSS

D6

Fortified BGA

Bottom view – ball side up

A-1 is the least significant address bit in x8 mode.

A21 is valid for 64Mb and above; otherwise, it is RFU.

A22 is valid for 128Mb and above; otherwise, it is RFU.

RFU = Reserved for future use.

12

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Signal Descriptions

Signal Descriptions

The signal description table below is a comprehensive list of signals for this device family. All signals listed may not be supported on this device. See Signal Assignments for information specific to this device.

Table 4: Signal Descriptions

Name

Type

Description

A[MAX:0]

Input

Address: Selects the cells in the array to access during READ operations. During WRITE operations, they control the commands sent to the command interface of the program/erase controller.

CE#

Input

Chip enable: Activates the device, enabling READ and WRITE operations to be performed.

When CE# is HIGH, the device goes to standby and data outputs are at High-Z.

OE#

Input

Output enable: Controls the bus READ operation.

WE#

Input

Write enable: Controls the bus WRITE operation of the command interface.

VPP/WP#

Input

VPP/Write Protect: Provides WRITE PROTECT function and VPPH function. These functions

protect the lowest or highest block or top two blocks or bottom two blocks, enable the device to enter unlock bypass mode and accelerate program speed, respectively. (Refer to Hardware Protection, Bypass Operations, and Program Operations for details.)

A 0.1μF capacitor should be connected between VPP/WP# and VSS to decouple the current

surges from the power supply when VPPH is applied. The PCB track widths must be sufficient

to carry the currents required during PROGRAM and ERASE operation when VPPH is applied.

(See DC Characteristics.)

BYTE#

Input

Byte/word organization select: Switches between x8 and x16 bus modes. When BYTE# is

LOW, the device is in x8 mode; when HIGH, the device is in x16 mode.

RST#

Input

Reset: Applies a hardware reset to the device, which is achieved by holding RST# LOW for at

least tPLPX. After RST# goes HIGH, the device is ready for READ and WRITE operations (after

tPHEL or tRHEL, whichever occurs last). See RESET AC Specifications for more details.

DQ[7:0]

I/O

Data I/O: Outputs the data stored at the selected address during a READ operation. During

WRITE operations, they represent the commands sent to the command interface of the internal state machine.

DQ[14:8]

I/O

Data I/O: Outputs the data stored at the selected address during a READ operation when

BYTE# is HIGH. When BYTE# is LOW, these pins are not used and are High-Z. During WRITE

operations, these bits are not used. When reading the status register, these bits should be ignored.

DQ15/A-1

I/O

Data I/O or address input: When the device operates in x16 bus mode, this pin behaves as

data I/O, together with DQ[14:8]. When the device operates in x8 bus mode, this pin behaves

as the least significant bit of the address.

Except where stated explicitly otherwise, DQ15 = data I/O (x16 mode); A-1 = address input (x8

mode).

PDF: 09005aef84dc44a7

m29ew_32Mb-128Mb.pdf - Rev. B 11/12 EN

13

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2012 Micron Technology, Inc. All rights reserved.

�32Mb, 64Mb, 128Mb: 3V Embedded Parallel NOR Flash

Memory Organization

Table 4: Signal Descriptions (Continued)

Name

Type

RY/BY#

Output

Description

Ready busy: Open-drain output that can be used to identify when the device is performing

a PROGRAM or ERASE operation. During PROGRAM or ERASE operations, RY/BY# is LOW,

and is High-Z during read mode, auto select mode, and erase suspend mode. After a hardware reset, READ and WRITE operations cannot begin until RY/BY# goes High-Z. (See RESET

AC Specifications for more details.)

The use of an open-drain output enables the RY/BY# pins from several devices to be connected to a single pull-up resistor to VCCQ. A low value will then indicate that one (or more) of

the devices is (are) busy. A 10K Ohm or bigger resistor is recommended as pull-up resistor to

achieve 0.1V VOL.

VCC

Supply

Supply voltage: Provides the power supply for READ, PROGRAM, and ERASE operations.

The command interface is disabled when VCC