256Mb, 512Mb, 1Gb StrataFlash Memory

Features

Micron StrataFlash Embedded Memory

MT28GU256AAA2EGC-0AAT, MT28GU512AAA2EGC-0AAT,

MT28GU01GAAA2EGC-0AAT

Features

• Power

– Core voltage: 1.7– 2.0V

– I/O voltage: 1.7–2.0V

– Standby current: 60μA (TYP) for 512Mb

– Automatic power savings mode

– 16-word synchronous-burst read current: 23mA

(TYP) @ 108 MHz; 24mA (TYP) @ 133 MHz

• Software

– Micron® Flash data integrator (FDI) optimized

– Basic command set (BCS) and extended command set (ECS) compatible

– Common Flash interface (CFI) capable

• Security

– One-time programmable (OTP) space

64 unique factory device identifier bits

2112 user-programmable OTP bits

– Absolute write protection: V PP = GND

– Power-transition erase/program lockout

– Individual zero latency block locking

– Individual block lock-down

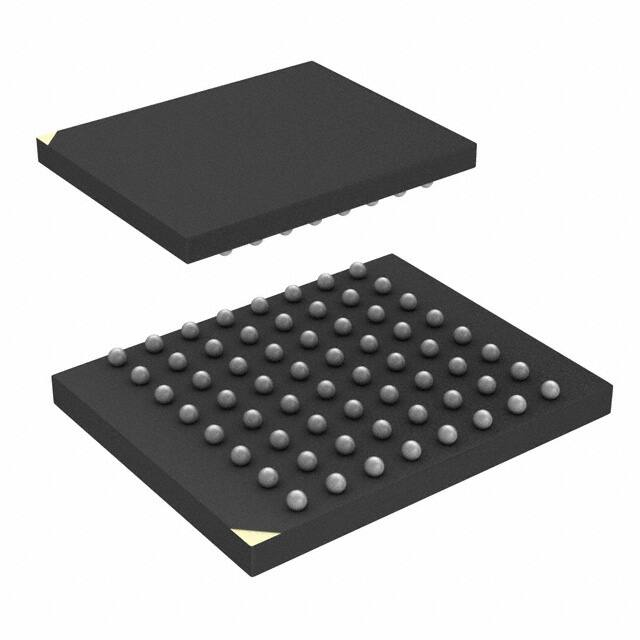

• Density and packaging

– 256Mb, 512Mb, and 1Gb

– Address-data multiplexed interface

– 64-Ball TBGA

• High-performance read, program, and erase

– 106ns initial read access

– 108 MHz with zero wait-state synchronous burst

reads: 7ns clock-to-data output

– 133 MHz with zero wait-state synchronous burst

reads: 6ns clock-to-data output

– 8-, 16-, and continuous-word synchronous-burst

reads

– Programmable WAIT configuration

– Customer-configurable output driver impedance

– Buffered programming: 2.0 μs/word (TYP),

512Mb

– Block erase: 0.9s per block (TYP)

– 20μs (TYP) program/erase suspend

• Architecture

– 16-bit wide data bus

– Multilevel cell technology

– Symmetrically-blocked array architecture

– 256KB erase blocks

– 1Gb device: Eight 128Mb partitions

– 512Mb device: Eight 64Mb partitions

– 256Mb device: Eight 32Mb partitions

– Status register for partition/device status

– Blank check feature

• Quality and reliability

– Automotive temperature: –40°C to +105°C (Grade

2 AEC-Q100)

– Minimum 100,000 ERASE cycles per block

– More than 20 years data retention

– 65nm process technology

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

Part Numbering Information

Devices are shipped from the factory with memory content bits erased to 1. For available options, such as packages or high/low protection, or for further information, contact the factory. Available part numbers can be verified

at www.micron.com. Feature and specification comparison by device type is available at www.micron.com/products. Contact the factory for devices not found.

Figure 1: Current Part Number Decoder

MT 28G U 512 A

A

A

2

GC -0

E

A

AT --

Micron Technology

Production Status

Part Family

Blank = Production

ES = Engineering samples

28G = G series parallel NOR

Voltage

Operating Temperature

U = 1.7–2.0V

AT = –40°C to +105°C (Grade 2 AEC-Q100)

Device Density

256 = 256Mb

512 = 512Mb

01G = 1Gb

Special Options

A = Automotive quality

Stack

A = Single die

Security Features

0 = Standard features

Lithography

65nm = A

Package Codes

GC = 64-ball TBGA, 10 x 8 x 1.2mm

Die Revision

Rev. A = A

Rev. B = B

Rev. C = C

Block Structure

E = Uniform

Interface

2 = x16 A/D MUX

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

Contents

Important Notes and Warnings ......................................................................................................................... 8

General Description ......................................................................................................................................... 8

Functional Overview ........................................................................................................................................ 9

Configuration and Memory Map ..................................................................................................................... 10

Device ID ....................................................................................................................................................... 13

Package Dimensions ....................................................................................................................................... 14

Signal Assignments ......................................................................................................................................... 15

Signal Descriptions ......................................................................................................................................... 16

Bus Interface .................................................................................................................................................. 18

Reset .......................................................................................................................................................... 18

Standby ..................................................................................................................................................... 18

Output Disable ........................................................................................................................................... 18

Asynchronous Read .................................................................................................................................... 19

Synchronous Read ...................................................................................................................................... 19

Burst Wrapping .......................................................................................................................................... 19

End-of-Wordline Delay ............................................................................................................................... 20

Write .......................................................................................................................................................... 21

Command Definitions .................................................................................................................................... 22

Status Register ................................................................................................................................................ 24

Clear Status Register ................................................................................................................................... 25

Read Configuration Register ........................................................................................................................... 26

Programming the Read Configuration Register ............................................................................................ 27

Latency Count Code and Clock Frequency ................................................................................................... 28

Extended Configuration Register ..................................................................................................................... 29

Output Driver Control ................................................................................................................................ 29

Programming the Extended Configuration Register ...................................................................................... 30

Read Operations ............................................................................................................................................. 31

Read Array ................................................................................................................................................. 31

Read ID ...................................................................................................................................................... 31

Read CFI .................................................................................................................................................... 32

Read Status Register ................................................................................................................................... 32

WAIT Operation ......................................................................................................................................... 33

Programming Modes ...................................................................................................................................... 34

Control Mode ............................................................................................................................................. 34

Object Mode .............................................................................................................................................. 35

Program Operations ....................................................................................................................................... 39

Single-Word Programming .......................................................................................................................... 39

Buffered Programming ............................................................................................................................... 40

Buffered Enhanced Factory Programming ................................................................................................... 40

Erase Operations ............................................................................................................................................ 43

BLOCK ERASE ............................................................................................................................................ 43

SUSPEND and RESUME Operations ................................................................................................................ 44

SUSPEND Operation .................................................................................................................................. 44

RESUME Operation .................................................................................................................................... 45

BLANK CHECK Operation .............................................................................................................................. 46

Block Lock ..................................................................................................................................................... 47

One-Time Programmable Operations .............................................................................................................. 49

Programming OTP Area .............................................................................................................................. 51

Reading OTP Area ....................................................................................................................................... 51

Global Main-Array Protection ......................................................................................................................... 52

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

Power and Reset Specifications ....................................................................................................................... 53

Initialization .............................................................................................................................................. 53

Power-Up and Down .................................................................................................................................. 53

Reset .......................................................................................................................................................... 53

Automatic Power Saving ............................................................................................................................. 55

Power Supply Decoupling ........................................................................................................................... 55

Electrical Specifications .................................................................................................................................. 56

Electrical Specifications – DC Current and Voltage Characteristics and Operating Conditions ............................ 57

Electrical Specifications – AC Characteristics and Operating Conditions ........................................................... 60

AC Test Conditions ..................................................................................................................................... 60

AC Read Specifications ................................................................................................................................... 62

AC Read Timing .......................................................................................................................................... 63

AC Write Specifications ................................................................................................................................... 68

Electrical Specifications – Program/Erase Characteristics ................................................................................. 73

Common Flash Interface ................................................................................................................................ 74

READ CFI Structure Output ........................................................................................................................ 74

CFI ID String .............................................................................................................................................. 75

System Interface Information ...................................................................................................................... 75

Device Geometry Definition ....................................................................................................................... 76

Primary Micron-Specific Extended Query .................................................................................................... 78

Program Flowcharts ....................................................................................................................................... 84

Erase Flowcharts ............................................................................................................................................ 92

Block Lock and Protection Flowcharts ............................................................................................................. 96

Blank Check Flowcharts ................................................................................................................................. 100

AADM Mode ................................................................................................................................................. 103

AADM Feature Overview ............................................................................................................................ 103

AADM Mode Enable (RCR[4] = 1) ............................................................................................................... 103

Bus Cycles and Address Capture ................................................................................................................. 103

WAIT Behavior .......................................................................................................................................... 103

Asynchronous READ and WRITE Cycles ..................................................................................................... 104

Asynchronous READ Cycles ....................................................................................................................... 104

Asynchronous WRITE Cycles ..................................................................................................................... 106

Synchronous READ and WRITE Cycles ....................................................................................................... 107

Synchronous READ Cycles ......................................................................................................................... 107

Synchronous WRITE Cycles ....................................................................................................................... 110

System Boot .............................................................................................................................................. 110

Revision History ............................................................................................................................................ 111

Rev. F – 5/18 .............................................................................................................................................. 111

Rev. E – 6/15 .............................................................................................................................................. 111

Rev. D – 4/15 ............................................................................................................................................. 111

Rev. C – 2/15 .............................................................................................................................................. 111

Rev. B – 10/14 ............................................................................................................................................ 111

Rev. A – 12/13 ............................................................................................................................................ 111

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

List of Figures

Figure 1: Current Part Number Decoder ........................................................................................................... 2

Figure 2: 64-Ball TBGA (10mm x 8mm x 1.2mm) – Package Code: GC ............................................................... 14

Figure 3: 64-Ball TBGA (Top View, Balls Down) ............................................................................................... 15

Figure 4: Main Array Word Lines .................................................................................................................... 20

Figure 5: Wrap/No-Wrap Example ................................................................................................................. 20

Figure 6: End-of-Wordline Delay .................................................................................................................... 20

Figure 7: Configurable Programming Regions: Control Mode and Object Mode ............................................... 35

Figure 8: Configurable Programming Regions: Control Mode and Object Mode Segments ................................ 37

Figure 9: BLOCK LOCK Operations ................................................................................................................ 48

Figure 10: OTP Area Map ............................................................................................................................... 50

Figure 11: V PP Supply Connection Example .................................................................................................... 52

Figure 12: RESET Operation Waveforms ......................................................................................................... 54

Figure 13: AC Input/Output Reference Waveform ........................................................................................... 60

Figure 14: Transient Equivalent Testing Load Circuit ....................................................................................... 60

Figure 15: Clock Input AC Waveform .............................................................................................................. 61

Figure 16: Asynchronous Single-Word Read .................................................................................................... 64

Figure 17: Synchronous 8- or 16-Word Burst Read (A/D MUX) ......................................................................... 65

Figure 18: Synchronous Continuous Misaligned Burst Read (A/D MUX) .......................................................... 66

Figure 19: Synchronous Burst with Burst-Interrupt (AD-MUX) ........................................................................ 66

Figure 20: Write Timing ................................................................................................................................. 69

Figure 21: Write to Write (A/D-MUX) ............................................................................................................. 70

Figure 22: Async Read to Write (A/D-MUX) .................................................................................................... 70

Figure 23: Write to Async Read (A/D-MUX) .................................................................................................... 71

Figure 24: Sync Read to Write (A/D-MUX) ...................................................................................................... 71

Figure 25: Write to Sync Read (A/D-MUX) ...................................................................................................... 72

Figure 26: Word Program Flow Chart .............................................................................................................. 84

Figure 27: Word Program Full Status Check Flow Chart ................................................................................... 85

Figure 28: Program Suspend/Resume Flow Chart ........................................................................................... 86

Figure 29: Buffer Programming Flow Chart ..................................................................................................... 88

Figure 30: Buffered Enhanced Factory Programming (BEFP) Flow Chart .......................................................... 90

Figure 31: Block Erase Flowchart .................................................................................................................... 92

Figure 32: Block Erase Full Status Check Flow Chart ........................................................................................ 93

Figure 33: Erase Suspend/Resume Flow Chart ................................................................................................ 94

Figure 34: Block Lock Operations Flow Chart .................................................................................................. 96

Figure 35: Protection Register Programming Flow Chart ................................................................................. 97

Figure 36: Protection Register Programming Full Status Check Flow Chart ....................................................... 99

Figure 37: Blank Check Flow Chart ................................................................................................................ 100

Figure 38: Blank Check Full Status Check Flow Chart ..................................................................................... 102

Figure 39: AADM Asynchronous READ Cycle (Latching A[MAX:0]) ................................................................. 105

Figure 40: AADM Asynchronous READ Cycle (Latching A[15:0] only) .............................................................. 105

Figure 41: AADM Asynchronous WRITE Cycle (Latching A[MAX:0]) ................................................................ 106

Figure 42: AADM Asynchronous WRITE Cycle (Latching A[15:0] only) ............................................................ 107

Figure 43: AADM Synchronous Burst READ Cycle (ADV# De-asserted Between Address Cycles) ....................... 109

Figure 44: AADM Synchronous Burst READ Cycle (ADV# Not De-asserted Between Address Cycles) ................ 109

Figure 45: AADM Synchronous Burst READ Cycle (Latching A[15:0] only) ....................................................... 110

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

List of Tables

Table 1: Main Array Memory Map – 256Mb ....................................................................................................

Table 2: Main Array Memory Map – 512Mb, 1Gb .............................................................................................

Table 3: Device ID Codes ...............................................................................................................................

Table 4: Signal Descriptions ...........................................................................................................................

Table 5: Address Mapping for Address/Data MUX Interface ............................................................................

Table 6: Bus Control Signals ...........................................................................................................................

Table 7: Command Set ..................................................................................................................................

Table 8: Status Register Bit Definitions (Default Value = 0080h) .......................................................................

Table 9: CLEAR STATUS REGISTER Command Bus Cycles ...............................................................................

Table 10: Read Configuration Register Bit Definitions .....................................................................................

Table 11: PROGRAM READ CONFIGURATION REGISTER Bus Cycles ..............................................................

Table 12: Supported Latency and Clock Frequency .........................................................................................

Table 13: Extended Configuration Register Bit Definitions (Default Value = 0004h) ...........................................

Table 14: Output Driver Control Characteristics ..............................................................................................

Table 15: Program Extended Configuration Register Command Bus Cycles ......................................................

Table 16: READ MODE Command Bus Cycles .................................................................................................

Table 17: Device Information .........................................................................................................................

Table 18: WAIT Behavior Summary – A/D MUX ..............................................................................................

Table 19: Programming Region Next State ......................................................................................................

Table 20: PROGRAM Command Bus Cycles ....................................................................................................

Table 21: BEFP Requirements and Considerations ..........................................................................................

Table 22: ERASE Command Bus Cycle ............................................................................................................

Table 23: Valid Commands During Suspend ...................................................................................................

Table 24: SUSPEND and RESUME Command Bus Cycles ................................................................................

Table 25: BLANK CHECK Command Bus Cycles .............................................................................................

Table 26: BLOCK LOCK Command Bus Cycles ................................................................................................

Table 27: Block Lock Configuration ................................................................................................................

Table 28: Program OTP Area Command Bus Cycles .........................................................................................

Table 29: Power Sequencing ...........................................................................................................................

Table 30: Reset Specifications ........................................................................................................................

Table 31: Absolute Maximum Ratings .............................................................................................................

Table 32: Operating Conditions ......................................................................................................................

Table 33: DC Current Characteristics and Operating Conditions (VCCQ = 1.7V-2.0V) .........................................

Table 34: DC Voltage Characteristics and Operating Conditions (V CCQ = 1.7V-2.0V) ..........................................

Table 35: AC Input Requirements ...................................................................................................................

Table 36: Test Configuration Load Capacitor Values for Worst Case Speed Conditions ......................................

Table 37: Capacitance ....................................................................................................................................

Table 38: AC Read Specifications (CLK-Latching, 133 MHz), V CCQ = 1.7V to 2.0V ...............................................

Table 39: AC Write Specifications ...................................................................................................................

Table 40: Program/Erase Characteristics ........................................................................................................

Table 41: Example of CFI Output (x16 Device) as a Function of Device and Mode .............................................

Table 42: CFI Database: Addresses and Sections .............................................................................................

Table 43: CFI ID String ...................................................................................................................................

Table 44: System Interface Information ..........................................................................................................

Table 45: Device Geometry ............................................................................................................................

Table 46: Block Region Map Information ........................................................................................................

Table 47: Primary Micron-Specific Extended Query ........................................................................................

Table 48: One Time Programmable (OTP) Space Information ..........................................................................

Table 49: Burst Read Informaton ....................................................................................................................

Table 50: Partition and Block Erase Region Information ..................................................................................

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

6

10

11

13

16

17

18

22

24

25

26

27

28

29

29

30

31

32

33

38

39

41

43

44

45

46

47

48

49

53

54

56

56

57

59

60

60

61

62

68

73

74

74

75

75

76

77

78

79

80

80

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Features

Table 51:

Table 52:

Table 53:

Table 54:

Table 55:

Table 56:

Table 57:

Table 58:

Table 59:

Table 60:

Table 61:

Table 62:

Table 63:

Table 64:

Table 65:

Table 66:

Table 67:

Table 68:

Partition Region 1 Information: Top and Bottom Offset/Address ....................................................... 81

Partition and Erase Block Map Information ...................................................................................... 83

Word Program Procedure ................................................................................................................ 84

Word Program Full Status Check Procedure ...................................................................................... 85

Program Suspend/Resume Procedure .............................................................................................. 87

Buffer Programming Procedure ....................................................................................................... 89

Buffered Enhanced Factory Programming (BEFP) Procedure ............................................................ 90

Block Erase Procedure ..................................................................................................................... 92

Block Erase Full Status Check Procedure .......................................................................................... 93

Erase Suspend/Resume Procedure .................................................................................................. 95

Block Lock Operations Procedure .................................................................................................... 96

Protection Register Programming Procedure .................................................................................... 98

Protection Register Programming Full Status Check Procedure ......................................................... 99

Blank Check Procedure .................................................................................................................. 100

Blank Check Full Status Check Procedure ........................................................................................ 102

AADM Asynchronous and Latching Timings ................................................................................... 104

AADM Asynchronous Write Timings ............................................................................................... 106

AADM Synchronous Timings .......................................................................................................... 107

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Important Notes and Warnings

Important Notes and Warnings

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document,

including without limitation specifications and product descriptions. This document supersedes and replaces all

information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized

by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims,

costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of

product liability, personal injury, death, or property damage resulting directly or indirectly from any use of nonautomotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron

products are not designed or intended for use in automotive applications unless specifically designated by Micron

as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys'

fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage

resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage

("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the

Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron

component for any critical application, customer and distributor shall indemnify and hold harmless Micron and

its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims,

costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of

product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the

Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems,

applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAILURE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE

WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR

PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included

in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential

damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal

or replacement of any products or rework charges) whether or not such damages are based on tort, warranty,

breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly

authorized representative.

General Description

Micron's 65nm device is the latest generation of StrataFlash® memory. The device provides high-performance, asynchronous read mode and synchronous-burst read mode

using 1.8V low-voltage, multilevel cell (MLC) technology.

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Functional Overview

The device is manufactured using 65nm process technologies and is available in industry-standard chip scale packaging.

Functional Overview

This device provides high read and write performance at low voltage on a 16-bit data

bus. The architecture provides individually erasable memory blocks sized for optimum

code and data storage.

The device supports synchronous burst reads up to 133 MHz using CLK latching.

Upon initial power-up or return from reset, the device defaults to asynchronous read

mode. Configuring the read configuration register enables synchronous burst mode

reads. In synchronous burst mode, output data is synchronized with a user-supplied

clock signal. In continuous-burst mode, a data read can traverse partition boundaries. A

WAIT signal simplifies synchronizing the CPU to the memory.

Designed for low-voltage applications, the device supports READ operations with V CC at

1.8V, and ERASE and PROGRAM operations with V PP at 1.8V or 9.0V. V CC and V PP can be

tied together for a simple, ultra low-power design. In addition to voltage flexibility, a

dedicated V PP connection provides complete data protection when V PP is less than

VPPLK.

A status register provides status and error conditions of ERASE and PROGRAM operations.

One-time programmable (OTP) area enables unique identification that can be used to

increase security. Additionally, the individual block lock feature provides zero-latency

block locking and unlocking to protect against unwanted program or erase of the array.

The device offers power-savings features, including automatic power savings mode and

standby mode. For power savings, the device automatically enters APS following a

READ cycle. Standby is initiated when the system deselects the device by de-asserting

CE#.

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

9

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Configuration and Memory Map

Configuration and Memory Map

The device features a symmetrical block architecture.

The main array of the 256Mb device is divided into eight 32Mb partitions. Each partition is divided into sixteen 256KB blocks (8 x 16 = 128 blocks).

The main array of the 512Mb device is divided into eight 64Mb partitions. Each partition is divided into thirty-two 256KB blocks (8 x 32 = 256 blocks).

The main array of the 1Gb device is divided into eight 128Mb partitions. Each partition

is divided into sixty-four 256KB blocks (8 x 64 = 512 blocks).

Each block is divided into as many as 256 1KB programming regions. Each region is

divided into as many as thirty-two 32-byte segments

Table 1: Main Array Memory Map – 256Mb

Partition

Size

(Mb)

Block #

Address Range

7

32

127

0FE0000-0FFFFFF

.

.

.

.

.

.

112

0E00000-0E1FFFF

111

0DE0000-0DFFFFF

.

.

.

.

.

.

96

0C00000-0C1FFFF

95

0BE0000-0BFFFFF

.

.

.

.

.

.

80

0A00000-0A1FFFF

79

09E0000-09FFFFF

.

.

.

.

.

.

64

0800000-081FFFF

63

07E0000-07FFFFF

.

.

.

.

.

.

48

0600000-061FFFF

6

5

4

3

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

32

32

32

32

10

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Configuration and Memory Map

Table 1: Main Array Memory Map – 256Mb (Continued)

Partition

Size

(Mb)

Block #

Address Range

2

32

47

05E0000-05FFFFF

.

.

.

.

.

.

32

0400000-041FFFF

31

03E0000-03FFFFF

.

.

.

.

.

.

16

0200000-021FFFF

15

01E0000-01FFFFF

.

.

.

.

.

.

0

0000000-001FFFF

1

32

0

32

Table 2: Main Array Memory Map – 512Mb, 1Gb

512Mb

1Gb

Partition

Size

(Mb)

Block #

Address Range

Size

(Mb)

Block #

Address Range

7

64

255

1FE0000-1FFFFFF

128

511

3FE0000-3FFFFFF

.

.

.

.

.

.

.

.

.

.

.

.

224

1C00000-1C1FFFF

448

3800000-381FFFF

223

1BE0000-1BFFFFF

447

37E0000-37FFFFF

.

.

.

.

.

.

.

.

.

.

.

.

192

1800000-181FFFF

384

3000000-301FFFF

191

17E0000-17FFFFF

383

2FE0000-2FFFFFF

.

.

.

.

.

.

.

.

.

.

.

.

160

1400000-141FFFF

320

2800000-281FFFF

6

5

64

64

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

11

128

128

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Configuration and Memory Map

Table 2: Main Array Memory Map – 512Mb, 1Gb (Continued)

512Mb

Partition

Size

(Mb)

Block #

4

64

3

2

1

0

64

64

64

64

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

1Gb

Address Range

Size

(Mb)

Block #

Address Range

159

13E0000-13FFFFF

128

319

27E0000-27FFFFF

.

.

.

.

.

.

.

.

.

.

.

.

128

1000000-101FFFF

256

2000000-201FFFF

127

0FE0000-0FFFFFF

255

1FE0000-1FFFFFF

.

.

.

.

.

.

.

.

.

.

.

.

96

0300000-031FFFF

192

1800000-181FFFF

95

0BE0000-0BFFFFF

191

17E0000-17FFFFF

.

.

.

.

.

.

.

.

.

.

.

.

64

0800000-081FFFF

128

1000000-101FFFF

63

07E0000-07FFFFF

127

0FE0000-0FFFFFF

.

.

.

.

.

.

.

.

.

.

.

.

32

0400000-041FFFF

64

0800000-081FFFF

31

03E0000-03FFFFF

63

07E0000-07FFFFF

.

.

.

.

.

.

.

.

.

.

.

.

0

0000000-001FFFF

0

0000000-001FFFF

12

128

128

128

128

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Device ID

Device ID

Table 3: Device ID Codes

Density

Product

Device Identifier Code (Hex)

256Mb

A/D MUX

8904

512Mb

A/D MUX

8881

1024Mb

A/D MUX

88B1

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

13

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Package Dimensions

Package Dimensions

Figure 2: 64-Ball TBGA (10mm x 8mm x 1.2mm) – Package Code: GC

0.78 TYP

Seating

plane

0.1

1.00 TYP

64X Ø0.43 ±0.1

1.5 ±0.1

8

7

6

5

4

3

2

Ball A0 ID

Ball A0 ID

1

0.5 ±0.1

A

B

C

D

8 ±0.1

E

F

1.00 TYP

G

H

10 ±0.1

1.20 MAX

Note:

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

1. All dimensions are in millimeters.

14

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Signal Assignments

Signal Assignments

Figure 3: 64-Ball TBGA (Top View, Balls Down)

1

2

3

4

5

6

7

8

RFU

RFU

RFU

VPP

RFU

VCC

A17

A21

RFU

VSS

RFU

CE#

RFU

A24

A18

A25

RFU

RFU

RFU

RFU

RFU

WP#

A19

A20

RFU

RFU

RFU

RST#

VCCQ

VCCQ

RFU

A16

A

B

C

D

E

ADQ8 ADQ1 ADQ9 ADQ3 ADQ4 CLK ADQ15 RFU

F

RFU ADQ0 ADQ10 ADQ11 ADQ12 ADV# WAIT

OE#

G

A22

RFU

DQ2

RFU

VSSQ

VCC

VCCQ ADQ5 ADQ6 ADQ14 WE#

H

Notes:

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

VSS

DQ13 VSSQ

DQ7

A23

1. B6 is A24 for 512Mb densities and above; otherwise, it is a no connect (NC).

2. B8 is A25 for 1Gb density; otherwise, it is a no connect (NC).

3. For AA/D MUX configuration, the upper addresses A[MAX;16] must be connected to VSS.

15

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Signal Descriptions

Signal Descriptions

Table 4: Signal Descriptions

Symbol

Type

Description

A[MAX:16]

Input

Address inputs: Upper address inputs for all READ/WRITE cycles.

A/DQ[15:0]

Input/Output

Address inputs or data: Lower address inputs during the address phase for all READ/

WRITE cycles; data or command inputs during WRITE cycles; data, status, or device information outputs during READ cycles.

CE#

Input

Chip enable: LOW true input. When LOW, CE# selects the die; when HIGH, CE# deselects the die and places it in standby.

A/D MUX

Control Signals

OE#

Input

Output enable: LOW true input. Must be LOW for READs and HIGH for WRITEs.

WE#

Input

Write enable: LOW true input. Must be LOW for WRITEs and HIGH for READs.

CLK

Input

Clock: Synchronizes burst READ operations with the host controller.

ADV#

Input

Address valid: LOW true input. When LOW, ADV# enables address inputs. For synchronous burst READs, address inputs are latched on the rising edge.

WP#

Input

Write protect: LOW true input. When LOW, WP# enables block lock down; when

HIGH, WP# disables block lock down.

RST#

Input

Reset: LOW true input. When LOW, RST# inhibits all operations; must be HIGH for

normal operations.

VPP

Input

Erase/program voltage: Enables voltage for PROGRAM and ERASE operations. Array

contents cannot be altered when VPP is at or below VPPLK.

WAIT

Output

WAIT: Configurable HIGH or LOW true output. When asserted, WAIT indicates

DQ[15:0] is invalid; when de-asserted, WAIT indicates DQ[15:0] is valid.

VCC

Power

Core power: Supply voltage for core circuits. All operations are inhibited when VCC is

at or below VLKO.

VCCQ

Power

I/O power: Supply voltage for all I/O drivers. All operations are inhibited when VCCQ is

at or below VLKOQ.

VSS

Power

Logic ground: Core logic ground return. Connect all VSS balls to system ground; do

not float any VSS balls.

VSSQ

Power

I/O ground: I/O driver ground return. Connect all VSSQ balls to system ground; do not

float any VSSQ balls.

RFU

Reserved

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

Reserved: Reserved for future use and should not be connected.

16

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Signal Descriptions

Table 5: Address Mapping for Address/Data MUX Interface

Address Bit

A/D MUX

Configuration

(RCR Bit 4 = 0) and OE# = 1

AADM Mode

(RCR Bit 4 = 1) and OE# = 1

AADM Mode

(RCR Bit 4 = 1) and OE# = 0

A0

DQ0

A0

A16

A1

DQ1

A1

A17

A2

DQ2

A2

A18

A3

DQ3

A3

A19

A4

DQ4

A4

A20

A5

DQ5

A5

A21

A6

DQ6

A6

A22

A7

DQ7

A7

A23

A8

DQ8

A8

A24

A9

DQ9

A9

A25

A10

DQ10

A10

–

A11

DQ11

A11

–

A12

DQ12

A12

–

A13

DQ13

A13

–

A14

DQ14

A14

–

A15

DQ15

A15

–

A16

A16

–

–

A17

A17

–

–

A18

A18

–

–

A19

A19

–

–

A20

A20

–

–

A21

A21

–

–

A22

A22

–

–

A23

A23

–

–

A24

A24

–

–

A25

A25

–

–

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

17

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Bus Interface

Bus Interface

The bus interface uses CMOS-compatible address, data, and bus control signals for all

bus WRITE and bus READ operations. The address signals are input only, the data signals are input/output (I/O), and the bus control signals are input only. The address inputs are used to specify the internal device location during bus READ and bus WRITE

operations. The data I/Os carry commands, data, or status to and from the device. The

control signals are used to select and deselect the device, indicate a bus READ or bus

WRITE operation, synchronize operations, and reset the device.

Do not float any inputs. All inputs must be driven or terminated for proper device operation. Some features may use additional signals. See Signal Descriptions for descriptions of these signals.

The following table shows the logic levels that must be applied to the bus control signal

inputs for the bus operations listed.

Table 6: Bus Control Signals

X = Don’t Care; High = VIH; Low = VIL

Bus Operations

RST#

CE#

CLK

ADV#

OE#

WE#

Address

Data I/O

RESET

LOW

X

X

X

X

X

X

High-Z

STANDBY

HIGH

HIGH

X

X

X

X

X

High-Z

OUTPUT DISABLE

HIGH

X

X

X

HIGH

X

X

High-Z

Asynchronous

READ

HIGH

LOW

X

LOW

LOW

HIGH

Valid

Output

Synchronous READ

HIGH

LOW

Running

Toggle

LOW

HIGH

Valid

Output

WRITE

HIGH

LOW

X

X

HIGH

LOW

Valid

Input

Reset

RST# LOW places the device in reset, where device operations are disabled; inputs are

ignored, and outputs are placed in High-Z.

Any ongoing ERASE or PROGRAM operation will be aborted and data at that location

will be indeterminate.

RST# HIGH enables normal device operations. A minimum delay is required before the

device is able to perform a bus READ or bus WRITE operation. See AC specifications.

Standby

RST# HIGH and CE# HIGH place the device in standby, where all other inputs are ignored, outputs are placed in High-Z (independent of the level placed on OE#), and power

consumption is substantially reduced.

Any ongoing ERASE or PROGRAM operation continues in the background and the device draws active current until the operation has finished.

Output Disable

When OE# is de-asserted with CE# asserted, the device outputs are disabled. Output

pins are placed in High-Z. WAIT is de-asserted.

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

18

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Bus Interface

Asynchronous Read

For RCR15 = 1 (default), CE# LOW and OE# LOW place the device in asynchronous bus

read mode:

•

•

•

•

RST# and WE# must be held HIGH; CLK must be tied either HIGH or LOW.

Address inputs must be held stable throughout the access, or latched with ADV#.

ADV# must be held LOW or can be toggled to latch the address.

Valid data is output on the data I/Os after tAVQV, tELQV, tVLQV, or tGLQV, whichever is

satisfied last.

Asynchronous READ operations are independent of the voltage level on V PP.

Synchronous Read

For RCR15 = 0, CE# LOW, OE# LOW, and ADV# LOW place the device in synchronous

bus read mode:

•

•

•

•

RST# and WE# must be held HIGH.

CLK must be running.

The first data word is output tCHQV after the latency count has been satisfied.

For array reads, the next address data is output tCHQV after valid CLK edges until the

burst length is satisfied.

• For nonarray reads, the same address data is output tCHQV after valid CLK edges until

the burst length is satisfied.

The address for synchronous read operations is latched on the ADV# rising edge or the

first rising CLK edge after ADV# LOW, whichever occurs first for devices that support up

to 108 MHz. For devices that support up to 133 MHz, the address is latched on the last

CLK edge when ADV# is LOW.

Burst Wrapping

Data stored within the memory array is arranged in rows or word lines. During synchronous burst reads, data words are sensed in groups from the array. The starting address

of a synchronous burst read determines which word within the wordgroup is output

first, and subsequent words are output in sequence until the burst length is satisfied.

The setting of the burst wrap bit (RCR3) determines whether synchronous burst reads

will wrap within the wordgroup or continue on to the next wordgroup.

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

19

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Bus Interface

Figure 4: Main Array Word Lines

16-Word sense group

16-bit data word

0x000030

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

0x000020

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

0x000010

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

0x000000

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

Word

lines

Address

Bit lines

256 bits

Figure 5: Wrap/No-Wrap Example

16-bit data word

2

3

4

5

6

7

8

9 A B

2

3

4

5

6

7

8

9 A B

Wrap

No wrap

End-of-Wordline Delay

Output delays may occur when the burst sequence crosses the first end-of-wordline

boundary onto the start of the next wordline.

No delays occur if the starting address is sense-group aligned or if the burst sequence

never crosses a wordline boundary. However, if the starting address is not sense-group

aligned, the worst-case end-of-wordline delay is one clock cycle less than the initial access latency count used. This delay occurs only once during the burst access. WAIT informs the system of this delay when it occurs.

Figure 6: End-of-Wordline Delay

0x000020

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

0x000010

0

1

2

3

4

5

6

7

8

9 A B

C

D

E

F

EOWL delay

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

20

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Bus Interface

Write

CE# LOW and WE# LOW place the device in bus write mode, where RST# and OE# must

be HIGH, CLK and ADV# are ignored, input data and address are sampled on the rising

edge of WE# or CE#, whichever occurs first.

During a WRITE operation in MUX devices, address is latched during the rising edge of

ADV# OR CE# whichever occurs first and data is latched during the rising edge of WE#

OR CE# whichever occurs first.

Bus WRITE cycles are asynchronous only.

The following conditions apply when a bus WRITE cycle occurs immediately before, or

immediately after, a bus READ cycle:

• When transitioning from a bus READ cycle to a bus WRITE cycle, CE# or ADV# must

toggle after OE# goes HIGH.

• When in synchronous read mode (RCR15 = 0; burst clock running), bus WRITE cycle

timings tVHWL (ADV# HIGH to WE# LOW), tCHWL (CLK HIGH to WE# LOW), and

tWHCH (WE# HIGH to CLK HIGH) must be met.

• When transitioning from a bus WRITE cycle to a bus READ cycle, CE# or ADV# must

toggle after WE# goes HIGH.

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

21

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Command Definitions

Command Definitions

Commands are written to the device to control all operations. Some commands are

two-cycle commands that use a SETUP and a CONFIRM command; other commands

are single-cycle commands that use only a SETUP command followed by a data READ

cycle or data WRITE cycle. Valid commands and their associated command codes are

shown in the table below.

Table 7: Command Set

Command

Code

(Setup/Confirm)

Description

Register Operations

PROGRAM READ CONFIGURATION REGISTER

0060h/0003h

Programs the read configuration register. The desired read configuration register value is placed on the address bus, and written to the read configuration register when the CONFIRM command is issued.

PROGRAM EXTENDED CONFIGURATION REGISTER

0060h/0004h

Programs the extended configuration register. The desired extended configuration register value is placed on the address bus,

and written to the read configuration register when the CONFIRM command is issued.

PROGRAM OTP AREA

00C0h

Programs OTP area and OTP lock registers. The desired register

data is written to the addressed register on the next WRITE cycle.

CLEAR STATUS REGISTER

0050h

Clears all error bits in the status register.

READ ARRAY

00FFh

Places the addressed partition in read array mode. Subsequent

reads outputs array data.

READ STATUS REGISTER

0070h

Places the addressed partition in read status mode. Subsequent

reads outputs status register data.

READ ID

0090h

Places the addressed partition in read ID mode. Subsequent

reads from specified address offsets output unique device information.

READ CFI

0098h

Places the addressed partition in read CFI mode. Subsequent

reads from specified address offsets output CFI data.

0041h

Programs a single word into the array. Data is written to the array on the next WRITE cycle. The addressed partition automatically switches to read status register mode.

00E9h/00D0h

Initiates and executes a BUFFERED PROGRAM operation. Additional bus READ/WRITE cycles are required between the and

confirm commands to properly perform this operation. The addressed partition automatically switches to read status register

mode.

Read Mode Operations

Array Programming Operations

SINGLE-WORD PROGRAM

BUFFERED PROGRAM

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

22

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Command Definitions

Table 7: Command Set (Continued)

Command

BUFFERED ENHANCED FACTORY

PROGRAM

Code

(Setup/Confirm)

Description

0080h/00D0h

Initiates and executes a BUFFERED ENHANCED FACTORY PROGRAM operation. Additional bus READ/WRITE cycles are required after the CONFIRM command to properly perform this

operation. The addressed partition automatically switches to

read status register mode.

0020h/00D0h

Erases a single, addressed block. The ERASE operation commences when the CONFIRM command is issued. The addressed partition automatically switches to read status register mode.

Lock Block

0060h/0001h

Sets the lock bit of the addressed block.

Unlock Block

0060h/00D0h

Clears the lock bit of the addressed block.

Lock-Down Block

0060h/002Fh

Sets the lock-down bit of the addressed block.

Block Erase Operations

BLOCK ERASE

Security Operations

Other Operations

SUSPEND

00B0h

Initiates a suspend of a PROGRAM or BLOCK ERASE operation

already in progress when issued to any device address

SR[6] = 1 indicates erase suspend

SR[2] = 1 indicates program suspend

RESUME

00D0h

Resumes a suspended PROGRAM or BLOCK ERASE operation

when issued to any device address. A program suspend nested

within an erase suspend is resumed first.

00BCh/00D0h

Performs a blank check of an addressed block. The addressed

partition automatically switches to read status register mode.

BLANK CHECK

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

23

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Status Register

Status Register

The status register is a 16-bit, read-only register that indicates device status, region status, and operating errors. Upon power-up or exit from reset, the status register defaults

to 0080h (device ready, no errors).

The status register has status bits and error bits. Status bits are set and cleared by the

device; error bits are only set by the device. Error bits are cleared using the CLEAR STATUS REGISTER command or by resetting the device.

To read from the status register, first issue the READ STATUS REGISTER command and

then read from the device. Note that some commands automatically switch from read

mode to read status register mode.

Table 8: Status Register Bit Definitions (Default Value = 0080h)

Bit

Name

15:10

Reserved

9:8

Partition program error

7

Device status

0 = Device is busy; SR[9,8,6:1] are invalid, SR[0] is valid

1 = Device is ready; SR[9:8], SR[6:1] are valid

6

Erase suspend

0 = Erase suspend not in effect

1 = Erase suspend in effect

5:4

Erase error/blank check error

program error

(command sequence

error)

3

VPP error

2

Program suspend

1

Block lock error

0 = Block not locked during program or erase; operation successful

1 = Block locked during program or erase; operation aborted

0

Partition status

SR[7]/SR[0]

0 0 = Active PROGRAM or ERASE operation in addressed partition

BEFP: Program or verify complete, or ready for data

0 1 = Active PROGRAM or ERASE operation in other partition

BEFP: Program or Verify in progress

1 0 = No active PROGRAM or ERASE operation in any partition

BEFP: Operation complete

1 1 = Reserved

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

Description

Reserved for future use; these bits will always be set to zero

SR[9]/SR[8]

0 0 = Region program successful

1 0 = Region program error: Attempted write with object data to control

mode region

0 1= Region-program error: Attempted rewrite to object mode region

1 1 = Region-program error: Attempted write using illegal command

(SR[4] will also be set along with SR[8,9] for the above error conditions)

SR[5]/SR[4]

0 0 = PROGRAM or ERASE operation successful

0 1 = Program error: operation aborted

1 0 = Erase error: Operation aborted; Blank check error: Operation failed

1 1 = Command sequence error: Command aborted

0 = VPP within acceptable limits during program or erase

1 = VPP < VPPLK during program or erase; operation aborted

0 = Program suspend not in effect

1 = Program suspend in effect

24

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Status Register

Clear Status Register

The status register has status bits and error bits. Status bits are set and cleared by the

device; error bits are only set by the device. Error bits are cleared using the CLEAR STATUS REGISTER command or by resetting the device.

Note: Care should be taken to avoid status register ambiguity. If a command sequence

error occurs while in erase suspend, SR[5:4] will be set, indicating a command sequence

error. When the ERASE operation is resumed (and finishes), any errors that may have

occurred during the ERASE operation will be masked by the command sequence error.

To avoid this situation, clear the status register prior to resuming any suspended ERASE

operation.

The CLEAR STATUS REGISTER command functions independent of the voltage level on

VPP. Issuing the CLEAR STATUS REGISTER command places the addressed partition in

read status register mode. Other partitions are not affected.

Table 9: CLEAR STATUS REGISTER Command Bus Cycles

Command

CLEAR STATUS

REGISTER

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

Setup WRITE Cycle

Address Bus

Setup WRITE Cycle

Data Bus

Device address

0050h

25

Confirm WRITE Cycle Confirm WRITE Cycle

Address Bus

Data Bus

–

–

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Read Configuration Register

Read Configuration Register

The read configuration register is a volatile, 16-bit read/write register used to select bus

read modes and to configure synchronous burst read behavior of the device.

The read configuration register is programmed using the PROGRAM READ CONFIGURATION REGISTER command. To read the read configuration register, issue the READ

ID command and then read from offset 0005h.

Upon power-up or exit from reset, the read configuration register defaults to asynchronous mode (RCR15 = 1; all other bits are ignored).

Table 10: Read Configuration Register Bit Definitions

Bit

Name

15

Read mode

Description

14:11

Latency count

0 0 1 1 = Code 3

0 1 0 0 = Code 4

0 1 0 1 = Code 5

0 1 1 0 = Code 6

0 1 1 1 = Code 7

1 0 0 0 = Code 8

1 0 0 1 = Code 9

1 0 1 0 = Code 10

1 0 1 1 = Code 11

1 1 0 0 = Code 12

1 1 0 1 = Code 13

1 1 1 0 = Code 14

Other bit settings are reserved; see the table below for supported

clock frequencies

10

WAIT polarity

0 = WAIT signal is LOW-true

1 = WAIT signal is HIGH-true

0 = Synchronous burst mode

1 = Asynchronous mode (default)

9

Reserved

8

WAIT delay

7:5

Reserved

Write 0 to reserved bits

4

Bus interface

0 = A/D MUX (default)

1 = AA/D MUX

3

Reserved

Write 0 to reserved bits

2:0

Burst length

CCMTD-1725822587-2936

MT28GUxxxAAA2EGC-0AAT.pdf - Rev. F 5/18 EN

Write 0 to reserved bits

0 = WAIT de-asserted with valid data

1 = WAIT de-asserted one clock cycle before valid data

0 1 0 = 8-word burst, wrap only

0 1 1 = 16-word burst, wrap only

1 1 1 = Continuous-burst: linear, no-wrap only

Other bit settings are reserved

26

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2013 Micron Technology, Inc. All rights reserved.

�256Mb, 512Mb, 1Gb StrataFlash Memory

Read Configuration Register

Programming the Read Configuration Register

The read configuration register is programmed by issuing the PROGRAM READ CONFIGURATION REGISTER command. The desired RCR[15:0] settings are placed on

A[15:0], while the PROGRAM READ CONFIGURATION REGISTER SETUP command is

placed on the data bus. Upon issuing the SETUP command, the read mode of the addressed partition is automatically changed to read status register mode.

Next, the CONFIRM command is placed on the data bus while the desired settings for

RCR[15:0] are again placed on A[15:0]. Upon issuing the CONFIRM command, the read

mode of the addressed partition is automatically switched to read array mode.

Because the desired read configuration register value is placed on the address bus, any

hardware-connection offsets between the host’s address outputs and the device’s address inputs must be taken into account. For example, if the host’s address outputs are

aligned to the device’s address inputs such that host address bit A1 is connected to address bit A0, the desired register value must be left-shifted by one (for example, 2532h