MP5611

2.9V to 5.2V Input, Triple-Output,

AMOLED Display Power Supply

DESCRIPTION

FEATURES

The MP5611 is a triple-output converter across

a 2.9 to 5.2V input voltage (VIN) range designed

for small-size AMOLED (active matrix organic

light-emitting diode) display power supplies.

•

•

•

•

•

The MP5611 integrates a boost converter for

ELVDD, an inverting buck-boost (IBB) converter

for ELVSS, and another boost converter for

AVDD. The one wire digital control pin (CTRL)

can program the ELVSS, ELVDD, and AVDD

voltages following digital protocol.

2.9 to 5.2V Input Voltage (VIN) Range

Triple Output AVDD, ELVDD, ELVSS

High Accuracy for Output Voltage (VOUT)

Good Line and Load Regulation

Configurable VELVDD = 4.6V to 5.2V, Default

4.6V

Configurable VELVSS = -1.4V to -6.4V,

Default -4V

500mA Output Current (IOUT) for ELVDD and

ELVSS

Configurable VAVDD = 5V to 7.7V, Default

5.8V

100mA IOUT for AVDD

Respective Enable for AVDD and ELVDD

Soft Start (SS)

Active Fast Discharge Function

Cycle-by-Cycle Current Limit Protection

AVDD Output Over-Current Protection

(OCP) 90mA to 270mA

ELVDD Output OCP 80mA to 650mA

Output Short-to-GND Protection

Over-Temperature Protection (OTP)

Available in a TQFN-16 (3mmx3mm)

Package

•

•

•

The MP5611 supports an independent start-up

sequence for AVDD and ELVDD via the

separated enable pins (EN_AVDD and CTRL). It

also integrates an optional fast discharge

function after the IC has been disabled.

•

•

•

•

•

•

The device features rich protections, including

VIN under-voltage lockout (UVLO), cycle-bycycle current limit protection, thermal shutdown

protection, short output protection, and overcurrent protection (OCP) for AVDD and ELVDD.

•

•

•

•

The fully integrated synchronous rectification

solution with low on resistance improves total

system

efficiency,

minimizes

external

components, and reduces PCB layout size.

APPLICATIONS

The MP5611 is available in a TQFN-16

(3mmx3mm) package.

•

•

AMOLED Smartphones

AMOLED Displays

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive.

For MPS green status, please visit the MPS website under Quality

Assurance. “MPS,” the MPS logo, and “Simple, Easy Solutions” are

trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

TYPICAL APPLICATION

L3 10µH

L1 4.7µH

VIN

C1

SW1

PVIN

AVIN

SW3

AVDD

AVDD

C4

AGND

ELVDD

PGND2

ELVDD

EN

C2

EN_AVDD

CTRL

CTRL

FD

FD

CT

5.8V

100mA

PGND1

MP5611

4.6V

500mA

FB

ELVSS

ELVSS

L2 4.7µH C3

-4V

500mA

SW2

C5

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

1

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

ORDERING INFORMATION

Part Number*

MP5611GQT

Package

TQFN-16 (3mmx3mm)

Top Marking

See Below

MSL Rating

1

* For Tape & Reel, add suffix -Z (e.g. MP5611GQT-Z).

TOP MARKING

BKH: Product code

Y: Year code

LLL: Lot number

PACKAGE REFERENCE

TOP VIEW

PIN 1 ID

AVIN

16

SW3 PGND2 AVDD

15

14

13

SW1

1

12

PVIN

PGND1

2

11

SW2

ELVDD

3

10

ELVSS

4

9

FB

5

6

FD

CT

7

CTRL

8

AGND EN_AVDD

EXPOSED PAD

CONNECT TO AGND

TQFN-16 (3mmx3mm)

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

2

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

PIN FUNCTIONS

Pin #

Name

1

2

3

4

SW1

PGND1

ELVDD

FB

5

FD

6

7

CT

AGND

8

9

10

11

12

13

EN_AVDD

CTRL

ELVSS

SW2

PVIN

AVDD

14

PGND2

15

SW3

16

AVIN

Exposed pad

Description

Switching node of the ELVDD boost converter.

Power ground of the ELVDD boost converter.

Output of the ELVDD boost converter.

Feedback. ELVDD output voltage (VOUT) sense pin.

Fast discharge enable and disable during shutdown. Pull this pin high to enable fast

discharge.

ELVSS transition time configured pin.

Analog ground.

AVDD boost converter enable pin. Pull this pin high to enable the AVDD converter.

Digital control. This pin also enables the ELVDD and ELVSS converter.

Output of the ELVSS inverting buck-boost (IBB) converter.

Switching node of the ELVSS IBB converter.

Power supply of the ELVSS IBB converter.

Output of the AVDD boost converter.

Power ground of the AVDD boost converter.

Switching node of the AVDD boost converter.

Power supply for internal circuit.

Exposed pad. Connect this pin to AGND.

ABSOLUTE MAXIMUM RATINGS (1)

VIN, SW1 ..................................... -0.3V to +5.3V

SW3, AVDD ................................. -0.3V to +10V

ELVSS ........................................ -7.5V to +0.3V

SW2............................................ -7.5V to +5.3V

All other pins ............................... -0.3V to +5.3V

Junction temperature ............................... 150°C

Lead temperature .................................... 260°C

Storage temperature ................ -65°C to +150°C

Continuous power dissipation (TA = 25°C) (2)

TQFN-16 (3mmx3mm) ...............................2.1W

ESD Ratings

Human body model (HBM) ..................... ±1.5kV

Charged device model (CDM).................... ±2kV

Thermal Resistance (4)

θJA

θJC

TQFN-16 (3mmx3mm)……..….60…...12...°C/W

Notes:

1) Exceeding these ratings may damage the device.

2) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-toambient thermal resistance θJA, and the ambient temperature

TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ

(MAX) – TA) / θJA. Exceeding the maximum allowable power

dissipation can generate an excessive die temperature, which

may cause the regulator to go into thermal shutdown. Internal

thermal shutdown circuitry protects the device from permanent

damage.

3) The device is not guaranteed to function outside of its operating

conditions.

4) Measured on JESD51-7, 4-layer PCB.

Recommended Operating Conditions (3)

Supply voltage (VIN) ....................... 2.9V to 5.2V

Operating junction temp (TJ) .... -40°C to +125°C

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

3

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

ELECTRICAL CHARACTERISTICS

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, TA = -40°C to +85°C, unless otherwise noted.

Parameter

General

Operating input voltage

Shutdown current

Quiescent supply current

Input under-voltage

lockout (UVLO) threshold

Input UVLO hysteresis

EN_AVDD/FD high

voltage

EN_AVDD/FD low voltage

EN_AVDD pull-down

resister

Over-temperature

protection (OTP)

threshold (5)

Thermal protection

hysteresis (5)

Boost Converter ELVDD

ELVDD voltage

ELVDD voltage variation

Low-side MOSFET

(LS-FET) on resistance

High-side MOSFET

(HS-FET) on resistance

Switching frequency

Current limit

Output over-current

protection (OCP)

threshold

Short protection threshold

Short protection detection

time

ELVDD sense threshold

Feedback (FB) sense

threshold

ELVDD/FB leakage

current

FB pull-down resister

Active discharge

resistance

Load regulation (5)

Line regulation (5)

MP5611 Rev. 1.0

12/16/2021

Symbol

VIN

ISD

IQ

VIN_UVLO

Condition

Min

Typ

2.9

EN_AVDD = CTRL = 0V

VIN = 3.7V, ELVDD switching

0.1

1.6

Rising edge

Max

Units

5.2

3

V

μA

mA

2.65

V

300

VEN_HIGH

Rising VEN

VEN_LOW

Falling VEN

mV

1.35

V

0.4

V

RDOWN

500

kΩ

TSD

150

°C

25

°C

4.6

VELVDD

TA = 25°C, no load

-40°C to +85°C, no load

-0.5

-0.8

+0.5

+0.8

V

%

%

RON_LS_ELVDD

ISW1 = 200mA

160

mΩ

RON_HS_ELVDD

ISW1 = 200mA

320

mΩ

1.35

1.5

MHz

A

IOCP_ELVDD = 650mA

650

mA

During operation

80

%

During operation

1

ms

fSW1

ILIMIT1

IOCP_ELVDD

VTELVDD

Increasing ELVDD-FB

350

mV

VTFB

Decreasing ELVDD-FB

250

mV

ILEAKAGE

CTRL = FD = 0V

RDOWN_FB

RDS_ELVDD

CTRL = 0V, IELVDD = 1mA

1mA < IELVDD < 300mA

2.9V < VIN < 4.3V, IELVDD = 200mA

2.9V < VIN < 5.2V, IELVDD = 200mA

5

μA

4

MΩ

75

Ω

0.2

0.015

1.5 (6)

%/A

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

%/V

4

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

ELECTRICAL CHARACTERISTICS (continued)

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, TA = -40°C to +85°C, unless otherwise noted.

Parameter

Symbol

Buck-Boost Converter ELVSS

ELVSS default output

voltage (VOUT)

ELVSS VOUT range

VELVSS

ELVSS regulation

LS-FET on resistance

HS-FET on resistance

Switching frequency

Current limit

Short protection threshold

at start-up

Short protection threshold

during operation

Short protection detection

time

ELVSS leakage current

ELVSS discharge

resistance

CT output impedance

CT comparator

Load regulation (5)

RON_LS_ELVSS

RON_HS_ELVSS

fSW2

ILIMIT2

MP5611 Rev. 1.0

12/16/2021

Min

Typ

Max

-4

V

200

350

1.7

3

V

mV

mV

mΩ

mΩ

MHz

A

At start-up

250

mV

Voltage drop from normal ELVSS

600

mV

At start-up

During operation

CTRL = FD = 0V

12.5

1

0.01

ms

ms

μA

CTRL = 0V, IELVSS = 1mA

150

TA = 25°C, no load

-40°C to +85°C, no load

ISW2 = 200mA

ISW2 = 200mA

-6.4

-30

-50

Units

2

-1.4

+30

+50

VELVSS_SCP

tSCP2

ILEAKAGE

RDC_ELVSS

RCT

130

1mA < IELVSS < 300mA

2.9V < VIN < 5.2V, IELVSS = 200mA

2.9V < VIN < 5.2V, IELVSS = 200mA

with an external rectifier diode

Line regulation (5)

Boost Converter AVDD

AVDD default voltage

AVDD voltage range

AVDD regulation

LS-FET on resistance

HS-FET on resistance

Switching frequency

Current limit

Output OCP threshold

Short protection threshold

Short protection detection

time

AVDD leakage current

Active discharge

resistance

Load regulation (5)

Line regulation (5)

Condition

300

50

1.5

0.45

5

Ω

490

kΩ

mV

%/A

%/V

0.08 (7)

5.8

500

1400

1.35

0.5

210

90

V

V

%

mΩ

mΩ

MHz

A

mA

%

During operation

1

ms

ILEAKAGE

CTRL = FD = 0V

2.8

RDS_AVDD

CTRL = 0V, IAVDD = 1mA

30

Ω

0.08

0.015

%/A

%/V

VAVDD

RON_LS_AVDD

RON_HS_AVDD

fSW3

ILIMIT3

IOCP_AVDD

-40°C to +85°C, no load

ISW3 = 200mA

ISW3 = 200mA

IOCP_AVDD = 210mA

During operation

1mA < IAVDD < 100mA

2.9V < VIN < 5.2V, IAVDD = 50mA

5

-1

7.7

+1

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

5.6

μA

5

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

ELECTRICAL CHARACTERISTICS (continued)

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, TA = -40°C to +85°C, unless otherwise noted.

Parameter

CTRL Interface

Logic high voltage

Logic low voltage

Pull-down resistor

Initialization time

Shutdown period (5)

Pulse high-level period (5)

Pulse low-level period (5)

Data storage and

acceptance period (5)

Symbol

Condition

Min

VH

VL

R

tINIT

tOFF

tHIGH

tLOW

1.35

tSTORE

30

Typ

Max

470

80

25

25

V

V

kΩ

μs

μs

μs

μs

80

μs

0.4

500

340

30

2

2

10

10

Units

Notes:

5) Guaranteed by characterization. Not tested in production.

6) When VIN is between 4.3V and 4.5V, ELVDD line regulation increases since VIN is close to ELVDD’s VOUT.

7) To improve ELVSS line regulation in heavy load when VIN < 3.5V, use an external Schottky diode as a rectifier between ELVSS and SW2.

TIMING DIAGRAM

tLOW tHIGH

CTRL

tINIT

tOFF

tSTORE

10ms

4.6V

VELVDD

VELVSS

tSET

-4V

-6.2V

Figure 1: Digital Interface (CTRL) Timing Diagram

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

6

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, L1 = L2 = 4.7µH, L3 = 10µH, TA = 25°C, unless otherwise noted.

ELVDD & ELVSS Efficiency vs.

Load Current

100

98

96

94

92

90

88

86

84

82

80

0

50

100

ELVDD & ELVSS EFFICIENCY (%)

AVDD EFFICIENCY (%)

AVDD Efficiency vs. Load Current

100

95

90

85

80

75

70

65

60

55

50

0

100

200

LOAD CURRENT (mA)

LOAD CURRENT (mA)

ELVDD Load Regulation

AVDD Load Regulation

4.7

OUTPUT VOLTAGE (V)

5.82

OUTPUT VOLTAGE (V)

300

5.81

5.8

5.79

5.78

5.77

5.76

4.65

4.6

4.55

4.5

5.75

0

50

LOAD CURRENT (mA)

0

100

100

200

LOAD CURRENT (mA)

300

SWITCHING FREQUENCY (MHz)

Switching Frequency vs. VIN

OUTPUT VOLTAGE (V)

ELVSS Load Regulation

-3.8

-3.85

-3.9

-3.95

-4

-4.05

-4.1

-4.15

-4.2

-4.25

-4.3

0

MP5611 Rev. 1.0

12/16/2021

100

200

LOAD CURRENT (mA)

300

2

ILOAD_ELVDD = 100mA,

ILOAD_ELVSS = 100mA,

ILOAD_AVDD = 50mA

1.8

1.6

1.4

FSW_AVDD

FSW_ELVDD

FSW_ELVSS

1.2

1

2.9

3.9

INPUT VOLTAGE (V)

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

4.9

7

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, L1 = L2 = 4.7µH, L3 = 10µH, TA = 25°C, unless otherwise noted.

EVLDD and ELVSS Start-Up

AVDD Start-Up

ILOAD = 0mA

ILOAD = 0mA

CH1:

EN_AVDD

CH1: CTRL

CH2: AVDD

CH2: ELVDD

CH3: ELVSS

CH3:

VSW_AVDD

CH4: IIN

CH4: IIN

ELVDD Steady State

ELVDD Steady State

ILOAD = 100mA

ILOAD = 300mA

CH2:

ELVDD (AC)

CH2:

ELVDD (AC)

CH3:

CH3:

VSW_ELVDD

VSW_ELVDD

CH4: IL_ELVDD

CH4: IL_ELVDD

ELVSS Steady State

ELVSS Steady State

ILOAD = 100mA

ILOAD = 300mA

CH2:

ELVSS (AC)

CH2:

ELVSS (AC)

CH3:

VSW_ELVSS

CH3:

VSW_ELVSS

CH4: IL_ELVSS

CH4: IL_ELVSS

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

8

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, L1 = L2 = 4.7µH, L3 = 10µH, TA = 25°C, unless otherwise noted.

AVDD Steady State

AVDD Steady State

ILOAD = 20mA

ILOAD = 50mA

CH2:

AVDD (AC)

CH2:

AVDD (AC)

CH3:

VSW_AVDD

CH3:

VSW_AVDD

CH4: IL_AVDD

CH4: IL_AVDD

ELVDD Load Transient Response

ELVSS Load Transient Response

ILOAD = 10mA to 100mA in 180µs

ILOAD = 10mA to 100mA in 180µs

CH4: ILOAD

CH4: ILOAD

CH2:

ELVDD (AC)

CH2:

ELVSS (AC)

AVDD Load Transient Response

AVDD Short to GND Protection

during Normal Operation

ILOAD = 30mA to 50mA in 180µs

CH1:

VSW_AVDD

CH4: ILOAD

CH2: AVDD

CH2:

AVDD (AC)

CH3: ILOAD

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

9

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 3.7V, VELVDD/ELVSS/AVDD = default, L1 = L2 = 4.7µH, L3 = 10µH, TA = 25°C, unless otherwise noted.

ELVDD Short to GND Protection

during Normal Operation

ELVSS Short to GND Protection

during Normal Operation

CH1:

VSW_ELVSS

CH1:

VSW_ELVDD

CH2: ELVSS

CH2: ELVDD

CH3: ILOAD

CH3: ILOAD

ELVDD Short to ELVSS Protection

during Normal Operation

CH1:

VSW_ELVSS

CH2: ELVDD

CH4: ELVSS

CH3: ILOAD

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

10

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

FUNCTIONAL BLOCK DIAGRAM

VIN

SW 3

SW 1

AVIN

AVDD

ELVDD

LDO

Driver

Driver

Output

Sense

FB

OCP

PWM

Control

PWM

Control

AVDD

VREF

DAC

ELVDD

ELVDD

ELVSS

OSC

I AVDD- OCP

CTRL

CTRL

EN _ AVDD

VREF

ELVSS

Protection

CT

CT

Control

Control

DAC

FD

Fast

Discharge

CTRL

Driver

50 mV

Digital

Interface

PVIN

CTRL

ELVSS

AGND

SW 2

PGND 1

PGND 2

Figure 2: Functional Block Diagram

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

11

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

OPERATION

The MP5611 is a triple-output converter

designed for small-size AMOLED (active matrix

organic light-emitting diode) display power

supplies. It integrates a boost converter for

ELVDD, an inverting buck-boost (IBB) converter

for ELVSS, and another boost converter for

AVDD. The one wire digital control pin (CTRL)

can program the ELVSS, ELVDD, and AVDD

voltages following digital protocol.

Feedback (FB) Connection for ELVDD

If the FB pin is floating or tied to GND, or (VELVDD

- VFB) > 350mV, then the ELVDD boost

converter’s output voltage (VOUT) is sensed via

the ELVDD pin directly. To improve the ELVDD

VOUT sense performance, externally connect FB

VIN

to the main ELVDD output capacitor’s positive

terminal. In this case, when (VELVDD - VFB) <

250mV, VOUT is sensed via FB pin with better

sense accuracy.

Fast Discharge Function

Pull the FD pin high to enable the active fast

discharge function when the MP5611 shuts

down. By connecting FD to GND, all outputs are

high-impedance when the IC shuts down. When

FD is pulled high, the fast discharge function can

also be disabled by applying 81 pulses to the

CTRL pin.

Figure 3 shows the start-up/shutdown sequence,

where the solid line is with active discharge

enabled and the dotted line is without active

discharge enabled.

UVLO

UVLO

EN_AVDD

~1.5ms

AVDD

5.8V

CTRL

~0.5ms

4.6V

ELVDD

ELVSS

10ms

10ms

~0.5ms -4V

Figure 3: Start-Up/Shutdown Sequence with and without Active Discharge Enable

Configuring the ELVSS Transition Time

When ELVSS is controlled by the CTRL pulse,

the voltage transition time can be configured by

the capacitor on the CT pin (CEXTERNAL), which

can be estimated using Equation (1):

2. CTRL is also ELVDD and ELVSS’s enable

signal. Once CTRL pulls high, ELVDD starts

up to the default value. After 10ms, ELVSS

establishes to its default value (see the

Timing Diagram section on page 6).

t (µs) = 3 x RINTERNAL (kΩ) x CEXTERNAL (nF) (1)

The reset information for ELVSS, ELVDD, and

AVDD follows:

Where RINTERNAL = 300kΩ. CEXTERNAL e.g. 100nF

is about 90ms of the transition time.

Digital Interface (CTRL)

The CTRL pin has two functions:

1. CTRL is the digital interface that configures

the output of ELVSS, ELVDD, and AVDD, as

well as the output over-current (OC) limit.

The number of pulse signal’s rising edges

applied on the CTRL pin is counted for

configuring the corresponding item to a

certain value (see Table 1 on page 13).

MP5611 Rev. 1.0

12/16/2021

•

A power cycle resets all settings to default.

•

CTRL is low, and lasts for a set time to reset

ELVDD and ELVSS to the default value.

•

EN_AVDD can enable/disable AVDD.

•

EN_AVDD and CTRL are both pulled low to

reset AVDD and all registers to the default

value.

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

12

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

Table 1: CTRL Configuration Table

Pulse #

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

ELVSS

-6.4V

-6.3V

-6.2V

-6.1V

-6V

-5.9V

-5.8V

-5.7V

-5.6V

-5.5V

-5.4V

-5.3V

-5.2V

-5.1V

-5V

-4.9V

-4.8V

-4.7V

-4.6V

-4.5V

-4.4V

-4.3V

-4.2V

-4.1V

-4V

-3.9V

-3.8V

-3.7V

Pulse #

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

29

-3.6V

Pulse #

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

-3.5V

-3.4V

-3.3V

-3.2V

-3.1V

-3V

-2.9V

-2.8V

-2.7V

-2.6V

-2.5V

-2.4V

-2.3V

-2.2V

-2.1V

-2V

-1.9V

-1.8V

-1.7V

-1.6V

-1.5V

-1.4V

0

80

81

Pulse #

0

82

83

Pulse #

0

84

85

86

87

88

89

90

Pulse #

0

91

92

93

94

MP5611 Rev. 1.0

12/16/2021

AVDD

+5V

+5.1V

+5.2V

+5.3V

+5.4V

+5.5V

+5.6V

+5.7V

+5.8V

+5.9V

+6V

+6.1V

+6.2V

+6.3V

+6.4V

+6.5V

+6.6V

+6.7V

+6.8V

+6.9V

+7V

+7.1V

+7.2V

+7.3V

+7.4V

+7.5V

+7.6V

+7.7V

VOUT Fast

Discharge

Controlled by FD

On

Off

250mV Detection

Off

On

Off

ELVDD

4.6V

4.6V

4.7V

4.8V

4.9V

5V

5.1V

5.2V

OCP (ELVDD)

650mA

80mA

175mA

270mA

365mA

Pulse #

95

96

97

Pulse #

0

98

99

100

101

102

103

104

OCP (ELVDD)

460mA

555mA

650mA

OCP (AVDD)

210mA

90mA

120mA

150mA

180mA

210mA

240mA

270mA

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

13

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

Diode Mode when VIN ≈ ELVDD

When the input voltage (VIN) is close to ELVDD,

the MP5611 operates in diode mode. In this

mode, the ELVDD boost converter’s high-side

MOSFET (HS-FET) is disabled, and its body

diode operates as a rectifier to regulate VOUT.

Note that the converter must work in continuous

conduction mode (CCM) to achieve proper

output regulation in diode mode.

ELVDD Over-Current Protection (OCP)

The MP5611 supports ELVDD over-current

protection (OCP). If EVDD’s output current (IOUT)

exceeds 650mA (default) or the threshold

configured via the CTRL signal, and lasts for

1ms, then OCP is triggered and the IC shuts

down until CTRL or the power resets.

AVDD OCP

The MP5611 supports AVDD OCP. When

AVDD’s IOUT exceeds 210mA (default) or the

threshold configured via the CTRL signal, and

lasts for 1ms, then OCP is triggered and the IC

shuts down until EN_AVDD or the power resets.

Short Output Voltage (VOUT) Protection

The MP5611 features complete short protection

functions, including AVDD, ELVDD, ELVSS

short to GND protection, as well as ELVDD short

to LEVSS protection.

The conditions required for the short protection

functions follow:

1. If ELVDD does not reach its regulated

voltage within 10ms after ELVDD is enabled

(CTRL = high), all output voltages shut down

MP5611 Rev. 1.0

12/16/2021

(for ELVDD short to GND protection at startup).

2. If ELVSS does not reach its regulated

voltage within 12.5ms after ELVSS is

enabled (22.5ms after CTRL = high), all

output voltages shut down (for ELVSS short

to GND protection at start-up).

3. If ELVSS > 250mV when ELVSS is enabled

(10ms after CTRL = high), ELVDD and

ELVSS shut down, and AVDD operates

normally (for ELVDD short to ELVSS

protection).

4. If AVDD decreases to 90% of its configured

voltage for 1ms, all output voltages shut

down (for AVDD short to GND protection

during operation).

5. If ELVDD decreases to 80% of its configured

voltage for 1ms, all output voltages shut

down (for ELVDD short to GND protection

during operation).

6. If ELVSS increases to >600mV for 1ms, all

output voltages shut down (for ELVSS short

to GND protection during operation).

Thermal Shutdown

To prevent the IC from operating at exceedingly

high temperatures, thermal shutdown is

implemented by monitoring the silicon die

temperature. When the die temperature exceeds

the upper threshold (TST), the IC shuts down.

Once the die temperature drops below the lower

threshold, the IC restarts and resumes normal

operation. The hysteresis is 25°C.

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

14

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

APPLICATION INFORMATION

Selecting the Inductor

It is recommended to use the ELVDD and

ELVSS converters with 4.7μH inductors, and the

AVDD boost converter with a 10μH inductor (see

Table 2).

voltage ripple. Generally, the lower IOUT, the

lower the required capacitance. It is

recommended to use ceramic capacitors with

X5R or X7R dielectrics for their low ESR and

small temperature coefficients.

For a given inductance, the inductor DC current

rating should be at least 40% greater than the

maximum input peak inductor current for most

applications. The inductor’s DC resistance

should be as small as possible for higher

efficiency.

Optional ELVSS External Rectifier Diode

Using an external Schottky diode as a rectifier for

ELVSS can be beneficial for improving ELVSS

line regulation in heavy load when VIN < 3.5V. If

necessary, a B0530WS Schottky diode in an

SOD-323 package is sufficient. Connect this

diode between ELVSS and SW2 (see the dotted

box in Figure 4 on page 16).

Selecting the Capacitor

Table 2 shows the recommended capacitors.

Lower capacitance may lead to increased

Table 2: Recommended Inductors and Capacitors

Ref

LSW1, LSW2

LSW3

CIN

CO_AVDD, CO_ELVDD

CO_ELVSS

CCT

MP5611 Rev. 1.0

12/16/2021

Value

4.7µH

10µH

3 x 10µF

10µF

2 x 10µF

100nF

Manufacturer

Coilcraft

Coilmaster

Murata

Murata

Murata

Murata

Manufacturer PN

XFL4020-4R7ML

MMPP252012-100N

GRM21BR71A106KE51

GRM21BR71A106KE51

GRM21BR71A106KE51

GRM155B11A104KA01

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

15

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

PCB Layout Guidelines

Efficient PCB layout and placement of the highfrequency switching path are critical to prevent

noise and electromagnetic interference (EMI).

For the best results, refer to Figure 4 and follow

the guidelines below:

4. Use short and wide traces to connect the

output capacitors on AVDD, ELVDD, and

ELVSS.

5. Connect the CT capacitor’s negative terminal

directly to the AGND pin.

6. Keep the loop between SW2, L2, the PVIN

input capacitor, the ELVSS output capacitor,

and GND as short as possible due to the

high-frequency pulse current.

1. Place the input capacitors on PVIN and AVIN

as close as possible to the device.

2. Place the output capacitors on AVDD,

ELVDD, and ELVSS as close as possible to

the device.

7. Connect the IC’s exposed thermal pad to

AGND, PGND1, and PGND2.

3. Use short and wide traces to connect the

input capacitors on PVIN and AVIN.

AVDD

L3

13 AVDD

SW1 1

GND

12 PVIN C5

L2

11 SW2

C6

D1

10 ELVSS

PGND1 2

C3

ELVDD 3

FB 4

EN_AVDD 8

C8

AGND 7

CT 6

9

FD 5

ELVDD

GND

C4

CTRL

C7

ELVSS

L1

15 SW3

16 AVIN

C1

14 PGND2

VIN

VIN

C2

Top

Bottom

Figure 4: Recommended PCB Layout

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

16

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

TYPICAL APPLICATION CIRCUIT

Figure 5: Typical Application Circuit

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

17

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

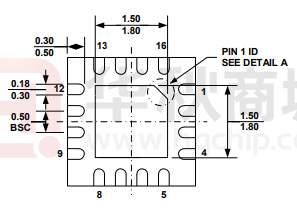

PACKAGE OUTLINE DRAWING FOR 16L TQFN (3x3mm)

PACKAGE INFORMATION

MF-PO-D-0041

revision 0.0

TQFN-16 (3mmx3mm)

2.90

3.10

1.50

1.80

0.30

0.50

PIN 1 ID

MARKING

0.18

0.30

2.90

3.10

PIN 1 ID

INDEX AREA

13

16

12

PIN 1 ID

SEE DETAIL A

1

1.50

1.80

0.50

BSC

4

9

5

8

TOP VIEW

BOTTOM VIEW

PIN 1 ID OPTION A

0.30x45º TYP.

PIN 1 ID OPTION B

R0.20 TYP.

0.70

0.80

0.20 REF

0.00

0.05

DETAIL A

SIDE VIEW

2.90

NOTE:

1.70

0.70

0.25

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

4) DRAWING CONFORMS TO JEDEC MO-220, VARIATION WEED-4.

5) DRAWING IS NOT TO SCALE.

0.50

RECOMMENDED LAND PATTERN

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

18

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

CARRIER INFORMATION

Pin1

1

1

ABCD

1

1

ABCD

ABCD

ABCD

Feed Direction

Part Number

MP5611GQT-Z

MP5611 Rev. 1.0

12/16/2021

Package

Description

TQFN-16

(3mmx3mm)

Quantity/

Reel

Quantity/

Tube

Quantity/

Tray

Reel

Diameter

Carrier

Tape Width

Carrier

Tape Pitch

5000

N/A

N/A

13in

12mm

8mm

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

19

�MP5611 – 2.9V TO 5.2V INPUT, TRIPLE-OUTPUT, AMOLED POWER SUPPLY

REVISION HISTORY

Revision #

Revision Date

1.0

12/16/2021

Description

Pages Updated

Initial Release

-

Notice: The information in this document is subject to change without notice. Please contact MPS for current specifications.

Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS

products into any application. MPS will not assume any legal responsibility for any said applications.

MP5611 Rev. 1.0

12/16/2021

MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2021 MPS. All Rights Reserved.

20

�