MP6003

Monolithic Flyback/SEPIC

DC-DC Converter

The Future of Analog IC Technology

DESCRIPTION

FEATURES

The MP6003 is a monolithic flyback DC-DC

converter which includes a 150V power switch

and is capable of delivering up to 15W output

power. It can also be used for SEPIC boost and

Flyback and Forward applications.

•

•

•

•

•

•

•

•

•

•

•

•

•

The MP6003 uses the fixed-frequency peak

current mode primary controller architecture. It

has an internal soft-start, auto-retry, and

incorporates over current, short circuit, and

over-voltage protection. The MP6003 can also

skip cycles to maintain zero load regulation.

It has a direct optocoupler interface which

bypasses the internal error amplifier when an

isolated output is desired.

The MP6003 is ideal for telecom applications,

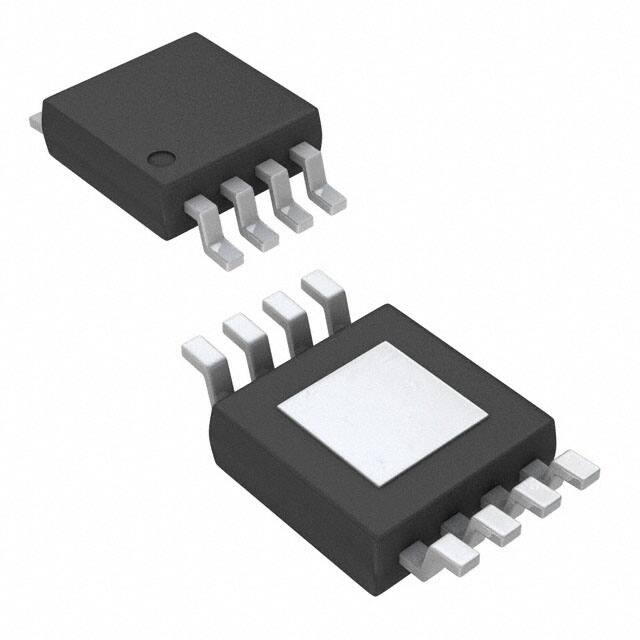

and is available in a compact, thermally

enhanced SOIC8 package with an exposed pad.

Integrated 0.9Ω 150V Power Switch

Cycle-by-Cycle Current Limiting

Programmable Switching Frequency

Duty Cycle Limiting with Line Feed Forward

Integrated 100V Startup Circuit

Internal Slope Compensation

Disable Function

Built-in Soft-Start

Line Under Voltage Lockout

Line Over Voltage Protection

Auto-Restart for Opened/Shorted Output

Zero Load Regulation

Thermal Shutdown

APPLICATIONS

•

•

•

Telecom Equipment

VoIP Phones, Power over Ethernet (PoE)

Distributed Power Conversion

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green

status, please visit MPS website under Products, Quality Assurance page.

“MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

TYPICAL APPLICATION

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

1

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

ORDERING INFORMATION

Part Number*

Package

Top Marking

Free Air Temperature (TA)

MP6003DN

SOIC8E

MP6003

-40°C to +85°C

* For Tape & Reel, add suffix –Z (eg. MP6003DN–Z).

For RoHS compliant packaging, add suffix –LF (eg. MP6003DN–LF–Z)

PACKAGE REFERENCE

TOP VIEW

GND

1

8

SW

LINE

2

7

VIN

FB

3

6

VCC

COMP

4

5

RT

ABSOLUTE MAXIMUM RATINGS (1)

Thermal Resistance

VSW ..............................................-0.5V to +180V

VIN ..............................................-0.3V to +120V

All Other Pins ...............................-0.3V to +6.5V

Continuous Power Dissipation… (TA = +25°C) (2)

……………………………………………......2.5W

Junction Temperature ...............................150°C

Lead Temperature ....................................260°C

Storage Temperature............... -65°C to +150°C

SOIC8E .................................. 50 ...... 10... °C/W

Recommended Operating Conditions

(3)

Supply Voltage VCC ...........................4.5 V to 6V

Output Voltage VSW .....................-0.5V to +150V

Input Voltage VIN .........................+10V to +100V

Maximum Junction Temp. (TJ) ................+125°C

MP6003 Rev. 1.01

1/26/2014

(4)

θJA

θJC

Notes:

1) Exceeding these ratings may damage the device.

2) The maximum allowable power dissipation is a function of the

maximum junction temperature TJ (MAX), the junction-toambient thermal resistance θJA, and the ambient temperature

TA. The maximum allowable continuous power dissipation at

any ambient temperature is calculated by PD (MAX) = (TJ

(MAX)-TA)/θJA. Exceeding the maximum allowable power

dissipation will cause excessive die temperature, and the

regulator will go into thermal shutdown. Internal thermal

shutdown circuitry protects the device from permanent

damage.

3) The device is not guaranteed to function outside of its

operating conditions.

4) Measured on JESD51-7 4-layer board.

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

2

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

ELECTRICAL CHARACTERISTICS

VCC = 5.0V, VLINE = 1.8V, RT = 10k, TA = +25°C, unless otherwise noted.

Parameter

Quiescent Supply Current

Line OV Threshold Voltage

Line OV Hysteresis

Line UV Threshold Voltage

Line UV Hysteresis

VCC Upper Threshold Voltage

VCC Lower Threshold Voltage

VCC Over Voltage Threshold

Voltage

Feedback Voltage

Feedback Input Current

Error Amplifier Gain Bandwidth (5)

Error Amplifier DC Gain (5)

Comp Output Source Current

Comp Output Sink Current

Switch-On Resistance

Switch Leakage Current

Minimum Oscillating Frequency

Maximum Oscillating Frequency

Thermal Shutdown (5)

Thermal Shutdown Hysteresis (5)

Current Limit (5)

Startup Current

Symbol Condition

ICC

1.2V < VLINE < 3.2V, VFB = 1.3V

VCC = 5.0V

VCC = 5.0V

VCC = 5.0V

VCC = 5.0V

VFB

IFB

GBW

AV

IOH

IOL

RON

ILK

FMIN

FMAX

ILIM

Ist

Min

5.7

4.30

Typ

1.0

3

300

1.21

100

6.0

4.50

6.3

4.70

Units

mA

V

mV

V

mV

V

V

6.3

6.6

6.9

V

1.16

1.21

50

1.26

V

nA

MHz

dB

mA

mA

Ω

µA

kHz

kHz

°C

°C

mA

mA

2.85

1.16

VFB = 1.2V

Max

1.5

3.15

1.26

1

60

VFB = 1.0V, VCOMP = 0.5V

VFB = 1.4V, VCOMP = 2.5V

VSW = 0.1V

VSW = 180V

RT = 100k

RT = 10k

6.5

3.3

0.9

1

550

VIN = 20V, VCC = 4.0V

60

550

150

30

700

6.5

Note:

5) Guaranteed by design, not production tested.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

3

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS

Performance waveforms are tested on the evaluation board of the Design Example section.

VIN = 36V, VOUT = 5V, IOUT = 1A, TA = 25ºC, unless otherwise noted.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

4

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board of the Design Example section.

VIN = 36V, VOUT = 5V, IOUT = 1A, TA = 25ºC, unless otherwise noted.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

5

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

PIN FUNCTIONS

Pin #

1

2

3

4

5

6

7

8

Name Description

GND

LINE

Ground. Power return and reference node.

UV/OV Set Point. Short to ground to turn the controller off.

Regulation Feedback Input. Inverting input of the error amplifier. The non-inverting is internally

FB

connected to 1.2V

COMP Error Amplifier Output.

Oscillator Resistor and Synchronous Clock Pin. Connect an external resistor to GND for

RT

oscillator frequency setting. It can be used as a synchronous input from external oscillator clock.

VCC Supply Bias Voltage. A capacitor no less than 1uF is recommended to connect between GND.

VIN High Voltage Startup Circuit Supply.

Output Switching Node. High voltage power N-Channel MOSFET drain output. The internal

SW

start bias current is supplied from this pin.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

6

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

OPERATION

The MP6003 uses programmable fixedfrequency, peak current-mode PWM with a

single-ended primary architecture to regulate

the output voltage. The MP6003 incorporates

features such as protection circuitry and an

integrated high voltage power switch into a

small 8-pin SOIC. This product targets high

performance, cost effective DC-DC converter

applications.

6 VCC

+

6.5V

4.5V

-LINE 2

+

3.0V

1.2V

OVLO

--

REGULATOR

IBIAS

REF

+

STARTUP

UVLO

--

7 VIN

8 SW

THERMAL

MONITOR

COMP 4

ERROR

AMPLIFIER

1.2V

FB 3

+

--

EA

--

+

PWM

COMPARATOR

SOFT-START

CURRENT LIMIT

CLOCK

RT 5

CONTROL

LOGIC

1 GND

-+

CURRENT LIMIT

COMPARATOR

+

1.0V

--

OSC

SLOPE

COMP

Σ

LEB

CURRENT SENSE

Figure 1—Functional Block Diagram

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

7

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

High Voltage Startup

The MP6003 features a 100V startup circuit,

see Figure 1. When power is applied, the

capacitor at the VCC pin is charged through the

VIN pin. When the voltage at the VCC pin

crosses 6.0V without fault, the controller is

enabled. The VCC pin is then disconnected

from the VIN pin and VCC voltage is discharged

via the operating current. When VCC drops to

4.5V, the VCC pin is reconnected to the VIN pin

and VCC will be recharged. The voltage at the

VCC pin repeats this ramp cycle between 4.5V

and 6.0V. VIN needs to be higher than 10V in

order to keep high voltage startup circuit

working properly. This can be guaranteed by

setting input UVLO ≥ 10V. It is also

recommended that the capacitor at VCC pin be

no less than 1uF to achieve stable operation.

The VCC pin can be powered with a voltage

higher than 4.5V from an auxiliary winding to

reduce the power dissipated in the internal

start-up circuit. The VCC pin is internally

clamped at 8V.

Under-Voltage and Over-Voltage Detection

The MP6003 includes a line monitor circuit.

Two external resistors form a voltage divider

from the input voltage to GND; its tap connects

to the LINE pin. The controller is operational

when the voltage at the UV/OV pin is between

1.2V and 3V. When the voltage at the UV/OV

pin goes out of this operating range, the

controller is disabled and goes into standby

mode. The LINE pin can also be used as a

remote enable. Grounding the UV/OV pin will

disable the controller.

Error Amplifier

The MP6003 includes an error amplifier with its

non-inverting input connected to internal 1.2V

reference voltage. The regulated voltage is fed

back through a resistor network or an

optocoupler to the FB pin. Figure 2 shows some

common error amplifier configurations.

6 VCC

D1

1.2V

C1

+

EA

--

R1

FB

COMP

3

4

C2

PRIMARY

WINDING

R3

C3

R2

(a) Using Primary winding to provide feedback

6 VCC

1.2V

+

EA

--

C2

COMP

FB

3

4

R3

R2

(b) Feedback is from Secondary (Common Collector)

Figure 2—Error Amplifier Configurations

Synchronize Programmable Oscillator

The MP6003 oscillating frequency is set by an

external resistor from the RT pin to ground. The

value of RT can be calculated from:

RT = 10kΩ ×

550kHz

fS

The MP6003 can be synchronized to an

external clock pulse. The frequency of the clock

pulse must be higher than the internal oscillator

frequency. The clock pulse width should be

within 50ns to 150ns. The external clock can be

coupled to the RT pin with a 100pF capacitor

and a peak level greater than 3.5V.

Duty Cycle Limiting with Line Feed Forward

The MP6003 has a DMAX (maximum duty cycle)

limit at 67.5% when the LINE pin voltage is

equal to 1.3V. As VLINE increases, DMAX reduces.

Maximum duty cycle can be calculated by:

⎡

⎤

2 .7 V

D MAX = ⎢

⎥ × 100%

⎣ 2.7 V + VLINE ⎦

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

8

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

Limiting the duty cycle at high line voltage

protects against magnetic saturation and

minimizes the output sensitivity to line

transients.

Auto-Restart

When VCC is biased from an auxiliary winding

and an open loop condition occurs, the voltage

at the VCC pin increases to 6.5V. When VCC

crosses the threshold voltage, the auto-restart

circuit turns off the power switch and puts the

controller in standby mode. When VCC drops to

4.5V, the startup switch turns on to charge VCC

up again. When VCC crosses 6.0V, the switch

turns off and the standby current discharges

VCC back to 4.5V. After repeating the ramp

cycles between the two threshold voltages 15

times, the auto-restart circuit is disabled and the

controller begins soft-start.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

9

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

APPLICATION INFORMATION

Switching Frequency

The frequency (fS), has big effects on the

selection of the transformer (Tr), the output cap,

(C2), and the input cap, (C1). The higher the

frequency, the smaller the sizes for Tr, C2, and

C1. However, a higher frequency also leads to

higher AC power losses in the power switch,

control circuitry, transformer, and in the external

interconnection. The general rule states that

lower the output power, higher the optimum

switching frequency. For low current (>

1

fS

Input Capacitor

The input capacitors (C1) are chosen based

upon the AC voltage ripple on the input

capacitors, RMS current ratings, and voltage

rating of the input capacitors.

MP6003 Rev. 1.01

1/26/2014

Output Filter

The simplest filter is an output capacitor (C2),

whose capacitance is determined by the output

ripple requirement.

The current waveform in the output capacitor is

mostly in rectangular shape. The full load

current is drawn from the capacitors during the

primary switch on time. The worse case for the

output ripple occurs under low line and full load

conditions. The ripple voltage can be estimated

by:

ΔV0 −PP −C = IO ×

D

C2 × f S

ESR also needs to be specified for the output

capacitors. This is due to the step change in D2

current results in a ripple voltage that is

proportional to the ESR. Assuming that the D2

current waveform is in rectangular shape, the

ESR requirement is then obtained by given the

output ripple voltage.

ΔVO −PP _ RESR =

IO × ESR

(1 − D)

The total ripple voltage can be estimated by:

ΔVO −PP = ΔVO −PP −C + ΔVO −PP _ ESR

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

13

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

Control Design

Generally, some of power supplies require the

galvanic isolation between a relatively high

input voltage and low output voltages. The most

widely used devices to transfer signals across

the isolation boundary are pulse transformers

and optocouplers.

VIN

RESR

CO

+

--

d

L1

22μ F/2.5A

VIN

1

VCC

3

R5

--

LINE

VIN

8

7

FB

COMP

VCC

RT

6

C4

10μ F

16V

5

R6

63.4kΩ

C3

10nF

R2 C1

R3

--

SW

R3

10kΩ

R1

R6

GND

R2

200kΩ

+

VREF

R4

TL431

Rb

Figure 7—Simplified Circuit of Isolated

Power Supply with Optocoupler Feedback

The MP6003 uses current mode control to

achieve easy compensation and fast transient

response. A type II compensation network

which has two poles and one zero is needed to

stabilize

the

system.

The

practical

compensation parameters are provided in the

EVQ6003DN datasheet.

180V

20mA

MP6003

R5

1.5kΩ

4

S

+

C2

1μ F

200V

2

RLOAD

D1

200V/1A

C1

10μ F

25V

R4

10kΩ

VO

D

Tr

Boost Controller Application Design

Example 2

The MP6003 can be used as a boost controller

as shown in Figure 8.

R1

60.4Ω

Figure 8—High Voltage LED Boost

Controller Circuit

Design Example

This design example shows an flyback topology

for industrial application. It has wide input

voltage rang from 36V to 80V and 5V output.

4

1

3

2

2

1

3

Figure 9—Reference Design Circuit for Flyback Application

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

14

�MP6003 – MONOLITHIC FLYBACK/SEPIC DC-DC CONVERTER

PACKAGE INFORMATION

SOIC8E

0.189(4.80)

0.197(5.00)

8

0.124(3.15)

0.136(3.45)

5

0.150(3.80)

0.157(4.00)

PIN 1 ID

1

0.228(5.80)

0.244(6.20)

0.089(2.26)

0.101(2.56)

4

TOP VIEW

BOTTOM VIEW

SEE DETAIL "A"

0.013(0.33)

0.020(0.51)

0.051(1.30)

0.067(1.70)

SEATING PLANE

0.000(0.00)

0.006(0.15)

0.0075(0.19)

0.0098(0.25)

SIDE VIEW

0.050(1.27)

BSC

FRONT VIEW

0.010(0.25)

x 45o

0.020(0.50)

GAUGE PLANE

0.010(0.25) BSC

0.050(1.27)

0.024(0.61)

0o-8o

0.016(0.41)

0.050(1.27)

0.063(1.60)

DETAIL "A"

0.103(2.62)

0.213(5.40)

NOTE:

0.138(3.51)

RECOMMENDED LAND PATTERN

1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN

BRACKET IS IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

OR PROTRUSIONS.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING)

SHALL BE 0.004" INCHES MAX.

5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

6) DRAWING IS NOT TO SCALE.

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications.

Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS

products into any application. MPS will not assume any legal responsibility for any said applications.

MP6003 Rev. 1.01

1/26/2014

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2014 MPS. All Rights Reserved.

15

�