MP8864

High-Efficiency, 4 A, 21 V, Synchronous

Step-Down Converter with I2C Interface

DESCRIPTION

FEATURES

The MP8864 is a high-frequency, synchronous,

rectified, step-down, switch-mode converter

with an I2C control interface. It offers a very

compact solution to achieve a 4 A continuous

output current with excellent load and line

regulation over a wide input supply range. The

MP8864 has synchronous-mode operation for

higher efficiency over the output load range.

The reference voltage level is controlled,

on-the-fly through a 3.4 Mbps I2C serial

interface. The voltage range can be adjusted

from 0.6 V to 1.87 V in 10 mV steps. Also, the

voltage slew rate, switching frequency, enable,

and power-saving mode are selectable through

the I2C interface.

Current-mode operation provides fast transient

response and eases loop stabilization. Full

protection

features

include

over-current

protection (OCP), over-voltage protection

(OVP), and thermal shutdown (TSD).

Wide 4.5 V to 21 V Operation Input Range

50 mΩ/23 mΩ Low RDS(ON) Internal Power

MOSFETs

1% VOUT Accuracy

I2C Programmable Reference Voltage

Range from 0.6 V to 1.87 V in 10 mV Steps

with Slew-Rate Control

I2C Selectable Switching Frequency. Default

600 kHz Switching Frequency

Programmable Output Voltage

Power-Saving Mode, OTP, and OCP via I2C

Power Good Indication

1-Bit I2C Address Set Pin

OCP in Hiccup Mode

External Soft-Start

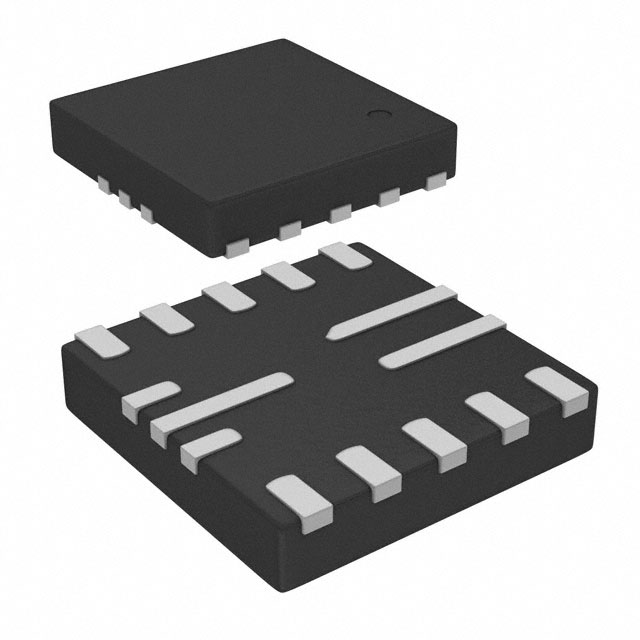

Available in a QFN 3mm x 3mm Package

APPLICATIONS

The MP8864 requires a minimal number of

readily available, standard external components

and is available in a 15-pin QFN15

(3mm x 3mm) package.

SoC and Media Processors

General Consumer

Distributed Power Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For

MPS green status, please visit the MPS website under Quality Assurance.

“MPS” and “The Future of Analog IC Technology” are registered trademarks of

Monolithic Power Systems, Inc.

TYPICAL APPLICATION

R8

10 Ω

VIN

4.5 V-21 V

C4

0.1 uF L1

BST

VIN

1 uH

SW

VOUT

C2

22 uF x 2

R9

100 kΩ

FB

EN

EN/SYNC

VCC

C1

0.22 μF

PG

MP8864

SDA

SCL

ADD

SS

R4

100 kΩ

PG

AGND

MP8864 Rev. 1.02

1/18/2018

R3

33 kΩ

PGND

1.2 V/4 A

R1

34 kΩ

VOUT

C5

47 uF

R2

34 kΩ

SDA

SCL

C7

22 nF

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

1

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

ORDERING INFORMATION

Part Number

MP8864GQ*

EVKT-8864

Package

QFN-15 (3mm x 3mm)

Evaluation Kit

Top Marking

See Below

*For Tape & Reel, add suffix –Z (e.g. MP8864GQ–Z);

TOP MARKING

APE: Product code of MP8864GQ

Y: Year code

LLL: Lot number

EVALUATION KIT EVKT-8864

EVKT-8864 Kit contents: (Items below can be ordered separately).

#

1

Part Number

EV8864-Q-00A

2

EVKT-USBI2C-02

3

Tdrive-8864

Item

MP8864GQ evaluation board

Includes one USB to I2C dongle, one USB cable, and one

ribbon cable

USB Flash drive that stores the GUI installation file and

supplemental documents

Quantity

1

1

1

Order direct from MonolithicPower.com or our distributors.

Input Power

Supply

Input

GUI

USB Cable

Ribbon Cable

USB to I2C Dongle

EV8864-Q-00A

Output

Load

Figure 1: EVKT-8864 Evaluation Kit Set-Up

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

2

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

PACKAGE REFERENCE

TOP VIEW

AGND VCC

15

VIN

PGND

14

SS

FB

VOUT

13

12

11

10

BST

9

SW

8

PGND

1

2

3

4

EN/SYNC PG

5

6

7

SDA

SCL

ADD

QFN-15 (3mm x 3mm)

ABSOLUTE MAXIMUM RATINGS (1)

Thermal Resistance (6)

VIN …………………………….. ...... -0.3 V to 22 V

VSW…………………………………-0.3 V(-5 V for

UVLO), the chip starts up to an output

voltage that is set by the FB feedback resistors

with a programmed soft-start time; then the I2C

bus can communicate with the master. If the

chip does not receive the I2C communication

signal continuously, it works efficiently through

FB feedback and performs similar to traditional

non-I2C parts.

Once the I2C receives valid output reference

voltage scaling instruction (if V_BOOT=“1”), the

output voltage is determined by the resistor

dividers R1, R2, and the VREF voltage. The VOUT

value can be calculated using equation (2). The

VREF default value is 0.6 V:

VOUT VREF (1

R1

)

R2

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

(2)

16

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

If V_BOOT=“0,” the output voltage is

determined by the I2C control loop (the output

voltage is sensed through VOUT), and the FB

feedback control loop is disabled.

If FB is pulled up to VCC, the chip starts up

directly to the default 0.9 V output voltage. In

this case, the output voltage is determined by

the I2C control loop.

The output reference voltage scaling is realized

by adjusting the internal reference voltage

(V_REF), which is the non-inverted input of the

error amplifier. After the MP8864 receives a

valid data byte of the output reference voltage

setting, it searches the truth table for the

corresponding reference voltage and then

sends the command to adjust Vref with the

controlled slew rate. The slew rate is

determined by 3 bits of another register, which

can be read and write, accordingly.

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

17

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

I2C INTERFACE

I2C Serial Interface Description

The I2C is a 2-wire, bidirectional serial interface,

consisting of a data line (SDA) and a clock line

(SCL). The lines are pulled externally to a bus

voltage when they are “idle.” Connecting to the

line, a master device generates the SCL signal

and device address and arranges the

communication sequence.

The MP8864

interface is an I2C slave, which supports both

fast mode (400 kHz) and typically high-speed

mode (3.4 Mhz). The I2C interface adds

flexibility to the power supply solution. The

output voltage, transition slew rate, and other

parameters can be controlled instantaneously

by the I2C interface.

Data Validity

One clock pulse is generated for each data bit

transferred. The data on the SDA line must be

stable during the high period of the clock. The

high or low state of the data line can only

change when the clock signal on the SCL line is

low (see Figure 7).

Figure 7—Bit transfer on the I2C bus

Start and stop conditions are always generated

by the master. The bus is busy once the start

condition begins; the bus is free again after a

minimum of 4.7 µs (after the stop condition).

The bus stays busy if a repeated start (Sr) is

generated instead of a stop condition. The start

(S) and repeated start (Sr) conditions are

functionally identical.

Transfer Data

Every byte put on the SDA line must be 8 bits

long. Each byte must be followed by an

acknowledge bit. The acknowledge-related

clock pulse is generated by the master. The

transmitter releases the SDA line (high) during

the acknowledge clock pulse. The receiver

must pull down the SDA line during the

acknowledge clock pulse, so it remains stable

(low) during the high period of the clock pulse.

Data transfers follow the format shown in Figure

9. After the start condition (S), a slave address

is sent. This address is 7 bits long, followed by

an eighth bit which is a data direction bit (R/W).

A “0” indicates a transmission (write), a “1”

indicates a request for data (read). A data

transfer is terminated always by a stop

condition (P) generated by the master. However,

if a master still wishes to communicate on the

bus, it can generate a repeated start condition

(Sr) and address another slave without first

generating a stop condition (see Figure 8).

Start and Stop Conditions

Start and stop are signaled by the master

device, which signals the beginning and the end

of the I2C transfer. The start condition is defined

as the SDA signal transitioning from high to low

while the SCL is high. The stop condition is

defined as the SDA signal transitioning from low

to high while the SCL is high, as shown in

Figure 8.

Figure 9—A complete data transfer

The MP8864 requires a start condition, a valid

I2C address, a register address byte, and a data

byte for a single data update. After the receipt

of each byte, the MP8864 acknowledges by

pulling the SDA line low during the high period

of a single clock pulse. A valid I2C address

selects

Figure 8—Start and stop conditions

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

18

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

to VCC. The other MP8864 address is “60” (hex)

or “1100000” (binary) if ADD is pulled to ground.

When the master sends the address as an 8-bit

value, the 7-bit address should be followed by

“0/1”

to

indicate

write/read

operation

(see Table 1).

the MP8864. The MP8864 performs an update

on the falling edge of the LSB byte.

MP8864 I2C Chip Address

ADD sets the MP8864 address. The default 7bit address of the MP8864 is “68” (hex) or

“1101000” (binary) if ADD is floated or pulled up

Table 1—MP8864 address

Address (binary)

ADD

Address (hex)

Float or connected to

VCC

Connected to GND

A7

A6

A5

A4

A3

A2

A1

A0

(R/W)

D0

1

1

0

1

0

0

0

0

D1

1

1

0

1

0

0

0

1

C0

1

1

0

0

0

0

0

0

C1

1

1

0

0

0

0

0

1

MP8864 Register Address

The MP8864 contains four registers: register 00 to register 03. The four registers complete the following

actions:

Register 00 sets the output voltage and decides whether the output voltage is controlled by the

FB resistor divider or is set by the I2C.

Register 01 sets the MP8864 operating features.

Registers 02 and 03 are read registers only. Register 03 indicates the MP8864 status. The

register map is shown in the next section.

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

19

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

REGISER DESCRIPTION

Register Map

ADD

00

01

NAME

VSEL

SysCntlreg1

R/W

R/W

D7

V_BOOT

D6

R/W

EN

GO_BIT

02

03

ID1

Status

R

R

Vendor ID

Reserved

D5

D4

D3

D2

D1

Output reference

Switching

Slew rate

frequency

IC revision

VID_OK

OC

OTEW

OT

D0

Mode

PG

Register Description

1. Reg00 VSEL

NAME

BITS

DEFAULT

V_BOOT

D7

1

Output

reference

D[6:0]

0000000

D[6:0]

000 0000

000 0001

000 0010

000 0011

000 0100

000 0101

000 0110

000 0111

000 1000

000 1001

000 1010

000 1011

000 1100

000 1101

000 1110

000 1111

001 0000

001 0001

001 0010

001 0011

001 0100

001 0101

001 0110

001 0111

001 1000

001 1001

001 1010

001 1011

001 1100

MP8864 Rev. 1.02

1/18/2018

VOUT

0.60

0.61

0.62

0.63

0.64

0.65

0.66

0.67

0.68

0.69

0.70

0.71

0.72

0.73

0.74

0.75

0.76

0.77

0.78

0.79

0.80

0.81

0.82

0.83

0.84

0.85

0.86

0.87

0.88

DESCRIPTION

FB control loop enable bit. V_BOOT=“1” means the output voltage is

determined by a resistor divider connected to FB (the FB control loop).

V_BOOT=“0” means the output voltage is controlled by the I2C through

“VOUT” (the I2C control loop). This bit is helpful for the default output

voltage setting before the I2C signal comes. If the I2C is not used, the part

works efficiently with FB.

Output reference voltage. Set the output reference voltage from 0.6 V to

1.87 V (see Table 2). The default value is 0.6 V. If FB is connected to VCC,

the default value is 0.9 V.

Table 2—Output reference voltage chart

D[6:0]

VOUT

D[6:0]

VOUT

010 0000

0.92

100 0000

1.24

010 0001

0.93

100 0001

1.25

010 0010

0.94

100 0010

1.26

010 0011

0.95

100 0011

1.27

010 0100

0.96

100 0100

1.28

010 0101

0.97

100 0101

1.29

010 0110

0.98

100 0110

1.30

010 0111

0.99

100 0111

1.31

010 1000

1.00

100 1000

1.32

010 1001

1.01

100 1001

1.33

010 1010

1.02

100 1010

1.34

010 1011

1.03

100 1011

1.35

010 1100

1.04

100 1100

1.36

010 1101

1.05

100 1101

1.37

010 1110

1.06

100 1110

1.38

010 1111

1.07

100 1111

1.39

011 0000

1.08

101 0000

1.40

011 0001

1.09

101 0001

1.41

011 0010

1.10

101 0010

1.42

011 0011

1.11

101 0011

1.43

011 0100

1.12

101 0100

1.44

011 0101

1.13

101 0101

1.45

011 0110

1.14

101 0110

1.46

011 0111

1.15

101 0111

1.47

011 1000

1.16

101 1000

1.48

011 1001

1.17

101 1001

1.49

011 1010

1.18

101 1010

1.50

011 1011

1.19

101 1011

1.51

011 1100

1.20

101 1100

1.52

D[6:0]

110 0000

110 0001

110 0010

110 0011

110 0100

110 0101

110 0110

110 0111

110 1000

110 1001

110 1010

110 1011

110 1100

110 1101

110 1110

110 1111

111 0000

111 0001

111 0010

111 0011

111 0100

111 0101

111 0110

111 0111

111 1000

111 1001

111 1010

111 1011

111 1100

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

VOUT

1.56

1.57

1.58

1.59

1.60

1.61

1.62

1.63

1.64

1.65

1.66

1.67

1.68

1.69

1.70

1.71

1.72

1.73

1.74

1.75

1.76

1.77

1.78

1.79

1.80

1.81

1.82

1.83

1.84

20

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

Table 2—Output reference voltage chart (continued)

D[6:0]

001 1101

001 1110

001 1111

VOUT

0.89

0.90

0.91

D[6:0]

011 1101

011 1110

011 1111

VOUT

1.21

1.22

1.23

D[6:0]

101 1101

101 1110

101 1111

VOUT

1.53

1.54

1.55

D[6:0]

111 1101

111 1110

111 1111

VOUT

1.85

1.86

1.87

2. Reg01 SysCntlreg1

NAME

BITS

DEFAULT

EN

D[7]

1

GO_BIT

D[6]

0

Slew rate

D[5:3]

100

Switching

frequency

D[2:1]

00

Mode

D0

0

DESCRIPTION

I2C controlled turn-on or turn-off the part. When the external EN is low,

the converter is off, and the I2C is in shutdown. When EN is high, the EN

bit will take over. The default EN bit is “1.”

Switch bit of I2C writing authority for output reference command

only. Set GO_BIT=“1” to enable the I2C authority of the writing output

reference. When the command is finished, GO_BIT is auto re-set to “0” to

prevent false operation of VOUT scaling. If the reference is adjusted

within 50 mV, GO_BIT will NOT be auto re-set to “0.” If this is the case,

manually set GO_BIT to “0.” Writing GO_BIT=“1” first is recommended,

then write the output reference voltage.

D[5:3]

SLEW RATE

D[5:3]

SLEW RATE

000

64 mV/us

100

4 mV/us

001

32 mV/us

101

2 mV/us

010

16 mV/us

110

1 mV/us

011

8 mV/us

111

0.5 mV/us

D[2:1]

Fs

00

600 kHz

01

850 kHz

10

1.1 MHz

11

1.6 MHz

A “0” enables PFM mode, a high disables PFM mode.

3. Reg02 ID1

NAME

Vendor ID

IC revision

BITS

D[7:4]

D[3:0]

DESCRIPTION

1000

IC revision

BITS

D[7:5]

DESCRIPTION

Reserved for future use. Always set at “0.”

I2C controlled voltage adjustment is complete. The internal circuit compares the

DAC output with the VOUT voltage. If VOUT is in the 90%-110% range of the DAC

output, the VID_OK bit is high (which means the voltage scaling is complete).

Otherwise, VID_OK=“0.”

Output over-current indication. When the bit is high, the IC is in hiccup mode.

Die temperature early warning bit. When the bit is high, the die temperature is

above 120˚C.

Over-temperature indication. When the bit is high, the IC is in thermal shutdown.

Output power good indication. When the bit is high, the VOUT power is good. This

means the VOUT is higher than 90% of the designed regulation voltage. For additional

details, please refer to the “Power Good Indicator” section on page 15.

4. Reg03 Status

NAME

Reserved

VID_OK

D[4]

OC

OTEW

D[3]

OT

D[1]

PG

D[0]

MP8864 Rev. 1.02

1/18/2018

D[2]

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

21

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

APPLICATION INFORMATION

Setting the Output Voltage in the FB Control

Loop

The reference voltage and the external resistor

divider set the output voltage through FB. The

feedback resistors R1 and RT set the feedbackloop bandwidth with the internal compensation

capacitor. Choose the value for R1 first, R2 is

then given by Equation (3) 11:

R2

R1

(3)

VOUT

1

VREF

Setting the Output Voltage in the I2C Control

Loop

In addition to setting the output voltage through

the FB loop, the I2C loop can set the output

voltage through VOUT by setting V_Boot=“0”. In

this case, the output voltage is the set reference

voltage. Please refer to Table 2 on page 20 for

additional details about the output voltage

setting.

Output Voltage Dynamic Scale

To dynamic scale the output voltage during

normal operation, refer to Figure 11 and

following the steps below:

NOTES:

11) VREF is 0.6 V when powering up or EN is on. After the

MP8864 is enabled, VREF can be programmed through the I2C.

Set V_BOOT=”1” to enable the FB control loop.

The T-type network (see Figure 10)

recommended highly when VOUT is low.

is

Step 1: Write GO_Bit (reg01[6]) to “1.”

Step 2: Write reg00 to select the feedback loop

by setting V_BOOT(reg00[7]) and set the

reference voltage by the output reference

(reg00[0:6]) simultaneously. If the reference

adjustment is within 50 mV, GO_BIT will not

auto re-set to “0.” If this is the case, manually

set GO_BIT to “0.” Repeat steps to dynamic

scale to another voltage.

Voltage scaling

start

Figure 10—T-type network

Table 3 lists the recommended T-type resistor

values for common output voltages.

Write reg01[6]

GO_Bit=“1”

Table 3—Resistor selection for common output

voltages with default 0.6V VREF(12)

VOUT

(V)

0.9

1

1.2

1.8

2.5

3.3

5

R1

(kΩ)

34(1%)

34(1%)

34(1%)

34(1%)

34(1%)

34(1%)

R2

RT

Cff

(kΩ)

(kΩ)

(pF)

Connect FB to VCC

51(1%) 33(1%) 15

34(1%) 33(1%) 10

16.5(1%) 15(1%) 10

10.7(1%) 15(1%) 15

7.5(1%) 15(1%) 15

4.64(1%) 7.5(1%) 15

CFB

L

(pF) (uH)

1

10

1

10

1

15

1.5

22

1.8

33

2.7

47

2.7

NOTE:

12) The recommended parameters are based on a 12 V input

voltage and a 22µF x 2 output capacitor. Different input voltage

and output capacitor values may affect the selection of R1, R2,

RT, Cff, and CFB. For additional component parameters, please

refer to the “Typical Application Circuits” section on page 26.

MP8864 Rev. 1.02

1/18/2018

Loop selection

FB control loop

(FB sense feedback)

I2C control loop

(VOUT direct sense

feedback)

Write reg00(Set

V_BOOT= “1” &

“Vref” code)

Write reg00(Set

V_BOOT= “0” &

“Vref” code)

Figure 11—Output voltage dynamic scale flow

chart

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

22

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

Selecting the Inductor

For most applications, use a 1 µH to 10 µH

inductor with a DC current rating at least 25%

higher than the maximum load current. For

highest efficiency, use an inductor with a DC

resistance less than 15 mΩ. For most designs,

the inductance value can be derived from

Equation (4):

L1

VOUT (VIN VOUT )

VIN IL fOSC

(4)

Where ΔIL is the inductor ripple current.

Choose the inductor ripple current to be

approximately 30% of the maximum load

current. The maximum inductor peak current

can be determined using Equation (5):

IL(MAX ) ILOAD

I

L

2

(5)

Use a larger inductor for improved efficiency

under light-load conditions—below 100 mA.

Selecting the Input Capacitor

The input current to the step-down converter is

discontinuous, therefore it requires a capacitor

to supply the AC current while maintaining the

DC input voltage. Use low ESR capacitors for

the best performance. Use ceramic capacitors

with X5R or X7R dielectrics for best results

because of their low ESR and small

temperature coefficients. For most applications,

use a 22µF x 2 capacitor.

Since C2 absorbs the input switching current, it

requires an adequate ripple-current rating. The

RMS current in the input capacitor can be

estimated using Equation (6):

IC2 ILOAD

VOUT VOUT

1

VIN

VIN

ILOAD

2

(6)

(7)

For simplification, choose an input capacitor

with an RMS current rating greater than half of

the maximum load current. The input capacitor

can be electrolytic, tantalum, or ceramic. When

using electrolytic or tantalum capacitors, add a

MP8864 Rev. 1.02

1/18/2018

fS C2

IN

VIN

VIN

Selecting the Output Capacitor

The output capacitor (C5) maintains the DC

output voltage. Use ceramic, tantalum, or low

ESR electrolytic capacitors. For best results,

use low ESR capacitors to keep the output

voltage ripple low. The output voltage ripple can

be estimated using Equation (9):

ΔVOUT

VOUT

V

1

1 OUT (RESR

) (9)

fS L1

VIN

8 fS C5

Where L1 is the inductor value and RESR is the

equivalent series resistance (ESR) value of the

output capacitor.

For ceramic capacitors, the capacitance

dominates the impedance at the switching

frequency, and the capacitance causes the

majority of the output voltage ripple. For

simplification, the output voltage ripple can be

estimated using Equation (10):

ΔVOUT

VOUT

1

2

8 fS L1 C5

VOUT

VIN

(10)

For tantalum or electrolytic capacitors, the ESR

dominates the impedance at the switching

frequency. For simplification, the output ripple

can be approximated using Equation (11):

ΔVOUT

The worse case condition occurs at VIN = 2VOUT.

See Equation (7).

IC2

small,

high-quality

ceramic

capacitor

(e.g. 0.1 μF) placed as close to the IC as

possible. Ensure ceramic capacitors have

enough capacitance to provide sufficient charge

to prevent excessive voltage ripple at the input.

The input voltage ripple caused by capacitance

can be estimated using equation (8):

I

V

V

(8)

ΔV LOAD OUT 1 OUT

VOUT

V

1 OUT

fS L1

VIN

RESR

(11)

The output capacitor affects the stability of the

regulation system. The MP8864 can be

optimized for a wide range of capacitance and

ESR values.

External Bootstrap Diode (BST)

BST voltage may become insufficient at

particular conditions. If any of these conditions

occur, an external bootstrap diode can enhance

the efficiency of the regulator and avoid

insufficient BST voltage at light-load PFM

operation.

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

23

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

Insufficient BST voltage is more likely to occur

at the following conditions:

VIN is low.

The duty cycle is large: D=

NOTE:

13)

The recommended layout is based on Figure15 and the

Typical Application circuit on page 26.

VOUT

>65%

VIN

If insufficient BST voltage occurs during these

conditions, the output voltage ripple may

become extremely large during light-load

conditions, or there may be bad efficiency

during heavy-load conditions. Add an external

BST diode from VCC to BST (see Figure 12).

Figure 12—Optional external bootstrap diode to

enhance efficiency

The recommended external BST diode is

1N4148, and the BST capacitor value is 0.1 µF

to 1 μF.

Top Layer

PCB Layout Guidelines (13)

Efficient PCB layout is critical to achieve stable

operation, especially for VCC capacitor and

input capacitor placement. For best results,

refer to Figure 13 and follow the guidelines

below:

1)

2)

3)

4)

5)

Use a large ground plane to connect

directly to GND. Add vias near GND if the

bottom layer is ground plane.

Place the VCC capacitor as close as

possible to VCC and GND. Make the trace

length of VCC to the VCC capacitor anode

to the VCC capacitor cathode chip to GND

as short as possible.

Place the ceramic input capacitor close to

IN and GND. Keep the connection of the

input capacitor and IN as short and wide as

possible.

Route SW and BST away from sensitive

analog areas such as FB. It is NOT

recommended to route a SW and BST

trace under the chip’s bottom layer.

Place the T-type feedback resistor R3 close

to the chip to ensure the trace (which

connects to FB) is as short as possible.

MP8864 Rev. 1.02

1/18/2018

Bottom Layer

Figure 13—Recommended PCB layout

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

24

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

Design Example

Table 4 shows a design example following the

application guidelines for the following

specifications:

Table 4—Design example

VIN

VOUT

IO

12 V

1.2 V

4A

The detailed application schematics are shown

in Figure 16. The typical performance and

circuit waveforms have been shown in the

“Typical Performance Characteristics” section.

For additional device applications, please refer

to the related evaluation board datasheets.

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

25

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

TYPICAL APPLICATION CIRCUITS (14)

R8

10 Ω

C4

0.1 uF

10

1

VIN

C8

C2

C3

22 uF 22 uF 0.1 uF

R7

100 kΩ

3

14

R6

NS

C1

0.22 μF

SW

VCC

PG

4

PG

5

SDA

SCL

ADD

7

C11

22 pF

VOUT

11

FB

12

AGND

SS

13

15

R5

10 Ω

C5

22 uF

C6

22 uF

VOUT

C12

NS

R9

100 kΩ

MP8864

SDA

SCL

0.9 V/4 A

9

EN/SYNC

R4

100 kΩ

6

L1

1 uH

BST

VIN

PGND

2,8

C7

22 nF

Figure 14—12 V Input-0.9 V/4 A Output (15)

R8

10 Ω

C4

0.1 uF

10

1

VIN

C8

C2

22 uF 22 uF

R7

C3 100 kΩ

0.1 uF

R6

NS

3

14

C1

0.22 μF

SW

VCC

VOUT

4

SDA

SCL

5

6

7

C11

22 pF

15

C5

22 uF

C6

22 uF

VOUT

C12

NS

R9

100 kΩ

C9

R3 15 pF

33 kΩ

PG

AGND

R5

10 Ω

11

MP8864

SDA

SCL

ADD

1 V/4 A

9

EN/SYNC

R4

100 kΩ

PG

L1

1 uH

BST

VIN

FB

12

SS

13

C10

10 pF

R1

34 kΩ

R2

51 kΩ

PGND

2,8

C7

22 nF

Figure 15—12 V Input-1 V/4 A Output

R8

10 Ω

C4

0.1 uF

10

1

VIN

C8

C2

22 uF 22 uF

R7

C3 100 kΩ

0.1 uF

R6

NS

PG

SDA

SCL

3

14

C1

0.22 μF

SW

VCC

VOUT

5

6

7

C11

22 pF

15

C5

22 uF

C6

22 uF

VOUT

C12

NS

R9

100 kΩ

C9

R3 10 pF

33 kΩ

PG

AGND

R5

10 Ω

11

MP8864

SDA

SCL

ADD

1.2V/4A

9

EN/SYNC

R4

100 kΩ

4

L1

1 uH

BST

VIN

FB

12

SS

13

C10

10 pF

R1

34 kΩ

R2

34 kΩ

PGND

2,8

C7

22 nF

Figure 16---12 V Input-1.2 V/4 A Output

Notes:

14) Excluding Figure 13, the circuits are based on a 0.6 V default reference voltage.

15) R5 is used for loop test purposes. It is NOT needed if the test loop signal is small.

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

26

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

R8

10Ω

C4

0.1uF

10

1

VIN

C8

22uF

C2

22uF

C3

0.1uF

L1

1.5uH

BST

VIN

R7

100kΩ

SW

3

14

R6

NS

C1

0.22μF

VOUT

R4

100kΩ

PG

4

SDA

SCL

5

6

7

C11

22pF

EN/SYNC

VCC

C5

22uF

C6

22uF

VOUT

C12

NS

R9

100kΩ

C9

R3 10pF

15kΩ

PG

FB

SDA

SCL

ADD

SS

15

R5

10Ω

11

MP8864

AGND

1.8V/4A

9

12

C10

15pF

13

R1

34kΩ

R2

16.5kΩ

PGND

2,8

C7

22nF

Figure 17—12 V Input-1.8 V/4 A Output

R8

10Ω

C4

0.1uF

10

1

VIN

C8

22uF

C2

22uF

C3

0.1uF

L1

1.8uH

BST

VIN

R7

100kΩ

SW

3

14

R6

NS

C1

0.22μF

VOUT

R4

100kΩ

PG

4

SDA

SCL

5

6

7

C11

22pF

EN/SYNC

VCC

C5

22uF

C6

22uF

VOUT

C12

NS

R9

100kΩ

C9

R3 15pF

15kΩ

PG

FB

SDA

SCL

ADD

SS

15

R5

10Ω

11

MP8864

AGND

2.5V/4A

9

12

C10

22pF

13

R1

34kΩ

R2

10.7kΩ

PGND

2,8

C7

22nF

Figure 18—12V Input-2.5 V/4 A Output

R8

10Ω

C4

0.1uF

10

1

VIN

C8

22uF

C2

22uF

C3

0.1uF

R7

100kΩ

SDA

SCL

SW

3

R6

NS

PG

L1

2.7uH

BST

VIN

14

C1

0.22μF

VOUT

R4

100kΩ

4

5

6

7

C11

22pF

EN/SYNC

VCC

FB

SS

15

C5

22uF

C6

22uF

VOUT

C12

NS

R9

100kΩ

C9

R3 15pF

15kΩ

PG

AGND

R5

10Ω

11

MP8864

SDA

SCL

ADD

3.3V/4A

9

12

C10

33pF

13

R1

34kΩ

R2

7.5kΩ

PGND

2,8

C7

22nF

Figure 19—12 V Input-3.3 V/4 A Output

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

27

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

R8

10Ω

C4

0.1uF

10

1

VIN

C8

22uF

C2

22uF

C3

0.1uF

R7

100kΩ

SDA

SCL

SW

3

R6

NS

PG

L1

2.7uH

BST

VIN

14

C1

0.22μF

VOUT

R4

100kΩ

PG

5

SDA

SCL

ADD

7

SS

15

C5

22uF

C6

22uF

VOUT

C12

NS

R9

100kΩ

FB

AGND

R5

10Ω

11

MP8864

4

6

C11

22pF

EN/SYNC

VCC

5V/4A

9

12

13

C9

R3 15pF

7.5kΩ

R1

34kΩ

C10

47pF

R2

4.64kΩ

PGND

2,8

C7

22nF

Figure 20—12 V Input-5 V/4 A Output

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

28

�MP8864 – SYNCHRONOUS STEP-DOWN CONVERTER

PACKAGE INFORMATION

QFN-15 (3mm X 3mm)

PIN 1 ID

0.10x45° TYP.

PIN 1 ID

MARKING

PIN 1 ID

INDEX AREA

BOTTOM VIEW

TOP VIEW

SIDE VIEW

NOTE:

0.10x45°

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) EXPOSED PADDLE SIZE DOES NOT INCLUDE

MOLD FLASH.

3) LEAD COPLANARITY SHALL BE 0.10

MILLIMETERS MAX.

4) JEDEC REFERENCE IS MO-220.

5) DRAWING IS NOT TO SCALE.

RECOMMENDED LAND PATTERN

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications.

Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS

products into any application. MPS will not assume any legal responsibility for any said applications.

MP8864 Rev. 1.02

1/18/2018

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2018 MPS. All Rights Reserved.

29

�