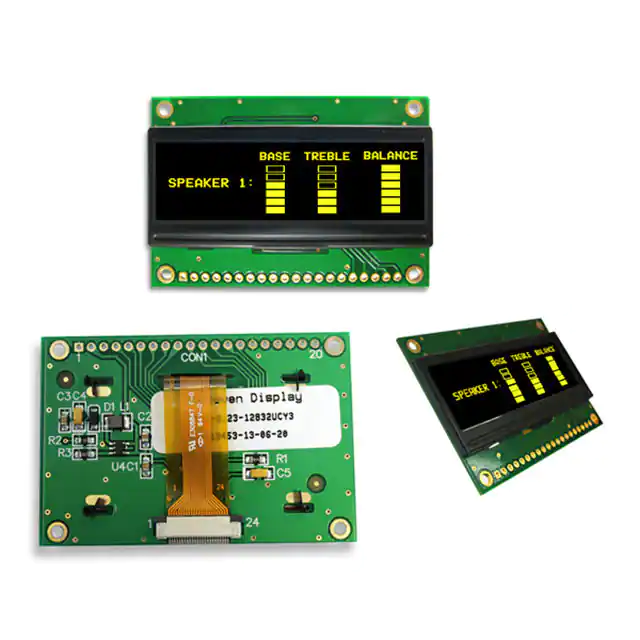

NHD-2.23-12832UCY3

Graphic OLED Display Module

NHD2.2312832UCY3-

Newhaven Display

2.23” diagonal size

128 x 32 pixel resolution

Model

Emitting Color: Yellow

+3V power supply

Newhaven Display International, Inc.

2511 Technology Drive, Suite 101

Elgin IL, 60124

Ph: 847-844-8795

Fax: 847-844-8796

www.newhavendisplay.com

nhtech@newhavendisplay.com

nhsales@newhavendisplay.com

�Document Revision History

Revision

0

1

2

Date

5/1/2011

2/22/2013

8/3/2020

3

9/1/2020

Description

Initial Product Release

Electrical characteristics and mechanical drawing updated

Included MIN Supply Voltage & Reformatted 2D Mechanical

Drawing

Updated 2D Mechanical Drawing

Functions and Features

•

•

•

•

•

128 x 32 pixel resolution

Built-in SSD1305 controller

Parallel or serial MPU interface

Single, low voltage power supply

RoHS compliant

[2]

Changed by

JN

AS

AS

�1

A

2

Mechanical Drawing

3

4

5

6

7

SYMBOL

8

REVISION

DATE

A

1

20

B

B

C

C

1

20

1

24

P0.43x128-0.02=55.02 (A/A)

D

D

(4,0)

(0, 0)

0.43

0.41

Segment 127

Segment 0

( Column 1 )

E

( Row 32 )

Common 47

Detail "A"

Common 15

( Row 1 )

1

E

Common 0

( Row 31 )

F

(131, 31)

( Column 128 )

Common 32

Notes:

1. Display Color:

2. Supply Voltage:

3. Driver IC:

4. Interface:

5. Brightness:

0.41

0.39

P0.41x32-0.02=13.1 (A/A)

"A"

( Row 2 )

STANDARD TOLERANCE:

(UNLESS OTHERWISE SPECIFIED)

Yellow

3.3V

SSD1305

Parallel (6800 or 8080), SPI or I2C Interface

120 cd/m2

2

3

LINEAR: ±0.3mm

DRAWN BY:

- DIMENSIONS ARE IN MILLIMETERS

DRAWN DATE:

- THIRD ANGLE PROJECTION

5

6

1.0

NHD-2.23-12832UCY3

UNLESS OTHERWISE SPECIFIED:

4

REVISION:

DRAWING/PART NUMBER:

A. Shah

9/1/20

APPROVED BY:

APPROVED DATE:

DO NOT SCALE DRAWING

SIZE:

A3

A. Shah

SCALE:

NS

9/1/20

SHEET 1 OF 1

THIS DRAWING IS SOLELY THE PROPERTY OF NEWHAVEN DISPLAY INTERNATIONAL, INC.

THE INFORMATION IT CONTAINS IS NOT TO BE DISCLOSED, REPRODUCED OR COPIED IN

WHOLE OR PART WITHOUT WRITTEN APPROVAL FROM NEWHAVEN DISPLAY.

7

8

F

�Interface Description

Parallel Interface:

Pin No.

Symbol

External

Connection

Power Supply

Power Supply

MPU

MPU

1

2

3

4

5

VSS

VDD

NC

D/C

R/W or /WR

6

E or /RD

MPU

7-14

15

16

17

18

19

20

DB0 – DB7

NC

/RES

/CS

NC

BS2

BS1

MPU

MPU

MPU

MPU

MPU

Function Description

Ground

Supply Voltage for OLED and logic.

No Connect

Register select signal. D/C=0: Command, D/C=1: Data

6800-interface:

Read/Write select signal, R/W=1: Read R/W: =0: Write

8080-interface:

Active LOW Write signal.

6800-interface:

Operation enable signal. Falling edge triggered.

8080-interface:

Active LOW Read signal.

8-bit Bi-directional data bus lines.

No Connect

Active LOW Reset signal.

Active LOW Chip Select signal.

No Connect

MPU Interface Select signal.

MPU Interface Select signal.

Serial Interface:

Pin No.

1

2

3

4

5-6

7

8

9

10-14

15

16

17

18

19

20

Symbol

VSS

VDD

NC

D/C

VSS

SCLK

SDIN

NC

VSS

NC

/RES

/CS

NC

BS2

BS1

External

Connection

Power Supply

Power Supply

MPU

Power Supply

MPU

MPU

Power Supply

MPU

MPU

MPU

MPU

Function Description

Ground

Supply Voltage for OLED and logic.

No Connect

Register select signal. D/C=0: Command, D/C=1: Data

Ground

Serial Clock signal.

Serial Data Input signal.

No Connect

Ground

No Connect

Active LOW Reset signal.

Active LOW Chip Select signal.

No Connect

MPU Interface Select signal.

MPU Interface Select signal.

[4]

�I2C Interface:

Pin No.

Symbol

1

2

3

4

5-6

7

8

9

10-14

15

16

17

18

19

20

External

Connection

Power Supply

Power Supply

MPU

Power Supply

MPU

MPU

MPU

Power Supply

MPU

Power Supply

MPU

MPU

VSS

VDD

NC

SA0

VSS

SCL

SDAIN

SDAOUT

VSS

NC

/RES

VSS

NC

BS2

BS1

Function Description

Ground

Supply Voltage for OLED and logic.

No Connect

Slave Address Selection signal.

Ground

Serial Clock signal.

Serial Data input signal (pins 8 and 9 can be tied together).

Serial Data output signal (pin9 can be no connect).

Ground

No Connect

Active LOW Reset signal.

Ground

No Connect

MPU Interface Select signal.

MPU Interface Select signal.

MPU Interface Pin Selections

Pin

Name

BS2

BS1

6800 Parallel

8-bit interface

1

0

8080 Parallel

8-bit interface

1

1

Serial

Interface

0

0

I2C

Interface

0

1

MPU Interface Pin Assignment Summery

Bus

Interface

8-bit 6800

8-bit 8080

SPI

I2C

D7

Data/Command Interface

D5 D4 D3

D2

D1

D[7:0]

D[7:0]

Tie LOW

NC

SDIN

Tie LOW

SDAIN

SDAOUT

D6

D0

SCLK

SCL

[5]

Control Signals

E

R/W /CS D/C

E

R/W /CS D/C

/RD /WR /CS D/C

Tie LOW

/CS D/C

Tie LOW

SA0

/RES

/RES

/RES

/RES

/RES

�Wiring Diagrams

[6]

�Electrical Characteristics

Item

Operating Temperature Range

Storage Temperature Range

Symbol

Top

Tst

Supply Voltage

Supply Current (logic)

VDD

IDD

Supply Current (display)

ICC

Sleep Mode Current

“H” Level input

“L” Level input

“H” Level output

“L” Level output

Condition

Absolute Max

Absolute Max

Ta=25°C, VDD=3.3V

50% ON, VDD=3.3V

100% ON, VDD=3.3V

IDD+ICCSLEEP

Vih

Vil

Voh

Vol

Min.

-40

-40

Typ.

-

Max.

+85

+90

Unit

⁰C

⁰C

3.0

0.8*VDD

VSS

0.9*VDD

VSS

3.3

180

60

108

3

-

3.5

300

70

120

15

VDD

0.2*VDD

VDD

0.1*VDD

V

µA

mA

mA

µA

V

V

V

V

Optical Characteristics

Item

Viewing Angle – Top

Viewing Angle – Bottom

Viewing Angle – Left

Viewing Angle – Right

Contrast Ratio

Response Time (rise)

Response Time (fall)

Brightness

Lifetime

Symbol

AV

AV

AH

AH

Cr

Tr

Tf

Condition

Min.

2000:1

100

40,000

Typ.

80

80

80

80

10

10

120

-

Max.

-

Unit

⁰

⁰

⁰

⁰

us

us

cd/m2

Hrs

50% checkerboard

Ta=25°C, 50%

checkerboard

Note: Lifetime at typical temperature is based on accelerated high-temperature operation. Lifetime is tested at

average 50% pixels on and is rated as Hours until Half-Brightness. The Display OFF command can be used to

extend the lifetime of the display.

Luminance of active pixels will degrade faster than inactive pixels. Residual (burn-in) images may occur. To avoid

this, every pixel should be illuminated uniformly.

[7]

�Built-in SSD1305 controller.

Instruction Table

Instruction

Set Lower Column

Start Address

Set Higher

Column Start

Address

Set Memory

Addressing Mode

HEX

00~ 0F

DB7

0

DB6

0

0

10~1F

0

0

0

0

20

A[1:0]

0

*

0

*

21

A[7:0]

B[7:0]

22

A[2:0]

B[2:0]

40~7F

0

A7

B7

0

*

*

0

81

A[7:0]

82

A[7:0]

91

X[5:0]

A[5:0]

B[5:0]

C[5:0]

Set Column

Address

0

Set Page Address

0

Set Display Start

Line

Set Contrast

Control

Set Brightness

Set Look-Up Table

Code

DB5 DB4

0

0

D/C

0

0

0

0

0

DB3

X3

DB2

X2

DB1

X1

DB0

X0

1

X3

X2

X1

1

*

0

*

0

*

0

*

0

A6

B6

0

*

*

1

1

A5

B5

1

*

*

X5

0

A4

B4

0

*

*

X4

0

A3

B3

0

*

*

X3

1

A7

1

A7

1

*

*

*

*

0

A6

0

A6

0

*

*

*

*

0

A5

0

A5

0

X5

A5

B5

C5

0

A4

0

A4

1

X4

A4

B4

C4

Description

RESET

value

Set the lower nibble of the column start address register for Page

Addressing Mode.

0

X0

Set the higher nibble of the column start address register for Page

Addressing Mode.

0

0

A1

0

A0

0

A2

B2

0

A2

B2

X2

0

A1

B1

1

A1

B1

X1

1

A0

B0

0

A0

B0

X0

A[1:0] = 00b, Horizontal Addressing Mode

A[1:0] = 01b, Vertical Addressing Mode

A[1:0] = 10b, Page Addressing Mode

A[1:0] = 11b, Invalid

Setup column start and end address

A[7:0]: Column start address. Range: 0-131d

B[7:0]: Column end address. Range: 0-131d

0

A3

0

A3

0

X3

A3

B3

C3

0

A2

0

A2

0

X2

A2

B2

C2

0

A1

1

A1

0

X1

A1

B1

C1

1

A0

0

A0

1

X0

A0

B0

C0

Set Bank Color of

Bank1 to Bank16

(Page 0)

0

92

A[7:0]

B[7:0]

C[7:0]

D[7:0]

1

A7

B7

C7

D7

0

A6

B6

C6

D6

0

A5

B5

C5

D5

1

A4

B4

C4

D4

0

A3

B3

C3

D3

0

A2

B2

C2

D2

1

A1

B1

C1

D1

0

A0

B0

C0

D0

Set Bank Color of

0

93

1

0

0

1

0

0

1

1

[8]

10b

0

131d

Setup page start and end address

A[2:0]: Page start address. Range: 0-7d

B[2:0]: Page end address. Range: 0-7d

0

7d

Set display RAM display start line register from 0-63d.

0

Double byte command to select 1 out of 256 contrast steps. Contrast

increases as the value increases.

0x80

Double byte command to select 1 out of 256 brightness steps.

Brightness increases as the value increases.

0x80

Set current drive pulse width of Bank 0, Color A, B and C.

Bank 0: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.

Color A: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.

Color B: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.

Color C: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.

Note: Color D pulse width is fixed at 64 clocks.

Sets the bank color of Bank1~Bank16 to any one of the 4 colors A,B,C,

and D.

A[1:0] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK1.

A[3:2] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK2.

.

.

.

D[5:4] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK15.

D[7:6] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK16.

Sets the bank color of Bank17~Bank32 to any one of the 4 colors

0x31

0x3F

0x3F

0x3F

�Bank17 to Bank32

(Page 1)

A[7:0]

B[7:0]

C[7:0]

D[7:0]

A7

B7

C7

D7

A6

B6

C6

D6

A5

B5

C5

D5

A4

B4

C4

D4

A3

B3

C3

D3

A2

B2

C2

D2

A1

B1

C1

D1

A0

B0

C0

D0

Set Segment

Remap

Entire Display ON

0

A0/A1

1

0

1

0

0

0

0

X0

0

A4/A5

1

0

1

0

0

1

0

X0

Set Normal/

Inverse Display

Set Multiplex

Ratio

Dim mode setting

0

A6/A7

1

0

1

0

0

1

1

X0

0

A8

A[5:0]

AB

A[3:0]

B[7:0]

C[7:0]

1

*

1

*

B7

C7

0

*

0

*

B6

C6

1

A5

1

*

B5

C5

0

A4

0

*

B4

C4

1

A3

1

A3

B3

C3

0

A2

0

A2

B2

C2

0

A1

1

A1

B1

C1

0

A0

1

A0

B0

C0

Master

configuration

Set Display ON/

OFF

0

1

1

1

0

0

0

1

0

1

0

0

0

1

1

1

1

1

1

0

1

A1

1

0

A0

Set Page Start

Address

Set COM Output

Scan Direction

Set Display Offset

0

AD

AE

AC/

AE/

AF

B0~B7

1

0

1

1

0

X2

X1

X0

0

C0/C8

1

1

0

0

X3

0

0

0

0

Set Display Clock

Divide Ratio /

Oscillator

Frequency

Set Area Color

Mode ON/OFF &

Low Power

Display Mode

Set Pre-charge

0

D3

A[5:0]

D5

A[7:0]

1

*

1

A7

1

*

1

A6

0

A5

0

A5

1

A4

1

A4

0

A3

0

A3

0

A2

1

A2

1

A1

0

A1

D8

X[5:0]

1

0

1

0

0

X5

1

X4

1

0

0

X2

D9

1

1

0

1

1

0

0

0

0

0

A,B,C, and D.

A[1:0] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK17.

A[3:2] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK18.

.

.

.

D[5:4] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK31.

D[7:6] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK32.

X[0] = 0; Column address 0 is mapped to SEG0

X[0] = 1; Column address 131 is mapped to SEG0

0

X[0] = 0; Resume RAM content display. Output follows RAM content.

X[0] = 1; Entire display ON. Output ignores RAM content.

X[0] = 0; Normal display.

X[0] = 1; Inverse display.

0

Set MUX ratio to N+1 MUX

N=A[5:0]; from 16MUX to 64MUX (0 to 14 are invalid)

64

0

A[3:0] = reserved. Set as 0000b

B[7:0] = Set contrast for BANK0. Range 0-255d. Refer to command

81h.

C[7:0] = Set brightness for color bank. Range 0-255d. Refer to

command 82h.

Selects external VCC supply

AEh

ACh = Display ON in dim mode

AEh = Display OFF (sleep mode)

AFh = Display ON in normal mode

AEh

Set GDRAM Page Start Address for Page Addressing Mode using X[2:0].

PAGE0~PAGE7

X[3] = 0; Normal mode. Scan from COM0 to COM[N-1]

X[3] = 1; Remapped mode. Scan from COM[N-1] to COM0

0

1

A0

1

A0

Set vertical shift by COM from 0~63.

0

0

0

0

X0

X[5:4] = 00b; Monochrome mode

X[5:4] = 11b; Area Color mode

X[2] = 0 and X[0] = 0; Normal power mode

X[2] = 1 and X[0] = 1; Set low power display mode

00

0

1

A[3:0] = Phase 1 period of up to 15 DCLK clocks. 0 is invalid.

A[7:4] = Phase 2 period of up to 15 DCLK clocks. 0 is invalid.

2h

2h

[9]

A[3:0] = Define the divide ratio of the display clocks.

Divide ratio = A[3:0] +1

A[7:4] = Set the Oscillator Frequency. Frequency increases with the

value of A[7:4]. Range 0000b~1111b.

0000b

0111b

00

�Period

Set COM pins

Hardware

configuration

A[7:0]

DA

X[5:4]

A7

1

0

A6

1

0

A5

0

X5

A4

1

X4

A3

1

0

A2

0

0

A1

1

1

A0

0

0

DB

A[5:2]

1

0

1

0

0

A5

1

A4

1

A3

0

A2

1

0

1

0

Set VCOMH

Deselect Level

0

Enter Read

Modify Write

mode

NOP

Exit Read Modify

Write mode

0

E0

1

1

1

0

0

0

0

0

X[4] = 0; Sequential COM pin configuration

X[4] = 1; Alternative COM pin configuration

X[5] = 0; Disable COM Left/Right remap

X[5] = 1; Enable COM Left/Right remap

A[5:2] = 0000b; VCOMH = ~0.43*VCC

A[5:2] = 1101b; VCOMH = ~0.77*VCC

A[5:2] = 1111b; VCOMH = ~0.83*VCC

Enter the Read/Modify/Write mode.

0

0

E3

EE

1

1

1

1

1

1

0

0

0

1

0

1

1

1

1

0

Command for No Operation

Exit the Read/Modify/Write mode.

0

For detailed instruction information, see datasheet: http://www.newhavendisplay.com/app_notes/SSD1305.pdf

[10]

1

1

1101

�MPU Interface

For detailed timing information, see datasheet: http://www.newhavendisplay.com/app_notes/SSD1305.pdf

6800-MPU Parallel Interface

The parallel interface consists of 8 bi-directional data pins, R/W, D/C, E, and /CS.

A LOW on R/W indicates write operation, and HIGH on R/W indicates read operation.

A LOW on D/C indicates “Command” read or write, and HIGH on D/C indicates “Data” read or write.

The E input serves as data latch signal, while /CS is LOW. Data is latched at the falling edge of E signal.

Function

Write Command

Read Status

Write Data

Read Data

E

↓

↓

↓

↓

R/W

0

1

0

1

/CS

0

0

0

0

D/C

0

0

1

1

8080-MPU Parallel Interface

The parallel interface consists of 8 bi-directional data pins, /RD, /WR, D/C, and /CS.

A LOW on D/C indicates “Command” read or write, and HIGH on D/C indicates “Data” read or write.

A rising edge of /RS input serves as a data read latch signal while /CS is LOW.

A rising edge of /WR input serves as a data/command write latch signal while /CS is LOW.

Function

Write Command

Read Status

Write Data

Read Data

/RD

1

↑

1

↑

/WR

↑

1

↑

1

/CS

0

0

0

0

D/C

0

0

1

1

Alternatively, /RD and /WR can be kept stable while /CS serves as the data/command latch signal.

Function

Write Command

Read Status

Write Data

Read Data

/RD

1

0

1

0

/WR

0

1

0

1

/CS

↑

↑

↑

↑

D/C

0

0

1

1

[11]

�Serial Interface

The serial interface consists of serial clock SCLK, serial data SDIN, D/C, and /CS.

D0 acts as SCLK and D1 acts as SDIN. D2 should be left open. D3~D7, E, and R/W should be connected to GND.

Function

Write Command

Write Data

/RD

0

0

/WR

0

0

/CS

0

0

D/C

0

1

D0

↑

↑

SDIN is shifted into an 8-bit shift register on every rising edge of SCLK in the order of D7, D6,…D0.

D/C is sampled on every eighth clock and the data byte in the shift register is written to the GDRAM or

command register in the same clock.

Note: Read is not available in serial mode.

I2C Interface

The I2C interface consists of a slave address bit SA0, I2C-bus data signal SDA, and I2C-bus clock signal SCL.

D1 and D2 can be tied together, and act as SDA. D0 acts as SCL. Both the data and clock signals must be

connected to pull-up resistors. /RES is used to initialize the device.

Note: SA0 bit allows the device to have a slave address of either “0111100” or “0111101”.

Note: Data and acknowledgement are sent through the SDA. The ITO track resistance and the pull-up

resistance at SDA becomes a voltage potential divider. As a result, it may not be possible to attain a valid logic

“0” level on SDA for the ACK signal. SDAIN must be connected, but SDAOUT may be disconnected and the ACK

signal will be ignored on the I2C bus.

For detailed protocol information, see datasheet: http://www.newhavendisplay.com/app_notes/SSD1305.pdf

[12]

�Example Initialization Sequence:

Set_Display_On_Off(0x00);

Set_Display_Clock(0x10);

Set_Multiplex_Ratio(0x1F);

Set_Display_Offset(0x00);

Set_Start_Line(0x00);

Set_Master_Config(0x00);

Set_Area_Color(0x05);

Set_Addressing_Mode(0x02);

Set_Segment_Remap(0x01);

Set_Common_Remap(0x08);

Set_Common_Config(0x10);

Set_LUT(0x3F,0x3F,0x3F,0x3F);

Set_Contrast_Control(Brightness);

Set_Area_Brightness(Brightness);

Set_Precharge_Period(0xD2);

Set_VCOMH(0x08);

Set_Entire_Display(0x00);

Set_Inverse_Display(0x00);

Fill_RAM(0x00);

Set_Display_On_Off(0x01);

// Display Off (0x00/0x01)

// Set Clock as 160 Frames/Sec

// 1/32 Duty (0x0F~0x3F)

// Shift Mapping RAM Counter (0x00~0x3F)

// Set Mapping RAM Display Start Line (0x00~0x3F)

// Disable Embedded DC/DC Converter (0x00/0x01)

// Set Monochrome & Low Power Save Mode

// Set Page Addressing Mode (0x00/0x01/0x02)

// Set SEG/Column Mapping (0x00/0x01)

// Set COM/Row Scan Direction (0x00/0x08)

// Set Alternative Configuration (0x00/0x10)

// Define All Banks Pulse Width as 64 Clocks

// Set SEG Output Current

// Set Brightness for Area Color Banks

// Set Pre-Charge as 13 Clocks & Discharge as 2 Clock

// Set VCOM Deselect Level

// Disable Entire Display On (0x00/0x01)

// Disable Inverse Display On (0x00/0x01)

// Clear Screen

// Display On (0x00/0x01)

[13]

�Quality Information

Test Item

Content of Test

High Temperature storage

Test the endurance of the display at high

storage temperature.

Test the endurance of the display at low

storage temperature.

Test the endurance of the display by

applying electric stress (voltage & current)

at high temperature.

Test the endurance of the display by

applying electric stress (voltage & current)

at low temperature.

Test the endurance of the display by

applying electric stress (voltage & current)

at high temperature with high humidity.

Test the endurance of the display by

applying electric stress (voltage & current)

during a cycle of low and high

temperatures.

Test the endurance of the display by

applying vibration to simulate

transportation and use.

Low Temperature storage

High Temperature

Operation

Low Temperature

Operation

High Temperature /

Humidity Operation

Thermal Shock resistance

Vibration test

Atmospheric Pressure test

Static electricity test

Test Condition

Test the endurance of the display by

applying atmospheric pressure to simulate

transportation by air.

Test the endurance of the display by

applying electric static discharge.

Note

+90⁰C , 240hrs

2

-40⁰C , 240hrs

1,2

+85⁰C 240hrs

2

-40⁰C , 240hrs

1,2

+60⁰C , 90% RH , 240hrs

1,2

-40⁰C,30min -> 25⁰C,5min ->

85⁰C,30min = 1 cycle

100 cycles

10-22Hz , 15mm amplitude.

22-500Hz, 1.5G

30min in each of 3 directions

X,Y,Z

115mbar, 40hrs

3

3

VS=800V, RS=1.5kΩ, CS=100pF

One time

Note 1: No condensation to be observed.

Note 2: Conducted after 2 hours of storage at 25⁰C, 0%RH.

Note 3: Test performed on product itself, not inside a container.

Evaluation Criteria:

1: Display is fully functional during operational tests and after all tests, at room temperature.

2: No observable defects.

3: Luminance >50% of initial value.

4: Current consumption within 50% of initial value

Precautions for using OLEDs/LCDs/LCMs

See Precautions at www.newhavendisplay.com/specs/precautions.pdf

Warranty Information and Terms & Conditions

http://www.newhavendisplay.com/index.php?main_page=terms

Newhaven Display International, Inc. reserves the right to alter this product or specification at any time without notification.

[14]

�