NXP Semiconductors

Data Sheet: Technical Data

K32L2B3x

Rev. 3, 09/2020

K32 L2B Microcontroller

K32L2B31Vxx0A

K32L2B21Vxx0A

K32L2B11Vxx0A

48 MHz Arm® Cortex®-M0+ and 64/128/256 KB Flash

The K32 L2B series is optimized for cost-sensitive and batterypowered applications requiring low-power USB connectivity and

an optional segment LCD (SLCD). The product offers:

• Optional low power segment LCD up to 24x8 or 28x4

• USB FS 2.0 device without requiring an external crystal

• Embedded ROM with boot loader for flexible program

upgrade

• High accuracy internal voltage and clock reference

• FlexIO to support any standard and customized serial

peripheral emulation

• Down to 54 uA/MHz in very low power run mode and 1.96

uA in deep sleep mode (RAM + RTC retained)

Core Processor

• Arm® Cortex®-M0+ core up to 48 MHz

Memories

• 64/128/256 KB program flash memory

• 32 KB SRAM

• 16 KB ROM with build-in bootloader

• 32-byte backup register

System

• 4-channel asynchronous DMA controller

• Watchdog

• Low-leakage wakeup unit

• Two-pin Serial Wire Debug (SWD) programming and

debug interface

• Micro Trace Buffer

• Bit manipulation engine

• Interrupt controller

Clocks

• 48 MHz high accuracy (up to 0.5%) internal reference

clock

• 8 MHz/2 MHz high accuracy (up to 3%) internal

reference clock

• 1 KHz reference clock active under all low-power

modes (except VLLS0)

• 32–40 KHz and 3–32 MHz crystal oscillator

32 QFN

5x5 mm P 0.5 mm

48 QFN

7x7 mm P 0.5 mm

64 LQFP

10x10 mm P 0.5 mm

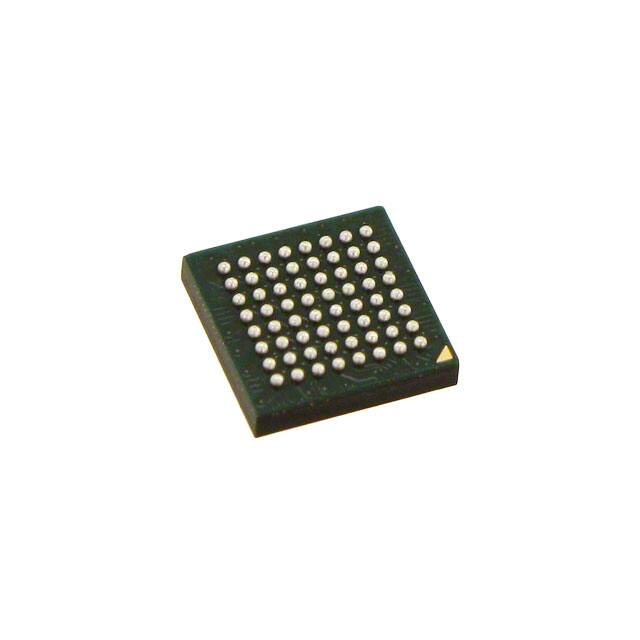

64 BGA

5x5 mm P 0.5 mm

Peripherals

• SLCD supporting up to 24x8 or 28x4 segments

• USB full-speed 2.0 device controller supporting

crystal-less operation

• One UART module supporting ISO7816, operating

up to 1.5 Mbit/s

• Two low-power UART modules supporting

asynchronous operation in low-power modes

• Two I2C modules and I2C0 supporting up to 1

Mbit/s

• Two 16-bit SPI modules supporting up to 24 Mbit/s

• One FlexIO module supporting emulation of

additional UART, SPI, I2C, PWM and other serial

modules, etc.

• One 16-bit 461 ksps ADC module with high

accuracy internal voltage reference (Vref) and up to

16 channels

• High-speed analog comparator containing a 6-bit

DAC for programmable reference input

• One 12-bit DAC

• 1.2 V internal voltage reference

I/O

• Up to 50 general-purpose input/output pins (GPIO)

and 6 high-drive pad

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

�Operating Characteristics

• Voltage range: 1.71 to 3.6 V

• Flash write voltage range: 1.71 to 3.6 V

• Temperature range: –40 to 105 °C

Timers

• One 6-channel Timer/PWM module

• Two 2-channel Timer/PWM modules

• One low-power timer

• Periodic interrupt timer

• Real time clock

Packages

• 64 LQFP 10mm x 10mm, 0.5 mm pitch, 1.6 mm

thickness

Security and Integrity

• 64 MAPBGA 5mm x 5mm, 0.5 mm pitch, 1.23 mm

• 80-bit unique identification number per chip

thickness

• Advanced flash security

• 48 QFN 7mm x 7mm, 0.5 mm pitch, 0.65 mm thickness

• 32 QFN 5mm x 5mm, 0.5 mm pitch, 0.65 mm thickness

Low Power

• Down to 54 μA/MHz in very low power run mode

• Down to 1.96 μA in VLLS3 mode (RAM + RTC

retained)

• Six flexible static modes

Related Resources

Type

Description

Resource

Selector

Guide

The NXP Selector Guide is a web-based tool that features interactive

application wizards and a dynamic product selector.

Selector Guide

Reference

Manual

The Reference Manual contains a comprehensive description of the

structure and function (operation) of a device.

K32L2B3xRM1

Data Sheet

The Data Sheet includes electrical characteristics and signal

connections.

This document.

Chip Errata

The chip mask set Errata provides additional or corrective information for K32L2B_1N71K1

a particular device mask set.

Package

drawing

Package dimensions are provided in package drawings.

64-LQFP: 98ASS23234W, 64MAPBGA: 98ASA00420D, 32QFN: 98ASA00615D, 48-QFN:

98ASA00616D1

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

2

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Table of Contents

1 Ordering information............................................................4

2 Overview............................................................................. 4

2.1 System features........................................................... 5

2.1.1

Arm Cortex-M0+ core.................................... 5

2.1.2

NVIC.............................................................. 6

2.1.3

AWIC............................................................. 6

2.1.4

Memory..........................................................7

2.1.5

Reset and boot.............................................. 7

2.1.6

Clock options................................................. 9

2.1.7

Security..........................................................12

2.1.8

Power management.......................................12

2.1.9

LLWU.............................................................14

2.1.10 Debug controller............................................ 15

2.1.11 COP............................................................... 15

2.2 Peripheral features.......................................................16

2.2.1

Segment LCD (SLCD)................................... 16

2.2.2

BME............................................................... 16

2.2.3

DMA and DMAMUX.......................................16

2.2.4

TPM............................................................... 17

2.2.5

ADC............................................................... 18

2.2.6

VREF............................................................. 19

2.2.7

CMP...............................................................19

2.2.8

DAC............................................................... 20

2.2.9

RTC............................................................... 20

2.2.10 PIT................................................................. 20

2.2.11 LPTMR...........................................................21

2.2.12 UART............................................................. 21

2.2.13 LPUART.........................................................22

2.2.14 SPI................................................................. 23

2.2.15 I2C................................................................. 23

2.2.16 USB............................................................... 24

2.2.17 FlexIO............................................................ 24

2.2.18 Port control and GPIO................................... 25

4.4.7

Human-machine interfaces (HMI)..................42

4.5 K32 L2B LQFP and MAPBGA pinouts.........................43

4.6 K32 L2B QFN Pinouts..................................................45

4.7 Package dimensions....................................................47

5 Electrical characteristics......................................................54

5.1 Ratings.........................................................................54

5.1.1

Thermal handling ratings............................... 54

5.1.2

Moisture handling ratings...............................55

5.1.3

ESD handling ratings..................................... 55

5.1.4

Voltage and current operating ratings............55

5.2 General........................................................................ 56

5.2.1

AC electrical characteristics...........................56

5.2.2

Nonswitching electrical specifications............56

5.2.3

Switching specifications.................................71

5.2.4

Thermal specifications................................... 72

5.3 Peripheral operating requirements and behaviors....... 73

5.3.1

Core modules................................................ 73

5.3.2

System modules............................................ 75

5.3.3

Clock modules............................................... 75

5.3.4

Memories and memory interfaces................. 78

5.3.5

Security and integrity modules.......................80

5.3.6

Analog............................................................80

5.4 Timers.......................................................................... 91

5.5 Communication interfaces........................................... 91

5.5.1

USB electrical specifications..........................91

5.5.2

USB VREG electrical specifications.............. 92

5.5.3

SPI switching specifications...........................92

5.5.4

I2C................................................................. 97

5.5.5

UART............................................................. 98

5.6 Human-machine interfaces (HMI)................................ 99

5.6.1

LCD electrical characteristics........................ 99

6 Design considerations......................................................... 100

6.1 Hardware design considerations..................................100

3 Memory map....................................................................... 26

4 Pinouts................................................................................ 27

4.1 K32 L2B Signal Multiplexing and Pin Assignments

(LQFP and MAPBGA)..................................................27

4.2 K32 L2B Signal Multiplexing and Pin Assignments

(QFN)........................................................................... 30

4.3 Pin properties...............................................................32

4.4 Module Signal Description Tables............................... 37

4.4.1

Core modules................................................ 37

4.4.2

System modules............................................ 37

4.4.3

Clock modules............................................... 38

4.4.4

Analog............................................................38

4.4.5

Timer Modules............................................... 39

4.4.6

Communication interfaces............................. 40

6.1.1

Printed circuit board recommendations......... 100

6.1.2

Power delivery system...................................101

6.1.3

Analog design................................................ 102

6.1.4

Digital design................................................. 102

6.1.5

Crystal oscillator............................................ 105

6.2 Software considerations...............................................107

Part identification.................................................................107

7.1 Description................................................................... 107

7.2 Format..........................................................................108

7.3 Fields........................................................................... 108

7.4 Example....................................................................... 108

Small package marking....................................................... 109

Package marking information..............................................109

Revision History.................................................................. 110

K32 L2B Microcontroller, Rev. 3, 09/2020

7

8

9

10

3

NXP Semiconductors

�Ordering information

1 Ordering information

The following chips are available for ordering.

Table 1. Ordering information

Product

Memory

Package

IO and ADC channel

Serial

Interface

Part number

Flash

(KB)

SRAM

(KB)

Pin

count

Package

GPIOs

GPIOs

(INT/HD)1

ADC

channels

(SE/DP)

SLCD

K32L2B31VLH0A

256

32

64

LQFP

50

31/6

16/2

Yes

K32L2B31VMP0A

256

32

64

MAPBGA

50

31/6

16/2

Yes

K32L2B31VFT0A

256

32

48

QFN

36

24/6

14/1

—

K32L2B31VFM0A

256

32

32

QFN

23

19/6

7/0

—

K32L2B21VLH0A

128

32

64

LQFP

50

31/6

16/2

Yes

K32L2B21VMP0A

128

32

64

MAPBGA

50

31/6

16/2

Yes

K32L2B21VFT0A

128

32

48

QFN

36

24/6

14/1

—

K32L2B21VFM0A

128

32

32

QFN

23

19/6

7/0

—

K32L2B11VLH0A

64

32

64

LQFP

50

31/6

16/2

Yes

K32L2B11VMP0A

64

32

64

MAPBGA

50

31/6

16/2

Yes

K32L2B11VFT0A

64

32

48

QFN

36

24/6

14/1

—

K32L2B11VFM0A

64

32

32

QFN

23

19/6

7/0

—

1. INT: interrupt pin numbers; HD: high drive pin numbers

2 Overview

The following figure shows the system diagram of this device

4

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

GPIOA

GPIOB

Slave

Master

Cortex M0+

GPIOC

GPIOD

GPIOE

CM0+ core

NVIC

M2

DMA

MUX

DMA

M3

FMC

S0

16 KB ROM

S1

32 KB RAM

S2

BME

USB FS Device Only

ADC(16-bit 16-ch)

64/128/256 KB

Flash

CMP

Peripheral Bridge(Bus Clock - Max 24MHZ)

Debug

(SWD)

M0

Crossabar Switch(Platform Clcok - Max 48MHZ)

IOPORT

1.2V Voltage reference

TPM0(6-channel)

TPM1(2-channel)

TPM2(2-channel)

LPTMR

PIT

RTC

LPUART0

LPUART1

UART2

SPI0

SPI1

I2C0

I2C1

FlexIO

Watchdog(COP)

MCG-Lite

OSC

Register File(32 Bytes)

HIRC48M

LLWU

LIRC2M/8M

SMC

RCM

PMC

SLCD

Figure 1. System diagram

The crossbar switch connects bus masters and slaves using a crossbar switch structure.

This structure allows up to four bus masters to access different bus slaves

simultaneously, while providing arbitration among the bus masters when they access

the same slave.

2.1 System features

The following sections describe the high-level system features.

K32 L2B Microcontroller, Rev. 3, 09/2020

5

NXP Semiconductors

�Overview

2.1.1 Arm Cortex-M0+ core

The enhanced Arm Cortex M0+ is the member of the Cortex-M series of processors

targeting microcontroller cores focused on very cost sensitive, low power applications.

It has a single 32-bit AMBA AHB-Lite interface and includes an NVIC component. It

also has hardware debug functionality including support for simple program trace

capability. The processor supports the ARMv6-M instruction set (Thumb) architecture

including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions. It

is upward compatible with other Cortex-M profile processors.

2.1.2 NVIC

The Nested Vectored Interrupt Controller supports nested interrupts and 4 priority

levels for interrupts. In the NVIC, each source in the IPR registers contains two bits. It

also differs in number of interrupt sources and supports 32 interrupt vectors.

The Cortex-M family uses a number of methods to improve interrupt latency to up to 15

clock cycles for Cortex-M0+. It also can be used to wake the MCU core from Wait and

VLPW modes.

2.1.3 AWIC

The asynchronous wake-up interrupt controller (AWIC) is used to detect asynchronous

wake-up events in Stop mode and signal to clock control logic to resume system

clocking. After clock restarts, the NVIC observes the pending interrupt and performs

the normal interrupt or event processing. The AWIC can be used to wake MCU core

from Stop and VLPS modes.

Wake-up sources are listed as below:

Table 2. AWIC stop wake-up sources

Wake-up source

Description

Available system resets

RESET pin when LPO is its clock source

Low-voltage detect

Power management controller—functional in Stop mode

Low-voltage warning

Power management controller—functional in Stop mode

Pin interrupts

Port control module—any enabled pin interrupt is capable of waking the system

ADC

The ADC is functional when using internal clock source or external crystal clock

CMP0

Interrupt in normal or trigger mode

I2Cx

Address match wakeup

Table continues on the next page...

6

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

Table 2. AWIC stop wake-up sources (continued)

Wake-up source

Description

LPUART0 , LPUART1

Any enabled interrupt can be a source as long as the module remains clocked

UART2

Active edge on RXD

RTC

Alarm or seconds interrupt

NMI

NMI pin

TPMx

Any enabled interrupt can be a source as long as the module remains clocked

LPTMR

Any enabled interrupt can be a source as long as the module remains clocked

SPIx

Slave mode interrupt

FlexIO

Any enabled interrupt can be a source as long as the module remains clocked

2.1.4 Memory

This device has the following features:

• 32 KB of embedded RAM accessible (read/write) at CPU clock speed with 0 wait

states.

• The non-volatile memory is divided into two arrays

• Up to 256 KB of embedded program memory

• 16 KB ROM (built-in bootloader to support UART, I2C, USB, and SPI

interfaces)

The program flash memory contains a 16-byte flash configuration field that stores

default protection settings and security information. The page size of program

flash is 1 KB.

The protection setting can protect 32 regions of the program flash memory from

unintended erase or program operations.

The security circuitry prevents unauthorized access to RAM or flash contents

from debug port.

• System register file

This device contains a 32-byte register file that is powered in all power modes.

Also, it retains contents during low power modes and is reset only during a

power-on reset.

K32 L2B Microcontroller, Rev. 3, 09/2020

7

NXP Semiconductors

�Overview

2.1.5 Reset and boot

The following table lists all the reset sources supported by this device.

NOTE

In the following table, Y means the specific module, except

for the registers, bits or conditions mentioned in the footnote,

is reset by the corresponding Reset source. N means the

specific module is not reset by the corresponding Reset

source.

Table 3. Reset source

Reset

sources

Descriptions

POR reset

Power-on reset (POR)

PMC

SIM

SMC

RCM

LLWU

Reset pin

is

negated

RTC

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y1

Y

Y

Y

Y

Y

N

Y

Y

Low leakage wakeup

(LLWU) reset

N

Y2

N

Y

N

Y3

N

N

Y

External pin reset

(RESET)

Y1

Y2

Y4

Y

Y

Y

N

N

Y

Computer operating

properly (COP) watchdog

reset

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

Stop mode acknowledge

error (SACKERR)

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

Software reset (SW)

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

Lockup reset (LOCKUP)

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

MDM DAP system reset

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

Debug reset

Y1

Y2

Y4

Y5

Y

Y

N

N

Y

System resets Low-voltage detect (LVD)

Debug reset

1.

2.

3.

4.

5.

Modules

LPTMR Others

Except PMC_LVDSC1[LVDV] and PMC_LVDSC2[LVWV]

Except SIM_SOPT1

Only if RESET is used to wake from VLLS mode.

Except SMC_PMCTRL, SMC_STOPCTRL, SMC_PMSTAT

Except RCM_RPFC, RCM_RPFW, RCM_FM

The CM0+ core adds support for a programmable Vector Table Offset Register

(VTOR) to relocate the exception vector table after reset. This device supports booting

from:

• internal flash

• ROM

8

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

The Flash Option (FOPT) register in the Flash Memory module (FTFA_FOPT) allows

the user to customize the operation of the MCU at boot time. The register contains

read-only bits that are loaded from the NVM's option byte in the flash configuration

field. Below is boot flow chart for this device.

POR or Reset

N

RCM[FORCEROM] =00

Y

FOPT[BOOTPIN_OPT]=0

N

Y

BOOTCFG0 pin=0

Y

N

N

FOPT[BOOTSRC

_SEL]=10/11

Y

Boot from ROM

Boot from Flash

Figure 2. Boot flow chart

The blank chip is default to boot from ROM and remaps the vector table to ROM base

address, otherwise, it remaps to flash address.

2.1.6 Clock options

This chip provides a wide range of sources to generate the internal clocks. These

sources include internal resistor capacitor (IRC) oscillators, external oscillators,

external clock sources, and ceramic resonators. These sources can be configured to

provide the required performance and optimize the power consumption.

The IRC oscillators include the high-speed internal resister capacitor (HIRC)

oscillator, the low-speed internal resister capacitor (LIRC) oscillator, and the low

power oscillator (LPO).

The HIRC oscillator generates a 48 MHz clock and synchronizes with the USB clock

in full speed mode to achieve the required accuracy.

The LIRC oscillator generates an 8 MHz or 2 MHz clock, and default to 8 MHz

system clock on reset. The LIRC oscillator cannot be used in any VLLS modes.

The LPO generates a 1 kHz clock and cannot be used in VLLS0 mode.

K32 L2B Microcontroller, Rev. 3, 09/2020

9

NXP Semiconductors

�Overview

The system oscillator supports low frequency crystals (32 kHz to 40 kHz), high

frequency crystals (3 MHz to 32 MHz), and ceramic resonators (3 MHz to 32 MHz). An

external clock source, DC to 48 MHz, can be used as the system clock through the

EXTAL0 pin. The external oscillator also supports a low speed external clock (32.768

kHz) on the RTC_CLKIN pin for use with the RTC.

For more details on the clock operations and configurations, see Reference Manual.

The following figure is a high level block diagram of the clock generation.

Multipurpose Clock

Generator Lite

IRC_TRIMs

System

Integration

HIRC48M

USB

MCGPCLK

USB_EN

MCGIRCLK

CG

LIRC_DIV2

LIRC

8MHz/ 8MHz

2MHz

IRC

2MHz

MCGOUTCLK

FCRDIV

OUTDIV1

CG

Core/Platform/System clock

OUTDIV4

CG

Bus/Flash clock

IRCS

CLKS

System oscillator

EREFS0

EXTAL0

OSCCLK

XTAL_CLK

OSC

logic OSC32KCLK

XTAL0

OSCERCLK

CG

ERCLK32K

RTC_CKLIN

OS32KSEL

RTCCLKOUTSEL

RTC

Counter logic

PMC PMC logic

LPO

RTC_CLKOUT

1Hz

CG — Clock gate

Figure 3. Clock block diagram

In order to provide flexibility, many peripherals can select from multiple clock sources

for operation. This enables the peripheral to select a clock that will always be available

during operation in various operational modes.

The following table summarizes the clocks associated with each module.

Table 4. Module clocks

Module

Bus interface clock

Internal clocks

I/O interface clocks

Core modules

Table continues on the next page...

10

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

Table 4. Module clocks (continued)

Module

Bus interface clock

Internal clocks

I/O interface clocks

Arm Cortex-M0+ core

Platform clock

Core clock

—

NVIC

Platform clock

—

—

DAP

Platform clock

—

SWD_CLK

System modules

DMA

System clock

—

—

DMA Mux

Bus clock

—

—

Port control

Bus clock

—

—

Crossbar Switch

Platform clock

—

—

Peripheral bridges

System clock

Bus clock

—

LLWU, PMC, SIM, RCM

Bus clock

LPO

—

Mode controller

Bus clock

—

—

MCM

Platform clock

—

—

COP watchdog

Bus clock

LPO, Bus Clock, MCGIRCLK,

OSCERCLK

—

Clocks

MCG_Lite

Bus clock

MCGOUTCLK, MCGPCLK,

MCGIRCLK, OSCERCLK,

ERCLK32K

—

OSC

Bus clock

OSCERCLK

—

Memory and memory interfaces

Flash Controller

Platform clock

Flash clock

—

Flash memory

Flash clock

—

—

Analog

ADC

Bus clock

OSCERCLK

—

CMP

Bus clock

—

—

Internal Voltage Reference

(VREF)

Bus clock

—

—

Timers

TPM

Bus clock

TPM clock

TPM_CLKIN0, TPM_CLKIN1

PIT

Bus clock

—

—

LPTMR

Bus clock

LPO, OSCERCLK,

MCGPCLK, ERCLK32K

—

RTC

Bus clock

ERCLK32K

RTC_CLKOUT, RTC_CLKIN

Communication interfaces

USB FS (Device Only)

System clock

USB FS clock

—

SPI0

Bus clock

—

SPI0_SCK

SPI1

System clock

—

SPI1_SCK

I2C0

System Clock

—

I2C0_SCL

I2C1

System Clock

—

I2C1_SCL

Table continues on the next page...

K32 L2B Microcontroller, Rev. 3, 09/2020

11

NXP Semiconductors

�Overview

Table 4. Module clocks (continued)

Module

Bus interface clock

Internal clocks

I/O interface clocks

LPUART0, LPUART1

Bus clock

LPUART0 clock

—

LPUART1 clock

UART2

Bus clock

—

—

FlexIO

Bus clock

FlexIO clock

—

Human-machine interfaces

GPIO

Platform clock

—

—

2.1.7 Security

Security state can be enabled via programming flash configuration field (0x40e). After

enabling device security, the SWD port cannot access the memory resources of the

MCU, and ROM boot loader is also limited to access flash and not allowed to read out

flash information via ROM boot loader commands.

Access interface

Secure state

Unsecure operation

SWD port

Cannot access memory source by SWD The debugger can write to the Flash

interface

Mass Erase in Progress field of the

MDM-AP Control register to trigger a

mass erase (Erase All Blocks)

command

ROM boot loader Interface

(UART/I2C/SPI/USB)

Limit access to the flash, cannot read

out flash content

Send “FlashEraseAllUnsecureh"

command or attempt to unlock flash

security using the backdoor key

This device features 80-bit unique identification number, which is programmed in

factory and loaded to SIM register after power-on reset.

2.1.8 Power management

The Power Management Controller (PMC) expands upon Arm’s operational modes of

Run, Sleep, and Deep Sleep, to provide multiple configurable modes. These modes can

be used to optimize current consumption for a wide range of applications. The WFI or

WFE instruction invokes a Wait or a Stop mode, depending on the current

configuration. For more information on Arm’s operational modes, See the Arm®

Cortex User Guide.

12

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

The PMC provides Run (Run), and Very Low Power Run (VLPR) configurations in

Arm’s Run operation mode. In these modes, the MCU core is active and can access all

peripherals. The difference between the modes is the maximum clock frequency of the

system and therefore the power consumption. The configuration that matches the

power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in

Arm’s Sleep operation mode. In these modes, even though the MCU core is inactive,

all of the peripherals can be enabled and operate as programmed. The difference

between the modes is the maximum clock frequency of the system and therefore the

power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS), Low Leakage Stop

(LLS), and Very Low Leakage Stop (VLLS) configurations in Arm’s Deep Sleep

operational mode. In these modes, the MCU core and most of the peripherals are

disabled. Depending on the requirements of the application, different portions of the

analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up

Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are

used to wake up the MCU from low power states. The NVIC is used to wake up the

MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU

core from STOP and VLPS modes. The LLWU is used to wake up the MCU core

from LLS and VLLSx modes.

For additional information regarding operational modes, power management, the

NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the

various operational modes and the modules that can wake MCU from low power

modes.

Table 6. Peripherals states in different operational modes

Core mode

Run mode

Sleep mode

Device mode

Descriptions

Run

In Run mode, all device modules are operational.

Very Low Power Run

In VLPR mode, all device modules are operational at a reduced frequency

except the Low Voltage Detect (LVD) monitor, which is disabled.

Wait

In Wait mode, all peripheral modules are operational. The MCU core is

placed into Sleep mode.

Very Low Power Wait

In VLPW mode, all peripheral modules are operational at a reduced

frequency except the Low Voltage Detect (LVD) monitor, which is disabled.

The MCU core is placed into Sleep mode.

Table continues on the next page...

K32 L2B Microcontroller, Rev. 3, 09/2020

13

NXP Semiconductors

�Overview

Table 6. Peripherals states in different operational modes (continued)

Core mode

Deep sleep

Device mode

Descriptions

Stop

In Stop mode, most peripheral clocks are disabled and placed in a static

state. Stop mode retains all registers and SRAMs while maintaining Low

Voltage Detection protection. In Stop mode, the ADC, CMP, LPTMR, RTC,

and pin interrupts are operational. The NVIC is disabled, but the AWIC can

be used to wake up from an interrupt.

Very Low Power Stop

In VLPS mode, the contents of the SRAM are retained. The CMP (low

speed), ADC, OSC, RTC, LPTMR, TPM, FlexIO, LPUART, USB, and DMA

are operational, LVD and NVIC are disabled, AWIC is used to wake up from

interrupt.

Low Leakage Stop

In LLS mode, the contents of the SRAM and the 32-byte system register file

are retained. The CMP (low speed), LLWU, LPTMR, and RTC are

operational. The ADC, DMA, FlexIO, I2C, LPUART, MCG-Lite, NVIC, PIT,

SPI, TPM, UART, USB, and COP are static, but retain their programming.

The GPIO, and VREF are static, retain their programming, and continue to

drive their previous values.

Very Low Leakage Stop In VLLS modes, most peripherals are powered off and will resume operation

from their reset state when the device wakes up. The LLWU, LPTMR, and

RTC are operational in all VLLS modes.

In VLLS3, the contents of the SRAM and the 32-byte system register file are

retained. The CMP (low speed), and PMC are operational. The GPIO, and

VREF are not operational but continue driving.

In VLLS1, the contents of the 32-byte system register file are retained. The

CMP (low speed), and PMC are operational. The GPIO, and VREF are not

operational but continue driving.

In VLLS0, the contents of the 32-byte system register file are retained. The

PMC is operational. The GPIO is not operational but continues driving. The

POR detection circuit can be enabled or disabled.

2.1.9 LLWU

The LLWU module is used to wake MCU from low leakage power mode (LLS and

VLLSx) and functional only on entry into a low-leakage power mode. After recovery

from LLS, the LLWU is immediately disabled. After recovery from VLLSx, the LLWU

continues to detect wake-up events until the user has acknowledged the wake-up event.

This device uses 8 external wakeup pin inputs and 4 internal modules as wakeup

sources to the LLWU module.

The following is internal peripheral and external pin inputs as wakeup sources to the

LLWU module.

14

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

Table 7. Wakeup source

LLWU pin

Module source or pin name

LLWU_P5

PTB0

LLWU_P6

PTC1

LLWU_P7

PTC3

LLWU_P8

PTC4

LLWU_P9

PTC5

LLWU_P10

PTC6

LLWU_P14

PTD4

LLWU_P15

PTD6

LLWU_M0IF

LPTMR0

LLWU_M1IF

CMP0

LLWU_M2IF

Reserved

LLWU_M3IF

Reserved

LLWU_M4IF

Reserved

LLWU_M5IF

RTC alarm

LLWU_M6IF

Reserved

LLWU_M7IF

RTC seconds

2.1.10 Debug controller

This device supports standard Arm 2-pin SWD debug port. It provides register and

memory accessibility from the external debugger interface, basic run/halt control plus

2 breakpoints and 2 watchpoints.

It also supports trace function with the Micro Trace Buffer (MTB), which provides a

simple execution trace capability for the Cortex-M0+ processor.

2.1.11 COP

The COP monitors internal system operation and forces a reset in case of failure. It

can run from bus clock, LPO, 8/2 MHz internal oscillator or external crystal oscillator.

Optional window mode can detect deviations in program flow or system frequency.

The COP has the following features:

• Support multiple clock input, 1 kHz clock(LPO), bus clock, 8/2 MHz internal

reference clock, external crystal oscillator

• Can work in Stop/VLPS and Debug mode

K32 L2B Microcontroller, Rev. 3, 09/2020

15

NXP Semiconductors

�Overview

• Configurable for short and long timeout values, the longest timeout is up to 262

seconds

• Support window mode

2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

2.2.1 Segment LCD (SLCD)

The SLCD module is a CMOS charge pump voltage inverter that is designed for lowvoltage and low-power operation. SLCD is designed to generate the appropriate

waveforms to drive multiplexed numeric, alphanumeric, or custom segment LCD

panels. SLCD also has several timing and control settings that can be software

configured depending on the application's requirements. Timing and control consists of

registers and control logic for:

• LCD frame frequency

• Duty cycle selection

• Front plane/back plane selection and enabling

• Blink modes and frequency

• Operation in low-power modes

2.2.2 BME

The Bit Manipulation Engine (BME) provides hardware support for atomic readmodify-write memory operations to the peripheral address space in Cortex-M0+ based

microcontrollers. It reduces up to 30% of the code size and up to 9% of the cycles for

bit-oriented operations to peripheral registers.

The BME supports unsigned bit field extract, load-and-set 1-bit, load-and-clear 1-bit,

bit field insert, logical AND/OR/XOR operations with byte, halfword or word-sized

data type.

16

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

2.2.3 DMA and DMAMUX

The DMA controller module enables fast transfers of data, which provides an efficient

way to move blocks of data with minimal processor interaction. The DMA controller

in this device implements four channels which can be routed from up to 63 DMA

request sources through DMA MUX module. Some of the peripheral request sources

have asynchronous DMA capability which can be used to wake MCU from Stop

mode. The peripherals which have such capability include . The DMA channel 0 and

1 can be periodically triggered by PIT via DMA MUX.

Main features are listed below:

• Dual-address transfers via 32-bit master connection to the system bus and data

transfers in 8-, 16-, or 32-bit blocks

• Supports programmable source and destination address and transfer size, optional

modulo addressing from 16 bytes to 256 KB

• Automatic updates of source and destination addresses

• Auto-alignment feature for source or destination accesses allows block transfers

to occur at the optimal size based on the address, byte count,and programmed

size, which significantly improves the speed of block transfer

• Automatic single or double channel linking allows the current DMA channel to

automatically trigger a DMA request to the linked channels without CPU

intervention

For more information on asynchronous DMA, see AN4631.

2.2.4 TPM

This device contains three low power TPM modules (TPM). All TPM modules are

functional in Stop/VLPS mode if the clock source is enabled.

The TPM features include:

• TPM clock mode is selectable from external clock input, internal clock source,

external crystal input clock, MCGIRCLK clock or clocking from MCGFLLCLK

and MCGPLLCLK/2

• Prescaler divide-by 1, 2, 4, 8, 16, 32, 64, or 128

• TPM includes a 16-bit counter

• Includes 6 channels that can be configured for input capture, output compare,

edge-aligned PWM mode, or center-aligned PWM mode

• Support the generation of an interrupt and/or DMA request per channel or counter

overflow

K32 L2B Microcontroller, Rev. 3, 09/2020

17

NXP Semiconductors

�Overview

• Support selectable trigger input to optionally reset or cause the counter to start or

stop incrementing

• Support the generation of hardware triggers when the counter overflows and per

channel

2.2.5 ADC

This device contains one ADC module. This ADC module supports hardware triggers

from TPM, LPTMR, PIT, RTC, external trigger pin and CMP output. It supports

wakeup of MCU in low power mode when using internal clock source or external

crystal clock.

ADC module has the following features:

• Linear successive approximation algorithm with up to 16-bit resolution

• Up to four pairs of differential and 17 single-ended external analog inputs

• Support selectable 16-bit, 13-bit, 11-bit, and 9-bit differential output mode, or 16bit, 12-bit, 10-bit, and 8-bit single-ended output modes

• Single or continuous conversion

• Configurable sample time and conversion speed/power

• Selectable clock source up to four

• Operation in low-power modes for lower noise

• Asynchronous clock source for lower noise operation with option to output the

clock

• Selectable hardware conversion trigger

• Automatic compare with interrupt for less-than, greater-than or equal-to, within

range, or out-of-range, programmable value

• Temperature sensor

• Hardware average function up to 32x

• Selectable voltage reference: external or alternate

• Self-calibration mode

2.2.5.1

Temperature sensor

This device integrates one temperature sensor internally connected to the input channel

of AD26, see for details of the linearity factor.

The sensor provides good linearity, but it has to be calibrated to gain good accuracy, see

also AN3031. We recommend to use internal reference voltage as ADC reference with

long sample time.

18

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

2.2.6 VREF

The Voltage Reference (VREF) can supply an accurate voltage output (1.2V typically)

trimmed in 0.5 mV steps. It can be used in applications to provide a reference voltage

to external devices or used internally as a reference to analog peripherals such as the

ADC or CMP.

The VREF supports the following programmable buffer modes:

• Bandgap on only, used for stabilization and startup

• High power buffer mode

• Low-power buffer mode

• Buffer disabled

The VREF voltage output signal, bonded on VREFH for 48 QFN, 64 LQFP and 64

MAPBGA packages and on PTE30 for 32 QFN packages, can be used by both

internal and external peripherals in low and high power buffer mode. A 100 nF

capacitor must always be connected between this pin and VSSA if the VREF is used.

This capacitor must be as close to VREF_OUT pin as possible.

2.2.7 CMP

The device contains one high-speed comparator and two 8-input multiplexers for both

the inverting and non-inverting inputs of the comparator. Each CMP input channel

connects to both muxes.

The CMP includes one 6-bit DAC, which provides a selectable voltage reference for

various user application cases. Besides, the CMP also has several module-to-module

interconnects in order to facilitate ADC triggering, TPM triggering, and interfaces.

The CMP has the following features:

• Inputs may range from rail to rail

• Programmable hysteresis control

• Selectable interrupt on rising-edge, falling-edge, or both rising or falling edges of

the comparator output

• Selectable inversion on comparator output

• Capability to produce a wide range of outputs such as sampled, digitally filtered

• External hysteresis can be used at the same time that the output filter is used for

internal functions

• Two software selectable performance levels: shorter propagation delay at the

expense of higher power and Low power with longer propagation delay

K32 L2B Microcontroller, Rev. 3, 09/2020

19

NXP Semiconductors

�Overview

•

•

•

•

DMA transfer support

Functional in all modes of operation except in VLLS0 mode

The filter functions are not available in Stop, VLPS, LLS, or VLLSx modes

Integrated 6-bit DAC with selectable supply reference source and can be power

down to conserve power

• Two 8-to-1 channel mux

2.2.8 DAC

The 12-bit Digital-to-Analog Converter (DAC) is a low-power, general-purpose DAC.

The output of the DAC can be placed on an external pin or set as one of the inputs to

the analog comparator, op-amps, or ADC.

The features of the DAC module include:

• On-chip programmable reference generator output. The voltage output range is

from 1⁄4096 Vin to Vin, and the step is 1⁄4096 Vin, where Vin is the input voltage.

• Vin can be selected from two reference sources.

• Static operation in Normal Stop mode.

• 2-word data buffer supported with multiple operation modes.

• DMA support.

2.2.9 RTC

The RTC is an always powered-on block that remains active in all low power modes.

The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an

external crystal using the oscillator or clock directly from RTC_CLKIN pin.

RTC is reset on power-on reset, and a software reset bit in RTC can also initialize all

RTC registers.

The RTC module has the following features

• 32-bit seconds counter with roll-over protection and 32-bit alarm

• 16-bit prescaler with compensation that can correct errors between 0.12 ppm and

3906 ppm

• Register write protection with register lock mechanism

• 1 Hz square wave or second pulse output with optional interrupt

20

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

2.2.10 PIT

The Periodic Interrupt Timer (PIT) is used to generate periodic interrupt to the CPU. It

has two independent channels and each channel has a 32-bit counter. Both channels

can be chained together to form a 64-bit counter.

Channel 0 can be used to periodically trigger DMA channel 0, and channel 1 can be

used to periodically trigger DMA channel 1. Either channel can be programmed as an

ADC trigger source, or TPM trigger source. Channel 0 can be programmed to trigger

DAC.

The PIT module has the following features:

• Each 32-bit timers is able to generate DMA trigger

• Each 32-bit timers is able to generate timeout interrupts

• Two timers can be cascaded to form a 64-bit timer

• Each timer can be programmed as ADC/TPM trigger source

• Timer 0 is able to trigger DAC

2.2.11 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with

optional prescaler, or as a pulse counter with optional glitch filter, across all power

modes, including the low-leakage modes. It can also continue operating through most

system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

• 16-bit time counter or pulse counter with compare

• Optional interrupt can generate asynchronous wakeup from any low-power

mode

• Hardware trigger output

• Counter supports free-running mode or reset on compare

• Configurable clock source for prescaler/glitch filter

• Configurable input source for pulse counter

2.2.12 UART

This device contains a basic universal asynchronous receiver/transmitter (UART)

module with DMA function supported. Generally, this module is used in RS-232,

RS-485, and other communications. It also supports LIN slave operation and

ISO7816.

K32 L2B Microcontroller, Rev. 3, 09/2020

21

NXP Semiconductors

�Overview

The UART module has the following features:

• Full-duplex operation

• 13-bit baud rate selection with /32 fractional divide, based on the module clock

frequency

• Programmable 8-bit or 9-bit data format

• Programmable transmitter output polarity

• Programmable receive input polarity

• Up to 14-bit break character transmission.

• 11-bit break character detection option

• Two receiver wakeup methods with idle line or address mark wakeup

• Address match feature in the receiver to reduce address mark wakeup ISR overhead

• Ability to select MSB or LSB to be the first bit on wire

• Support for ISO 7816 protocol to interface with SIM cards and smart cards

• Receiver framing error detection

• Hardware parity generation and checking

• 1/16 bit-time noise detection

• DMA interface

2.2.13 LPUART

This product contains two Low-Power UART modules, both of their clock sources are

selectable from IRC48M, IRC8M/2M or external crystal clock, and can work in Stop

and VLPS modes. They also support 4x to 32x data oversampling rate to meet different

applications.

The LPUART module has the following features:

• Programmable baud rates (13-bit modulo divider) with configurable oversampling

ratio from 4x to 32x

• Transmit and receive baud rate can operate asynchronous to the bus clock and can

be configured independently of the bus clock frequency, support operation in Stop

mode

• Interrupt, DMA or polled operation

• Hardware parity generation and checking

• Programmable 8-bit, 9-bit or 10-bit character length

• Programmable 1-bit or 2-bit stop bits

• Three receiver wakeup methods

• Idle line wakeup

• Address mark wakeup

• Receive data match

• Automatic address matching to reduce ISR overhead:

22

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

• Address mark matching

• Idle line address matching

• Address match start, address match end

• Optional 13-bit break character generation / 11-bit break character detection

• Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle

characters

• Selectable transmitter output and receiver input polarity

2.2.14 SPI

This device contains two SPI modules. SPI modules support 8-bit and 16-bit modes.

FIFO function is available only on SPI1 module.

The SPI modules have the following features:

• Full-duplex or single-wire bidirectional mode

• Programmable transmit bit rate

• Double-buffered transmit and receive data register

• Serial clock phase and polarity options

• Slave select output

• Mode fault error flag with CPU interrupt capability

• Control of SPI operation during wait mode

• Selectable MSB-first or LSB-first shifting

• Programmable 8- or 16-bit data transmission length

• Receive data buffer hardware match feature

• 64-bit FIFO mode for high speed/large amounts of data transfers

• Support DMA

2.2.15 I2C

This device contains two I2C modules, which support up to 1 Mbits/s by dual buffer

features, and address match to wake MCU from the low power mode.

I2C modules support DMA transfer, and the interrupt condition can trigger DMA

request when DMA function is enabled.

The I2C modules have the following features:

• Support for system management bus (SMBus) specification, version 2

• Software programmable for one of 64 different serial clock frequencies

• Software-selectable acknowledge bit

• Arbitration-lost interrupt with automatic mode switching from master to slave

K32 L2B Microcontroller, Rev. 3, 09/2020

23

NXP Semiconductors

�Overview

•

•

•

•

•

•

•

•

•

•

•

•

Calling address identification interrupt

START and STOP signal generation and detection

Repeated-START signal generation and detection

Acknowledge bit generation and detection

Bus busy detection

General call recognition

10-bit address extension

Programmable input glitch filter

Low power mode wakeup on slave address match

Range slave address support

DMA support

Double buffering support to achieve higher baud rate

2.2.16 USB

This device contains one USB module which implements a USB2.0 full-speed

compliant peripheral and interfaces to the on-chip USBFS transceiver. It implements

keep-alive feature to avoid re-enumerating when exiting from low power modes and

enables HIRC48M to allow crystal-less USB operation.

The USBFS has the following features:

• USB 1.1 and 2.0 compliant full-speed device controller

• 16 bidirectional end points

• DMA or FIFO data stream interfaces

• Low-power consumption

• HIRC48 with clock-recovery is supported to eliminate the 48 MHz crystal. It is

used for USB device-only implementation.

• USB keeps alive in low power mode down to VLPS and is able to wake MCU from

low power mode

2.2.17 FlexIO

The FlexIO is a highly configurable module providing a wide range of protocols

including, but not limited to UART, I2C, SPI, Camera IF, LCD RGB, PWM/Waveform

generation. The module supports programmable baud rates independent of bus clock

frequency, with automatic start/stop bit generation.

The FlexIO module has the following features:

24

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Overview

• Functional in VLPR/VLPW/Stop/VLPS mode provided the clock it is using

remains enabled

• Four 32-bit double buffered shift registers with transmit, receive, and data match

modes, and continuous data transfer

• The timing of the shifter's shift, load and store events are controlled by the highly

flexible 16-bit timer assigned to the shifter

• Two or more shifters can be concatenated to support large data transfer sizes

• Each 16-bit timers operates independently, supports for reset, enable and disable

on a variety of internal or external trigger conditions with programmable trigger

polarity

• Flexible pin configuration supporting output disabled, open drain, bidirectional

output data and output mode

• Supports interrupt, DMA or polled transmit/receive operation

2.2.18 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control,

digital filtering, and external interrupt functions. The GPIO data direction and output

data registers control the direction and output data of each pin when the pin is

configured for the GPIO function. The GPIO input data register displays the logic

value on each pin when the pin is configured for any digital function, provided the

corresponding Port Control and Interrupt module for that pin is enabled.

The PORT module has the following features:

• all PIN support interrupt enable

• Configurable edge (rising, falling, or both) or level sensitive interrupt type

• Support DMA request

• Asynchronous wake-up in low-power modes

• Configurable pullup, pulldown, and pull-disable on select pins

• Configurable high and low drive strength on selected pins

• Configurable fast and slow slew rates on selected pins

• Configurable passive filter on selected pins

• Individual mux control field supporting analog or pin disabled, GPIO, and up to

chip-specific digital functions

• Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

• Port Data Input register visible in all digital pin-multiplexing modes

• Port Data Output register with corresponding set/clear/toggle registers

K32 L2B Microcontroller, Rev. 3, 09/2020

25

NXP Semiconductors

�Memory map

• Port Data Direction register

• GPIO support single-cycle access via fast GPIO.

3 Memory map

This device contains various memories and memory-mapped peripherals which are

located in a 4 GB memory space. The following figure shows the system memory and

peripheral locations

0x4000_0000

Reserved

0x4000_8000

DMA controller

0x4000_F000

0x4002_0000

0x0000_0000

0x4002_1000

Flash

0x0000_0000

0x07FF_FFFF

Code space

0x07FF_FFFF

0x1C00_0000

0x1C00_0000

ROM

Boot ROM

0x1C00_3FFF

0x1C00_4000

0x1FFF_E000

Data Space

0x2000_5FFF

SRAM_L

0x2000_0000

Reserved

SRAM_U

0x4000_0000

0x2000_5FFF

Public

peripheral

0x4000_0000

0x400F_F000

0x4400_0000

0x6000_0000

0xE000_0000

0xE010_0000

0x4007_FFFF

Reserved

AIPS

peripherals

0x400F_F000

BME

Reserved

0x400F_FFFF

Private

peripheral

GPIO

Reserved

MTB

MTBDWT

Others

Others

ROM Table

MCM

0xFFFF_FFFF

Reserved

IOPORT

Flash memory

DMA Channel Multiplexer

0x4003_7000

PIT

0x4003_8000

LPTPM0

0x4003_9000

LPTPM1

0x4003_A000

LPTPM2

0x4003_B000

ADC0

0x4003_D000

RTC

0x4003_F000

DAC

0x4004_0000

LPTMR

0x4004_1000

0x4004_7000

0x1FFF_E000

GPIO Controller (alias to 0x400F_F000)

System register file

SIM low power logic

0x4004_8000

SIM

0x4004_9000

PORTA

0x4004_A000

PORTB

0x4004_B000

PORTC

0x4004_C000

PORTD

0x4004_D000

PORTE

0x4005_3000

SLCD

0x4005_4000

LPUART0

0x4005_5000

LPUART1

0x4005_F000

FlexIO

0x4006_4000

MCG Lite

0x4006_5000

OSC

0x4006_6000

I2C0

0x4006_7000

I2C1

0x4006_C000

UART2

0x4007_2000

USB

0x4007_3000

CMP

0x4007_4000

VREF

0x4007_6000

SPI0

0x4007_7000

SPI1

0x4007_C000

LLWU

0x4007_D000

PMC

0x4007_E000

SMC

0x4007_F000

RCM

GPIO

0x400F_F000

Figure 4. Memory map

26

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020

�Pinouts

4 Pinouts

4.1 K32 L2B Signal Multiplexing and Pin Assignments (LQFP

and MAPBGA)

The following table shows the signals available on each pin and the locations of these

pins on the devices supported by this document. The Port Control Module is

responsible for selecting which ALT functionality is available on each pin.

NOTE

VREFH can act as VREF_OUT when VREFV1 module is

enabled.

NOTE

When FTFA_FOPT[RESET_PIN_CONFIG]=0, the PTA20

pin acts as RESET_B function only during the POR. After

POR, this pin cannot be used as the RESET function. Then,

writing to PORTA_PCR20[MUX]=0x1, the PTA20 pin will

act as GPIO function (with setting value of ALT1). When

FTFA_FOPT[RESET_PIN_CONFIG]=1, the PTA20 pin

acts as RESET_B and cannot switch to GPIO function

regardless of PORTA_PCR20[MUX]'s setting value.

64

64

MAP LQFP

BGA

Pin Name

Default

ALT0

ALT1

ALT2

ALT3

ALT4

ALT5

ALT6

ALT7

A1

1

PTE0

LCD_P48

LCD_P48

PTE0/

CLKOUT32K

SPI1_MISO

LPUART1_TX RTC_CLKOUT CMP0_OUT

I2C1_SDA

LCD_P48

B1

2

PTE1

LCD_P49

LCD_P49

PTE1

SPI1_MOSI

LPUART1_RX

I2C1_SCL

LCD_P49

—

3

VDD

VDD

VDD

C4

4

VSS

VSS

VSS

E1

5

USB0_DP

USB0_DP

USB0_DP

D1

6

USB0_DM

USB0_DM

USB0_DM

E2

7

VOUT33

VOUT33

VOUT33

D2

8

VREGIN

VREGIN

VREGIN

G1

9

PTE20

LCD_P59/

ADC0_DP0/

ADC0_SE0

LCD_P59/

ADC0_DP0/

ADC0_SE0

FXIO0_D4

LCD_P59

K32 L2B Microcontroller, Rev. 3, 09/2020

PTE20

TPM1_CH0

SPI1_MISO

LPUART0_TX

27

NXP Semiconductors

�Pinouts

64

64

MAP LQFP

BGA

Pin Name

Default

ALT0

ALT1

ALT2

ALT3

ALT4

ALT5

ALT6

ALT7

LCD_P60

F1

10

PTE21

LCD_P60/

ADC0_DM0/

ADC0_SE4a

LCD_P60/

ADC0_DM0/

ADC0_SE4a

PTE21

TPM1_CH1

LPUART0_RX

FXIO0_D5

G2

11

PTE22

ADC0_DP3/

ADC0_SE3

ADC0_DP3/

ADC0_SE3

PTE22

TPM2_CH0

UART2_TX

FXIO0_D6

F2

12

PTE23

ADC0_DM3/

ADC0_SE7a

ADC0_DM3/

ADC0_SE7a

PTE23

TPM2_CH1

UART2_RX

FXIO0_D7

F4

13

VDDA

VDDA

VDDA

G4

14

VREFH

VREFH

VREFH

G3

15

VREFL

VREFL

VREFL

F3

16

VSSA

VSSA

VSSA

H1

17

PTE29

CMP0_IN5/

ADC0_SE4b

CMP0_IN5/

ADC0_SE4b

PTE29

TPM0_CH2

TPM_CLKIN0

H2

18

PTE30

DAC0_OUT/

ADC0_SE23/

CMP0_IN4

DAC0_OUT/

ADC0_SE23/

CMP0_IN4

PTE30

TPM0_CH3

TPM_CLKIN1

H3

19

PTE31

DISABLED

PTE31

TPM0_CH4

H4

20

PTE24

DISABLED

PTE24

TPM0_CH0

I2C0_SCL

H5

21

PTE25

DISABLED

PTE25

TPM0_CH1

I2C0_SDA

D3

22

PTA0

SWD_CLK

PTA0

TPM0_CH5

D4

23

PTA1

DISABLED

PTA1

LPUART0_RX TPM2_CH0

E5

24

PTA2

DISABLED

PTA2

LPUART0_TX TPM2_CH1

D5

25

PTA3

SWD_DIO

PTA3

I2C1_SCL

TPM0_CH0

SWD_DIO

G5

26

PTA4

NMI_b

PTA4

I2C1_SDA

TPM0_CH1

NMI_b

USB_CLKIN

TPM0_CH2

LPUART1_TX LPTMR0_

ALT1

SWD_CLK

F5

27

PTA5

DISABLED

PTA5

H6

28

PTA12

DISABLED

PTA12

TPM1_CH0

G6

29

PTA13

DISABLED

PTA13

TPM1_CH1

G7

30

VDD

VDD

VDD

H7

31

VSS

VSS

VSS

H8

32

PTA18

EXTAL0

EXTAL0

PTA18

LPUART1_RX TPM_CLKIN0

G8

33

PTA19

XTAL0

XTAL0

PTA19

LPUART1_TX TPM_CLKIN1

F8

34

PTA20

RESET_b

F7

35

PTB0/

LLWU_P5

LCD_P0/

ADC0_SE8

LCD_P0/

ADC0_SE8

PTB0/

LLWU_P5

I2C0_SCL

TPM1_CH0

LCD_P0

F6

36

PTB1

LCD_P1/

ADC0_SE9

LCD_P1/

ADC0_SE9

PTB1

I2C0_SDA

TPM1_CH1

LCD_P1

E7

37

PTB2

LCD_P2/

ADC0_SE12

LCD_P2/

ADC0_SE12

PTB2

I2C0_SCL

TPM2_CH0

LCD_P2

E8

38

PTB3

LCD_P3/

ADC0_SE13

LCD_P3/

ADC0_SE13

PTB3

I2C0_SDA

TPM2_CH1

LCD_P3

E6

39

PTB16

LCD_P12

LCD_P12

PTB16

SPI1_MOSI

LPUART0_RX TPM_CLKIN0

28

NXP Semiconductors

LPTMR0_

ALT1

SPI1_MISO

LCD_P12

K32 L2B Microcontroller, Rev. 3, 09/2020

�Pinouts

64

64

MAP LQFP

BGA

Pin Name

Default

ALT0

ALT1

ALT2

ALT4

LPUART0_TX TPM_CLKIN1

ALT5

ALT6

40

PTB17

LCD_P13

LCD_P13

PTB17

D6

41

PTB18

LCD_P14

LCD_P14

PTB18

TPM2_CH0

LCD_P14

C7

42

PTB19

LCD_P15

LCD_P15

PTB19

TPM2_CH1

LCD_P15

D8

43

PTC0

LCD_P20/

ADC0_SE14

LCD_P20/

ADC0_SE14

PTC0

EXTRG_IN

C6

44

PTC1/

LLWU_P6/

RTC_CLKIN

LCD_P21/

ADC0_SE15

LCD_P21/

ADC0_SE15

PTC1/

LLWU_P6/

RTC_CLKIN

I2C1_SCL

TPM0_CH0

LCD_P21

B7

45

PTC2

LCD_P22/

ADC0_SE11

LCD_P22/

ADC0_SE11

PTC2

I2C1_SDA

TPM0_CH1

LCD_P22

C8

46

PTC3/

LLWU_P7

LCD_P23

LCD_P23

PTC3/

LLWU_P7

SPI1_SCK

LPUART1_RX TPM0_CH2

E3

47

VSS

VSS

VSS

E4

—

VDD

VDD

VDD

C5

48

VLL3

VLL3

VLL3

A6

49

VLL2

VLL2/

LCD_P4

VLL2/

LCD_P4

PTC20

LCD_P4

B5

50

VLL1

VLL1/

LCD_P5

VLL1/

LCD_P5

PTC21

LCD_P5

B4

51

VCAP2

VCAP2/

LCD_P6

VCAP2/

LCD_P6

PTC22

LCD_P6

A5

52

VCAP1

VCAP1/

LCD_P39

VCAP1/

LCD_P39

PTC23

LCD_P39

B8

53

PTC4/

LLWU_P8

LCD_P24

LCD_P24

PTC4/

LLWU_P8

SPI0_SS

LPUART1_TX TPM0_CH3

A8

54

PTC5/

LLWU_P9

LCD_P25

LCD_P25

PTC5/

LLWU_P9

SPI0_SCK

LPTMR0_

ALT2

A7

55

PTC6/

LLWU_P10

LCD_P26/

CMP0_IN0

LCD_P26/

CMP0_IN0

PTC6/

LLWU_P10

SPI0_MOSI

EXTRG_IN

SPI0_MISO

LCD_P26

B6

56

PTC7

LCD_P27/

CMP0_IN1

LCD_P27/

CMP0_IN1

PTC7

SPI0_MISO

audioUSB_

SOF_OUT

SPI0_MOSI

LCD_P27

C3

57

PTD0

LCD_P40

LCD_P40

PTD0

SPI0_SS

TPM0_CH0

FXIO0_D0

LCD_P40

A4

58

PTD1

LCD_P41/

ADC0_SE5b

LCD_P41/

ADC0_SE5b

PTD1

SPI0_SCK

TPM0_CH1

FXIO0_D1

LCD_P41

C2

59

PTD2

LCD_P42

LCD_P42

PTD2

SPI0_MOSI

UART2_RX

TPM0_CH2

SPI0_MISO

FXIO0_D2

LCD_P42

B3

60

PTD3

LCD_P43

LCD_P43

PTD3

SPI0_MISO

UART2_TX

TPM0_CH3

SPI0_MOSI

FXIO0_D3

LCD_P43

A3

61

PTD4/

LLWU_P14

LCD_P44

LCD_P44

PTD4/

LLWU_P14

SPI1_SS

UART2_RX

TPM0_CH4

FXIO0_D4

LCD_P44

C1

62

PTD5

LCD_P45/

ADC0_SE6b

LCD_P45/

ADC0_SE6b

PTD5

SPI1_SCK

UART2_TX

TPM0_CH5

FXIO0_D5

LCD_P45

B2

63

PTD6/

LLWU_P15

LCD_P46/

ADC0_SE7b

LCD_P46/

ADC0_SE7b

PTD6/

LLWU_P15

SPI1_MOSI

LPUART0_RX

SPI1_MISO

FXIO0_D6

LCD_P46

A2

64

PTD7

LCD_P47

LCD_P47

PTD7

SPI1_MISO

LPUART0_TX

SPI1_MOSI

FXIO0_D7

LCD_P47

audioUSB_

SOF_OUT

SPI1_MOSI

ALT7

D7

K32 L2B Microcontroller, Rev. 3, 09/2020

SPI1_MISO

ALT3

LCD_P13

CMP0_OUT

LCD_P20

CLKOUT

LCD_P23

LCD_P24

CMP0_OUT

LCD_P25

29

NXP Semiconductors

�Pinouts

4.2 K32 L2B Signal Multiplexing and Pin Assignments (QFN)

The following table shows the signals available on each pin and the locations of these

pins on the devices supported by this document. The Port Control Module is responsible

for selecting which ALT functionality is available on each pin.

NOTE

When FTFA_FOPT[RESET_PIN_CONFIG]=0, the PTA20

pin acts as RESET_B function only during the POR. After

POR, this pin cannot be used as the RESET function. Then,

writing to PORTA_PCR20[MUX]=0x1, the PTA20 pin will

act as GPIO function (with setting value of ALT1). When

FTFA_FOPT[RESET_PIN_CONFIG]=1, the PTA20 pin acts

as RESET_B and cannot switch to GPIO function regardless

of PORTA_PCR20[MUX]'s setting value.

32

QFN

48

QFN

Pin Name

Default

ALT0

—

1

VDD

VDD

VDD

—

7

PTE20

ADC0_DP0/

ADC0_SE0

ADC0_DP0/

ADC0_SE0

PTE20

TPM1_CH0

LPUART0_TX

FXIO0_D4

—

8

PTE21

ADC0_DM0/

ADC0_SE4a

ADC0_DM0/

ADC0_SE4a

PTE21

TPM1_CH1

LPUART0_RX

FXIO0_D5

—

10

VREFH

VREFH

VREFH

—

11

VREFL

VREFL

VREFL

—

13

PTE29

CMP0_IN5/

ADC0_SE4b

CMP0_IN5/

ADC0_SE4b

PTE29

TPM0_CH2

TPM_CLKIN0

—

15

PTE24

DISABLED

PTE24

TPM0_CH0

I2C0_SCL

—

16

PTE25

DISABLED

PTE25

TPM0_CH1

I2C0_SDA

—

29

PTB2

ADC0_SE12

ADC0_SE12

PTB2

I2C0_SCL

TPM2_CH0

—

30

PTB3

ADC0_SE13

ADC0_SE13

PTB3

I2C0_SDA

TPM2_CH1

—

31

PTB16

DISABLED

PTB16

SPI1_MOSI

LPUART0_RX TPM_CLKIN0

SPI1_MISO

—

32

PTB17

DISABLED

PTB17

SPI1_MISO

LPUART0_TX

TPM_CLKIN1

SPI1_MOSI

—

33

PTC0

ADC0_SE14

EXTRG_IN

audioUSB_

SOF_OUT

CMP0_OUT

—

41

PTD0

DISABLED

—

42

PTD1

ADC0_SE5b

—

43

PTD2

—

44

1

2

ADC0_SE14

ALT1

ALT2

PTC0

ALT3

ALT4

ALT5

ALT6

PTD0

SPI0_SS

TPM0_CH0

FXIO0_D0

PTD1

SPI0_SCK

TPM0_CH1

FXIO0_D1

DISABLED

PTD2

SPI0_MOSI

UART2_RX

TPM0_CH2

SPI0_MISO

FXIO0_D2

PTD3

DISABLED

PTD3

SPI0_MISO

UART2_TX

TPM0_CH3

SPI0_MOSI

FXIO0_D3

—

PTE0

DISABLED

PTE0/

CLKOUT32K

SPI1_MISO

LPUART1_TX

RTC_CLKOUT CMP0_OUT

I2C1_SDA

2

VSS

VSS

30

NXP Semiconductors

ADC0_SE5b

ALT7

VSS

K32 L2B Microcontroller, Rev. 3, 09/2020

�Pinouts

32

QFN

48

QFN

Pin Name

Default

ALT0

3

3

USB0_DP

USB0_DP

USB0_DP

4

4

USB0_DM

USB0_DM

USB0_DM

5

5

VOUT33

VOUT33

VOUT33

6

6

VREGIN

VREGIN

VREGIN

7

9

VDDA

VDDA

VDDA

8

12

VSSA

VSSA

VSSA

9

14

PTE30

DAC0_OUT/

ADC0_SE23/

CMP0_IN4

DAC0_OUT/

ADC0_SE23/

CMP0_IN4

10

17

PTA0

11

18

12

ALT1

ALT2

ALT3

ALT4

ALT5

TPM_CLKIN1

LPUART1_TX

ALT6

ALT7

PTE30

TPM0_CH3

SWD_CLK

PTA0

TPM0_CH5

PTA1

DISABLED

PTA1

LPUART0_RX TPM2_CH0

19

PTA2

DISABLED

PTA2

LPUART0_TX

TPM2_CH1

13

20

PTA3

SWD_DIO

PTA3

I2C1_SCL

TPM0_CH0

SWD_DIO

14

21

PTA4

NMI_b

PTA4

I2C1_SDA

TPM0_CH1

NMI_b

15

22

VDD

VDD

VDD

16

23

VSS

VSS

VSS

17

24

PTA18

EXTAL0

EXTAL0

PTA18

LPUART1_RX TPM_CLKIN0

18

25

PTA19

XTAL0

XTAL0

PTA19

LPUART1_TX

19

26

PTA20

RESET_b

20

27

PTB0/

LLWU_P5

ADC0_SE8

ADC0_SE8

PTB0/

LLWU_P5

I2C0_SCL

TPM1_CH0

21

28

PTB1

ADC0_SE9

ADC0_SE9

PTB1

I2C0_SDA

TPM1_CH1

22

34

PTC1/

LLWU_P6/

RTC_CLKIN

ADC0_SE15

ADC0_SE15

PTC1/

LLWU_P6/

RTC_CLKIN

I2C1_SCL

TPM0_CH0

23

35

PTC2

ADC0_SE11

ADC0_SE11

PTC2

I2C1_SDA

TPM0_CH1

24

36

PTC3/

LLWU_P7

DISABLED

PTC3/

LLWU_P7

SPI1_SCK

LPUART1_RX TPM0_CH2

25

37

PTC4/

LLWU_P8

DISABLED

PTC4/

LLWU_P8

SPI0_SS

LPUART1_TX

26

38

PTC5/

LLWU_P9

DISABLED

PTC5/

LLWU_P9

SPI0_SCK

LPTMR0_

ALT2

27

39

PTC6/

LLWU_P10

CMP0_IN0

CMP0_IN0

PTC6/

LLWU_P10

SPI0_MOSI

EXTRG_IN

SPI0_MISO

28

40

PTC7

CMP0_IN1

CMP0_IN1

PTC7

SPI0_MISO

audioUSB_

SOF_OUT

SPI0_MOSI

29

45

PTD4/

LLWU_P14

DISABLED

PTD4/

LLWU_P14

SPI1_SS

UART2_RX

TPM0_CH4

FXIO0_D4

30

46

PTD5

ADC0_SE6b

ADC0_SE6b

PTD5

SPI1_SCK

UART2_TX

TPM0_CH5

FXIO0_D5

31

47

PTD6/

LLWU_P15

ADC0_SE7b

ADC0_SE7b

PTD6/

LLWU_P15

SPI1_MOSI

LPUART0_RX

SPI1_MISO

FXIO0_D6

32

48

PTD7

DISABLED

PTD7

SPI1_MISO

LPUART0_TX

SPI1_MOSI

FXIO0_D7

K32 L2B Microcontroller, Rev. 3, 09/2020

LPTMR0_

ALT1

SWD_CLK

TPM_CLKIN1

LPTMR0_

ALT1

CLKOUT

TPM0_CH3

CMP0_OUT

31

NXP Semiconductors

�Pinouts

4.3 Pin properties

Pin interrupt

Open drain

Passive pin filter after POR

Slew rate after POR

Pullup/ pulldown setting after POR

Default status after POR

Driver strength

Pin name

64 LQFP

64 MAPBGA

The following table lists the pin properties of 64 LQFP/MAPBGA package.

1

A1

PTE0

ND

Hi-Z

—

SS

N

N

N

2

B1

PTE1

ND

Hi-Z

—

SS

N

N

N

3

—

VDD

—

—

—

—

—

—

—

4

C4

VSS

—

—

—

—

—

—

—

5

E1

USB0_DP

—

—

—

—

—

—

—

6

D1

USB0_DM

—

—

—

—

—

—

—

7

E2

VOUT33

—

—

—

—

—

—

—

8

D2

VREGIN

—

—

—

—

—

—

—

9

G1

PTE20

ND

Hi-Z

—

SS

N

N

N

10

F1

PTE21

ND

Hi-Z

—

SS

N

N

N

11

G2

PTE22

ND

Hi-Z

—

SS

N

N

N

12

F2

PTE23

ND

Hi-Z

—

SS

N

N

N

13

F4

VDDA

—

—

—

—

—

—

—

14

G4

VREFH

—

—

—

—

—

—

—

15

G3

VREFL

—

—

—

—

—

—

—

16

F3

VSSA

—

—

—

—

—

—

—

17

H1

PTE29

ND

Hi-Z

—

SS

N

N

N

18

H2

PTE30

ND

Hi-Z

—

SS

N

N

N

19

H3

PTE31

ND

Hi-Z

—

SS

N

N

N

20

H4

PTE24

ND

Hi-Z

—

SS

N

N

N

21

H5

PTE25

ND

Hi-Z

—

SS

N

N

N

22

D3

PTA0

ND

L

PD

SS

N

N

Y

23

D4

PTA1

ND

Hi-Z

—

SS

N

N

Y

24

E5

PTA2

ND

Hi-Z

—

SS

N

N

Y

Table continues on the next page...

32

NXP Semiconductors

K32 L2B Microcontroller, Rev. 3, 09/2020