Freescale Semiconductor

Document Number: MPC8280EC

Rev. 2, 09/2011

Technical Data

MPC8280

PowerQUICC II Family

Hardware Specifications

This document contains detailed information about power

considerations, DC/AC electrical characteristics, and AC

timing specifications for .13µm (HiP7) members of the

PowerQUICC II family of integrated communications

processors—the MPC8280, the MPC8275, and the

MPC8270 (collectively called the MPC8280 throughout this

document).

© 2011 Freescale Semiconductor, Inc. All rights reserved.

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

Contents

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . 7

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . 9

Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . 12

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

AC Electrical Characteristics . . . . . . . . . . . . . . . . . . 16

Clock Configuration Modes . . . . . . . . . . . . . . . . . . . 26

Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

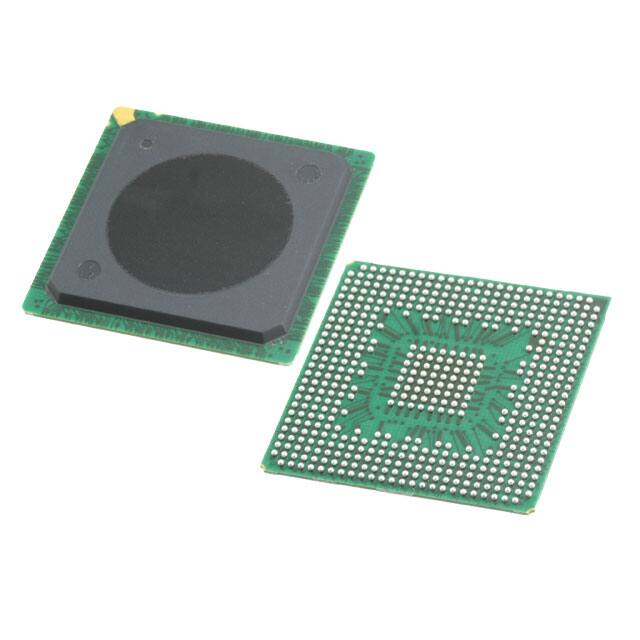

Package Description . . . . . . . . . . . . . . . . . . . . . . . . . 75

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 79

Document Revision History . . . . . . . . . . . . . . . . . . . 79

�Overview

1

Overview

This table shows the functionality supported by each SoC in the MPC8280 family.

Table 1. MPC8280 PowerQUICC II Family Functionality

SoCs

Functionality

MPC8270

Package1 480 TBGA

MPC8275

MPC8280

516 PBGA

516 PBGA

480 TBGA

Serial communications controllers (SCCs)

4

4

4

4

QUICC multi-channel controller (QMC)

—

—

—

—

Fast communication controllers (FCCs)

3

3

3

3

I-Cache (Kbyte)

16

16

16

16

D-Cache (Kbyte)

16

16

16

16

Ethernet (10/100)

3

3

3

3

UTOPIA II Ports

0

0

2

2

Multi-channel controllers (MCCs)

1

1

1

2

PCI bridge

Yes

Yes

Yes

Yes

Transmission convergence (TC) layer

—

—

—

Yes

Inverse multiplexing for ATM (IMA)

—

—

—

Yes

Universal serial bus (USB) 2.0 full/low rate

1

1

1

1

Security engine (SEC)

—

—

—

—

1

See Table 2.

Devices in the MPC8280 family are available in four packages—the standard ZU and VV packages and

the alternate VR or ZQ packages—as shown in Table 2. Note that throughout this document, references to

the MPC8280 and the MPC8270 are inclusive of VR and ZQ package devices unless otherwise specified.

For more information on VR and ZQ packages, contact your Freescale sales office. For package ordering

information, see Section 10, “Ordering Information.”

Table 2. HiP7 PowerQUICC II Device Packages

Code

(Package)

ZU

(480 TBGA—Leaded)

VV

VR

(480 TBGA—Lead Free) (516 PBGA—Lead free)

ZQ

(516 PBGA—Lead spheres)

MPC8280

MPC8280

MPC8275VR

MPC8275ZQ

MPC8270

MPC8270

MPC8270VR

MPC8270ZQ

Device

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

2

Freescale Semiconductor

�Overview

This figure shows the block diagram of the SoC. Shaded portions are SoC-specific; see the notes below

the figure.

16 KB

I-Cache

I-MMU

System Interface Unit

(SIU)

G2_LE Core

16 KB

D-Cache

Bus Interface Unit

Communication Processor Module (CPM)

Timers

Interrupt

Controller

Parallel I/O

MCC2

Serial

DMAs

FCC2

FCC3

TC Layer Hardware1

SCC1

SCC2

Local Bus

32 bits, up to 100 MHz

Clock Counter

4 Virtual

IDMAs

IMA 1

Microcode

FCC1

or

Memory Controller

32 KB

Data

RAM

32-bit RISC Microcontroller

and Program ROM

Baud Rate

Generators

MCC11

32 KB

Instruction

RAM

PCI Bus

32 bits, up to 66 MHz

60x-to-PCI

Bridge

60x-to-Local

Bridge

D-MMU

60x Bus

SCC3

SCC4/

USB

System Functions

SMC1

SMC2

SPI

I2C

Time Slot Assigner

Serial Interface2

8 TDM Ports2

3 MII or RMII

Ports

2 UTOPIA

Ports3

Non-Multiplexed

I/O

Notes:

1 MPC8280 only (not on MPC8270, the VR package, nor the ZQ package)

2 MPC8280 has 2 serial interface (SI) blocks and 8 TDM ports. MPC8270 and the VR and ZQ packages have

only 1 SI block and 4 TDM ports (TDM2[A–D]).

3 MPC8280, MPC8275VR, MPC8275ZQ only (not on MPC8270, MPC8270VR, nor MPC8270ZQ)

Figure 1. SoC Block Diagram

1.1

Features

The major features of the SoC are as follows:

• Dual-issue integer (G2_LE) core

— A core version of the EC603e microprocessor

— System core microprocessor supporting frequencies of 166–450 MHz

— Separate 16 KB data and instruction caches:

– Four-way set associative

– Physically addressed

– LRU replacement algorithm

— Power Architecture®-compliant memory management unit (MMU)

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

3

�Overview

•

•

•

•

•

•

— Common on-chip processor (COP) test interface

— High-performance (SPEC95 benchmark at 450 MHz; 855 Dhrystones MIPS at 450 MHz)

— Supports bus snooping

— Support for data cache coherency

— Floating-point unit (FPU)

Separate power supply for internal logic and for I/O

Separate PLLs for G2_LE core and for the communications processor module (CPM)

— G2_LE core and CPM can run at different frequencies for power/performance optimization

— Internal core/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 4.5:1, 5:1, 6:1,

7:1, 8:1

— Internal CPM/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1, 8:1

ratios

64-bit data and 32-bit address 60x bus

— Bus supports multiple master designs

— Supports single- and four-beat burst transfers

— 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

— Supports data parity or ECC and address parity

32-bit data and 18-bit address local bus

— Single-master bus, supports external slaves

— Eight-beat burst transfers

— 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

60x-to-PCI bridge

— Programmable host bridge and agent

— 32-bit data bus, 66.67/83.3/100 MHz, 3.3 V

— Synchronous and asynchronous 60x and PCI clock modes

— All internal address space available to external PCI host

— DMA for memory block transfers

— PCI-to-60x address remapping

PCI bridge

— PCI Specification Revision 2.2 compliant and supports frequencies up to 66 MHz

— On-chip arbitration

— Support for PCI-to-60x-memory and 60x-memory-to-PCI streaming

— PCI host bridge or peripheral capabilities

— Includes 4 DMA channels for the following transfers:

– PCI-to-60x to 60x-to-PCI

– 60x-to-PCI to PCI-to-60x

– 60x-to-PCI to 60x-to-PCI

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

4

Freescale Semiconductor

�Overview

•

•

•

•

— Includes all of the configuration registers (which are automatically loaded from the EPROM

and used to configure the MPC8280) required by the PCI standard as well as message and

doorbell registers

— Supports the I2O standard

— Hot-swap friendly (supports the hot swap specification as defined by PICMG 2.1 R1.0 August

3, 1998)

— Support for 66.67/83.33/100 MHz, 3.3 V specification

— 60x-PCI bus core logic that uses a buffer pool to allocate buffers for each port

— Uses the local bus signals, removing need for additional pins

System interface unit (SIU)

— Clock synthesizer

— Reset controller

— Real-time clock (RTC) register

— Periodic interrupt timer

— Hardware bus monitor and software watchdog timer

— IEEE 1149.1 JTAG test access port

12-bank memory controller

— Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash, and other

user-definable peripherals

— Byte write enables and selectable parity generation

— 32-bit address decodes with programmable bank size

— Three user-programmable machines, general-purpose chip-select machine, and page mode

pipeline SDRAM machine

— Byte selects for 64-bit bus width (60x) and byte selects for 32-bus width (local)

— Dedicated interface logic for SDRAM

CPU core can be disabled and the device can be used in slave mode to an external core

Communications processor module (CPM)

— Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support

for communications protocols

— Interfaces to G2_LE core through an on-chip 32 KB dual-port data RAM, an on-chip 32 KB

dual-port instruction RAM and DMA controller

— Serial DMA channels for receive and transmit on all serial channels

— Parallel I/O registers with open-drain and interrupt capability

— Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

— Three fast communications controllers supporting the following protocols:

– 10/100-Mbit Ethernet/IEEE 802.3 CDMA/CS interface through media independent

interface (MII) or reduced media independent interface (RMII)

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

5

�Overview

•

– ATM—Full-duplex SAR protocols at 155 Mbps, through UTOPIA interface, AAL5, AAL1,

AAL0 protocols, TM 4.0 CBR, VBR, UBR, ABR traffic types, up to 64 K external

connections (no ATM support for the MPC8270)

– Transparent

– HDLC—Up to T3 rates (clear channel)

– FCC2 can also be connected to the TC layer (MPC8280 only)

— Two multichannel controllers (MCCs) (one MCC on the MPC8270)

– Each MCC handles 128 serial, full-duplex, 64-Kbps data channels. Each MCC can be split

into four subgroups of 32 channels each.

– Almost any combination of subgroups can be multiplexed to single or multiple TDM

interfaces up to four TDM interfaces per MCC

— Four serial communications controllers (SCCs) identical to those on the MPC860, supporting

the digital portions of the following protocols:

– Ethernet/IEEE 802.3 CDMA/CS

– HDLC/SDLC and HDLC bus

– Universal asynchronous receiver transmitter (UART)

– Synchronous UART

– Binary synchronous (BISYNC) communications

– Transparent

Universal serial bus (USB) controller

— Supports USB 2.0 full/low rate compatible

— USB host mode

– Supports control, bulk, interrupt, and isochronous data transfers

– CRC16 generation and checking

– NRZI encoding/decoding with bit stuffing

– Supports both 12- and 1.5-Mbps data rates (automatic generation of preamble token and

data rate configuration). Note that low-speed operation requires an external hub.

– Flexible data buffers with multiple buffers per frame

– Supports local loopback mode for diagnostics (12 Mbps only)

— Supports USB slave mode

– Four independent endpoints support control, bulk, interrupt, and isochronous data transfers

– CRC16 generation and checking

– CRC5 checking

– NRZI encoding/decoding with bit stuffing

– 12- or 1.5-Mbps data rate

– Flexible data buffers with multiple buffers per frame

– Automatic retransmission upon transmit error

— Two serial management controllers (SMCs), identical to those of the MPC860

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

6

Freescale Semiconductor

�Operating Conditions

•

•

2

– Provides management for BRI devices as general-circuit interface (GCI) controllers in

time-division-multiplexed (TDM) channels

– Transparent

– UART (low-speed operation)

— One serial peripheral interface identical to the MPC860 SPI

— One I2C controller (identical to the MPC860 I2C controller)

– Microwire compatible

– Multiple-master, single-master, and slave modes

— Up to eight TDM interfaces (four on the MPC8270)

– Supports two groups of four TDM channels for a total of eight TDMs (one group of four on

the MPC8270 and the MPC8275)

– 2,048 bytes of SI RAM

– Bit or byte resolution

– Independent transmit and receive routing, frame synchronization

– Supports T1, CEPT, T1/E1, T3/E3, pulse code modulation highway, ISDN basic rate, ISDN

primary rate, Freescale interchip digital link (IDL), general circuit interface (GCI), and

user-defined TDM serial interfaces

— Eight independent baud rate generators and 20 input clock pins for supplying clocks to FCCs,

SCCs, SMCs, and serial channels

— Four independent 16-bit timers that can be interconnected as two 32-bit timers

Inverse multiplexing for ATM capabilities (IMA) (MPC8280 only). Supported by eight transfer

transmission convergence (TC) layers between the TDMs and FCC2.

Transmission convergence (TC) layer (MPC8280 only)

Operating Conditions

This table shows the maximum electrical ratings.

Table 3. Absolute Maximum Ratings1

Rating

Symbol

Value

Unit

Core supply voltage2

VDD

–0.3 – 2.25

V

PLL supply voltage2

VCCSYN

–0.3 – 2.25

V

VDDH

–0.3 – 4.0

V

VIN

GND(–0.3) – 3.6

V

Tj

120

°C

TSTG

(–55) – (+150)

°C

I/O supply

voltage3

Input voltage4

Junction temperature

Storage temperature range

1

Absolute maximum ratings are stress ratings only; functional operation (see Table 4) at the maximums is not

guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

7

�Operating Conditions

2

Caution: VDD/VCCSYN must not exceed VDDH by more than 0.4 V during normal operation. It is recommended that

VDD/VCCSYN should be raised before or simultaneous with VDDH during power-on reset. VDD/VCCSYN may

exceed VDDH by more than 0.4 V during power-on reset for no more than 100 ms.

3

Caution: VDDH can exceed VDD/VCCSYN by 3.3 V during power on reset by no more than 100 mSec. VDDH should

not exceed VDD/VCCSYN by more than 2.5 V during normal operation.

4 Caution: VIN must not exceed VDDH by more than 2.5 V at any time, including during power-on reset.

This table lists recommended operational voltage conditions.

Table 4. Recommended Operating Conditions1

Rating

Symbol

Value

Unit

Core supply voltage

VDD

1.45 – 1.60

V

PLL supply voltage

VCCSYN

1.45 – 1.60

V

I/O supply voltage

VDDH

3.135 – 3.465

V

VIN

GND (–0.3) – 3.465

V

Tj

1052

°C

TA

0–702

°C

Input voltage

Junction temperature (maximum)

Ambient temperature

1

Caution: These are the recommended and tested operating conditions. Proper operation outside of these conditions

is not guaranteed.

2 Note that for extended temperature parts the range is (-40) – 105 .

T

Tj

A

This SoC contains circuitry protecting against damage due to high static voltage or electrical fields;

however, it is advised that normal precautions be taken to avoid application of any voltages higher than

maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused

inputs are tied to an appropriate logic voltage level (either GND or VCC).

This figure shows the undershoot and overshoot voltage of the 60x and local bus memory interface of the

SoC. Note that in PCI mode the I/O interface is different.

VIH

VIL

4V

GVDD + 5%

GVDD

GND

GND – 0.3 V

GND – 1.0 V

Not to exceed 10%

of tSDRAM_CLK

Figure 2. Overshoot/Undershoot Voltage

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

8

Freescale Semiconductor

�DC Electrical Characteristics

3

DC Electrical Characteristics

This table shows DC electrical characteristics.

Table 5. DC Electrical Characteristics1

Characteristic

Input high voltage—all inputs except TCK, TRST and PORESET

Input low voltage

2

Symbol

Min

Max

Unit

VIH

2.0

3.465

V

VIL

GND

0.8

V

CLKIN input high voltage

VIHC

2.4

3.465

V

CLKIN input low voltage

VILC

GND

0.4

V

IIN

—

10

µA

Input leakage current, VIN = VDDH3

Hi-Z (off state) leakage current, VIN = VDDH

3

IOZ

—

10

µA

4

Signal low input current, V IL = 0.8 V

IL

—

1

µA

Signal high input current, VIH = 2.0 V

IH

—

1

µA

VOH

2.4

—

V

VOL

—

0.5

V

Output high voltage, IOH = –2 mA

except UTOPIA mode, and open drain pins

In UTOPIA mode5 (UTOPIA pins only): IOH = -8.0mA

PA[0-31]

PB[4-31]

PC[0-31]

PD[4-31]

In UTOPIA mode5 (UTOPIA pins only): IOL = 8.0mA

PA[0-31]

PB[4-31]

PC[0-31]

PD[4-31]

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

9

�DC Electrical Characteristics

Table 5. DC Electrical Characteristics1 (continued)

Characteristic

IOL = 6.0mA

BR

BG

ABB/IRQ2

TS

A[0-31]

TT[0-4]

TBST

TSIZE[0–3]

AACK

ARTRY

DBG

DBB/IRQ3

D[0-63]

DP(0)/RSRV/EXT_BR2

DP(1)/IRQ1/EXT_BG2

DP(2)/TLBISYNC/IRQ2/EXT_DBG2

DP(3)/IRQ3/EXT_BR3/CKSTP_OUT

DP(4)/IRQ4/EXT_BG3/CORE_SREST

DP(5)/TBEN/EXT_DBG3/IRQ5/CINT

DP(6)/CSE(0)/IRQ6

DP(7)/CSE(1)/IRQ7

PSDVAL

TA

TEA

GBL/IRQ1

CI/BADDR29/IRQ2

WT/BADDR30/IRQ3

L2_HIT/IRQ4

CPU_BG/BADDR31/IRQ5/CINT

CPU_DBG

CPU_BR

IRQ0/NMI_OUT

IRQ7/PCI_RSTINT_OUT/APE

PORESET

HRESET

SRESET

RSTCONF

Symbol

Min

Max

Unit

VOL

—

0.4

V

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

10

Freescale Semiconductor

�DC Electrical Characteristics

Table 5. DC Electrical Characteristics1 (continued)

Characteristic

IOL = 5.3mA

CS[0-9]

CS(10)/BCTL1

CS(11)/AP(0)

BADDR[27–28]

ALE

BCTL0

PWE[0–7]/PSDDQM[0–7]/PBS[0–7]

PSDA10/PGPL0

PSDWE/PGPL1

POE/PSDRAS/PGPL2

PSDCAS/PGPL3

PGTA/PUPMWAIT/PGPL4/PPBS

PSDAMUX/PGPL5

LWE[0–3]LSDDQM[0–3]/LBS[0–3]/PCI_CFG[0–3]

LSDA10/LGPL0/PCI_MODCKH0

LSDWE/LGPL1/PCI_MODCKH1

LOE/LSDRAS/LGPL2/PCI_MODCKH2

LSDCAS/LGPL3/PCI_MODCKH3

LGTA/LUPMWAIT/LGPL4/LPBS

LSDAMUX/LGPL5/PCI_MODCK

LWR

MODCK[1–3]/AP[1–3]/TC[0–2]/BNKSEL[0–2]

IOL = 3.2mA

L_A14/PAR

L_A15/FRAME/SMI

L_A16/TRDY

L_A17/IRDY/CKSTP_OUT

L_A18/STOP

L_A19/DEVSEL

L_A20/IDSEL

L_A21/PERR

L_A22/SERR

L_A23/REQ0

L_A24/REQ1/HSEJSW

L_A25/GNT0

L_A26/GNT1/HSLED

L_A27/GNT2/HSENUM

L_A28/RST/CORE_SRESET

L_A29/INTAL_A30/REQ2

L_A31

LCL_D[0-31)]/AD[0-31]

LCL_DP[03]/C/BE[0-3]

PA[0–31]

PB[4–31]

PC[0–31]

PD[4–31]

TDO

QREQ

Symbol

Min

Max

Unit

VOL

—

0.4

V

1

The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC

current, either pull unused pins to GND or VDDH or configure them as outputs.

2 TCK, TRST and PORESET have min VIH = 2.5V.

3 The leakage current is measured for nominal VDDH,VCCSYN, and VDD.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

11

�Thermal Characteristics

4

VIL for IIC interface does not match IIC standard, but does meet IIC standard for VOL and should not cause any compatibility

issue.

5

MPC8280, MPC8275VR, MPC8275ZQ only.

4

Thermal Characteristics

This table describes thermal characteristics for both the packages. See Table 2 for information on a given

SoC’s package. Discussions of each characteristic are provided in Section 4.1, “Estimation with

Junction-to-Ambient Thermal Resistance,” and Section 4.5, “Experimental Determination.” For the these

discussions, PD = (VDD × IDD) + PI/O, where PI/O is the power dissipation of the I/O drivers.

Table 6. Thermal Characteristics

Value

Characteristic

Symbol

Junction to ambient—

single-layer board1

RθJA

Junction to ambient—

four-layer board

RθJA

Junction to board2

Unit

480 TBGA

516 PBGA

16

27

11

21

12

19

Air Flow

Natural convection

°C/W

1 m/s

Natural convection

°C/W

9

16

1 m/s

RθJB

6

11

°C/W

—

Junction to case3

RθJC

2

8

°C/W

—

Junction-to-package top4

ΨJT

2

2

°C/W

—

1

Assumes no thermal vias

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on

the top surface of the board near the package.

3 Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method

1012.1).

4

Thermal characterization parameter indicating the temperature difference between package top and the junction temperature

per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

2

4.1

Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, TJ, in

TJ = TA + (RθJA × PD)

C can be obtained from the following equation:

where:

TA = ambient temperature (ºC)

RθJA = package junction-to-ambient thermal resistance (ºC/W)

PD = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy

estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated

that errors of a factor of two (in the quantity TJ – TA) are possible.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

12

Freescale Semiconductor

�Thermal Characteristics

4.2

Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal

resistance and a case-to-ambient thermal resistance:

RθJA = RθJC + RθCA

where:

RθJA = junction-to-ambient thermal resistance (ºC/W)

RθJC = junction-to-case thermal resistance (ºC/W)

RθCA = case-to-ambient thermal resistance (ºC/W)

RθJC is device related and cannot be influenced by the user. The user adjusts the thermal environment to

affect the case-to-ambient thermal resistance, RθCA. For instance, the user can change the air flow around

the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the

thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful

for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink

to the ambient environment. For most packages, a better model is required.

4.3

Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a

two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The

junction-to-case thermal resistance covers the situation where a heat sink is used or where a substantial

amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance

describes the thermal performance when most of the heat is conducted to the printed circuit board. It has

been observed that the thermal performance of most plastic packages, especially PBGA packages, is

strongly dependent on the board temperature.

If the board temperature is known, an estimate of the junction temperature in the environment can be made

using the following equation:

TJ = TB + (RθJB × PD)

where:

RθJB = junction-to-board thermal resistance (ºC/W)

TB = board temperature (ºC)

PD = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored,

acceptable predictions of junction temperature can be made. For this method to work, the board and board

mounting must be similar to the test board used to determine the junction-to-board thermal resistance,

namely a 2s2p (board with a power and a ground plane) and by attaching the thermal balls to the ground

plane.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

13

�Thermal Characteristics

4.4

Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple

two-resistor model can be used with the thermal simulation of the application, or a more accurate and

complex model of the package can be used in the thermal simulation.

4.5

Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the

thermal characterization parameter (ΨJT) can be used to determine the junction temperature with a

measurement of the temperature at the top center of the package case using the following equation:

TJ = TT + (ΨJT × PD)

where:

ΨJT = thermal characterization parameter

TT = thermocouple temperature on top of package

PD = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40-gauge

type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned

so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the

thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is

placed flat against the case to avoid measurement errors caused by cooling effects of the thermocouple

wire.

4.6

Layout Practices

Each VDD and VDDH pin should be provided with a low-impedance path to the board’s power supplies.

Each ground pin should likewise be provided with a low-impedance path to ground. The power supply pins

drive distinct groups of logic on chip. The VDD and VDDH power supplies should be bypassed to ground

using bypass capacitors located as close as possible to the four sides of the package. For filtering high

frequency noise, a capacitor of 0.1uF on each VDD and VDDH pin is recommended. Further, for medium

frequency noise, a total of 2 capacitors of 47uF for VDD and 2 capacitors of 47uF for VDDH are also

recommended. The capacitor leads and associated printed circuit traces connecting to chip VDD, VDDH

and ground should be kept to less than half an inch per capacitor lead. Boards should employ separate inner

layers for power and GND planes.

All output pins on the SoC have fast rise and fall times. Printed circuit (PC) trace interconnection length

should be minimized to minimize overdamped conditions and reflections caused by these fast output

switching times. This recommendation particularly applies to the address and data buses. Maximum PC

trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as

well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes

especially critical in systems with higher capacitive loads because these loads create higher transient

currents in the VDD and GND circuits. Pull up all unused inputs or signals that will be inputs during reset.

Special care should be taken to minimize the noise levels on the PLL supply pins.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

14

Freescale Semiconductor

�Power Dissipation

5

Power Dissipation

This table provides preliminary, estimated power dissipation for various configurations. Note that suitable

thermal management is required to ensure the junction temperature does not exceed the maximum

specified value. Also note that the I/O power should be included when determining whether to use a heat

sink. For a complete list of possible clock configurations, see Section 7, “Clock Configuration Modes.”

Table 7. Estimated Power Dissipation for Various Configurations1

Bus

(MHz)

CPM

Multiplication

Factor

CPM

(MHz)

CPU

Multiplication

Factor

PINT(W)2,3

CPU

(MHz)

Vddl 1.5 Volts

Nominal

Maximum

66.67

2.5

166

3.5

233

0.95

1.0

66.67

2.5

166

4

266

1.0

1.05

66.67

3

200

4

266

1.05

1.1

66.67

3.5

233

4.5

300

1.05

1.15

83.33

3

250

4

333

1.25

1.35

83.33

3

250

4.5

375

1.3

1.4

83.33

3.5

292

5

417

1.45

1.55

100

3

300

4

400

1.5

1.6

100

3

300

4.5

450

1.55

1.65

1

Test temperature = 105° C

PINT = IDD x VDD Watts

3 Values do not include I/O. Add the following estimates for active I/O based on the following bus speeds:

66.7 MHz = 0.45 W (nominal), 0.5 W (maximum)

83.3 MHz = 0.5W (nominal), 0.6 W (maximum)

100 MHz = 0.6 W (nominal), 0.7 W (maximum)

2

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

15

�AC Electrical Characteristics

6

AC Electrical Characteristics

The following sections include illustrations and tables of clock diagrams, signals, and CPM outputs and

inputs for 66.67/83.33/100 MHz devices. Note that AC timings are based on a 50-pf load for MAX Delay

and 10-pf load for MIN delay. Typical output buffer impedances are shown in this table.

Table 8. Output Buffer Impedances1

Output Buffers

Typical Impedance (Ω)

45 or 272

60x bus

Local bus

45

45 or 272

Memory controller

Parallel I/O

45

PCI

27

1

These are typical values at 65° C. Impedance may vary by ±25% with process and

temperature.

2 On silicon revision 0.0 (mask #: 0K49M), selectable impedance is not available.

Impedance is set at 45 Ω.

On all other revisions, impedance value is selected through the SIUMCR[20,21]. See

the SoC reference manual.

6.1

CPM AC Characteristics

This table lists CPM output characteristics.

Table 9. AC Characteristics for CPM Outputs1

Spec Number

Max

Characteristic

Value (ns)

Min

Maximum Delay

Minimum Delay

66 MHz

83 MHz

100 MHz

66 MHz

83 MHz

100 MHz

sp36a

sp37a FCC outputs—internal clock (NMSI)

6

5.5

5.5

0.5

0.5

0.5

sp36b

sp37b FCC outputs—external clock (NMSI)

8

8

8

2

2

2

sp38a

sp39a SCC/SMC/SPI/I2C outputs—internal

clock (NMSI)

10

10

10

0

0

0

sp38b

sp39b SCC/SMC/SPI/I2C outputs—external

clock (NMSI)

8

8

8

2

2

2

sp40

sp41

TDM outputs/SI

11

11

11

2.5

2.5

2.5

sp42

sp43

TIMER/IDMA outputs

11

11

11

0.5

0.5

0.5

sp42a

sp43a PIO outputs

11

11

11

0.5

0.5

0.5

1

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are

measured at the pin.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

16

Freescale Semiconductor

�AC Electrical Characteristics

This table lists CPM input characteristics.

NOTE: Rise/Fall Time on CPM Input Pins

It is recommended that the rise/fall time on CPM input pins should not

exceed 5 ns. This should be enforced especially on clock signals. Rise time

refers to signal transitions from 10% to 90% of VCC; fall time refers to

transitions from 90% to 10% of VCC.

Table 10. AC Characteristics for CPM Inputs1

Spec Number

Setup

1

Value (ns)

Hold

Characteristic

Setup

Hold

66 MHz

83 MHz

100 MHz

66 MHz

83 MHz

100 MHz

sp16a

sp17a FCC inputs—internal clock (NMSI)

6

6

6

0

0

0

sp16b

sp17b FCC inputs—external clock (NMSI)

2.5

2.5

2.5

2

2

2

sp18a

sp19a SCC/SMC/SPI/I2C inputs—internal clock

(NMSI)

6

6

6

0

0

0

sp18b

sp19b SCC/SMC/SPI/I2C inputs—external clock

(NMSI)

4

4

4

2

2

2

sp20

sp21

TDM inputs/SI

5

5

5

2.5

2.5

2.5

sp22

sp23

PIO/TIMER/IDMA inputs

8

8

8

0.5

0.5

0.5

Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are

measured at the pin.

NOTE

Although the specifications generally reference the rising edge of the clock,

the following AC timing diagrams also apply when the falling edge is the

active edge.

This figure shows the FCC internal clock.

BRG_OUT

sp17a

sp16a

FCC input signals

sp36a/sp37a

FCC output signals

Note: When GFMR[TCI] = 0

sp36a/sp37a

FCC output signals

Note: When GFMR.[TCI] = 1

Figure 3. FCC Internal Clock Diagram

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

17

�AC Electrical Characteristics

This figure shows the FCC external clock.

Serial ClKin

sp17b

sp16b

FCC input signals

sp36b/sp37b

FCC output signals

Note: When GFMR[TCI] = 0

sp36b/sp37b

FCC output signals

Note: When GFMR[TCI] = 1

Figure 4. FCC External Clock Diagram

This figure shows the SCC/SMC/SPI/I2C external clock.

Serial CLKin

sp18b

sp19b

SCC/SMC/SPI/I2C input signals

(See note)

sp38b/sp39b

SCC/SMC/SPI/I2C output signals

(See note)

Note: There are four possible timing conditions for SCC and SPI:

1. Input sampled on the rising edge and output driven on the rising edge (shown).

2. Input sampled on the rising edge and output driven on the falling edge.

3. Input sampled on the falling edge and output driven on the falling edge.

4. Input sampled on the falling edge and output driven on the rising edge.

Figure 5. SCC/SMC/SPI/I2C External Clock Diagram

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

18

Freescale Semiconductor

�AC Electrical Characteristics

This figure shows the SCC/SMC/SPI/I2C internal clock.

BRG_OUT

sp19a

sp18a

SCC/SMC/SPI/I2C input signals

(See note)

sp38a/sp39a

SCC/SMC/SPI/I2C output signals

(See note)

Note: There are four possible timing conditions for SCC and SPI:

1. Input sampled on the rising edge and output driven on the rising edge (shown).

2. Input sampled on the rising edge and output driven on the falling edge.

3. Input sampled on the falling edge and output driven on the falling edge.

4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I2C Internal Clock Diagram

This figure shows TDM input and output signals.

Serial CLKin

sp20

sp21

TDM input signals

sp40/sp41

TDM output signals

Note: There are four possible TDM timing conditions:

1. Input sampled on the rising edge and output driven on the rising edge (shown).

2. Input sampled on the rising edge and output driven on the falling edge.

3. Input sampled on the falling edge and output driven on the falling edge.

4. Input sampled on the falling edge and output driven on the rising edge.

Figure 7. TDM Signal Diagram

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

19

�AC Electrical Characteristics

This figure shows PIO and timer signals.

Sys clk

sp23

sp22

PIO/IDMA/TIMER[TGATE assertion] input signals

(See note)

sp23

sp22

TIMER input signal [TGATE deassertion]

(See note)

sp42/sp43

IDMA output signals

sp42/sp43

sp42a/sp43a

TIMER(sp42/43)/ PIO(sp42a/sp43a)

output signals

Note: TGATE is asserted on the rising edge of the clock; it is deasserted on the falling edge.

Figure 8. PIO and Timer Signal Diagram

6.2

SIU AC Characteristics

This table lists SIU input characteristics.

NOTE: CLKIN Jitter and Duty Cycle

The CLKIN input to the SoC should not exceed +/– 150 psec of jitter

(peak-to-peak). This represents total input jitter—the combination of short

term (cycle-to-cycle) and long term (cumulative). The duty cycle of CLKIN

should not exceed the ratio of 40:60. The rise/file time of CLKIN should

adhere to the typical SDRAM device AC clock requirement of 1 V/ns to

meet SDRAM AC specs.

NOTE: Spread Spectrum Clocking

Spread spectrum clocking is allowed with 1% input frequency down-spread

at maximum 60 KHz modulation rate regardless of input frequency.

NOTE: PCI AC Timing

The SoC meets the timing requirements of PCI Specification Revision 2.2.

See Section 7, “Clock Configuration Modes,” and “Note: Tval (Output

Hold)” to determine if a specific clock configuration is compliant.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

20

Freescale Semiconductor

�AC Electrical Characteristics

NOTE: Conditions

The following conditions must be met in order to operate the MPC8272

family devices with 133 MHz bus: single PowerQUICC II Bus mode must

be used (no external master, BCR[EBM] = 0); data bus must be in Pipeline

mode (BRx[DR] = 1); internal arbiter and memory controller must be used.

For expected load of above 40 pF, it is recommended that data and address

buses be configured to low (25 Ω) impedance (SIUMCR[HLBE0] = 1,

SIUMCR[HLBE1] = 1).

Table 11. AC Characteristics for SIU Inputs1

Spec Number

Value (ns)

Setup

Characteristic

Setup

1

Hold

Hold

66

MHz

83

MHz

100

MHz

133

MHz

66

MHz

83

MHz

100

MHz

133

MHz

sp11

sp10 AACK/TA/TS/DBG/BG/BR/ARTRY/TEA

6

5

3.5

N/A

0.5

0.5

0.5

N/A

sp12

sp10 Data bus in normal mode

5

4

3.5

N/A

0.5

0.5

0.5

N/A

sp13

sp10 Data bus in pipeline mode (without ECC and

PARITY)

N/A

4

2.5

1.5

N/A

0.5

0.5

0.5

sp15

sp10 All other pins

5

4

3.5

N/A

0.5

0.5

0.5

N/A

Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are

measured at the pin.

This table lists SIU output characteristics.

Table 12. AC Characteristics for SIU Outputs1

Spec Number

Value (ns)

Maximum Delay

Characteristic

Max

Min

sp31

sp30

sp32

Minimum Delay

66

MHz

83

MHz

100

MHz

133

MHz

66

MHz

83

MHz

100

MHz

133

MHz

PSDVAL/TEA/TA

7

6

5.5

N/A

1

1

1

N/A

sp30

ADD/ADD_atr./BADDR/CI/GBL/WT

8

6.5

5.5

4.52

1

1

1

12

sp33

sp30

Data bus3

6.5

6.5

5.5

4.5

0.8

0.8

0.8

1

sp34

sp30

Memory controller signals/ALE

6

5.5

5.5

4.5

1

1

1

1

sp35

sp30

All other signals

6

5.5

5.5

N/A

1

1

1

N/A

1

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are

measured at the pin.

2

Value is for ADD only; other sp32/sp30 signals are not applicable.

3 To achieve 1 ns of hold time at 66.67/83.33/100 MHZ, a minimum loading of 20 pF is required.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

21

�AC Electrical Characteristics

NOTE

Activating data pipelining (setting BRx[DR] in the memory controller)

improves the AC timing.

This table lists SIU input characteristics.

Table 13. AC Characteristics for SIU Inputs1

Spec Number

Setup

Value (ns)

Hold

Characteristic

Setup

Hold

66 MHz

83 MHz

100 MHz

66 MHz

83 MHz

100 MHz

sp11

sp10

AACK/TA/TS/DBG/BG/BR/ARTRY/

TEA

6

5

3.5

0.5

0.5

0.5

sp12

sp10

Data bus in normal mode

5

4

3.5

0.5

0.5

0.5

sp13

sp10

Data bus in ECC and PARITY modes

7

5

3.5

0.5

0.5

0.5

sp13a

sp10

Pipeline mode—Data bus (with or without

ECC/PARITY)

5

4

2.5

0.5

0.5

0.5

sp14

sp10

DP pins

7

5

3.5

0.5

0.5

0.5

sp14a

sp10

Pipeline mode—DP pins

—

4

2.5

—

0.5

0.5

sp15

sp10

All other pins

5

4

3.5

0.5

0.5

0.5

1

Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are

measured at the pin.

This table lists SIU output characteristics.

Table 14. AC Characteristics for SIU Outputs1

Spec Number

Max

Value (ns)

Min

Characteristic

Maximum Delay

Minimum Delay

66 MHz

83 MHz

100 MHz

66 MHz

83 MHz

100 MHz

sp31

sp30

PSDVAL/TEA/TA

7

6

5.5

1

1

1

sp32

sp30

ADD/ADD_atr./BADDR/CI/GBL/WT

8

6.5

5.5

1

1

1

6.5

6.5

5.5

0.7

0.7

0.7

bus2

sp33a

sp30

Data

sp33b

sp30

DP

6

5.5

5.5

1

1

1

sp34

sp30

Memory controller signals/ALE

6

5.5

5.5

1

1

1

sp35

sp30

All other signals

6

5.5

5.5

1

1

1

sp35a

sp30

AP

7

7

7

1

1

1

1

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are

measured at the pin.

2

To achieve 1 ns of hold time at 66, 83, or 100 MHz, a minimum loading of 20 pF is required.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

22

Freescale Semiconductor

�AC Electrical Characteristics

This figure shows the interaction of several bus signals.

CLKin

sp11

sp10

sp11a

sp10

AACK/TA/TS/

DBG/BG/BR input signals

ARTRY/TEA input signals

sp12

sp10

sp15

sp10

DATA bus normal mode

input signal

All other input signals

sp31

sp30

sp32

sp30

sp33a

sp30

sp35

sp30

sp35a

sp30

PSDVAL/TEA/TA output signals

ADD/ADD_atr/BADDR/CI/

GBL/WT output signals

DATA bus output signals

All other output signals

(except AP)

AP signals

Figure 9. Bus Signals

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

23

�AC Electrical Characteristics

This figure shows signal behavior for all parity modes (including ECC, RMW parity, and standard parity).

CLKin

sp10

sp13

DATA bus, ECC, and PARITY mode

input signals

sp10

sp13a

Pipeline mode—

DATA bus, ECC, and PARITY mode

input signals

sp10

sp14

DP mode input signal

sp10

sp14a

Pipeline mode—

DP mode input signal

sp33b

sp30

DP mode output signal

Figure 10. Parity Mode Diagram

This figure shows signal behavior in MEMC mode.

CLKin

V_CLK

sp34/sp30

Memory controller signals

Figure 11. MEMC Mode Diagram

NOTE

Generally, all SoC bus and system output signals are driven from the rising

edge of the input clock (CLKin). Memory controller signals, however,

trigger on four points within a CLKin cycle. Each cycle is divided by four

internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and

T3 at the falling edge, of CLKin. However, the spacing of T2 and T4

depends on the PLL clock ratio selected, as shown in Table 15.

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

24

Freescale Semiconductor

�AC Electrical Characteristics

Table 15. Tick Spacing for Memory Controller Signals

Tick Spacing (T1 Occurs at the Rising Edge of CLKin)

PLL Clock Ratio

T2

T3

T4

1:2, 1:3, 1:4, 1:5, 1:6

1/4 CLKin

1/2 CLKin

3/4 CLKin

1:2.5

3/10 CLKin

1/2 CLKin

8/10 CLKin

1:3.5

4/14 CLKin

1/2 CLKin

11/14 CLKin

This table is a representation of the information in Table 15.

CLKin

for 1:2, 1:3, 1:4, 1:5, 1:6

T1

T2

T3

T4

CLKin

for 1:2.5

T1

T2

T3

T4

for 1:3.5

CLKin

T1

T2

T3

T4

Figure 12. Internal Tick Spacing for Memory Controller Signals

NOTE

The UPM machine outputs change on the internal tick determined by the

memory controller programming; the AC specifications are relative to the

internal tick. Note that SDRAM and GPCM machine outputs change on

CLKin’s rising edge.

6.3

JTAG Timings

This table lists the JTAG timings.

Table 16. JTAG Timings1

Symbol2

Min

Max

Unit

Notes

JTAG external clock frequency of operation

fJTG

0

33.3

MHz

—

JTAG external clock cycle time

tJTG

30

—

ns

—

tJTKHKL

15

—

ns

—

tJTGR and

tJTGF

0

5

ns

6

tTRST

25

—

ns

3 6

tJTDVKH

tJTIVKH

4

4

—

—

ns

ns

Parameter

JTAG external clock pulse width measured at 1.4V

JTAG external clock rise and fall times

TRST assert time

,

Input setup times

Boundary-scan data

TMS, TDI

4, 7

4 7

,

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

25

�Clock Configuration Modes

Table 16. JTAG Timings1 (continued)

Symbol2

Min

Max

Unit

Notes

Boundary-scan data

TMS, TDI

tJTDXKH

tJTIXKH

10

10

—

—

ns

ns

4 7

,

Boundary-scan data

TDO

tJTKLDV

tJTKLOV

—

—

10

10

ns

ns

Boundary-scan data

TDO

tJTKLDX

tJTKLOX

1

1

—

—

ns

ns

JTAG external clock to output high impedance

Boundary-scan data

TDO

tJTKLDZ

tJTKLOZ

1

1

10

10

ns

ns

Parameter

Input hold times

4 7

,

Output valid times

5, 7

5 7

.

Output hold times

1

2

3

4

5

6

7

7

5 7

,

5 7

,

5, 6

5 6

,

All outputs are measured from the midpoint voltage of the falling/rising edge of tTCLK to the midpoint of the signal in question.

The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load. Time-of-flight delays

must be added for trace lengths, vias, and connectors in the system.

The symbols used for timing specifications herein follow the pattern of t(first two letters of functional block)(signal)(state) (reference)(state)

for inputs and t((first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tJTDVKH symbolizes JTAG

device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the tJTG clock reference

(K) going to the high (H) state or setup time. Also, tJTDXKH symbolizes JTAG timing (JT) with respect to the time data input

signals (D) went invalid (X) relative to the tJTG clock reference (K) going to the high (H) state. Note that, in general, the clock

reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall

times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

Non-JTAG signal input timing with respect to tTCLK.

Non-JTAG signal output timing with respect to tTCLK.

Guaranteed by design.

Guaranteed by design and device characterization.

Clock Configuration Modes

This SoC includes the following clocking modes:

• Local

• PCI host

• PCI agent

The clocking mode is set according to the following input pins as shown in the following table:

• PCI_MODE

• PCI_CFG[0]

• PCI_MODCK

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

26

Freescale Semiconductor

�Clock Configuration Modes

Table 17. SoC Clocking Modes

Pins

PCI_CFG[0] PCI_MODCK1

PCI_MODE

1

Clocking Mode

PCI Clock

Frequency Range

(MHZ)

Reference

1

—

—

Local bus

—

Table 18

0

0

0

PCI host

50–66

Table 19

0

0

1

25–50

Table 20

0

1

0

50–66

Table 21

0

1

1

25–50

Table 22

PCI agent

Determines PCI clock frequency range. See Section 7.2, “PCI Host Mode,” and Section 7.3, “PCI Agent Mode.”

Within each mode, the configuration of bus, core, PCI, and CPM frequencies is determined by seven bits

during the power-on reset—three hardware configuration pins (MODCK[1–3]) and four bits from

hardware configuration word[28–31] (MODCK_H). Both the PLLs and the dividers are set according to

the selected clock operation mode as described in the following sections.

7.1

Local Bus Mode

This table lists clock configurations for the SoC in local bus mode. The frequencies listed are for the

purpose of illustration only. Users must select a mode and input bus frequency so that the resulting

configuration does not exceed the frequency rating of the user’s device.

NOTE

Clock configurations change only after PORESET is asserted.

Table 18. Clock Configurations for Local Bus Mode1

Mode2

MODCK_H-MODCK[1:3]

Bus Clock3

(MHz)

Low

High

CPM

Multiplication

Factor4

CPM Clock

(MHz)

Low

High

CPU

Multiplication

Factor5

CPU Clock

(MHz)

Low

High

Default Modes (MODCK_H= 0000)

0000_000

37.5

133.3

3

112.5

400.0

4

150.0

533.3

0000_001

33.3

133.3

3

100.0

400.0

5

166.7

666.7

0000_010

37.5

100.0

4

150.0

400.0

4

150.0

400.0

0000_011

30.0

100.0

4

120.0

400.0

5

150.0

500.0

0000_100

60.0

167.0

2

120.0

334.0

2.5

150.0

417.5

0000_101

50.0

167.0

2

100.0

334.0

3

150.0

501.0

0000_110

60.0

160.0

2.5

150.0

400.0

2.5

150.0

400.0

0000_111

50.0

160.0

2.5

125.0

400.0

3

150.0

480.0

334.0

4

200.0

668.0

Full Configuration Modes

0001_000

50.0

167.0

2

100.0

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

27

�Clock Configuration Modes

Table 18. Clock Configurations for Local Bus Mode1 (continued)

Mode2

Bus Clock3

(MHz)

MODCK_H-MODCK[1:3]

Low

High

0001_001

50.0

167.0

0001_010

50.0

145.8

CPM

Multiplication

Factor4

CPM Clock

(MHz)

Low

High

2

100.0

334.0

2

100.0

291.7

0001_011

Reserved

0001_100

Reserved

CPU

Multiplication

Factor5

CPU Clock

(MHz)

Low

High

5

250.0

835.0

6

300.0

875.0

0001_101

37.5

133.3

3

112.5

400.0

4

150.0

533.3

0001_110

33.3

133.3

3

100.0

400.0

5

166.7

666.7

1000_111

33.3

133.3

3

100.0

400.0

5.5

183.3

733.3

0001_111

33.3

133.3

3

100.0

400.0

6

200.0

800.0

0010_000

Reserved

0010_001

Reserved

0010_010

37.5

100.0

4

150.0

400.0

4

150.0

400.0

0010_011

30.0

100.0

4

120.0

400.0

5

150.0

500.0

0010_100

25.0

100.0

4

100.0

400.0

6

150.0

600.0

0010_101

25.0

100.0

4

100.0

400.0

7

175.0

700.0

0010_110

25.0

100.0

4

100.0

400.0

8

200.0

800.0

0010_111

Reserved

0011_000

30.0

80.0

5

150.0

400.0

5

150.0

400.0

0011_001

25.0

80.0

5

125.0

400.0

6

150.0

480.0

0011_010

25.0

80.0

5

125.0

400.0

7

175.0

560.0

0011_011

25.0

80.0

5

125.0

400.0

8

200.0

640.0

0011_100

Reserved

0011_101

Reserved

0011_110

25.0

66.7

6

150.0

400.0

6

150.0

400.0

0011_111

25.0

66.7

6

150.0

400.0

7

175.0

466.7

0100_000

25.0

66.7

6

150.0

400.0

8

200.0

533.3

0101_101

75.0

167.0

2

150.0

334.0

2

166.7

334.0

0101_110

60.0

167.0

2

120.0

334.0

2.5

166.7

417.5

0101_111

50.0

167.0

2

100.0

334.0

3

200.0

501.0

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

28

Freescale Semiconductor

�Clock Configuration Modes

Table 18. Clock Configurations for Local Bus Mode1 (continued)

Mode2

Bus Clock3

(MHz)

MODCK_H-MODCK[1:3]

Low

High

0110_000

50.0

167.0

0110_001

50.0

0110_010

50.0

CPM

Multiplication

Factor4

CPM Clock

(MHz)

Low

High

2

100.0

334.0

167.0

2

100.0

167.0

2

100.0

0110_011

CPU

Multiplication

Factor5

CPU Clock

(MHz)

Low

High

3.5

250.0

584.5

334.0

4

250.0

668.0

334.0

4.5

250.0

751.5

Reserved

0110_100

60.0

160.0

2.5

150.0

400.0

2.5

150.0

400.0

0110_101

50.0

160.0

2.5

125.0

400.0

3

150.0

480.0

0110_110

42.9

160.0

2.5

107.1

400.0

3.5

150.0

560.0

0110_111

40.0

160.0

2.5

100.0

400.0

4

160.0

640.0

0111_000

40.0

160.0

2.5

100.0

400.0

4.5

180.0

720.0

0111_001

Reserved

0111_010

Reserved

0111_011

50.0

133.3

3

150.0

400.0

3

150.0

400.0

0111_100

42.9

133.3

3

128.6

400.0

3.5

150.0

466.7

0111_101

37.5

133.3

3

112.5

400.0

4

150.0

533.3

0111_110

33.3

133.3

3

100.0

400.0

4.5

150.0

600.0

0111_111

Reserved

1000_000

Reserved

1000_001

Reserved

1000_010

42.9

114.3

3.5

150.0

400.0

3.5

150.0

400.0

1000_011

37.5

114.3

3.5

131.3

400.0

4

150.0

457.1

1000_100

33.3

114.3

3.5

116.7

400.0

4.5

150.0

514.3

1000_101

30.0

114.3

3.5

105.0

400.0

5

150.0

571.4

1000_110

28.6

114.3

3.5

100.0

400.0

5.5

150.0

628.6

1100_000

Reserved

1100_001

Reserved

1100_010

Reserved

1101_000

Reserved

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

29

�Clock Configuration Modes

1

The “low” values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry

guarantees only the required minimum CPU operating frequency. The “high” values are for the purpose of illustration only.

Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of

the user’s device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For

modes with a CPU multiplication factor = 3.5: for Rev0.1 the minimum

CPU frequency is 250 MHz; for Rev A or later the minimum CPU frequency is 150 MHz for commercial temperature devices

and 175 MHz for extended temperature devices.

MODCK_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

60x and local bus frequency. Identical to CLKIN.

CPM multiplication factor = CPM clock/bus clock

CPU multiplication factor = Core PLL multiplication factor

2

3

4

5

7.2

PCI Host Mode

These tables show clock configurations for PCI host mode. The frequency values listed are for the purpose

of illustration only. Users must select a mode and input bus frequency so that the resulting configuration

does not exceed the frequency rating of the user’s device. Note that in PCI host mode the input clock is the

following:

NOTE: PCI_MODCK

In PCI mode only, PCI_MODCK comes from the LGPL5 pin and

MODCK_H[0–3] comes from {LGPL0, LGPL1, LGPL2, LGPL3}.

NOTE: Tval (Output Hold)

The minimum Tval = 2 ns when PCI_MODCK = 1, and the minimum

Tval = 1 ns when PCI_MODCK = 0. Therefore, designers should use clock

configurations that fit this condition to achieve PCI-compliant AC timing.

Table 19. Clock Configurations for PCI Host Mode (PCI_MODCK=0)1,2

Mode3

MODCK_HMODCK[1-3]

Bus Clock4

(MHz)

Low

High

CPM

Multiplication

Factor5

CPM Clock

(MHz)

Low

High

CPU

Multiplication

Factor6

CPU Clock

(MHz)

Low

High

PCI

Division

Factor

PCI Clock

(MHz)

Low High

Default Modes (MODCK_H=0000)

0000_000

60.0

66.7

2

120.0 133.3

2.5

150.0 166.7

2

60.0 66.7

0000_001

50.0

66.7

2

100.0 133.3

3

150.0 200.0

2

50.0 66.7

0000_010

60.0

80.0

2.5

150.0 200.0

3

180.0 240.0

3

50.0 66.7

0000_011

60.0

80.0

2.5

150.0 200.0

3.5

210.0 280.0

3

50.0 66.7

0000_100

60.0

80.0

2.5

150.0 200.0

4

240.0 320.0

3

50.0 66.7

0000_101

50.0

66.7

3

150.0 200.0

3

150.0 200.0

3

50.0 66.7

0000_110

50.0

66.7

3.5

150.0 200.0

3.5

175.0 233.3

3

50.0 66.7

0000_111

50.0

66.7

3

150.0 200.0

4

200.0 266.6

3

50.0 66.7

250.0 333.3

3

50.0 66.7

Full Configuration Modes

0001_000

50.0

66.7

3

150.0 200.0

5

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

30

Freescale Semiconductor

�Clock Configuration Modes

Table 19. Clock Configurations for PCI Host Mode (PCI_MODCK=0)1,2 (continued)

Mode3

Bus Clock4

(MHz)

CPM

Multiplication

Factor5

CPM Clock

(MHz)

CPU

Multiplication

Factor6

CPU Clock

(MHz)

PCI

Division

Factor

PCI Clock

(MHz)

MODCK_HMODCK[1-3]

Low

High

0001_001

50.0

66.7

3

150.0 200.0

6

300.0 400.0

3

50.0 66.7

0001_010

50.0

66.7

3

150.0 200.0

7

350.0 466.6

3

50.0 66.7

0001_011

50.0

66.7

3

150.0 200.0

8

400.0 533.3

3

50.0 66.7

0010_000

50.0

66.7

4

200.0 266.6

5

250.0 333.3

4

50.0 66.7

0010_001

50.0

66.7

4

200.0 266.6

6

300.0 400.0

4

50.0 66.7

0010_010

50.0

66.7

4

200.0 266.6

7

350.0 466.6

4

50.0 66.7

0010_011

50.0

66.7

4

200.0 266.6

8

400.0 533.3

4

50.0 66.7

0010_100

75.0

100.0

4

300.0 400.0

5

375.0 500.0

6

50.0 66.7

0010_101

75.0

100.0

4

300.0 400.0

5.5

412.5 549.9

6

50.0 66.7

0010_110

75.0

100.0

4

300.0 400.0

6

450.0 599.9

6

50.0 66.7

0011_000

50.0

66.7

5

250.0 333.3

5

250.0 333.3

5

50.0 66.7

0011_001

50.0

66.7

5

250.0 333.3

6

300.0 400.0

5

50.0 66.7

0011_010

50.0

66.7

5

250.0 333.3

7

350.0 466.6

5

50.0 66.7

0011_011

50.0

66.7

5

250.0 333.3

8

400.0 533.3

5

50.0 66.7

Low

High

0100_000

Low

High

Low High

Reserved

0100_001

50.0

66.7

6

300.0 400.0

6

300.0 400.0

6

50.0 66.7

0100_010

50.0

66.7

6

300.0 400.0

7

350.0 466.6

6

50.0 66.7

0100_011

50.0

66.7

6

300.0 400.0

8

400.0 533.3

6

50.0 66.7

0101_000

60.0

66.7

2

120.0 133.3

2.5

150.0 166.7

2

60.0 66.7

0101_001

50.0

66.7

2

100.0 133.3

3

150.0 200.0

2

50.0 66.7

0101_010

50.0

66.7

2

100.0 133.3

3.5

175.0 233.3

2

50.0 66.7

0101_011

50.0

66.7

2

100.0 133.3

4

200.0 266.6

2

50.0 66.7

0101_100

50.0

66.7

2

100.0 133.3

4.5

225.0 300.0

2

50.0 66.7

0110_000

60.0

80.0

2.5

150.0 200.0

2.5

150.0 200.0

3

50.0 66.7

0110_001

60.0

80.0

2.5

150.0 200.0

3

180.0 240.0

3

50.0 66.7

0110_010

60.0

80.0

2.5

150.0 200.0

3.5

210.0 280.0

3

50.0 66.7

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

31

�Clock Configuration Modes

Table 19. Clock Configurations for PCI Host Mode (PCI_MODCK=0)1,2 (continued)

Mode3

Bus Clock4

(MHz)

CPM

Multiplication

Factor5

CPM Clock

(MHz)

CPU

Multiplication

Factor6

CPU Clock

(MHz)

PCI

Division

Factor

PCI Clock

(MHz)

MODCK_HMODCK[1-3]

Low

High

0110_011

60.0

80.0

2.5

150.0 200.0

4

240.0 320.0

3

50.0 66.7

0110_100

60.0

80.0

2.5

150.0 200.0

4.5

270.0 360.0

3

50.0 66.7

0110_101

60.0

80.0

2.5

150.0 200.0

5

300.0 400.0

3

50.0 66.7

0110_110

60.0

80.0

2.5

150.0 200.0

6

360.0 480.0

3

50.0 66.7

Low

High

0111_000

Low

High

Low High

Reserved

0111_001

50.0

66.7

3

150.0 200.0

3

150.0 200.0

3

50.0 66.7

0111_010

50.0

66.7

3

150.0 200.0

3.5

175.0 233.3

3

50.0 66.7

0111_011

50.0

66.7

3

150.0 200.0

4

200.0 266.6

3

50.0 66.7

0111_100

50.0

66.7

3

150.0 200.0

4.5

225.0 300.0

3

50.0 66.7

1000_000

Reserved

1000_001

66.7

88.9

3

200.0 266.6

3

200.0 266.6

4

50.0 66.7

1000_010

66.7

88.9

3

200.0 266.6

3.5

233.3 311.1

4

50.0 66.7

1000_011

66.7

88.9

3

200.0 266.6

4

266.7 355.5

4

50.0 66.7

1000_100

66.7

88.9

3

200.0 266.6

4.5

300.0 400.0

4

50.0 66.7

1000_101

66.7

88.9

3

200.0 266.6

6

400.0 533.3

4

50.0 66.7

1000_110

66.7

88.9

3

200.0 266.6

6.5

433.3 577.7

4

50.0 66.7

1001_000

Reserved

1001_001

Reserved

1001_010

57.1

76.2

3.5

200.0 266.6

3.5

200.0 266.6

4

50.0 66.7

1001_011

57.1

76.2

3.5

200.0 266.6

4

228.6 304.7

4

50.0 66.7

1001_100

57.1

76.2

3.5

200.0 266.6

4.5

257.1 342.8

4

50.0 66.7

1001_101

85.7

114.3

3.5

300.0 400.0

5

428.6 571.4

6

50.0 66.7

1001_110

85.7

114.3

3.5

300.0 400.0

5.5

471.4 628.5

6

50.0 66.7

1001_111

85.7

114.3

3.5

300.0 400.0

6

514.3 685.6

6

50.0 66.7

1010_000

75.0

100.0

2

150.0 200.0

2

150.0 200.0

3

50.0 66.7

1010_001

75.0

100.0

2

150.0 200.0

2.5

187.5 250.0

3

50.0 66.7

1010_010

75.0

100.0

2

150.0 200.0

3

225.0 300.0

3

50.0 66.7

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

32

Freescale Semiconductor

�Clock Configuration Modes

Table 19. Clock Configurations for PCI Host Mode (PCI_MODCK=0)1,2 (continued)

Mode3

Bus Clock4

(MHz)

CPM

Multiplication

Factor5

CPM Clock

(MHz)

CPU

Multiplication

Factor6

CPU Clock

(MHz)

PCI

Division

Factor

PCI Clock

(MHz)

MODCK_HMODCK[1-3]

Low

High

1010_011

75.0

100.0

2

150.0 200.0

3.5

262.5 350.0

3

50.0 66.7

1010_100

75.0

100.0

2

150.0 200.0

4

300.0 400.0

3

50.0 66.7

Low

High

1011_000

Low

High

Low High

Reserved

1011_001

80.0

106.7

2.5

200.0 266.6

2.5

200.0 266.6

4

50.0 66.7

1011_010

80.0

106.7

2.5

200.0 266.6

3

240.0 320.0

4

50.0 66.7

1011_011

80.0

106.7

2.5

200.0 266.6

3.5

280.0 373.3

4

50.0 66.7

1011_100

80.0

106.7

2.5

200.0 266.6

4

320.0 426.6

4

50.0 66.7

1011_101

80.0

106.7

2.5

200.0 266.6

4.5

360.0 480.0

4

50.0 66.7

1101_000

100.0 133.3

2.5

250.0 333.3

3

300.0 400.0

5

50.0 66.7

1101_001

100.0 133.3

2.5

250.0 333.3

3.5

350.0 466.6

5

50.0 66.7

1101_010

100.0 133.3

2.5

250.0 333.3

4

400.0 533.3

5

50.0 66.7

1101_011

100.0 133.3

2.5

250.0 333.3

4.5

450.0 599.9

5

50.0 66.7

1101_100

100.0 133.3

2.5

250.0 333.3

5

500.0 666.6

5

50.0 66.7

1101_101

125.0 166.7

2

250.0 333.3

3

375.0 500.0

5

50.0 66.7

1101_110

125.0 166.7

2

250.0 333.3

4

500.0 666.6

5

50.0 66.7

1110_000

100.0 133.3

3

300.0 400.0

3.5

350.0 466.6

6

50.0 66.7

1110_001

100.0 133.3

3

300.0 400.0

4

400.0 533.3

6

50.0 66.7

1110_010

100.0 133.3

3

300.0 400.0

4.5

450.0 599.9

6

50.0 66.7

1110_011

100.0 133.3

3

300.0 400.0

5

500.0 666.6

6

50.0 66.7

1110_100

100.0 133.3

3

300.0 400.0

5.5

550.0 733.3

6

50.0 66.7

1100_000

Reserved

1100_001

Reserved

1100_010

Reserved

MPC8280 PowerQUICC II Family Hardware Specifications, Rev. 2

Freescale Semiconductor

33

�Clock Configuration Modes

1

The “low” values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry

guarantees only the required minimum CPU operating frequency. The “high” values are for the purpose of illustration only.

Users must select a mode and input bus frequency so that the resulting configuration does not violate the frequency rating of

the user’s device. The minimum CPM frequency is 120 MHz. Minimum CPU frequency is determined by the clock mode. For

modes with a CPU multiplication factor = 3.5: for Rev0.1 the minimum

CPU frequency is 250 MHz; for Rev A or later the minimum CPU frequency is 150 MHz for commercial temperature devices

and 175 MHz for extended temperature devices.

As Table 17 shows, PCI_MODCK determines the PCI clock frequency range. See Table 20 for lower configurations.

MODCK_H = hard reset configuration word [28–31]. MODCK[1-3] = three hardware configuration pins.

60x and local bus frequency. Identical to CLKIN.

CPM multiplication factor = CPM clock/bus clock

CPU multiplication factor = Core PLL multiplication factor

2

3

4

5

6

Table 20. Clock Configurations for PCI Host Mode (PCI_MODCK=1)1,2

Mode3

MODCK_HMODCK[1-3]

Bus Clock4

(MHz)

Low

High

CPM

Multiplication

Factor5

CPM Clock

(MHz)

Low

High

CPU

Multiplication

Factor6

CPU Clock

(MHz)

Low

High

PCI

Division

Factor

PCI Clock

(MHz)

Low High

Default Modes (MODCK_H=0000)

0000_000

60.0

100.0

2

120.0 200.0

2.5

150.0 250.0

4

30.0 50.0

0000_001

50.0

100.0

2

100.0 200.0

3

150.0 300.0

4

25.0 50.0

0000_010

60.0

120.0

2.5

150.0 300.0

3

180.0 360.0

6

25.0 50.0

0000_011

60.0

120.0

2.5

150.0 300.0

3.5

210.0 420.0

6

25.0 50.0

0000_100

60.0

120.0

2.5

150.0 300.0

4

240.0 480.0

6

25.0 50.0

0000_101

50.0

100.0

3

150.0 300.0

3

150.0 300.0

6

25.0 50.0

0000_110

50.0

100.0

3

150.0 300.0

3.5

175.0 350.0

6

25.0 50.0

0000_111

50.0

100.0

3

150.0 300.0

4

200.0 400.0

6

25.0 50.0

Full Configuration Modes

0001_000

50.0

100.0

3

150.0 300.0

5

250.0 500.0

6

25.0 50.0

0001_001

50.0

100.0