MC68HC705P6A

Advance Information Data Sheet

M68HC05

Microcontrollers

MC68HC705P6A

Rev. 2.1

9/2005

freescale.com

This document contains certain information on a new product.Specifications and information herein are subject to change without notice.

�Blank

�MC68HC705P6A

Advance Information Data Sheet

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://www.freescale.com/

The following revision history table summarizes changes contained in this document. For your

convenience, the page number designators have been linked to the appropriate location.

Revision History

Date

Revision

Level

November,

2001

Format update to current publication standards

N/A

2.0

Figure 11-1. Mask Option Register (MOR) — Definition of bit 6

corrected.

92

September,

2005

2.1

Updated to meet Freescale identity guidelines.

Description

Page

Number(s)

Throughout

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

3

�Revision History

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

4

Freescale Semiconductor

�List of Chapters

Chapter 1 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 3 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 4 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Chapter 5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Chapter 6 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Chapter 7 Serial Input/Output Port (SIOP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Chapter 8 Capture/Compare Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Chapter 9 Analog Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Chapter 10 EPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Chapter 11 Mask Option Register (MOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Chapter 12 Central Processor Unit (CPU) Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Chapter 13 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 14 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Chapter 15 Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Chapter 16 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

5

�List of Chapters

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

6

Freescale Semiconductor

�Table of Contents

Chapter 1

General Description

1.1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3

Functional Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1

VDD and VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2

OSC1 and OSC2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2.1

Crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2.2

Ceramic Resonator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2.3

External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.3

RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.4

PA0–PA7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.5

PB5/SDO, PB6/SDI, and PB7/SCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.6

PC0-PC2, PC3/AD3, PC4/AD2, PC5/AD1, PC6/AD0, and PC7/VREFH . . . . . . . . . . . . . . . .

1.3.7

PD5 and PD7/TCAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.8

TCMP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.9

IRQ/VPP (Maskable Interrupt Request) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

13

15

15

15

16

16

16

16

16

16

16

16

17

17

Chapter 2

Memory

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Mode Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bootloader Mode Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input/Output and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM/ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mask Option Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Computer Operating Properly (COP) Clear Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

19

19

19

19

19

24

25

Chapter 3

Operating Modes

3.1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2

User Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3

Bootloader Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1

STOP Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1.1

Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1.2

Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2

WAIT Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

COP Watchdog Timer Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

27

27

27

28

28

28

30

30

30

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

7

�Table of Contents

Chapter 4

Resets

4.1

4.2

4.3

4.3.1

4.3.2

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Reset (RESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Computer Operating Properly (COP) Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

31

31

31

31

32

Chapter 5

Interrupts

5.1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2

Interrupt Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1

Reset Interrupt Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2

Software Interrupt (SWI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3

Hardware Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3.1

External Interrupt (IRQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3.2

Input Capture Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3.3

Output Compare Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3.4

Timer Overflow Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

33

35

35

35

35

35

35

36

36

Chapter 6

Input/Output Ports

6.1

6.2

6.3

6.4

6.5

6.6

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Port Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

37

37

38

38

39

39

Chapter 7

Serial Input/Output Port (SIOP)

7.1

7.2

7.2.1

7.2.2

7.2.3

7.3

7.3.1

7.3.2

7.3.3

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIOP Signal Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Clock (SCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Data Input (SDI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Data Output (SDO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIOP Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIOP Control Register (SCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIOP Status Register (SSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIOP Data Register (SDR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

42

42

42

42

43

43

44

44

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

8

Freescale Semiconductor

�Table of Contents

Chapter 8

Capture/Compare Timer

8.1

8.2

8.2.1

8.2.2

8.3

8.3.1

8.3.2

8.3.3

8.3.4

8.3.5

8.3.6

8.4

8.5

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Alternate Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Capture Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Compare Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer During Wait/Halt Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer During Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

45

46

46

46

46

47

48

49

49

50

50

51

51

Chapter 9

Analog Subsystem

9.1

9.2

9.2.1

9.2.2

9.2.3

9.3

9.4

9.4.1

9.4.2

9.4.3

9.5

9.6

9.7

9.8

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ratiometric Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference Voltage (VREFH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Accuracy and Precision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Conversion Process. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Conversion Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal versus External Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multi-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Status and Control Register (ADSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Conversion Data Register (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Subsystem Operation during Halt/Wait Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Subsystem Operation during Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

53

53

53

53

53

53

54

54

54

54

55

56

56

Chapter 10

EPROM

10.1

10.2

10.3

10.4

10.5

10.6

10.7

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM Erasing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM Programming Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM Programming Register (EPROG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EPROM Bootloader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Programming from an External Memory Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

57

57

57

57

57

59

59

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

9

�Table of Contents

Chapter 11

Mask Option Register (MOR)

11.1

11.2

11.3

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Mask Option Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

MOR Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Chapter 12

Central Processor Unit (CPU) Core

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.1

Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.2

Index Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.3

Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.4

Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.5

Condition Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

67

67

68

68

68

68

Chapter 13

Instruction Set

13.1

13.2

13.2.1

13.2.2

13.2.3

13.2.4

13.2.5

13.2.6

13.2.7

13.2.8

13.3

13.3.1

13.3.2

13.3.3

13.3.4

13.3.5

13.4

13.5

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Inherent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Direct . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Extended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed, No Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed, 8-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Indexed,16-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Relative . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instruction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register/Memory Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Read-Modify-Write Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Jump/Branch Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bit Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Opcode Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

71

71

71

71

71

72

72

72

72

72

73

73

74

75

76

76

77

82

Chapter 14

Electrical Specifications

14.1

14.2

14.3

14.4

14.5

14.6

14.7

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.0-Volt DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3-Volt DC Electrical Charactertistics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

85

85

85

85

86

87

88

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

10

Freescale Semiconductor

�Table of Contents

14.8 EPROM Programming Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

14.9 SIOP Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

14.10 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Chapter 15

Mechanical Specifications

15.1

15.2

15.3

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Plastic Dual In-Line Package (Case 710) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Small Outline Integrated Circuit Package (Case 751F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Chapter 16

Ordering Information

16.1

16.2

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

11

�Table of Contents

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

12

Freescale Semiconductor

�Chapter 1

General Description

1.1 Introduction

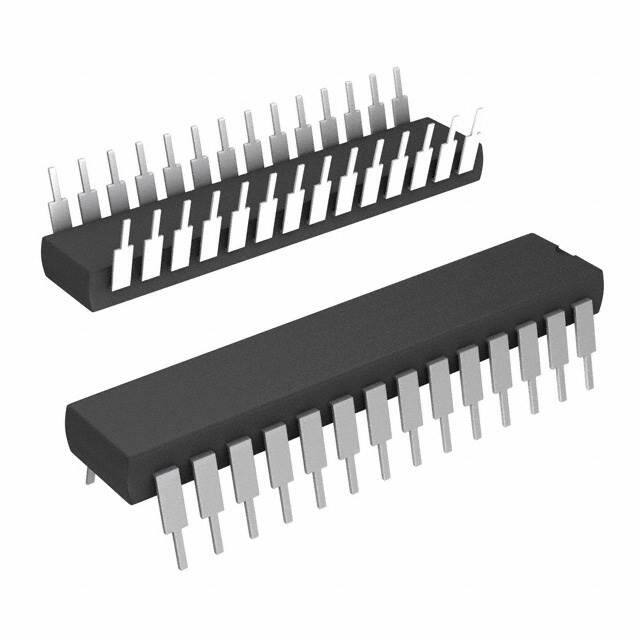

The MC68HC705P6A is an EPROM version of the MC68HC05P6 microcontroller. It is a low-cost

combination of an M68HC05 Family microprocessor with a 4-channel, 8-bit analog-to-digital (A/D)

converter, a 16-bit timer with output compare and input capture, a serial communications port (SIOP), and

a computer operating properly (COP) watchdog timer. The M68HC05 CPU core contains 176 bytes of

RAM, 4672 bytes of user EPROM, 239 bytes of bootloader ROM, and 21 input/output (I/O) pins (20

bidirectional, 1 input-only). This device is available in either a 28-pin plastic dual in-line (PDIP) or a 28-pin

small outline integrated circuit (SOIC) package.

A functional block diagram of the MC68HC705P6A is shown in Figure 1-1.

1.2 Features

Features of the MC68HC705P6A include:

• Low cost

• M68HC05 core

• 28-pin SOIC, PDIP, or windowed DIP package

• 4672 bytes of user EPROM (including 48 bytes of page zero EPROM and 16 bytes of user vectors)

•

239 bytes of bootloader ROM

• 176 bytes of on-chip RAM

• 4-channel 8-bit A/D converter

• SIOP serial communications port

• 16-bit timer with output compare and input capture

• 20 bidirectional I/O lines and 1 input-only line

• PC0 and PC1 high-current outputs

• Single-chip, bootloader, and test modes

• Power-saving stop, halt, and wait modes

• Static EPROM mask option register (MOR) selectable options:

– COP watchdog timer enable or disable

– Edge-sensitive or edge- and level-sensitive external interrupt

– SIOP most significant bit (MSB) or least significant bit (LSB) first

– SIOP clock rates: OSC divided by 8, 16, 32, or 64

– Stop instruction mode, STOP or HALT

– EPROM security external lockout

– Programmable keyscan (pullups/interrupts) on PA0–PA7

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

13

�General Description

INTERNAL

CPU CLOCK

COP

÷2

CPU CONTROL

ALU

RESET

M68HC05 CPU

IRQ/VPP

÷4

OSC

16-BIT TIMER

1 INPUT CAPTURE

1 OUTPUT COMPARE

PORT D LOGIC

OSC 1

OSC 2

PD7/TCAP

TCMP

PD5

ACCUM

PROGRAM COUNTER

COND CODE REG

1 1 1H I NZC

PC7/VREFH

PC6/AD0

MUX

A/ D CONVERTER

0 0 0 0 0 0 0 0 1 1 STK PNTR

PORT C

INDEX REG

DATA DIRECTION REGISTER

CPU REGISTERS

PC5/AD1

PC4/AD2

PC3/AD3

PC2

PC1

PC0

SRAM — 176 BYTES

BOOTLOADER ROM — 239 BYTES

PB5/SDO

PB6/SDI

PB7/SCK

PORT B AND

SIOP

REGISTERS

AND LOGIC

PA6

PA5

PORT A

USER EPROM — 4672 BYTES

DATA DIRECTION REG

PA7

PA4

PA3

PA2

PA1

PA0

VDD

VSS

Figure 1-1. MC68HC705P6A Block Diagram

NOTE

A line over a signal name indicates an active low signal. For example,

RESET is active high and RESET is active low.

Any reference to voltage, current, or frequency specified in the following

sections will refer to the nominal values. The exact values and their

tolerances or limits are specified in Chapter 14 Electrical Specifications.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

14

Freescale Semiconductor

�Functional Pin Description

1.3 Functional Pin Description

The following paragraphs describe the functionality of each pin on the MC68HC705P6A package. Pins

connected to subsystems described in other chapters provide a reference to the chapter instead of a

detailed functional description.

1.3.1 VDD and VSS

Power is supplied to the MCU through VDD and VSS. VDD is connected to a regulated +5 volt supply and

VSS is connected to ground.

Very fast signal transitions occur on the MCU pins. The short rise and fall times place very high

short-duration current demands on the power supply. To prevent noise problems, take special care to

provide good power supply bypassing at the MCU. Use bypass capacitors with good high-frequency

characteristics and position them as close to the MCU as possible. Bypassing requirements vary,

depending on how heavily the MCU pins are loaded.

1.3.2 OSC1 and OSC2

The OSC1 and OSC2 pins are the control connections for the on-chip oscillator. The OSC1 and OSC2

pins can accept the following:

1. A crystal as shown in Figure 1-2(a)

2. A ceramic resonator as shown in Figure 1-2(a)

3. An external clock signal as shown in Figure 1-2(b)

The frequency, fosc, of the oscillator or external clock source is divided by two to produce the internal bus

clock operating frequency, fop. The oscillator cannot be turned off by software unless the MOR bit, SWAIT,

is clear when a STOP instruction is executed.

To VDD (or STOP)

OSC1

MCU

OSC2

To VDD (or STOP)

OSC1

MCU

OSC2

4.7 MΩ

UNCONNECTED

EXTERNAL CLOCK

37 pF

(a)

37 pF

Crystal or Ceramic

Resonator Connections

(b)

External Clock Source

Connections

Figure 1-2. Oscillator Connections

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

15

�General Description

1.3.2.1 Crystal

The circuit in Figure 1-2(a) shows a typical oscillator circuit for an AT-cut, parallel resonant crystal. Follow

the crystal manufacturer’s recommendations, as the crystal parameters determine the external

component values required to provide maximum stability and reliable startup. The load capacitance

values used in the oscillator circuit design should include all stray capacitances. Mount the crystal and

components as close as possible to the pins for startup stabilization and to minimize output distortion.

1.3.2.2 Ceramic Resonator

In cost-sensitive applications, use a ceramic resonator in place of a crystal. Use the circuit in Figure 1-2(a)

for a ceramic resonator and follow the resonator manufacturer’s recommendations, as the resonator

parameters determine the external component values required for maximum stability and reliable starting.

The load capacitance values used in the oscillator circuit design should include all stray capacitances.

Mount the resonator and components as close as possible to the pins for startup stabilization and to

minimize output distortion.

1.3.2.3 External Clock

An external clock from another CMOS-compatible device can be connected to the OSC1 input, with the

OSC2 input not connected, as shown in Figure 1-2(b).

1.3.3 RESET

Driving this input low will reset the MCU to a known startup state. The RESET pin contains an internal

Schmitt trigger to improve its noise immunity. Refer to Chapter 4 Resets.

1.3.4 PA0–PA7

These eight I/O pins comprise port A. The state of any pin is software programmable and all port A lines

are configured as inputs during power-on or reset. Port A has mask-option register enabled interrupt

capability with internal pullup devices selectable for any pin. Refer to Chapter 6 Input/Output Ports.

1.3.5 PB5/SDO, PB6/SDI, and PB7/SCK

These three I/O pins comprise port B and are shared with the SIOP communications subsystem. The

state of any pin is software programmable, and all port B lines are configured as inputs during power-on

or reset. Refer to Chapter 6 Input/Output Ports and Chapter 7 Serial Input/Output Port (SIOP).

1.3.6 PC0-PC2, PC3/AD3, PC4/AD2, PC5/AD1, PC6/AD0, and PC7/VREFH

These eight I/O pins comprise port C and are shared with the A/D converter subsystem. The state of any

pin is software programmable and all port C lines are configured as inputs during power-on or reset. Refer

to Chapter 6 Input/Output Ports and Chapter 9 Analog Subsystem.

1.3.7 PD5 and PD7/TCAP

These two I/O pins comprise port D and one of them is shared with the 16-bit timer subsystem. The state

of PD5 is software programmable and is configured as an input during power-on or reset. PD7 is always

an input. It may be read at any time, regardless of which mode of operation the 16-bit timer is in. Refer to

Chapter 6 Input/Output Ports and Chapter 8 Capture/Compare Timer.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

16

Freescale Semiconductor

�Functional Pin Description

1.3.8 TCMP

This pin is the output from the 16-bit timer’s output compare function. It is low after reset. Refer to

Chapter 8 Capture/Compare Timer.

1.3.9 IRQ/VPP (Maskable Interrupt Request)

This input pin drives the asynchronous interrupt function of the MCU in user mode and provides the VPP

programming voltage in bootloader mode. The MCU will complete the current instruction being executed

before it responds to the IRQ interrupt request. When the IRQ/VPP pin is driven low, the event is latched

internally to signify an interrupt has been requested. When the MCU completes its current instruction, the

interrupt latch is tested. If the interrupt latch is set and the interrupt mask bit (I bit) in the condition code

register is clear, the MCU will begin the interrupt sequence.

Depending on the MOR LEVEL bit, the IRQ/VPP pin will trigger an interrupt on either a negative edge at

the IRQ/VPP pin and/or while the IRQ/VPP pin is held in the low state. In either case, the IRQ/VPP pin must

be held low for at least one tILIH time period. If the edge- and level-sensitive mode is selected (LEVEL bit

set), the IRQ/VPP input pin requires an external resistor connected to VDD for wired-OR operation. If the

IRQ/VPP pin is not used, it must be tied to the VDD supply. The IRQ/VPP pin input circuitry contains an

internal Schmitt trigger to improve noise immunity. Refer to Chapter 5 Interrupts.

NOTE

If the voltage level applied to the IRQ/VPP pin exceeds VDD, it may affect

the MCU’s mode of operation. See Chapter 3 Operating Modes.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

17

�General Description

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

18

Freescale Semiconductor

�Chapter 2

Memory

2.1 Introduction

The MC68HC705P6A utilizes 13 address lines to access an internal memory space covering 8 Kbytes.

This memory space is divided into I/O, RAM, ROM, and EPROM areas.

2.2 User Mode Memory Map

When the MC68HC705P6A is in the user mode, the 32 bytes of I/O, 176 bytes of RAM, 4608 bytes of user

EPROM, 48 bytes of user page zero EPROM, 239 bytes of bootloader ROM, and 16 bytes of user vectors

EPROM are all active as shown in Figure 2-1.

2.3 Bootloader Mode Memory Map

Memory space is identical to the user mode. See Figure 2-1.

2.4 Input/Output and Control Registers

Figure 2-2 and Figure 2-3 briefly describe the I/O and control registers at locations $0000–$001F.

Reading unimplemented bits will return unknown states, and writing unimplemented bits will be ignored.

2.5 RAM

The user RAM consists of 176 bytes (including the stack) at locations $0050 through $00FF. The stack

begins at address $00FF. The stack pointer can access 64 bytes of RAM from $00FF to $00C0.

NOTE

Using the stack area for data storage or temporary work locations requires

care to prevent it from being overwritten due to stacking from an interrupt

or subroutine call.

2.6 EPROM/ROM

There are 4608 bytes of user EPROM at locations $0100 through $12FF, plus 48 bytes in user page zero

locations $0020 through $004F, and 16 additional bytes for user vectors at locations $1FF0 through

$1FFF. The bootloader ROM and vectors are at locations $1F01 through $1FEF.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

19

�Memory

$0000

$001F

$0020

$004F

$0050

$00BF

$00C0

$00FF

$0100

I/O

32 BYTES

USER EPROM

48 BYTES

INTERNAL RAM

176 BYTES

STACK

64 BYTES

0000

0031

0032

0079

0080

4863

4864

$1FEF

$1FF0

$1FFF

MASK OPTION REGISTERS

BOOTLOADER ROM

AND VECTORS 239 BYTES

USER VECTORS EPROM

16 BYTES

$001F

0255

0256

UNIMPLEMENTED

3071 BYTES

$1EFE

$1EFF

$1F00

$1F01

I/O REGISTERS

SEE Figure 2-2

0191

0192

USER EPROM

4608 BYTES

$12FF

$1300

$0000

7934

7935

7936

7937

COP CLEAR REGISTER(1)

$1FF0

UNUSED

$1FF1

UNUSED

$1FF2

UNUSED

$1FF3

UNUSED

$1FF4

UNUSED

$1FF5

UNUSED

$1FF6

UNUSED

$1FF7

TIMER VECTOR (HIGH BYTE)

$1FF8

TIMER VECTOR (LOW BYTE)

$1FF9

8175

8176

IRQ VECTOR (HIGH BYTE)

$1FFA

IRQ VECTOR (LOW BYTE)

$1FFB

8191

SWI VECTOR (HIGH BYTE)

$1FFC

SWI VECTOR (LOW BYTE)

$1FFD

RESET VECTOR (HIGH BYTE)

$1FFE

RESET VECTOR (LOW BYTE)

$1FFF

Note 1. Writing zero to bit 0 of $1FF0 clears the COP watchdog timer. Reading $1FF0 returns user EPROM data.

Figure 2-1. MC68HC705P6A User Mode Memory Map

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

20

Freescale Semiconductor

�EPROM/ROM

PORT A DATA REGISTER

$0000

PORT B DATA REGISTER

$0001

PORT C DATA REGISTER

$0002

PORT D DATA REGISTER

$0003

PORT A DATA DIRECTION REGISTER

$0004

PORT B DATA DIRECTION REGISTER

$0005

PORT C DATA DIRECTION REGISTER

$0006

PORT D DATA DIRECTION REGISTER

$0007

UNIMPLEMENTED

$0008

UMIMPLEMENTED

$0009

SIOP CONTROL REGISTER

$000A

SIOP STATUS REGISTER

$000B

SIOP DATA REGISTER

$000C

RESERVED

$000D

UNIMPLEMENTED

$000E

UNIMPLEMENTED

$000F

UNIMPLEMENTED

$0010

UNIMPLEMENTED

$0011

TIMER CONTROL REGISTER

$0012

TIMER STATUS REGISTER

$0013

INPUT CAPTURE MSB

$0015

INPUT CAPTURE LSB

$0016

OUTPUT COMPARE MSB

$0017

OUTPUT COMPARE LSB

$0017

TIMER MSB

$0018

TIMER LSB

$0019

ALTERNATE COUNTER MSB

$001A

ALTERNATE COUNTER LSB

$001B

EPROM PROGRAMMING REGISTER

$001C

A/D CONVERTER DATA REGISTER

$001D

A/D CONVERTER CONTROL AND STATUS REGISTER

$001E

RESERVED

$001F

Figure 2-2. MC68HC705P6A I/O and Control

Registers Memory Map

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

21

�Memory

Addr.

$0000

$0001

$0002

$0003

$0004

$0005

$0006

Register Name

Port A Data Register

(PORTA)

See page 37.

Port B Data Register

(PORTB)

See page 38.

Port C Data Register

(PORTC)

See page 38.

Port D Data Register

(PORTD)

See page 39.

Port A Data Direction

Register (DDRA)

See page 37.

Port B Data Direction

Register (DDRB)

See page 38.

Port C Data Direction

Register (DDRC)

See page 38.

$0007

Port D Data Direction

Register (DDRD)

See page 39.

$0008

Unimplemented

$0009

Unimplemented

$000A

SIOP Control Register

(SCR)

See page 43.

$000B

$000C

SIOP Status Register

(SSR)

See page 44.

SIOP Data Register

(SDR)

See page 44.

Read:

Write:

Bit 7

6

5

4

3

2

1

Bit 0

PA7

PA6

PA5

PA4

PA3

PA2

PA1

PA0

0

0

0

PC2

PC1

PC0

0

0

0

Reset:

Read:

Write:

Unaffected by reset

PB7

PB6

PB5

Reset:

Read:

Write:

PC7

PC6

PC5

PC4

PC3

Unaffected by reset

PD7

0

Write:

PD5

Reset:

Read:

0

Unaffected by reset

Reset:

Read:

0

1

0

Unaffected by reset

DDRA7

DDRA6

DDRA5

DDRA4

DDRA3

DDRA2

DDRA1

DDRA0

0

0

0

0

0

0

0

0

DDRB7

DDRB6

DDRB5

1

1

1

1

1

0

0

0

0

0

0

0

0

DDRC7

DDRC6

DDRC5

DDRC4

DDRC3

DDRC2

DDRC1

DDRC0

Reset:

0

0

0

0

0

0

0

0

Read:

0

0

0

0

0

0

0

Reset:

0

0

0

0

0

0

0

Read:

0

0

0

0

0

Write:

Reset:

Read:

Write:

Reset:

Read:

Write:

Write:

Write:

SPE

DDRD5

0

0

MSTR

Reset:

0

0

0

0

0

0

0

0

Read:

SPIF

DCOL

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SDR7

SDR6

SDR5

SDR4

SDR3

SSDR2

SDR1

SDR0

Write:

Reset:

Read:

Write:

Reset:

Unaffected by reset

= Unimplemented

R

= Reserved

U = Undetermined

Figure 2-3. I/O and Control Register Summary (Sheet 1 of 3)

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

22

Freescale Semiconductor

�EPROM/ROM

Addr.

Register Name

$000D

Reserved for Test

$000E

Unimplemented

$000F

Unimplemented

$0010

Unimplemented

$0011

Unimplemented

$0012

Timer Control Register

(TCR)

See page 47.

$0013

$0014

$0015

$0016

$0017

$0018

$0019

$001A

Timer Status Register

(TSR)

See page 48.

Input Capture Register

MSB (ICRH)

See page 50.

Input Capture Register

LSB (ICRL)

See page 50.

Output Compare

Register MSB (OCRH)

See page 50.

Output Compare

Register LSB (OCRL)

See page 50.

Timer Register MSB

(TRH)

See page 49.

Timer Register LSB (TRL)

See page 49.

Alternate Timer

Register MSB (ATRH)

See page 49.

Bit 7

6

5

4

3

2

1

Bit 0

R

R

R

R

R

R

R

R

ICIE

OCIE

TOIE

0

0

0

IEDG

OLVL

Reset:

0

0

0

0

0

0

U

0

Read:

ICF

OCF

TOF

0

0

0

0

0

Read:

Write:

Write:

Reset:

U

U

U

0

0

0

0

0

Read:

ICRH7

ICRH6

ICRH5

ICRH4

ICRH3

ICRH2

ICRH1

ICRH0

ICRL2

ICRL1

ICRL0

OCRH2

OCRH1

OCRH0

OCRL2

OCRL1

OCRL0

Write:

Reset:

Read:

Unaffected by reset

ICRL7

ICRL6

ICRL5

ICRL4

ICRL3

Write:

Reset:

Read:

Write:

Unaffected by reset

OCRH7

OCRH6

OCRH5

Reset:

Read:

OCRH4

OCRH3

Unaffected by reset

OCRL7

OCRL6

OCRL5

TRH7

TRH6

TRH5

TRH4

TRH3

TRH2

TRH1

TRH0

Reset:

1

1

1

1

1

1

1

1

Read:

TRL7

TRL6

TRL5

TRL4

TRL3

TRL2

TRL1

TRL0

Reset:

1

1

1

1

1

1

0

0

Read:

ACRH7

ACRH6

ACRH5

ACRH4

ACRH3

ACRH2

ACRH1

ACRH0

1

1

1

1

1

1

1

1

R

= Reserved

Write:

Reset:

Read:

OCRL4

OCRL3

Unaffected by reset

Write:

Write:

Write:

Reset:

= Unimplemented

U = Undetermined

Figure 2-3. I/O and Control Register Summary (Sheet 2 of 3)

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

23

�Memory

Addr.

$001B

$001C

$001D

Register Name

Alternate Timer

Register LSB (ATRL)

See page 49.

$001F

Reserved for Test

5

4

3

2

1

Bit 0

ACRL5

ACRL4

ACRL3

ACRL2

ACRL1

ACRL0

Reset:

1

1

1

1

1

1

0

0

Read:

0

0

0

0

0

Reset:

0

0

0

0

0

0

0

0

Read:

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

CH2

CH1

CH0

Write:

A/D Conversion Value

Data Register (ADC)

See page 55.

$001E

6

ACRL6

Write:

EPROM Programming

Register (EPROG)

See page 58.

A/D Status and Control

Register (ADSC)

See page 54.

Bit 7

ACRL7

Read:

0

ELAT

EPGM

Write:

Reset:

Unaffected by reset

Read:

CC

Write:

Reset:

ADRC

0

ADON

0

0

0

0

0

0

0

0

0

R

R

R

R

R

R

R

R

R

= Reserved

= Unimplemented

U = Undetermined

Figure 2-3. I/O and Control Register Summary (Sheet 3 of 3)

2.7 Mask Option Register

The mask option register (MOR) is a pair of EPROM bytes located at $1EFF and $1F00. It controls the

programmable options on the MC68HC705P6A. See Chapter 11 Mask Option Register (MOR) for

additional information.

$1EFF

Read:

Write:

Erased State:

$1F00

Read:

Write:

Erased State:

Bit 7

6

5

4

3

2

1

Bit 0

PA7PU

PA6PU

PA5PU

PA4PU

PA3PU

PA2PU

PA1PU

PA0PU

0

0

0

0

0

0

0

0

Bit 7

6

5

4

3

2

1

Bit 0

SWAIT

SPR1

SPR0

LSBF

LEVEL

COP

0

0

0

0

0

0

SECURE

0

0

= Unimplemented

Figure 2-4. Mask Option Register (MOR)

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

24

Freescale Semiconductor

�Computer Operating Properly (COP) Clear Register

2.8 Computer Operating Properly (COP) Clear Register

The computer operating properly (COP) watchdog timer is located at address $1FF0. Writing a logical 0

to bit zero of this location will clear the COP watchdog counter as described in 4.3.2 Computer Operating

Properly (COP) Reset.

$1FF0

Bit 7

6

5

4

3

2

1

Bit 0

Read:

0

0

0

0

0

0

0

0

Write:

Reset:

COPR

0

0

0

0

0

0

0

0

= Unimplemented

Figure 2-5. COP Watchdog Timer Location

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

25

�Memory

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

26

Freescale Semiconductor

�Chapter 3

Operating Modes

3.1 Introduction

The MC68HC705P6A has two modes of operation that affect the pinout and architecture of the MCU:

user mode and bootloader mode. The user mode is normally used for the application and the bootloader

mode is used for programming the EPROM. The conditions required to enter each mode are shown in

Table 3-1. The mode of operation is determined by the voltages on the IRQ/VPP and PD7/TCAP pins on

the rising edge of the external RESET pin.

Table 3-1. Operating Mode Conditions After Reset

RESET Pin

IRQ/VPP

PD7/TCAP

Mode

VSS to VDD

VSS to VDD

Single chip

VPP

VDD

Bootloader

The mode of operation is also determined whenever the internal computer operating properly (COP)

watchdog timer resets the MCU. When the COP timer expires, the voltage applied to the IRQ/VPP pin

controls the mode of operation while the voltage applied to PD7/TCAP is ignored. The voltage applied to

PD7/TCAP during the last rising edge on RESET is stored in a latch and used to determine the mode of

operation when the COP watchdog timer resets the MCU.

3.2 User Mode

The user mode allows the MCU to function as a self-contained microcontroller, with maximum use of the

pins for on-chip peripheral functions. All address and data activity occurs within the MCU and are not

available externally. User mode is entered on the rising edge of RESET if the IRQ/VPP pin is within the

normal operating voltage range. The pinout for the user mode is shown in Figure 3-1.

In the user mode, there is an 8-bit I/O port, a second 8-bit I/O port shared with the analog-to-digital (A/D)

subsystem, one 3-bit I/O port shared with the serial input/output port (SIOP), and a 3-bit port shared with

the 16-bit timer subsystem, which includes one general-purpose I/O pin.

3.3 Bootloader Mode

The bootloader mode provides a means to program the user EPROM from an external memory device or

host computer. This mode is entered on the rising edge of RESET if VPP is applied to the IRQ/VPP pin and

VDD is applied to the PD7/TCAP pin. The user code in the external memory device must have data located

in the same address space it will occupy in the internal MCU EPROM, including the mask option register

(MOR) at $1EFF and $1F00.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

27

�Operating Modes

RESET

1

28

VDD

IRQ/VPP

2

27

OSC1

PA7

3

26

OSC2

PA6

4

25

PD7/TCAP

PA5

5

24

TCMP

PA4

6

23

PD5

PA3

7

22

PC0

PA2

8

21

PC1

PA1

9

20

PC2

PA0

10

19

PC3/AD3

SDO/PB5

11

18

PC4/AD2

SDI/PB6

12

17

PC5/AD1

SCK/PB7

13

16

PC6/AD0

VSS

14

15

PC7/VREFH

Figure 3-1. User Mode Pinout

3.4 Low-Power Modes

The MC68HC705P6A is capable of running in a low-power mode in each of its configurations. The WAIT

and STOP instructions provide three modes that reduce the power required for the MCU by stopping

various internal clocks and/or the on-chip oscillator. The SWAIT bit in the MOR is used to modify the

behavior of the STOP instruction from stop mode to halt mode. The flow of the stop, halt, and wait modes

is shown in Figure 3-2.

3.4.1 STOP Instruction

The STOP instruction can result in one of two modes of operation depending on the state of the SWAIT

bit in the MOR. If the SWAIT bit is clear, the STOP instruction will behave like a normal STOP instruction

in the M68HC05 Family and place the MCU in stop mode. If the SWAIT bit in the MOR is set, the STOP

instruction will behave like a WAIT instruction (with the exception of a brief delay at startup) and place the

MCU in halt mode.

3.4.1.1 Stop Mode

Execution of the STOP instruction when the SWAIT bit in the MOR is clear places the MCU in its lowest

power consumption mode. In stop mode, the internal oscillator is turned off, halting all internal processing,

including the COP watchdog timer. Execution of the STOP instruction automatically clears the I bit in the

condition code register so that the IRQ external interrupt is enabled. All other registers and memory

remain unaltered. All input/output lines remain unchanged.

The MCU can be brought out of stop mode only by an IRQ external interrupt or an externally generated

RESET. When exiting stop mode, the internal oscillator will resume after a 4064 internal clock cycle

oscillator stabilization delay.

NOTE

Execution of the STOP instruction when the SWAIT bit in the MOR is clear

will cause the oscillator to stop, and, therefore, disable the COP watchdog

timer. To avoid turning off the COP watchdog timer, stop mode should be

changed to halt mode by setting the SWAIT bit in the MOR. See 3.5 COP

Watchdog Timer Considerations for additional information.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

28

Freescale Semiconductor

�Low-Power Modes

STOP

MOR

SWAIT

BIT SET?

HALT

WAIT

EXTERNAL OSCILLATOR ACTIVE

AND

INTERNAL TIMER CLOCK ACTIVE

Y

N

STOP EXTERNAL OSCILLATOR,

STOP INTERNAL TIMER CLOCK,

RESET STARTUP DELAY

Y

STOP INTERNAL

PROCESSOR CLOCK,

CLEAR I BIT IN CCR

STOP INTERNAL

PROCESSOR CLOCK,

CLEAR I BIT IN CCR

EXTERNAL OSCILLATOR ACTIVE

AND

INTERNAL TIMER CLOCK ACTIVE

EXTERNAL

RESET?

STOP INTERNAL

PROCESSOR CLOCK,

CLEAR I BIT IN CCR

N

EXTERNAL

RESET?

Y

Y

IRQ

EXTERNAL

INTERRUPT?

N

IRQ

EXTERNAL

INTERRUPT?

N

Y

N

N

Y

Y

TIMER

INTERNAL

INTERRUPT?

RESTART EXTERNAL OSCILLATOR,

START STABILIZATION DELAY

END

OF STABILIZATION

DELAY?

Y

COP

INTERNAL

RESET?

Y

Y

Y

RESTART

INTERNAL PROCESSOR CLOCK

2.

TIMER

INTERNAL

INTERRUPT?

N

N

N

1.

IRQ

EXTERNAL

INTERRUPT?

N

N

Y

EXTERNAL

RESET?

COP

INTERNAL

RESET?

N

FETCH RESET VECTOR

OR

SERVICE INTERRUPT

A. STACK

B. SET I BIT

C. VECTOR TO INTERRUPT ROUTINE

Figure 3-2. STOP/WAIT Flowcharts

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

29

�Operating Modes

3.4.1.2 Halt Mode

NOTE

Halt mode is NOT designed for intentional use. Halt mode is only provided

to keep the COP watchdog timer active in the event a STOP instruction is

executed inadvertently. This mode of operation is usually achieved by

invoking wait mode.

Execution of the STOP instruction when the SWAIT bit in the MOR is set places the MCU in this low-power

mode. Halt mode consumes the same amount of power as wait mode (both halt and wait modes consume

more power than stop mode).

In halt mode, the internal clock is halted, suspending all processor and internal bus activity. Internal timer

clocks remain active, permitting interrupts to be generated from the 16-bit timer or a reset to be generated

from the COP watchdog timer. Execution of the STOP instruction automatically clears the I bit in the

condition code register, enabling the IRQ external interrupt. All other registers, memory, and input/output

lines remain in their previous states.

If the 16-bit timer interrupt is enabled, it will cause the processor to exit the halt mode and resume normal

operation. The halt mode also can be exited when an IRQ external interrupt or external RESET occurs.

When exiting the halt mode, the internal clock will resume after a delay of one to 4064 internal clock

cycles. This varied delay time is the result of the halt mode exit circuitry testing the oscillator stabilization

delay timer (a feature of the stop mode), which has been free-running (a feature of the wait mode).

3.4.2 WAIT Instruction

The WAIT instruction places the MCU in a low-power mode which consumes more power than stop mode.

In wait mode, the internal clock is halted, suspending all processor and internal bus activity. Internal timer

clocks remain active, permitting interrupts to be generated from the 16-bit timer and reset to be generated

from the COP watchdog timer. Execution of the WAIT instruction automatically clears the I bit in the

condition code register, enabling the IRQ external interrupt. All other registers, memory, and input/output

lines remain in their previous state.

If the 16-bit timer interrupt is enabled, it will cause the processor to exit wait mode and resume normal

operation. The 16-bit timer may be used to generate a periodic exit from wait mode. Wait mode may also

be exited when an IRQ external interrupt or RESET occurs.

3.5 COP Watchdog Timer Considerations

The COP watchdog timer is active in user mode of operation when the COP bit in the MOR is set.

Executing the STOP instruction when the SWAIT bit in the MOR is clear will cause the COP to be

disabled. Therefore, it is recommended that the STOP instruction be modified to produce halt mode (set

bit SWAIT in the MOR) if the COP watchdog timer is required to function at all times.

Furthermore, it is recommended that the COP watchdog timer be disabled for applications that will use

the wait mode for time periods that will exceed the COP timeout period.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

30

Freescale Semiconductor

�Chapter 4

Resets

4.1 Introduction

The MCU can be reset from three sources: one external input and two internal reset conditions. The

RESET pin is a Schmitt trigger input as shown in Figure 4-1. The CPU and all peripheral modules will be

reset by the RST signal which is the logical OR of internal reset functions and is clocked by PH1.

RESET

VDD

OSC

DATA

ADDRESS

POWER-ON

RESET

(POR)

COP

WATCHDOG

(COPR)

D

RST

RES

DFF

TO CPU AND

PERIPHERALS

PH1

Figure 4-1. Reset Block Diagram

4.2 External Reset (RESET)

The RESET input is the only external reset and is connected to an internal Schmitt trigger. The external

reset occurs whenever the RESET input is driven below the lower threshold and remains in reset until the

RESET pin rises above the upper threshold. The upper and lower thresholds are given in Chapter 14

Electrical Specifications.

4.3 Internal Resets

The two internally generated resets are the initial power-on reset (POR) function and the computer

operating properly (COP) watchdog timer function.

4.3.1 Power-On Reset (POR)

The internal POR is generated at power-up to allow the clock oscillator to stabilize. The POR is strictly for

power turn-on conditions and should not be used to detect a drop in the power supply voltage. There is a

4064 internal clock cycle oscillator stabilization delay after the oscillator becomes active.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

31

�Resets

The POR will generate the RST signal and reset the MCU. If any other reset function is active at the end

of this 4064 internal clock cycle delay, the RST signal will remain active until the other reset condition(s)

end.

4.3.2 Computer Operating Properly (COP) Reset

When the COP watchdog timer is enabled (COP bit in the MOR is set), the internal COP reset is

generated automatically by a timeout of the COP watchdog timer. This timer is implemented with an

18-stage ripple counter that provides a timeout period of 65.5 ms when a 4-MHz oscillator is used. The

COP watchdog counter is cleared by writing a logical 0 to bit zero at location $1FF0.

The COP watchdog timer can be disabled by clearing the COP bit in the MOR or by applying 2 x VDD to

the IRQ/VPP pin (for example, during bootloader). When the IRQ/VPP pin is returned to its normal

operating voltage range (between VSS–VDD), the COP watchdog timer’s output will be restored if the COP

bit in the mask option register (MOR) is set.

The COP register is shared with the least significant byte (LSB) of an unused vector address as shown

in Figure 4-2. Reading this location will return the programmed value of the unused user interrupt vector,

usually 0. Writing to this location will clear the COP watchdog timer.

Address:

Read:

$1FF0

Bit 7

6

5

4

3

2

1

0

0

0

0

0

0

0

Bit 0

0

COPR

Write:

= Unimplemented

Figure 4-2. Unused Vector and COP Watchdog Timer

When the COP watchdog timer expires, it will generate the RST signal and reset the MCU. If any other

reset function is active at the end of the COP reset signal, the RST signal will remain in the reset condition

until the other reset condition(s) end. When the reset condition ends, the MCU’s operating mode will be

selected (see Table 3-1. Operating Mode Conditions After Reset).

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

32

Freescale Semiconductor

�Chapter 5

Interrupts

5.1 Introduction

The MCU can be interrupted six different ways:

1. Non-maskable software interrupt instruction (SWI)

2. External asynchronous interrupt (IRQ)

3. Input capture interrupt (TIMER)

4. Output compare interrupt (TIMER)

5. Timer overflow interrupt (TIMER)

6. Port A interrupt (if selected via mask option register)

Interrupts cause the processor to save the register contents on the stack and to set the interrupt mask (I

bit) to prevent additional interrupts. Unlike reset, hardware interrupts do not cause the current instruction

execution to be halted, but are considered pending until the current instruction is completed.

When the current instruction is completed, the processor checks all pending hardware interrupts. If

interrupts are not masked (I bit in the condition code register is clear) and the corresponding interrupt

enable bit is set, the processor proceeds with interrupt processing. Otherwise, the next instruction is

fetched and executed. The SWI is executed the same as any other instruction, regardless of the I-bit state.

When an interrupt is to be processed, the CPU puts the register contents on the stack, sets the I bit in the

CCR, and fetches the address of the corresponding interrupt service routine from the vector table at

locations $1FF8 through $1FFF. If more than one interrupt is pending when the interrupt vector is fetched,

the interrupt with the highest vector location shown in Table 5-1 will be serviced first.

Table 5-1. Vector Addresses for Interrupts and Reset

Register

Flag

Name

N/A

N/A

Interrupts

Reset

CPU

Interrupt

Vector

Address

RESET

$1FFE–$1FFF

N/A

N/A

Software

SWI

$1FFC–$1FFD

N/A

N/A

External Interrupt

IRQ

$1FFA–$1FFB

TSR

ICF

Timer Input Capture

TIMER

$1FF8–$1FF9

TSR

OCF

Timer Output Compare

TIMER

$1FF8–$1FF9

TSR

TOF

Timer Overflow

TIMER

$1FF8–$1FF9

An RTI instruction is used to signify when the interrupt software service routine is completed. The RTI

instruction causes the CPU state to be recovered from the stack and normal processing to resume at the

next instruction that was to be executed when the interrupt took place. Figure 5-1 shows the sequence of

events that occurs during interrupt processing.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

33

�Interrupts

FROM RESET

Y

IS I BIT

SET?

N

IRQ

INTERRUPT?

Y

CLEAR IRQ

REQUEST

LATCH

N

TIMER

INTERRUPT?

Y

N

STACK

PC, X, A, CC

SET

I BIT IN CCR

LOAD PC FROM:

SWI: $1FFC, $1FFD

IRQ: $1FFA-$1FFB

TIMER: $1FF8-$1FF9

FETCH NEXT

INSTRUCTION

SWI

INSTRUCTION?

Y

N

RTI

INSTRUCTION?

Y

RESTORE RESISTERS

FROM STACK

CC, A, X, PC

N

EXECUTE INSTRUCTION

Figure 5-1. Interrupt Processing Flowchart

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

34

Freescale Semiconductor

�Interrupt Types

5.2 Interrupt Types

The interrupts fall into three categories: reset, software, and hardware.

5.2.1 Reset Interrupt Sequence

The reset function is not in the strictest sense an interrupt; however, it is acted upon in a similar manner

as shown in Figure 5-1. A low-level input on the RESET pin or internally generated RST signal causes

the program to vector to its starting address which is specified by the contents of memory locations $1FFE

and $1FFF. The I bit in the condition code register is also set. The MCU is configured to a known state

during this type of reset as previously described in Chapter 4 Resets.

5.2.2 Software Interrupt (SWI)

The SWI is an executable instruction. It is also a non-maskable interrupt since it is executed regardless

of the state of the I bit in the CCR. As with any instruction, interrupts pending during the previous

instruction will be serviced before the SWI opcode is fetched. The interrupt service routine address for the

SWI instruction is specified by the contents of memory locations $1FFC and $1FFD.

5.2.3 Hardware Interrupts

All hardware interrupts are maskable by the I bit in the CCR. If the I bit is set, all hardware interrupts

(internal and external) are disabled. Clearing the I bit enables the hardware interrupts. Four hardware

interrupts are explained in the following subsections.

5.2.3.1 External Interrupt (IRQ)

The IRQ/VPP pin drives an asynchronous interrupt to the CPU. An edge detector flip-flop is latched on the

falling edge of IRQ/VPP. If either the output from the internal edge detector flip-flop or the level on the

IRQ/VPP pin is low, a request is synchronized to the CPU to generate the IRQ interrupt. If the LEVEL bit

in the mask option register is clear (edge-sensitive only), the output of the internal edge detector flip-flop

is sampled and the input level on the IRQ/VPP pin is ignored. The interrupt service routine address is

specified by the contents of memory locations $1FFA and $1FFB. If the port A interrupts are enabled by

the MOR, they generate external interrupts identically to the IRQ/VPP pin.

NOTE

The internal interrupt latch is cleared nine internal clock cycles after the

interrupt is recognized (immediately after location $1FFA is read).

Therefore, another external interrupt pulse could be latched during the IRQ

service routine.

Another interrupt will be serviced if the IRQ pin is still in a low state when

the RTI in the service routine is executed.

5.2.3.2 Input Capture Interrupt

The input capture interrupt is generated by the 16-bit timer as described in Chapter 8 Capture/Compare

Timer. The input capture interrupt flag is located in register TSR and its corresponding enable bit can be

found in register TCR. The I bit in the CCR must be clear for the input capture interrupt to be enabled. The

interrupt service routine address is specified by the contents of memory locations $1FF8 and $1FF9.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

35

�Interrupts

5.2.3.3 Output Compare Interrupt

The output compare interrupt is generated by a 16-bit timer as described in Chapter 8 Capture/Compare

Timer. The output compare interrupt flag is located in register TSR and its corresponding enable bit can

be found in register TCR. The I bit in the CCR must be clear for the output compare interrupt to be

enabled. The interrupt service routine address is specified by the contents of memory locations $1FF8

and $1FF9.

5.2.3.4 Timer Overflow Interrupt

The timer overflow interrupt is generated by the 16-bit timer as described in Chapter 8 Capture/Compare

Timer. The timer overflow interrupt flag is located in register TSR and its corresponding enable bit can be

found in register TCR. The I bit in the CCR must be clear for the timer overflow interrupt to be enabled.

This internal interrupt will vector to the interrupt service routine located at the address specified by the

contents of memory locations $1FF8 and $1FF9.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

36

Freescale Semiconductor

�Chapter 6

Input/Output Ports

6.1 Introduction

In the user mode, 20 bidirectional I/O lines are arranged as two 8-bit I/O ports (ports A and C), one 3-bit

I/O port (port B), and one 1-bit I/O port (port D). These ports are programmable as either inputs or outputs

under software control of the data direction registers (DDRs). Port D also contains one input-only pin.

6.2 Port A

Port A is an 8-bit bidirectional port, which does not share any of its pins with other subsystems (see

Figure 6-1). The port A data register is located at address $0000 and its data direction register (DDR) is

located at address $0004. The contents of the port A data register are indeterminate at initial power up

and must be initialized by user software. Reset does not affect the data registers, but does clear the

DDRs, thereby setting all of the port pins to input mode. Writing a 1 to a DDR bit sets the corresponding

port pin to output mode. Port A has mask option register enabled interrupt capability with an internal pullup

device

NOTE

The keyscan (pullup/interrupt) feature available on port A is NOT available

in the ROM device, MC68HC05P6.

VDD

PULLUP MASK

OPTION REGISTER

READ $0004

WRITE $0004

RESET

(RST)

WRITE $0000

DATA DIRECTION

REGISTER BIT

DATA

REGISTER BIT

OUTPUT

I/O

PIN

READ $0000

INTERNAL HC05

DATA BUS

TO IRQ

INTERRUPT SYSTEM

Figure 6-1. Port A I/O and Interrupt Circuitry

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

Freescale Semiconductor

37

�Input/Output Ports

6.3 Port B

Port B is a 3-bit bidirectional port which can share pins PB5–PB7 with the SIOP communications

subsystem. The port B data register is located at address $0001 and its data direction register (DDR) is

located at address $0005. The contents of the port B data register are indeterminate at initial powerup

and must be initialized by user software. Reset does not affect the data registers, but clears the DDRs,

thereby setting all of the port pins to input mode. Writing a 1 to a DDR bit sets the corresponding port pin

to output mode (see Figure 6-2).

Port B may be used for general I/O applications when the SIOP subsystem is disabled. The SPE bit in

register SPCR is used to enable/disable the SIOP subsystem. When the SIOP subsystem is enabled, port

B registers are still accessible to software. Writing to either of the port B registers while a data transfer is

under way could corrupt the data. See Chapter 7 Serial Input/Output Port (SIOP) for a discussion of the

SIOP subsystem.

READ $0005

WRITE $0005

RESET

(RST)

WRITE $0001

DATA DIRECTION

REGISTER BIT

DATA

REGISTER BIT

OUTPUT

I/O

PIN

READ $0001

INTERNAL HC05

DATA BUS

Figure 6-2. Port B I/O Circuitry

6.4 Port C

Port C is an 8-bit bidirectional port which can share pins PC3–PC7 with the A/D subsystem. The port C

data register is located at address $0002 and its data direction register (DDR) is located at address

$0006. The contents of the port C data register are indeterminate at initial powerup and must be initialized

by user software. Reset does not affect the data registers, but clears the DDRs, thereby setting all of the

port pins to input mode. Writing a 1 to a DDR bit sets the corresponding port pin to output mode (see

Figure 6-3).

Port C may be used for general I/O applications when the A/D subsystem is disabled. The ADON bit in

register ADSC is used to enable/disable the A/D subsystem. Care must be exercised when using pins

PC0–PC2 while the A/D subsystem is enabled. Accidental changes to bits that affect pins PC3–PC7 in

the data or DDR registers will produce unpredictable results in the A/D subsystem. See Chapter 9 Analog

Subsystem.

MC68HC705P6A Advance Information Data Sheet, Rev. 2.1

38

Freescale Semiconductor

�Port D

READ $0006

WRITE $0006

RESET

(RST)

DATA DIRECTION

REGISTER BIT

WRITE $0002

DATA

REGISTER BIT

OUTPUT

I/O

PIN

READ $0002

INTERNAL HC05

DATA BUS

Figure 6-3. Port C I/O Circuitry

6.5 Port D

Port D is a 2-bit port with one bidirectional pin (PD5) and one input-only pin (PD7). Pin PD7 is shared with

the 16-bit timer. The port D data register is located at address $0003 and its data direction register (DDR)

is located at address $0007. The contents of the port D data register are indeterminate at initial powerup

and must be initialized by user software. Reset does not affect the data registers, but clears the DDRs,

thereby setting PD5 to input mode. Writing a 1 to DDR bit 5 sets PD5 to output mode (see Figure 6-4).

Port D may be used for general I/O applications regardless of the state of the 16-bit timer. Since PD7 is

an input-only line, its state can be read from the port D data register at any time.

READ $0007

WRITE $0007

RESET

(RST)

DATA DIRECTION

REGISTER BIT

WRITE $0003

DATA

REGISTER BIT

OUTPUT

I/O