NXP Semiconductors

Data Sheet: Technical Data

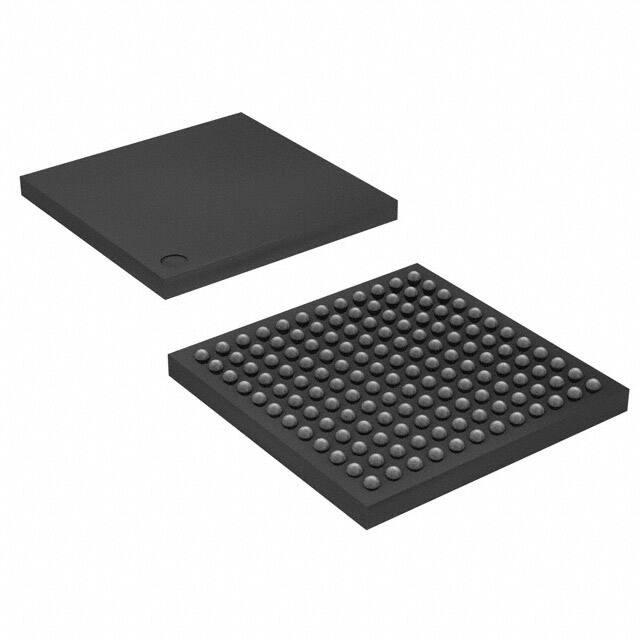

K61 Sub-Family

Document Number K61P256M150SF3

Rev. 7, 02/2018

K61P256M150SF3

Supports the following:

MK61FX512VMJ15,

MK61FN1M0VMJ15

Key features

• Operating Characteristics

– Voltage range: 1.71 to 3.6 V

– Flash write voltage range: 1.71 to 3.6 V

– Temperature range (ambient): -40 to 105°C

• Performance

– Up to 150 MHz Arm® Cortex®-M4 core with DSP

instructions delivering 1.25 Dhrystone MIPS per

MHz

• Memories and memory interfaces

– Up to 1024 KB program flash memory on nonFlexMemory devices

– Up to 512 KB program flash memory on

FlexMemory devices

– Up to 512 KB FlexNVM on FlexMemory devices

– 16 KB FlexRAM on FlexMemory devices

– Up to 128 KB RAM

– Serial programming interface (EzPort)

– FlexBus external bus interface

– DDR controller interface

– NAND flash controller interface

• Clocks

– 3 to 32 MHz crystal oscillator

– 32 kHz crystal oscillator

– Multi-purpose clock generator

• System peripherals

– Multiple low-power modes to provide power

optimization based on application requirements

– Memory protection unit with multi-master

protection

– 32-channel DMA controller, supporting up to 128

request sources

– External watchdog monitor

– Software watchdog

– Low-leakage wakeup unit

• Security and integrity modules

– Hardware CRC module to support fast cyclic

redundancy checks

– Tamper detect and secure storage

– Hardware random-number generator

– Hardware encryption supporting DES, 3DES, AES,

MD5, SHA-1, and SHA-256 algorithms

– 128-bit unique identification (ID) number per chip

• Human-machine interface

– Low-power hardware touch sensor interface (TSI)

– General-purpose input/output

• Analog modules

– Four 16-bit SAR ADCs

– Programmable gain amplifier (PGA) (up to x64)

integrated into each ADC

– Two 12-bit DACs

– Four analog comparators (CMP) containing a 6-bit

DAC and programmable reference input

– Voltage reference

• Timers

– Programmable delay block

– Two 8-channel motor control/general purpose/PWM

timers

– Two 2-channel quadrature decoder/general purpose

timers

– IEEE 1588 timers

– Periodic interrupt timers

– 16-bit low-power timer

– Carrier modulator transmitter

– Real-time clock

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

�• Communication interfaces

– Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

– USB high-/full-/low-speed On-the-Go controller with ULPI interface

– USB full-/low-speed On-the-Go controller with on-chip transceiver

– USB Device Charger detect (USBDCD)

– Two Controller Area Network (CAN) modules

– Three SPI modules

– Two I2C modules

– Six UART modules

– Secure Digital Host Controller (SDHC)

– Two I2S modules

K61 Sub-Family, Rev. 7, 02/2018

2

NXP Semiconductors

�Table of Contents

1 Ordering parts.......................................................................................5

6.2 System modules........................................................................... 29

1.1 Determining valid orderable parts............................................... 5

6.3 Clock modules............................................................................. 29

2 Part identification................................................................................. 5

6.3.1

MCG specifications..................................................... 29

2.1 Description...................................................................................5

6.3.2

Oscillator electrical specifications...............................32

2.2 Format.......................................................................................... 5

6.3.3

32 kHz oscillator electrical characteristics.................. 34

2.3 Fields............................................................................................5

6.4 Memories and memory interfaces................................................34

2.4 Example....................................................................................... 6

6.4.1

Flash (FTFE) electrical specifications.........................34

3 Terminology and guidelines.................................................................6

6.4.2

EzPort switching specifications...................................39

3.1 Definitions................................................................................... 6

6.4.3

NAND flash controller specifications......................... 40

3.2 Examples......................................................................................6

6.4.4

DDR controller specifications..................................... 43

3.3 Typical-value conditions..............................................................7

6.4.5

Flexbus switching specifications.................................46

3.4 Relationship between ratings and operating requirements.......... 7

3.5 Guidelines for ratings and operating requirements......................8

4 Ratings..................................................................................................8

6.5 Security and integrity modules.................................................... 48

6.5.1

DryIce Tamper Electrical Specifications.....................48

6.6 Analog..........................................................................................49

4.1 Thermal handling ratings............................................................. 8

6.6.1

ADC electrical specifications...................................... 49

4.2 Moisture handling ratings............................................................ 9

6.6.2

CMP and 6-bit DAC electrical specifications............. 56

4.3 ESD handling ratings................................................................... 9

6.6.3

12-bit DAC electrical characteristics...........................58

4.4 Voltage and current operating ratings..........................................9

6.6.4

Voltage reference electrical specifications..................61

5 General................................................................................................. 10

6.7 Timers.......................................................................................... 62

5.1 AC electrical characteristics........................................................ 10

6.8 Communication interfaces........................................................... 62

5.2 Nonswitching electrical specifications........................................ 10

6.8.1

Ethernet switching specifications................................ 62

5.2.1

Voltage and current operating requirements............... 10

6.8.2

USB electrical specifications.......................................65

5.2.2

LVD and POR operating requirements....................... 12

6.8.3

USB DCD electrical specifications............................. 65

5.2.3

Voltage and current operating behaviors.....................13

6.8.4

USB VREG electrical specifications...........................66

5.2.4

Power mode transition operating behaviors................ 16

6.8.5

ULPI timing specifications..........................................66

5.2.5

Power consumption operating behaviors.....................17

6.8.6

CAN switching specifications..................................... 67

5.2.6

EMC radiated emissions operating behaviors............. 20

6.8.7

DSPI switching specifications (limited voltage

5.2.7

Designing with radiated emissions in mind.................21

5.2.8

Capacitance attributes..................................................21

6.8.8

DSPI switching specifications (full voltage range)..... 69

5.3 Switching specifications.............................................................. 21

6.8.9

Inter-Integrated Circuit Interface (I2C) timing............71

range)...........................................................................67

5.3.1

Device clock specifications......................................... 21

6.8.10

UART switching specifications...................................72

5.3.2

General switching specifications.................................22

6.8.11

SDHC specifications................................................... 72

5.4 Thermal specifications................................................................. 24

6.8.12

I2S/SAI switching specifications................................ 73

5.4.1

Thermal operating requirements..................................24

5.4.2

Thermal attributes........................................................24

6.9 Human-machine interfaces (HMI)...............................................80

6.9.1

TSI electrical specifications........................................ 80

5.5 Power sequencing........................................................................ 25

7 Dimensions...........................................................................................81

6 Peripheral operating requirements and behaviors................................ 25

7.1 Obtaining package dimensions.................................................... 81

6.1 Core modules............................................................................... 25

8 Pinout................................................................................................... 81

6.1.1

Debug trace timing specifications............................... 25

8.1 Pins with active pull control after reset....................................... 81

6.1.2

JTAG electricals.......................................................... 26

8.2 K61 Signal Multiplexing and Pin Assignments...........................82

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

3

�8.3 K61 Pinouts..................................................................................91

9 Revision History...................................................................................92

K61 Sub-Family, Rev. 7, 02/2018

4

NXP Semiconductors

�Ordering parts

1 Ordering parts

1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part

numbers for this device, go to nxp.com and perform a part number search for the

following device numbers: PK61 and MK61

2 Part identification

2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the

values of these fields to determine the specific part you have received.

2.2 Format

Part numbers for this device have the following format:

Q K## A M FFF T PP CC N

2.3 Fields

This table lists the possible values for each field in the part number (not all combinations

are valid):

Field

Description

Values

Q

Qualification status

• M = Fully qualified, general market flow

• P = Prequalification

K##

Kinetis family

• K61

A

Key attribute

• F = Cortex-M4 w/ DSP and FPU

M

Flash memory type

• N = Program flash only

• X = Program flash and FlexMemory

FFF

Program flash memory size

• 512 = 512 KB

• 1M0 = 1 MB

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

5

�Terminology and guidelines

Field

Description

Values

T

Temperature range (°C)

• V = –40 to 105

• C = –40 to 85

PP

Package identifier

• MJ = 256 MAPBGA (17 mm x 17 mm)

CC

Maximum CPU frequency (MHz)

• 15 = 150 MHz

N

Packaging type

• R = Tape and reel

• (Blank) = Trays

2.4 Example

This is an example part number:

MK61FN1M0VMJ15

3 Terminology and guidelines

3.1 Definitions

Key terms are defined in the following table:

Term

Rating

Definition

A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent

chip failure:

• Operating ratings apply during operation of the chip.

• Handling ratings apply when the chip is not powered.

NOTE: The likelihood of permanent chip failure increases rapidly as soon as a characteristic

begins to exceed one of its operating ratings.

Operating requirement

A specified value or range of values for a technical characteristic that you must guarantee during

operation to avoid incorrect operation and possibly decreasing the useful life of the chip

Operating behavior

A specified value or range of values for a technical characteristic that are guaranteed during

operation if you meet the operating requirements and any other specified conditions

Typical value

A specified value for a technical characteristic that:

• Lies within the range of values specified by the operating behavior

• Is representative of that characteristic during operation when you meet the typical-value

conditions or other specified conditions

NOTE: Typical values are provided as design guidelines and are neither tested nor guaranteed.

K61 Sub-Family, Rev. 7, 02/2018

6

NXP Semiconductors

�Terminology and guidelines

3.2 Examples

EX

A

M

PL

E

Operating rating:

EX

AM

PL

E

Operating requirement:

EX

AM

PL

E

Operating behavior that includes a typical value:

3.3 Typical-value conditions

Typical values assume you meet the following conditions (or other conditions as

specified):

Symbol

Description

Value

Unit

TA

Ambient temperature

25

°C

VDD

Supply voltage

3.3

V

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

7

�Ratings

3.4 Relationship between ratings and operating requirements

e

Op

ing

rat

r

(

ng

ati

n.

mi

)

ing

rat

e

Op

e

re

ir

qu

)

in.

t (m

n

me

ing

rat

e

Op

e

ir

qu

re

t (m

n

me

ax

.)

ing

rat

e

Op

(m

ng

ati

.)

ax

r

Fatal range

Degraded operating range

Normal operating range

Degraded operating range

Fatal range

Expected permanent failure

- No permanent failure

- Possible decreased life

- Possible incorrect operation

- No permanent failure

- Correct operation

- No permanent failure

- Possible decreased life

- Possible incorrect operation

Expected permanent failure

–∞

∞

Operating (power on)

ng

dli

n

Ha

n.)

mi

g(

in

rat

ma

g(

ng

dli

n

Ha

in

rat

x.)

Fatal range

Handling range

Fatal range

Expected permanent failure

No permanent failure

Expected permanent failure

–∞

∞

Handling (power off)

3.5 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

• Never exceed any of the chip’s ratings.

• During normal operation, don’t exceed any of the chip’s operating requirements.

• If you must exceed an operating requirement at times other than during normal

operation (for example, during power sequencing), limit the duration as much as

possible.

4 Ratings

4.1 Thermal handling ratings

Symbol

Description

Min.

Max.

Unit

Notes

TSTG

Storage temperature

–55

150

°C

1

TSDR

Solder temperature, lead-free

—

260

°C

2

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

K61 Sub-Family, Rev. 7, 02/2018

8

NXP Semiconductors

�Ratings

4.2 Moisture handling ratings

Symbol

MSL

Description

Moisture sensitivity level

Min.

Max.

Unit

Notes

—

3

—

1

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

4.3 ESD handling ratings

Symbol

Description

Min.

Max.

Unit

Notes

VHBM

Electrostatic discharge voltage, human body model

-2000

+2000

V

1

VCDM

Electrostatic discharge voltage, charged-device model

-500

+500

V

2

Latch-up current at ambient temperature of 105°C

-100

+100

mA

3

ILAT

1. Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human Body

Model (HBM).

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for

Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

4.4 Voltage and current operating ratings

Symbol

Description

Min.

Max.

Unit

Digital supply voltage1

–0.3

3.8

V

VDD_INT

Core supply voltage

–0.3

3.8

V

VDD_DDR

DDR I/O supply voltage

–0.3

3.8

V

Digital supply current

—

300

mA

IDD_INT

Core supply current

—

185

mA

IDD_DDR

DDR supply current

—

220

mA

Digital input voltage (except RESET, EXTAL0/XTAL0, and

EXTAL1/XTAL1) 2

–0.3

5.5

V

DDR input voltage

–0.3

VDD_DDR + 0.3

V

Analog3, RESET, EXTAL0/XTAL0, and EXTAL1/XTAL1 input

voltage

–0.3

VDD + 0.3

V

Maximum current single pin limit (applies to all digital pins)

–25

25

mA

VDD – 0.3

VDD + 0.3

V

VDD

IDD

VDIO

VDDDR

VAIO

ID

VDDA

Analog supply voltage

VUSB0_DP

USB0_DP input voltage

–0.3

3.63

V

VUSB1_DP

USB1_DP input voltage

–0.3

3.63

V

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

9

�General

Symbol

Description

Min.

Max.

Unit

VUSB0_DM

USB0_DM input voltage

–0.3

3.63

V

VUSB1_DM

USB1_DM input voltage

–0.3

3.63

V

VREGIN

USB regulator input

–0.3

6.0

V

RTC battery supply voltage

–0.3

3.8

V

VBAT

1. It applies for all port pins except Tamper pins.

2. It covers digital pins except Tamper pins and DDR pins.

3. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

5 General

5.1 AC electrical characteristics

Unless otherwise specified, propagation delays are measured from the 50% to the 50%

point, and rise and fall times are measured at the 20% and 80% points, as shown in the

following figure.

VIH

Input Signal

High

Low

80%

50%

20%

Midpoint1

Fall Time

VIL

Rise Time

The midpoint is VIL + (VIH - VIL) / 2

Figure 1. Input signal measurement reference

All digital I/O switching characteristics assume:

1. output pins

• have CL=30pF loads,

• are configured for fast slew rate (PORTx_PCRn[SRE]=0), and

• are configured for high drive strength (PORTx_PCRn[DSE]=1)

2. input pins

• have their passive filter disabled (PORTx_PCRn[PFE]=0)

5.2 Nonswitching electrical specifications

K61 Sub-Family, Rev. 7, 02/2018

10

NXP Semiconductors

�General

5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

Symbol

Description

Min.

Max.

Unit

VDD

Supply voltage

max [VDD_DDR, 1.71 V]

3.6

V

1.71

VDD

V

• DDR1

2.3

2.7

V

• DDR2/LPDDR1

1.71

1.9

V

0.49 × VDD_DDR

VDD_DDR

V

1.71

3.6

V

VDD – VDDA VDD-to-VDDA differential voltage

–0.1

0.1

V

VSS – VSSA VSS-to-VSSA differential voltage

–0.1

0.1

V

1.71

3.6

V

0.7 × VDD

—

V

0.75 × VDD

—

V

—

0.35 × VDD

V

—

0.3 × VDD

V

VREF_DDR + 0.15

—

V

VREF_DDR + 0.125

—

V

0.7 × VDD_DDR

—

V

—

VREF_DDR – 0.15

V

—

VREF_DDR – 0.125

V

VDD_INT

Core supply voltage

VDD_DDR

DDR voltage — memory I/O buffers

VREF_DDR

VDDA

VBAT

VIH

Input reference voltage (DDR1/DDR2/

LPDDR1)

Analog supply voltage

RTC battery supply voltage

Input high voltage (digital pins except

Tamper pins and DDR pins)

• 2.7 V ≤ VDD ≤ 3.6 V

• 1.7 V ≤ VDD ≤ 2.7 V

VIL

Input low voltage (digital pins except Tamper

pins and DDR pins)

• 2.7 V ≤ VDD ≤ 3.6 V

• 1.7 V ≤ VDD ≤ 2.7 V

VIH_DDR

Input high voltage (DDR pins)

• DDR1

• DDR2

• LPDDR1

VIL_DDR

Input low voltage (DDR pins)

• DDR1

• DDR2

• LPDDR1

VHYS

Input hysteresis (digital pins except Tamper

pins and DDR pins)

IICDIO

Digital pin (except Tamper pins) negative DC

injection current — single pin

—

0.3 × VDD_DDR

V

0.06 × VDD

—

V

-5

—

mA

Notes

1

2

• VIN < VSS-0.3V

IICAIO

Analog3, EXTAL0/XTAL0, and EXTAL1/

XTAL1 pin DC injection current — single pin

• VIN < VSS-0.3V (Negative current

injection)

• VIN > VDD+0.3V (Positive current

injection)

4

mA

-5

—

—

+5

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

11

�General

Table 1. Voltage and current operating requirements (continued)

Symbol

IICcont

Description

Contiguous pin DC injection current —

regional limit, includes sum of negative

injection currents or sum of positive injection

currents of 16 contiguous pins

• Negative current injection

Min.

Max.

-25

—

—

+25

Unit

Notes

mA

• Positive current injection

VODPU

Open drain pullup voltage level

VDD

VDD

V

VRAM

VDD (VDD_INT) voltage required to retain RAM

1.2

—

V

VPOR_VBAT

—

V

VRFVBAT

VBAT voltage required to retain the VBAT

register file

5

1. For DDR1/DDR2, connect VREF_DDR to the same reference voltage used for the memory. For LPDDR1, connect VREF_DDR

to the VDD_DDR voltage.

2. All 5 V tolerant digital I/O pins are internally clamped to VSS through an ESD protection diode. There is no diode

connection to VDD. If VIN is less than VDIO_MIN, a current limiting resistor is required. If VIN greater than VDIO_MIN

(=VSS-0.3V) is observed, then there is no need to provide current limiting resistors at the pads. The negative DC injection

current limiting resistor is calculated as R=(VDIO_MIN-VIN)/|IICDIO|.

3. Analog pins are defined as pins that do not have an associated general purpose I/O port function. Additionally, EXTAL and

XTAL are analog pins.

4. All analog pins are internally clamped to VSS and VDD through ESD protection diodes. If VIN is less than VAIO_MIN or greater

than VAIO_MAX, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as

R=(VAIO_MIN-VIN)/|IICAIO|. The positive injection current limiting resistor is calculated as R=(VIN-VAIO_MAX)/|IICAIO|. Select the

larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

5. Open drain outputs must be pulled to VDD.

5.2.2 LVD and POR operating requirements

Table 2. LVD and POR operating requirements

Symbol

Description

Min.

Typ.

Max.

Unit

VPOR

Falling VDD POR detect voltage

0.8

1.1

1.5

V

VLVDH

Falling low-voltage detect threshold — high

range (LVDV=01)

2.48

2.56

2.64

V

2.62

2.70

2.78

V

2.72

2.80

2.88

V

2.82

2.90

2.98

V

2.92

3.00

3.08

V

—

±80

—

mV

1.54

1.60

1.66

V

1.74

1.80

1.86

V

1.84

1.90

1.96

V

VLVW1H

VLVW2H

VLVW3H

VLVW4H

Low-voltage warning thresholds — high range

• Level 1 falling (LVWV=00)

• Level 2 falling (LVWV=01)

• Level 3 falling (LVWV=10)

Low-voltage inhibit reset/recover hysteresis —

high range

VLVDL

Falling low-voltage detect threshold — low range

(LVDV=00)

VLVW2L

1

• Level 4 falling (LVWV=11)

VHYSH

VLVW1L

Notes

Low-voltage warning thresholds — low range

• Level 1 falling (LVWV=00)

1

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

12

NXP Semiconductors

�General

Table 2. LVD and POR operating requirements (continued)

Symbol

Description

Min.

Typ.

Max.

Unit

VLVW3L

• Level 2 falling (LVWV=01)

1.94

2.00

2.06

V

VLVW4L

• Level 3 falling (LVWV=10)

2.04

2.10

2.16

V

—

±60

—

mV

Notes

• Level 4 falling (LVWV=11)

VHYSL

Low-voltage inhibit reset/recover hysteresis —

low range

VBG

Bandgap voltage reference

0.97

1.00

1.03

V

tLPO

Internal low power oscillator period

900

1000

1100

μs

factory trimmed

1. Rising thresholds are falling threshold + hysteresis voltage

Table 3. VBAT power operating requirements

Symbol

Description

VPOR_VBAT Falling VBAT supply POR detect voltage

Min.

Typ.

Max.

Unit

0.8

1.1

1.5

V

Notes

5.2.3 Voltage and current operating behaviors

Table 4. Voltage and current operating behaviors

Symbol

Min.

Typ.

• 2.7 V ≤ VDD ≤ 3.6 V, IOH = -9mA

VDD – 0.5

—

• 1.71 V ≤ VDD ≤ 2.7 V, IOH = -3mA

VDD – 0.5

—

• 2.7 V ≤ VDD ≤ 3.6 V, IOH = -2mA

VDD – 0.5

—

• 1.71 V ≤ VDD ≤ 2.7 V, IOH = -0.6mA

VDD – 0.5

—

Output high current total for all ports

—

—

100

mA

IOHT_io60

Output high current total for fast digital ports

—

—

100

mA

VOH_DDR

Output high voltage for DDR pins

VDD_DDR 0.36

—

—

V

—

—

V

—

—

V

—

—

V

—

—

V

VOH

Description

Output high voltage — high drive strength

• DDR1 (IOH = -16.2 mA)

• DDR2 half strength (IOH = -5.36 mA)

• DDR2 full strength (IOH = -13.4 mA)

• LPDDR1 half strength (IOH = -0.1 mA)

• LPDDR1 full strength (IOH = -0.1 mA)

Unit

Notes

—

Output high voltage — low drive strength

IOHT

Max.

—

V

V

—

VDD_DDR 0.28

VDD_DDR 0.28

—

V

V

0.9 x

VDD_DDR

0.9 x

VDD_DDR

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

13

�General

Table 4. Voltage and current operating behaviors (continued)

Symbol

Description

IOHT_DDR

Output high current total for DDR pins

• DDR1

• DDR2

Min.

Typ.

Max.

Unit

—

—

100

mA

—

—

56

mA

—

—

39

mA

VBAT – 0.5

—

—

V

VBAT – 0.5

—

—

V

VBAT – 0.5

—

—

V

VBAT – 0.5

—

—

V

—

—

100

mA

0.5

V

0.5

V

0.5

V

0.5

V

Notes

• LPDDR1

VOH_Tamper Output high voltage — high drive strength

• 2.7 V ≤ VBAT ≤ 3.6 V, IOH = -10mA

• 1.71 V ≤ VBAT ≤ 2.7 V, IOH = -3mA

Output high voltage — low drive strength

• 2.7 V ≤ VBAT ≤ 3.6 V, IOH = -2mA

• 1.71 V ≤ VBAT ≤ 2.7 V, IOH = -0.6mA

IOH_Tamper Output high current total for Tamper pins

VOL

Output low voltage — high drive strength

—

• 2.7 V ≤ VDD ≤ 3.6 V, IOL = 10 mA

—

• 1.71 V ≤ VDD ≤ 2.7 V, IOL = 5 mA

—

Output low voltage — low drive strength

IOLT

—

—

• 2.7 V ≤ VDD ≤ 3.6 V, IOL = 2 mA

—

• 1.71 V ≤ VDD ≤ 2.7 V, IOL = 1 mA

—

—

Output low current total for all ports

—

—

100

mA

IOLT_io60

Output low current total for fast digital ports

—

—

100

mA

VOL_DDR

Output low voltage for DDR pins

—

—

0.37

V

• DDR1 (IOL = 16.2 mA)

—

—

0.28

V

• DDR2 half strength (IOL = 5.36 mA)

—

—

0.28

V

• DDR2 full strength (IOL = 13.4 mA)

—

—

—

—

0.1 x

VDD_DDR

V

• LPDDR1 half strength (IOL = 0.1 mA)

• LPDDR1 full strength (IOL = 0.1 mA)

IOLT_DDR

Output low current total for DDR pins

V

0.1 x

VDD_DDR

—

—

• DDR1

• DDR2

100

mA

56

mA

39

mA

• LPDDR1

VOL_Tamper Output low voltage — high drive strength

• 2.7 V ≤ VBAT ≤ 3.6 V, IOL = 10mA

—

—

0.5

V

—

—

0.5

V

—

—

0.5

V

—

—

0.5

V

• 1.71 V ≤ VBAT ≤ 2.7 V, IOL = 3mA

Output low voltage — low drive strength

• 2.7 V ≤ VBAT ≤ 3.6 V, IOL = 2mA

• 1.71 V ≤ VBAT ≤ 2.7 V, IOL = 0.6mA

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

14

NXP Semiconductors

�General

Table 4. Voltage and current operating behaviors (continued)

Symbol

Description

IOL_Tamper Output low current total for Tamper pins

IINA

Min.

Typ.

Max.

Unit

—

—

100

mA

Input leakage current, analog pins and digital

pins configured as analog inputs

Notes

1, 2

• VSS ≤ VIN ≤ VDD

• All pins except EXTAL32, XTAL32,

EXTAL, XTAL

• EXTAL (PTA18) and XTAL (PTA19)

• EXTAL32, XTAL32

IIND

—

0.002

0.5

μA

—

0.004

1.5

μA

—

0.075

10

μA

Input leakage current, digital pins

2, 3

• VSS ≤ VIN ≤ VIL

• All digital pins

—

0.002

0.5

μA

—

0.002

0.5

μA

—

0.004

1

μA

• VIN = VDD

• All digital pins except PTD7

• PTD7

IIND

Input leakage current, digital pins

2, 3, 4

• VIL < VIN < VDD

IIND

• VDD = 3.6 V

—

18

26

μA

• VDD = 3.0 V

—

12

19

μA

• VDD = 2.5 V

—

8

13

μA

• VDD = 1.7 V

—

3

6

μA

Input leakage current, digital pins

• VDD < VIN < 5.5 V

ZIND

2, 3

—

1

50

μA

Input impedance examples, digital pins

2, 5

• VDD = 3.6 V

—

—

48

kΩ

• VDD = 3.0 V

—

—

55

kΩ

• VDD = 2.5 V

—

—

57

kΩ

• VDD = 1.7 V

—

—

85

kΩ

IIN_DDR

Input leakage current (per DDR pin) for full

temperature range

—

—

1

μA

IIN_DDR

Input leakage current (per DDR pin) at 25°C

—

—

0.025

μA

IIN_Tamper

Input leakage current (per Tamper pin) for full

temperature range

—

—

1

μA

IIN_Tamper

Input leakage current (per Tamper pin) at 25°C

—

—

0.025

μA

RPU

Internal pullup resistors (except Tamper pins)

20

—

50

kΩ

6

RPD

Internal pulldown resistors (except Tamper pins)

20

—

50

kΩ

7

RODT

On-die termination (ODT) resistance for DDR2

60

—

90

Ω

120

—

180

Ω

• Rtt1(eff) - 75 Ω

• Rtt2(eff) - 150 Ω

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

15

�General

1.

2.

3.

4.

5.

Analog pins are defined as pins that do not have an associated general purpose I/O port function.

Digital pins have an associated GPIO port function and have 5V tolerant inputs, except EXTAL and XTAL.

Internal pull-up/pull-down resistors disabled.

Characterized, not tested in production.

Examples calculated using VIL relation, VDD, and max IIND: ZIND=VIL/IIND. This is the impedance needed to pull a high

signal to a level below VIL due to leakage when VIL < VIN < VDD. These examples assume signal source low = 0 V. See

Figure 2.

6. Measured at VDD supply voltage = VDD min and Vinput = VSS

7. Measured at VDD supply voltage = VDD min and Vinput = VDD

Figure 2. 5 V Tolerant Input IIND Parameter

5.2.4 Power mode transition operating behaviors

All specifications except tPOR, and VLLSx→RUN recovery times in the following table

assume this clock configuration:

•

•

•

•

•

CPU and system clocks = 100 MHz

Bus clock = 50 MHz

FlexBus clock = 50 MHz

Flash clock = 25 MHz

MCG mode: FEI

Table 5. Power mode transition operating behaviors

Symbol

tPOR

Description

Min.

Max.

After a POR event, amount of time from the point VDD

reaches 1.71 V to execution of the first instruction

across the operating temperature range of the chip.

• VDD slew rate ≥ 5.7 kV/s

• VDD slew rate < 5.7 kV/s

• VLLS1 → RUN

• VLLS2 → RUN

Unit

Notes

1

μs

—

300

—

1.7 V / (VDD

slew rate)

—

160

μs

—

114

μs

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

16

NXP Semiconductors

�General

Table 5. Power mode transition operating behaviors (continued)

Symbol

Description

• VLLS3 → RUN

• LLS → RUN

• VLPS → RUN

• STOP → RUN

Min.

Max.

Unit

—

114

μs

—

5.0

μs

—

5

μs

—

4.8

μs

Notes

1. Normal boot (FTFE_FOPT[LPBOOT]=1)

5.2.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

Symbol

IDDA

IDD_RUN

IDD_RUN

Description

Analog supply current

Min.

Typ.

Max.

Unit

Notes

—

—

See note

mA

1

Run mode current — all peripheral clocks

disabled, code executing from flash

2

• @ 1.8V

—

58.01

83.95

mA

• @ 3.0V

—

57.93

84.14

mA

Run mode current — all peripheral clocks

enabled, code executing from flash

3

• @ 1.8V

—

89.26

116.53

mA

• @ 3.0V

—

89.23

117.26

mA

IDD_WAIT

Wait mode high frequency current at 3.0 V — all

peripheral clocks disabled

—

40.18

65.25

mA

2

IDD_WAIT

Wait mode reduced frequency current at 3.0 V —

all peripheral clocks disabled

—

18.08

42.96

mA

4

IDD_STOP

Stop mode current at 3.0 V

• @ –40 to 25°C

—

1.25

1.62

mA

• @ 70°C

—

2.93

4.39

mA

• @ 105°C

—

7.08

10.74

mA

IDD_VLPR

Very-low-power run mode current at 3.0 V — all

peripheral clocks disabled

—

1.03

4.48

mA

5

IDD_VLPR

Very-low-power run mode current at 3.0 V — all

peripheral clocks enabled

—

1.58

4.96

mA

5

IDD_VLPW

Very-low-power wait mode current at 3.0 V

—

0.64

4.29

mA

5

IDD_VLPS

Very-low-power stop mode current at 3.0 V

—

0.22

0.38

mA

—

0.78

1.33

mA

• @ –40 to 25°C

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

17

�General

Table 6. Power consumption operating behaviors (continued)

Symbol

Description

Min.

Typ.

Max.

Unit

—

2.18

3.56

mA

• @ –40 to 25°C

—

0.22

0.37

mA

• @ 70°C

—

0.78

1.33

mA

• @ 105°C

—

2.16

3.52

mA

• @ –40 to 25°C

—

4.09

5.58

μA

• @ 70°C

—

20.98

28.93

μA

• @ 105°C

—

84.95

111.15

μA

• @ –40 to 25°C

—

2.68

4.22

μA

• @ 70°C

—

8.8

10.74

μA

• @ 105°C

—

37.28

43.61

μA

• @ –40 to 25°C

—

2.46

4.02

μA

• @ 70°C

—

7.04

8.99

μA

• @ 105°C

—

30.68

37.04

μA

• @ 70°C

Notes

• @ 105°C

IDD_LLS

IDD_VLLS3

IDD_VLLS2

IDD_VLLS1

IDD_VBAT

Low leakage stop mode current at 3.0 V

Very low-leakage stop mode 3 current at 3.0 V

Very low-leakage stop mode 2 current at 3.0 V

Very low-leakage stop mode 1 current at 3.0 V

Average current when CPU is not accessing

RTC registers at 3.0 V

6

• @ –40 to 25°C

—

0.89

1.10

μA

• @ 70°C

—

1.28

1.85

μA

• @ 105°C

—

3.10

4.30

μA

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See

each module's specification for its supply current.

2. 150 MHz core and system clock, 75 MHz bus, 50 MHz FlexBus clock, and 25 MHz flash clock. MCG configured for PEE

mode. All peripheral clocks disabled.

3. 150 MHz core and system clock, 75 MHz bus, 50 MHz FlexBus clock, and 25 MHz flash clock. MCG configured for PEE

mode. All peripheral clocks enabled, but peripherals are not in active operation.

4. 25 MHz core and system clock, 25 MHz bus clock, and 12.5 MHz FlexBus and flash clock. MCG configured for FEI mode.

5. 4 MHz core, system, 2 MHz FlexBus, and 2 MHz bus clock and 0.5 MHz flash clock. MCG configured for BLPE mode. All

peripheral clocks disabled.

6. Includes 32kHz oscillator current and RTC operation.

5.2.5.1

Diagram: Typical IDD_RUN operating behavior

The following data was measured under these conditions:

• MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater

than 50 MHz frequencies. MCG in PEE mode at greater than 100 MHz frequencies.

K61 Sub-Family, Rev. 7, 02/2018

18

NXP Semiconductors

�General

•

•

•

•

USB regulator disabled

No GPIOs toggled

Code execution from flash with cache enabled

For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 3. Run mode supply current vs. core frequency

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

19

�General

Figure 4. VLPR mode supply current vs. core frequency

5.2.6 EMC radiated emissions operating behaviors

Table 7. EMC radiated emissions operating behaviors for 256MAPBGA

Symbol

Description

Frequency

band (MHz)

Typ.

Unit

Notes

1, 2, 3

VRE1

Radiated emissions voltage, band 1

0.15–50

21

dBμV

VRE2

Radiated emissions voltage, band 2

50–150

24

dBμV

VRE3

Radiated emissions voltage, band 3

150–500

29

dBμV

VRE4

Radiated emissions voltage, band 4

500–1000

28

dBμV

1. Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150

kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of

Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband

TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported

emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the

measured orientations in each frequency range.

2. VDD = 3.3 V, TA = 25 °C, fOSC = 12 MHz (crystal), fSYS = 72 MHz, fBUS = 72 MHz

3. Determined according to IEC Standard JESD78, IC Latch-Up Test

K61 Sub-Family, Rev. 7, 02/2018

20

NXP Semiconductors

�General

5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize

interference from radiated emissions:

1. Go to www.nxp.com.

2. Perform a keyword search for “EMC design.”

5.2.8 Capacitance attributes

Table 8. Capacitance attributes

Symbol

Description

Min.

Max.

Unit

CIN_A

Input capacitance: analog pins

—

7

pF

CIN_D

Input capacitance: digital pins

—

7

pF

Input capacitance: fast digital pins

—

9

pF

CIN_D_io60

5.3 Switching specifications

5.3.1 Device clock specifications

Table 9. Device clock specifications

Symbol

Description

Min.

Max.

Unit

System and core clock

—

150

MHz

fSYS_USBFS

System and core clock when Full Speed USB in

operation

20

—

MHz

fSYS_USBHS

System and core clock when High Speed USB in

operation

60

—

MHz

fENET

System and core clock when ethernet in operation

Notes

Normal run mode

fSYS

• 10 Mbps

• 100 Mbps

MHz

5

—

50

—

Bus clock

—

75

MHz

FlexBus clock

—

50

MHz

fFLASH

Flash clock

—

25

MHz

fDDR

DDR clock

—

150

MHz

—

25

MHz

fBUS

FB_CLK

fLPTMR

LPTMR clock

VLPR

mode1

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

21

�General

Table 9. Device clock specifications (continued)

Symbol

Description

Min.

Max.

Unit

fSYS

System and core clock

—

4

MHz

fBUS

Bus clock

—

4

MHz

FlexBus clock

—

4

MHz

fFLASH

Flash clock

—

0.5

MHz

fLPTMR

LPTMR clock

—

4

MHz

FB_CLK

Notes

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any

other module.

5.3.2 General switching specifications

These general purpose specifications apply to all pins configured for:

• GPIO signaling

• Other peripheral module signaling not explicitly stated elsewhere

Table 10. General switching specifications

Symbol

Description

Min.

Max.

Unit

Notes

GPIO pin interrupt pulse width (digital glitch filter

disabled) — Synchronous path

1.5

—

Bus clock

cycles

1, 2

GPIO pin interrupt pulse width (digital glitch filter

disabled, analog filter enabled) — Asynchronous path

100

—

ns

3

GPIO pin interrupt pulse width (digital glitch filter

disabled, analog filter disabled) — Asynchronous path

16

—

ns

3

External reset pulse width (digital glitch filter disabled)

100

—

ns

3

2

—

Bus clock

cycles

Mode select (EZP_CS) hold time after reset

deassertion

Port rise and fall time (high drive strength)

4

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

14

ns

• 2.7 ≤ VDD ≤ 3.6V

—

8

ns

• 1.71 ≤ VDD ≤ 2.7V

—

36

ns

• 2.7 ≤ VDD ≤ 3.6V

—

24

ns

• Slew enabled

Port rise and fall time (low drive strength)

5

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

14

ns

• 2.7 ≤ VDD ≤ 3.6V

—

8

ns

—

36

ns

• Slew enabled

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

22

NXP Semiconductors

�General

Table 10. General switching specifications (continued)

Symbol

Description

• 1.71 ≤ VDD ≤ 2.7V

Min.

Max.

Unit

—

24

ns

Notes

• 2.7 ≤ VDD ≤ 3.6V

tio50

Port rise and fall time (high drive strength)

6

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

7

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

3

ns

—

• 1.71 ≤ VDD ≤ 2.7V

—

28

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

14

ns

—

• Slew enabled

tio50

Port rise and fall time (low drive strength)

-1

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

18

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

9

ns

—

• 1.71 ≤ VDD ≤ 2.7V

—

48

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

24

ns

—

• Slew enabled

tio60

Port rise and fall time (high drive strength)

6

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

6

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

3

ns

—

• 1.71 ≤ VDD ≤ 2.7V

—

28

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

14

ns

—

• Slew enabled

tio60

Port rise and fall time (low drive strength)

-1

• Slew disabled

• 1.71 ≤ VDD ≤ 2.7V

—

18

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

6

ns

—

• 1.71 ≤ VDD ≤ 2.7V

—

48

ns

—

• 2.7 ≤ VDD ≤ 3.6V

—

24

ns

—

• Slew enabled

1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or

may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be

recognized in that case.

2. The greater synchronous and asynchronous timing must be met.

3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and

VLLSx modes.

4. 75 pF load

5. 15 pF load

6. 25 pF load

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

23

�General

5.4 Thermal specifications

5.4.1 Thermal operating requirements

Table 11. Thermal operating requirements

Symbol

TJ

TA

Description

Min.

Max.

Unit

Die junction temperature

–40

125

°C

–40

105

°C

Ambient

temperature1

1. Maximum TA can be exceeded only if the user ensures that TJ does not exceed maximum TJ. The simplest method to

determine TJ is:

TJ = TA + RθJA x chip power dissipation

5.4.2 Thermal attributes

Board type

Symbol

Description

256 MAPBGA

Unit

Notes

Single-layer (1s)

RθJA

Thermal

43

resistance, junction

to ambient (natural

convection)

°C/W

1, 2

Four-layer (2s2p)

RθJA

Thermal

28

resistance, junction

to ambient (natural

convection)

°C/W

1,2, 3

Single-layer (1s)

RθJMA

Thermal

36

resistance, junction

to ambient (200 ft./

min. air speed)

°C/W

1,3

Four-layer (2s2p)

RθJMA

Thermal

25

resistance, junction

to ambient (200 ft./

min. air speed)

°C/W

1,3

—

RθJB

Thermal

17

resistance, junction

to board

°C/W

4

—

RθJC

Thermal

8

resistance, junction

to case

°C/W

5

—

ΨJT

Thermal

2

characterization

parameter, junction

to package top

outside center

(natural

convection)

°C/W

6

K61 Sub-Family, Rev. 7, 02/2018

24

NXP Semiconductors

�Peripheral operating requirements and behaviors

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site

(board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board

thermal resistance.

2. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions

—Natural Convection (Still Air) with the single layer board horizontal. Board meets JESD51-9 specification.

3. Determined according to JEDEC Standard JESD51-6, Integrated Circuits Thermal Test Method Environmental Conditions

—Forced Convection (Moving Air) with the board horizontal.

4. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions

—Junction-to-Board. Board temperature is measured on the top surface of the board near the package.

5. Determined according to Method 1012.1 of MIL-STD 883, Test Method Standard, Microcircuits, with the cold plate

temperature used for the case temperature. The value includes the thermal resistance of the interface material between

the top of the package and the cold plate.

6. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions

—Natural Convection (Still Air).

5.5 Power sequencing

Voltage supplies must be sequenced in the proper order to avoid damaging internal

diodes. There is no limit on how long after one supply powers up before the next supply

must power up. Note that VDD and VDD_INT can use the same power source.

The power-up sequence is:

1. VDD/VDDA

2. VDD_INT

3. VDD_DDR

The power-down sequence is the reverse:

1. VDD_DDR

2. VDD_INT

3. VDD/VDDA

6 Peripheral operating requirements and behaviors

6.1 Core modules

6.1.1 Debug trace timing specifications

Table 12. Debug trace operating behaviors

Symbol

Description

Tcyc

Clock period

Twl

Low pulse width

Min.

Max.

Unit

Frequency dependent

MHz

2

—

ns

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

25

�Peripheral operating requirements and behaviors

Table 12. Debug trace operating behaviors (continued)

Symbol

Min.

Max.

Unit

High pulse width

2

—

ns

Tr

Clock and data rise time

—

3

ns

Tf

Clock and data fall time

—

3

ns

Ts

Data setup

3

—

ns

Th

Data hold

2

—

ns

Twh

Description

TRACECLK

Tr

Tf

Twh

Twl

Tcyc

Figure 5. TRACE_CLKOUT specifications

TRACE_CLKOUT

Ts

Th

Ts

Th

TRACE_D[3:0]

Figure 6. Trace data specifications

6.1.2 JTAG electricals

Table 13. JTAG limited voltage range electricals

Symbol

J1

Description

Min.

Max.

Unit

Operating voltage

2.7

3.6

V

TCLK frequency of operation

MHz

• Boundary Scan

0

10

• JTAG and CJTAG

0

25

• Serial Wire Debug

0

50

1/J1

—

ns

50

—

ns

20

—

ns

J2

TCLK cycle period

J3

TCLK clock pulse width

• Boundary Scan

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

26

NXP Semiconductors

�Peripheral operating requirements and behaviors

Table 13. JTAG limited voltage range electricals (continued)

Symbol

Description

• JTAG and CJTAG

Min.

Max.

Unit

10

—

ns

• Serial Wire Debug

J4

TCLK rise and fall times

—

3

ns

J5

Boundary scan input data setup time to TCLK rise

20

—

ns

J6

Boundary scan input data hold time after TCLK rise

2.4

—

ns

J7

TCLK low to boundary scan output data valid

—

25

ns

J8

TCLK low to boundary scan output high-Z

—

25

ns

J9

TMS, TDI input data setup time to TCLK rise

8

—

ns

J10

TMS, TDI input data hold time after TCLK rise

1

—

ns

J11

TCLK low to TDO data valid

—

17

ns

J12

TCLK low to TDO high-Z

—

17

ns

J13

TRST assert time

100

—

ns

J14

TRST setup time (negation) to TCLK high

8

—

ns

Table 14. JTAG full voltage range electricals

Symbol

J1

Description

Min.

Max.

Unit

Operating voltage

1.71

3.6

V

TCLK frequency of operation

MHz

• Boundary Scan

0

10

• JTAG and CJTAG

0

20

• Serial Wire Debug

0

40

1/J1

—

ns

• Boundary Scan

50

—

ns

• JTAG and CJTAG

25

—

ns

• Serial Wire Debug

12.5

—

ns

J2

TCLK cycle period

J3

TCLK clock pulse width

J4

TCLK rise and fall times

—

3

ns

J5

Boundary scan input data setup time to TCLK rise

20

—

ns

J6

Boundary scan input data hold time after TCLK rise

2.4

—

ns

J7

TCLK low to boundary scan output data valid

—

25

ns

J8

TCLK low to boundary scan output high-Z

—

25

ns

J9

TMS, TDI input data setup time to TCLK rise

8

—

ns

J10

TMS, TDI input data hold time after TCLK rise

1.4

—

ns

J11

TCLK low to TDO data valid

—

22.1

ns

J12

TCLK low to TDO high-Z

—

22.1

ns

J13

TRST assert time

100

—

ns

J14

TRST setup time (negation) to TCLK high

8

—

ns

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

27

�Peripheral operating requirements and behaviors

J2

J3

J3

TCLK (input)

J4

J4

Figure 7. Test clock input timing

TCLK

J5

Data inputs

J6

Input data valid

J7

Data outputs

Output data valid

J8

Data outputs

J7

Data outputs

Output data valid

Figure 8. Boundary scan (JTAG) timing

K61 Sub-Family, Rev. 7, 02/2018

28

NXP Semiconductors

�Peripheral operating requirements and behaviors

TCLK

J9

TDI/TMS

J10

Input data valid

J11

TDO

Output data valid

J12

TDO

J11

TDO

Output data valid

Figure 9. Test Access Port timing

TCLK

J14

J13

TRST

Figure 10. TRST timing

6.2 System modules

There are no specifications necessary for the device's system modules.

6.3 Clock modules

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

29

�Peripheral operating requirements and behaviors

6.3.1 MCG specifications

Table 15. MCG specifications

Symbol

Description

Min.

Typ.

Max.

Unit

—

32.768

—

kHz

31.25

—

39.0625

kHz

Δfdco_res_t Resolution of trimmed average DCO output

frequency at fixed voltage and temperature —

using SCTRIM and SCFTRIM

—

± 0.3

± 0.6

%fdco

1

Δfdco_res_t Resolution of trimmed average DCO output

frequency at fixed voltage and temperature —

using SCTRIM only

—

± 0.2

± 0.5

%fdco

1

Total deviation of trimmed average DCO output

frequency over fixed voltage and temperature

range of 0–70°C

—

± 4.5

—

%fdco

1

fintf_ft

Internal reference frequency (fast clock) —

factory trimmed at nominal VDD and 25°C

—

4

—

MHz

fintf_t

Internal reference frequency (fast clock) — user

trimmed at nominal VDD and 25 °C

3

—

5

MHz

fints_ft

Internal reference frequency (slow clock) —

factory trimmed at nominal VDD and 25 °C

fints_t

Internal reference frequency (slow clock) — user

trimmed

Δfdco_t

floc_low

Loss of external clock minimum frequency —

RANGE = 00

(3/5) x

fints_t

—

—

kHz

floc_high

Loss of external clock minimum frequency —

RANGE = 01, 10, or 11

(16/5) x

fints_t

—

—

kHz

31.25

—

39.0625

kHz

20

20.97

25

MHz

40

41.94

50

MHz

60

62.91

75

MHz

80

83.89

100

MHz

—

23.99

—

MHz

—

47.97

—

MHz

—

71.99

—

MHz

—

95.98

—

MHz

—

180

—

Notes

FLL

ffll_ref

fdco

FLL reference frequency range

DCO output

frequency range

Low range (DRS=00)

2, 3

640 × ffll_ref

Mid range (DRS=01)

1280 × ffll_ref

Mid-high range (DRS=10)

1920 × ffll_ref

High range (DRS=11)

2560 × ffll_ref

fdco_t_DMX32 DCO output

frequency

Low range (DRS=00)

4, 5

732 × ffll_ref

Mid range (DRS=01)

1464 × ffll_ref

Mid-high range (DRS=10)

2197 × ffll_ref

High range (DRS=11)

2929 × ffll_ref

Jcyc_fll

FLL period jitter

ps

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

30

NXP Semiconductors

�Peripheral operating requirements and behaviors

Table 15. MCG specifications (continued)

Symbol

Description

• fVCO = 48 MHz

• fVCO = 98 MHz

tfll_acquire

FLL target frequency acquisition time

Min.

Typ.

Max.

Unit

Notes

—

150

—

—

—

1

ms

6

8

—

16

MHz

PLL0,1

fpll_ref

PLL reference frequency range

fvcoclk_2x

VCO output frequency

fvcoclk

PLL output frequency

fvcoclk_90

180

90

PLL quadrature output frequency

Ipll

PLL0 operating current

• VCO @ 184 MHz (fosc_hi_1 = 32 MHz, fpll_ref

= 8 MHz, VDIV multiplier = 23)

Ipll

PLL0 operating current

• VCO @ 360 MHz (fosc_hi_1 = 32 MHz, fpll_ref

= 8 MHz, VDIV multiplier = 45)

Ipll

PLL1 operating current

• VCO @ 184 MHz (fosc_hi_1 = 32 MHz, fpll_ref

= 8 MHz, VDIV multiplier = 23)

Ipll

PLL1 operating current

• VCO @ 360 MHz (fosc_hi_1 = 32 MHz, fpll_ref

= 8 MHz, VDIV multiplier = 45)

tpll_lock

Lock detector detection time

Jcyc_pll

PLL period jitter (RMS)

Jacc_pll

90

—

—

—

360

180

180

MHz

MHz

MHz

—

2.8

—

mA

—

4.7

—

mA

—

2.3

—

mA

—

3.6

—

mA

—

—

100 × 10-6

+ 1075(1/

fpll_ref)

s

7

7

7

8

9

• fvco = 180 MHz

—

100

—

ps

• fvco = 360 MHz

—

75

—

ps

PLL accumulated jitter over 1µs (RMS)

10

• fvco = 180 MHz

—

600

—

ps

• fvco = 360 MHz

—

300

—

ps

1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock

mode).

2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

3. The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation

(Δfdco_t) over voltage and temperature should be considered.

4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

6. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed,

DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE,

FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

8. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled

(BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes

it is already running.

9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of

each PCB and results will vary.

10. Accumulated jitter depends on VCO frequency and VDIV.

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

31

�Peripheral operating requirements and behaviors

6.3.2 Oscillator electrical specifications

6.3.2.1

Oscillator DC electrical specifications

Table 16. Oscillator DC electrical specifications

Symbol

Description

Min.

Typ.

Max.

Unit

VDD

Supply voltage

1.71

—

3.6

V

IDDOSC

IDDOSC

Supply current — low-power mode (HGO=0)

Notes

1

• 32 kHz

—

500

—

nA

• 4 MHz

—

200

—

μA

• 8 MHz (RANGE=01)

—

300

—

μA

• 16 MHz

—

950

—

μA

• 24 MHz

—

1.2

—

mA

• 32 MHz

—

1.5

—

mA

Supply current — high-gain mode (HGO=1)

1

• 32 kHz

—

25

—

μA

• 4 MHz

—

400

—

μA

• 8 MHz (RANGE=01)

—

500

—

μA

• 16 MHz

—

2.5

—

mA

• 24 MHz

—

3

—

mA

• 32 MHz

—

4

—

mA

Cx

EXTAL load capacitance

—

—

—

2, 3

Cy

XTAL load capacitance

—

—

—

2, 3

RF

Feedback resistor — low-frequency, low-power

mode (HGO=0)

—

—

—

MΩ

Feedback resistor — low-frequency, high-gain

mode (HGO=1)

—

10

—

MΩ

Feedback resistor — high-frequency, low-power

mode (HGO=0)

—

—

—

MΩ

Feedback resistor — high-frequency, high-gain

mode (HGO=1)

—

1

—

MΩ

Series resistor — low-frequency, low-power

mode (HGO=0)

—

—

—

kΩ

Series resistor — low-frequency, high-gain mode

(HGO=1)

—

200

—

kΩ

Series resistor — high-frequency, low-power

mode (HGO=0)

—

—

—

kΩ

—

0

—

kΩ

RS

2, 4

Series resistor — high-frequency, high-gain

mode (HGO=1)

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

32

NXP Semiconductors

�Peripheral operating requirements and behaviors

Table 16. Oscillator DC electrical specifications (continued)

Symbol

Vpp5

1.

2.

3.

4.

5.

Description

Min.

Typ.

Max.

Unit

Peak-to-peak amplitude of oscillation (oscillator

mode) — low-frequency, low-power mode

(HGO=0)

—

0.6

—

V

Peak-to-peak amplitude of oscillation (oscillator

mode) — low-frequency, high-gain mode

(HGO=1)

—

VDD

—

V

Peak-to-peak amplitude of oscillation (oscillator

mode) — high-frequency, low-power mode

(HGO=0)

—

0.6

—

V

Peak-to-peak amplitude of oscillation (oscillator

mode) — high-frequency, high-gain mode

(HGO=1)

—

VDD

—

V

Notes

VDD=3.3 V, Temperature =25 °C

See crystal or resonator manufacturer's recommendation

Cx and Cy can be provided by using either integrated capacitors or external components.

When low-power mode is selected, RF is integrated and must not be attached externally.

The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any

other device.

6.3.2.2

Symbol

Oscillator frequency specifications

Table 17. Oscillator frequency specifications

Description

Min.

Typ.

Max.

Unit

fosc_lo

Oscillator crystal or resonator frequency — lowfrequency mode (MCG_C2[RANGE]=00)

32

—

40

kHz

fosc_hi_1

Oscillator crystal or resonator frequency — highfrequency mode (low range)

(MCG_C2[RANGE]=01)

3

—

8

MHz

fosc_hi_2

Oscillator crystal or resonator frequency — high

frequency mode (high range)

(MCG_C2[RANGE]=1x)

8

—

32

MHz

fec_extal

Input clock frequency (external clock mode)

—

—

60

MHz

tdc_extal

Input clock duty cycle (external clock mode)

40

50

60

%

Crystal startup time — 32 kHz low-frequency,

low-power mode (HGO=0)

—

1000

—

ms

Crystal startup time — 32 kHz low-frequency,

high-gain mode (HGO=1)

—

500

—

ms

Crystal startup time — 8 MHz high-frequency

(MCG_C2[RANGE]=01), low-power mode

(HGO=0)

—

0.6

—

ms

Crystal startup time — 8 MHz high-frequency

(MCG_C2[RANGE]=01), high-gain mode

(HGO=1)

—

1

—

ms

tcst

Notes

1

2, 3

4, 5

1. Frequencies less than 8 MHz are not in the PLL range.

2. Other frequency limits may apply when external clock is being used as a reference for the FLL or PLL.

3. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by

FRDIV, it remains within the limits of the DCO input clock frequency.

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

33

�Peripheral operating requirements and behaviors

4. Proper PC board layout procedures must be followed to achieve specifications.

5. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG_S register

being set.

NOTE

The 32 kHz oscillator works in low power mode by default and

cannot be moved into high power/gain mode.

6.3.3 32 kHz oscillator electrical characteristics

6.3.3.1

32 kHz oscillator DC electrical specifications

Table 18. 32kHz oscillator DC electrical specifications

Symbol

Description

Min.

Typ.

Max.

Unit

VBAT

Supply voltage

1.71

—

3.6

V

Internal feedback resistor

—

100

—

MΩ

Cpara

Parasitical capacitance of EXTAL32 and XTAL32

—

5

7

pF

Vpp1

Peak-to-peak amplitude of oscillation

—

0.6

—

V

RF

1. When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to

required oscillator components and must not be connected to any other devices.

6.3.3.2

Symbol

fosc_lo

tstart

32 kHz oscillator frequency specifications

Table 19. 32 kHz oscillator frequency specifications

Description

Min.

Typ.

Max.

Unit

Oscillator crystal

—

32.768

—

kHz

Crystal start-up time

—

1000

—

ms

1

700

—

VBAT

mV

2, 3

vec_extal32 Externally provided input clock amplitude

Notes

1. Proper PC board layout procedures must be followed to achieve specifications.

2. This specification is for an externally supplied clock driven to EXTAL32 and does not apply to any other clock input. The

oscillator remains enabled and XTAL32 must be left unconnected.

3. The parameter specified is a peak-to-peak value and VIH and VIL specifications do not apply. The voltage of the applied

clock must be within the range of VSS to VBAT.

6.4 Memories and memory interfaces

6.4.1 Flash (FTFE) electrical specifications

This section describes the electrical characteristics of the FTFE module.

K61 Sub-Family, Rev. 7, 02/2018

34

NXP Semiconductors

�Peripheral operating requirements and behaviors

6.4.1.1

Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are

active and do not include command overhead.

Table 20. NVM program/erase timing specifications

Symbol

Description

Min.

Typ.

Max.

Unit

thvpgm8

thversscr

Notes

Program Phrase high-voltage time

—

7.5

18

μs

Erase Flash Sector high-voltage time

—

13

113

ms

1

thversblk128k Erase Flash Block high-voltage time for 128 KB

—

104

1808

ms

1

thversblk256k Erase Flash Block high-voltage time for 256 KB

—

208

3616

ms

1

Notes

1. Maximum time based on expectations at cycling end-of-life.

6.4.1.2

Symbol

Flash timing specifications — commands

Table 21. Flash command timing specifications

Description

Min.

Typ.

Max.

Unit

Read 1s Block execution time

trd1blk128k

• 128 KB data flash

—

—

0.5

ms

trd1blk256k

• 256 KB program flash

—

—

1.0

ms

256 KB data flash

trd1sec4k

Read 1s Section execution time (4 KB flash)

—

—

100

μs

1

tpgmchk

Program Check execution time

—

—

80

μs

1

trdrsrc

Read Resource execution time

—

—

40

μs

1

tpgm8

Program Phrase execution time

—

70

150

μs

Erase Flash Block execution time

2

tersblk128k

• 128 KB data flash

—

110

925

ms

tersblk256k

• 256 KB program flash

—

220

1850

ms

Erase Flash Sector execution time

—

15

115

ms

Program Section execution time (4KB flash)

—

20

—

ms

256 KB data flash

tersscr

tpgmsec4k

2

Read 1s All Blocks execution time

trd1allx

• FlexNVM devices

—

—

3.4

ms

trd1alln

• Program flash only devices

—

—

3.4

ms

Read Once execution time

—

—

30

μs

Program Once execution time

—

70

—

μs

tersall

Erase All Blocks execution time

—

650

5600

ms

2

tvfykey

Verify Backdoor Access Key execution time

—

—

30

μs

1

trdonce

tpgmonce

1

Swap Control execution time

Table continues on the next page...

K61 Sub-Family, Rev. 7, 02/2018

NXP Semiconductors

35

�Peripheral operating requirements and behaviors

Table 21. Flash command timing specifications (continued)

Symbol

Description

Min.

Typ.

Max.

Unit

tswapx01

• control code 0x01

—

200

—

μs

tswapx02

• control code 0x02

—

70

150

μs

tswapx04

• control code 0x04

—

70

150

μs

tswapx08

• control code 0x08

—

—

30

μs

Notes

Program Partition for EEPROM execution time

tpgmpart64k

• 64 KB EEPROM backup

—

235

—

ms

tpgmpart256k

• 256 KB EEPROM backup

—

240

—

ms

• Control Code 0xFF

—

205

—

μs

tsetram64k

• 64 KB EEPROM backup

—

1.6

2.5

ms

tsetram128k

• 128 KB EEPROM backup

—

2.7

3.8

ms

tsetram256k

• 256 KB EEPROM backup

—

4.8

6.2

ms

—

140

225

μs

Set FlexRAM Function execution time:

tsetramff

t eewr8bers

Byte-write to erased FlexRAM location execution

time

3

Byte-write to FlexRAM execution time:

teewr8b64k

• 64 KB EEPROM backup

—

400

1700

μs

teewr8b128k

• 128 KB EEPROM backup

—

450

1800

μs

teewr8b256k

• 256 KB EEPROM backup

—

525

2000

μs