NXP Semiconductors

Data Sheet: Technical Data

MKW36Z/35Z Data Sheet

An ultra low power, highly integrated Bluetooth® Low

Energy 5.0 wireless microcontroller

MKW36Z512

Rev. 8, 05/2020

MKW36Z512VHT4

MKW36Z512VFP4

MKW35Z512VHT4

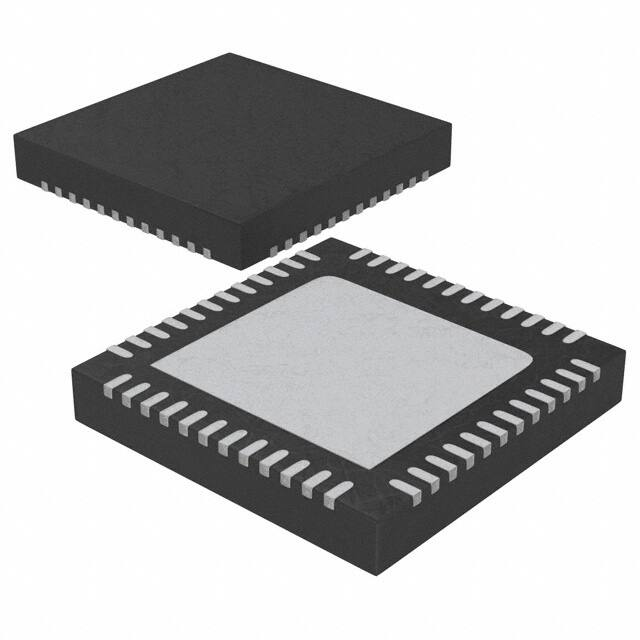

48 LQFN

40 "Wettable" HVQFN

7x7 mm Pitch 0.5 mm 6x6 mm Pitch 0.5 mm

Multi-Standard Radio

System peripherals

• 2.4 GHz Bluetooth Low Energy (Bluetooth LE) version

• Nine MCU low-power modes to provide power

5.0 compliant supporting up to 8 simultaneous

optimization based on application requirements

hardware connections

• DC-DC Converter supporting Buck and Bypass

• Generic FSK modulation

operating modes

• Data Rate: 250, 500 and 1000 kbps

• Direct memory access (DMA) Controller

• Modulations: GFSK BT = 0.3, 0.5, and 0.7;

• Computer operating properly (COP) watchdog

FSK/MSK

• Serial wire debug (SWD) Interface and Micro Trace

• Modulation Index: 0.32, 0.5, 0.7, and 1.0

buffer

• Typical Receiver Sensitivity

• Bit Manipulation Engine (BME)

(Bluetooth LE 1 Mbps) = –95 dBm

Analog Modules

• Typical Receiver Sensitivity

• 16-bit Analog-to-Digital Converter (ADC)

(250 kbps GFSK-BT=0.5, h=0.5) = –99 dBm

• 6-bit High Speed Analog Comparator (CMP)

• Programmable Transmitter Output Power:

• 1.2 V voltage reference (VREF)

–30 dBm to 5 dBm

• Low external component counts for low cost application

Timers

• On-chip balun with single ended bidirectional RF port

• 16-bit low-power timer (LPTMR)

• 3 Timer/PWM Modules(TPM): One 4 channel TPM

MCU and Memories

and two 2 channel TPMs

• 256 KB program flash memory plus 256 KB FlexNVM

• Programmable Interrupt Timer (PIT)

on KW36Z

• Real-Time Clock (RTC)

• 8 KB FlexRAM supporting EEPROM emulation on

KW36Z

Communication interfaces

• 512 KB program flash memory on KW35Z

• 2 serial peripheral interface (SPI) modules

• Up to 48 MHz Arm® Cortex®-M0+ core

• 2 inter-integrated circuit (I2C) modules

• On-chip 64 KB SRAM

• Low Power UART (LPUART) module with LIN

support (2x LPUART on KW36Z)

Low Power Consumption

• Carrier Modulator Timer (CMT)

• Transceiver current (DC-DC buck mode, 3.6 V supply)

• FlexCAN module (with CAN FD support up to 3.2

Mbps baudrate) on KW36Z

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

�Security

• AES-128 Hardware Accelerator (AESA)

• True Random Number Generator (TRNG)

• Advanced flash security on Program Flash

• 80-bit unique identification number per chip

• 40-bit unique media access control (MAC) subaddress

• LE Secure Connections

• Typical Rx Current: 6.3 mA

• Typical Tx current: 5.7 mA (0 dBm output)

• Low Power Mode (VLLS0) Current: 258 nA

Clocks

• 26 and 32 MHz supported for Bluetooth LE and

Generic FSK modes

• 32.768 kHz Crystal Oscillator

Operating Characteristics

• Voltage range: 1.71 V to 3.6 V

• Ambient temperature range: –40 to 105 °C

• Industrial Qualification

Human-machine interface

• General-purpose input/output

Orderable parts details

Top Line

Marking

Qualification

CAN

FD

2nd UART with LIN

FlexRAM

Package

MKW36Z512VHT4 (F)M36Z

Industrial

Y

Y

Y

7X7 mm 48-pin

LQFN

MKW36Z512VFP4 M36Z9V4

Industrial

Y

Y

Y

6X6 mm 40-pin

"Wettable" HVQFN

MKW35Z512VHT4 (F)M35Z

Industrial

N

N

N

7X7 mm 48-pin

LQFN

Device

Related Resources

Type

Description

Resource

Product

Selector

The Product Selector lets you find the right Kinetis part for your design.

W-Series Product Selector

Fact Sheet

The Fact Sheet gives overview of the product key features and its uses.

KW36-35-34 Fact Sheet

Reference

Manual

The Reference Manual contains a comprehensive description of the

structure and function (operation) of a device.

MKW36A512RM1

Data Sheet

The Data Sheet includes electrical characteristics and signal

connections.

This document.

Chip Errata

The chip mask set Errata provides additional or corrective information for KINETIS_W_1N41U1

a particular device mask set.

Package

drawing

Package dimensions are provided in package drawings.

• 40-pin "Wettable" HVQFN

(6x6): 98ASA01025D1

• 48-pin LQFN (7x7):

98ASA00694D1

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

2

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Table of Contents

1 Introduction......................................................................... 4

2 Feature Descriptions........................................................... 5

2.1 Block Diagram..............................................................5

2.2 Radio features..............................................................6

2.3 Microcontroller features............................................... 7

2.4 System features........................................................... 8

2.5 Peripheral features.......................................................10

2.6 Security Features.........................................................14

3 Transceiver Description.......................................................16

3.1 Key Specifications........................................................16

3.2 Channel Map Frequency Plans ...................................16

3.2.1 Channel Plan for Bluetooth Low Energy.......... 16

3.2.2 Other Channel Plans .......................................18

3.3 Transceiver Functions..................................................18

4 Transceiver Electrical Characteristics................................. 19

4.1 Radio operating conditions.......................................... 19

4.2 Receiver Feature Summary......................................... 19

4.3 Transmit and PLL Feature Summary...........................22

5 System and Power Management........................................ 26

5.1 Power Management.....................................................27

5.1.1 DC-DC Converter.............................................27

5.2 Modes of Operation..................................................... 27

5.2.1 Power modes................................................... 27

6 KW36Z/35Z Electrical Characteristics.................................30

6.1 AC electrical characteristics.........................................30

6.2 Nonswitching electrical specifications..........................30

6.2.1 Voltage and current operating requirements....30

6.2.2 LVD and POR operating requirements............ 31

6.2.3 Voltage and current operating behaviors......... 32

6.2.4 Power mode transition operating behaviors.....33

6.2.5 Power consumption operating behaviors......... 34

6.2.6 Diagram: Typical IDD_RUN operating

behavior........................................................... 40

6.4.1 Thermal operating requirements...................... 45

6.4.2 Thermal attributes............................................ 46

6.5 Peripheral operating requirements and behaviors....... 46

6.5.1 Core modules...................................................46

6.5.2 System modules.............................................. 47

6.5.3 Clock modules................................................. 48

6.5.4 Memories and memory interfaces....................52

6.5.5 Security and integrity modules......................... 54

6.5.6 Analog.............................................................. 54

6.5.7 Timers.............................................................. 62

6.5.8 Communication interfaces................................62

6.5.9 Human-machine interfaces (HMI).................... 67

6.6 DC-DC Converter Operating Requirements................ 67

6.7 Ratings.........................................................................70

6.7.1 Thermal handling ratings................................. 70

6.7.2 Moisture handling ratings................................. 70

6.7.3 ESD handling ratings....................................... 70

6.7.4 Voltage and current operating ratings.............. 71

7 Pin Diagrams and Pin Assignments.................................... 71

7.1 KW36Z Signal Multiplexing and Pin Assignments....... 71

7.2 KW36Z Pinouts............................................................ 74

7.3 KW35Z Signal Multiplexing and Pin Assignments....... 75

7.4 KW35Z Pinouts............................................................ 78

7.5 Module Signal Description Tables............................... 78

7.5.1 Core Modules...................................................79

7.5.2 Radio Modules................................................. 79

7.5.3 System Modules.............................................. 80

7.5.4 Clock Modules................................................. 81

7.5.5 Analog Modules............................................... 81

7.5.6 Timer Modules................................................. 82

7.5.7 Communication Interfaces............................... 83

7.5.8 Human-Machine Interfaces(HMI)..................... 85

8 Package Information........................................................... 85

6.2.7 SoC Power Consumption.................................42

6.2.8 Designing with radiated emissions in mind...... 43

6.2.9 Capacitance attributes..................................... 43

6.3 Switching electrical specifications................................44

6.3.1 Device clock specifications.............................. 44

6.3.2 General switching specifications...................... 44

6.4 Thermal specifications................................................. 45

8.1 Obtaining package dimensions....................................85

9 Part identification.................................................................85

9.1 Description................................................................... 85

9.2 Format..........................................................................86

9.3 Fields........................................................................... 86

9.4 Example....................................................................... 86

10 Revision History.................................................................. 87

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

3

NXP Semiconductors

�Introduction

1 Introduction

The KW36Z/35Z wireless microcontrollers (MCU), which includes the KW36Z and

KW35Z families of devices, are highly integrated single-chip devices that enable

Bluetooth Low Energy (Bluetooth LE) and Generic FSK connectivity for industrial and

medical/healthcare embedded systems. The target applications center on wirelessly

bridging the embedded world with mobile devices to enhance the human interface

experience, share embedded data between devices and the cloud and enable wireless

firmware updates.

The KW36Z/35Z Wireless MCU integrates an Arm® Cortex®-M0+ CPU with up to

512 KB flash and 64 KB SRAM and a 2.4 GHz radio that supports Bluetooth LE 5.0

and Generic FSK modulations. The Bluetooth LE radio supports up to 8 simultaneous

connections in any master/slave combination. The Medical Body Area Network

(MBAN) frequencies from 2.36 to 2.4 GHz are also supported enabling wearable or

implantable wireless medical devices.

The KW36Z includes an integrated FlexCAN module enabling seamless integration

into an industrial CAN communication network, enabling communication with external

control and sensor monitoring devices over Bluetooth LE. The FlexCAN module can

support CAN’s flexible data-rate (CAN FD) protocol for increased bandwidth and

lower latency.

The KW36Z/35Z devices can be used as a "BlackBox" modem in order to add

Bluetooth LE or Generic FSK connectivity to an existing host MCU or MPU

(microprocessor), or may be used as a standalone smart wireless sensor with embedded

application where no host controller is required.

The RF circuit of the KW36Z/35Z is optimized to require very few external

components, achieving the smallest RF footprint possible on a printed circuit board.

Extremely long battery life is achieved through the efficiency of code execution in the

Cortex-M0+ CPU core and the multiple low power operating modes of the KW36Z/

35Z. For power critical applications, an integrated DC-DC converter enables operation

from a single coin cell or Li-ion battery with a significant reduction of peak receive and

transmit current consumption.

4

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

2 Feature Descriptions

This section provides a simplified block diagram and highlights the KW36Z/35Z

features.

2.1 Block Diagram

Arm Cortex M0+ Core

Serial Wire Debug

DAP

MDM

DWT

MTB

Unified Bus

NVIC

WIC

IOPORT

MCG

DMA MUX

FLL

4ch DMA

AHBLite

IRC

4 MHz

32K Osc

IRC

32 kHz

32M Osc

AHBLite

M2A

M0

Crossbar-Lite Switch (AXBS)

S0

S1

64 KByte

SRAM

DCDC

VDCDC_IN

Flash

Controller

Flash

256 KB

FlexNVM

256 KB

FlexRAM

8 KB

S2

ADC

SIM

SMC

GPIO

CMP

PIT

BME

I2C x2

LTC(AESA)

TPM x3

LPUART x2

TRNG

LPTMR

SPI x2

RTC

CMT

AIPS-Lite

RCM

VREF

PMC

Radio

APB

IPS

IPS

FlexCAN

Figure 1. KW36 Detailed Block Diagram

Arm Cortex M0+ Core

Serial Wire Debug

DAP

MDM

DWT

MTB

Unified Bus

NVIC

WIC

IOPORT

MCG

DMA MUX

FLL

4ch DMA

AHBLite

IRC

4 MHz

32K Osc

IRC

32 kHz

32M Osc

AHBLite

M2A

M0

Crossbar-Lite Switch (AXBS)

S0

S1

64 KByte

SRAM

Flash

Controller

Flash

512 KB

Prg Acc RAM

8 KB

S2

SIM

SMC

ADC

CMP

GPIO

LTC(AESA)

PIT

TPM x3

I2C x2

BME

LPUART

AIPS-Lite

RCM

TRNG

LPTMR

SPI x2

RTC

CMT

Radio

IPS

VDCDC_IN

DCDC

PMC

VREF

APB

IPS

Figure 2. KW35 Detailed Block Diagram

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

5

NXP Semiconductors

�Feature Descriptions

2.2 Radio features

Operating frequencies:

• 2.4 GHz ISM band (2400-2483.5 MHz)

• Medical Body Area Network (MBAN) 2360-2400 MHz

Supported standards:

• Bluetooth Low Energy Version 5.0 compliant radio

• Generic FSK modulation supporting data rates up to 1 Mbit/s

• Support for up to 8 simultaneous Bluetooth LE hardware connections in any

master, slave combination

• Bluetooth LE Application Profiles

Receiver performance:

• Receive sensitivity of up to –95 dBm for Bluetooth LE

• Receive sensitivity of up to –99 dBm for a 250 kbit/s GFSK mode with a

modulation index of 0.5. Receive sensitivity in Generic FSK modes depends on

mode selection and data rate.

Other features:

• Programmable transmit output power from –30 dBm to +5 dBm

• 26 MHz and 32 MHz crystals supported for Bluetooth LE and Generic FSK modes

• Bluetooth Low Energy version 5.0 Link Layer hardware with 1 Mbit/s PHY

support

• Hardware acceleration for Generic FSK packet processing

• Generic FSK modulation at 250, 500 and 1000 kbit/s

• Supports 8 simultaneous Bluetooth LE connections in any master/slave

combination

• Enhanced Bluetooth LE automatic deep sleep modes (DSM) supporting Slave

Latency

• Up to 26 devices supported by whitelist in hardware

• Up to 8 private resolvable addresses supported in hardware

• Supports DMA capture of IQ data with sampling rate of up to 2 MHz, when using a

32 MHz crystal

• Integrated on-chip balun

• Single ended bidirectional RF port shared by transmit and receive

• Low external component count

• Supports transceiver range extension using external PA and/or LNA

6

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

2.3 Microcontroller features

Arm Cortex-M0+ CPU

• Up to 48 MHz CPU

• As compared to Cortex-M0, the Cortex-M0+ uses an optimized 2-stage pipeline

microarchitecture for reduced power consumption and improved architectural

performance (cycles per instruction)

• Supports up to 32 interrupt request sources

• Binary compatible instruction set architecture with the Cortex-M0 core

• Thumb instruction set combines high code density with 32-bit performance

• Serial Wire Debug (SWD) reduces the number of pins required for debugging

• Micro Trace Buffer (MTB) provides lightweight program trace capabilities using

system RAM as the destination memory

Nested Vectored Interrupt Controller (NVIC)

• 32 vectored interrupts, 4 programmable priority levels

• Includes a single non-maskable interrupt

Wake-up Interrupt Controller (WIC)

• Supports interrupt handling when system clocking is disabled in low-power

modes

• Takes over and emulates the NVIC behavior when correctly primed by the NVIC

on entry to very-deep-sleep

• A rudimentary interrupt masking system with no prioritization logic signals for

wake-up as soon as a non-masked interrupt is detected

Debug Controller

•

•

•

•

Two-wire Serial Wire Debug (SWD) interface

Hardware breakpoint unit for 2 code addresses

Hardware watchpoint unit for 2 data items

Micro Trace Buffer for program tracing

On-Chip Memory

• Up to 512 KB Flash

• KW36Z contains 256 KB program flash with ECC and 256 KB FlexNVM.

• KW35Z contains 512 KB program flash with ECC.

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

7

NXP Semiconductors

�Feature Descriptions

•

•

•

•

• Flash implemented as two equal blocks each of 256 KB block. Code can

execute or read from one block while the other block is being erased or

programmed on KW35Z only.

• Firmware distribution protection. Program flash can be marked execute-only

on a per-sector (8 KB) basis to prevent firmware contents from being read by

third parties.

64 KB SRAM

KW36Z contains 8 KB FlexRAM.

KW35Z contains 8 KB program acceleration RAM.

Security circuitry to prevent unauthorized access to RAM and flash contents

through the debugger

2.4 System features

Power Management Control Unit (PMC)

•

•

•

•

•

•

•

•

•

•

Programmable power saving modes

Available wake-up from power saving modes via internal and external sources

Integrated Power-on Reset (POR)

Integrated Low Voltage Detect (LVD) with reset (brownout) capability

Selectable LVD trip points

Programmable Low Voltage Warning (LVW) interrupt capability

Individual peripheral clocks can be gated off to reduce current consumption

Internal Buffered bandgap reference voltage

Factory programmed trim for bandgap and LVD

1 kHz Low-power Oscillator (LPO)

DC-DC Converters

• Internal switched mode power supply supporting Buck and Bypass operating

modes

• Buck operation supports external voltage sources of 2.1 V to 3.6 V

• When DC-DC is not used, the device supports an external voltage range of 1.5 V to

3.6 V (1.5 - 3.6 V on VDD_RF1, VDD_RF2, VDD_RF3 and

VDD_1P5OUT_PMCIN pins. 1.71 - 3.6 V on VDD_0, VDD_1, and VDDA pins)

• An external inductor is required to support the Buck mode

Direct Memory Access (DMA) Controller

• All data movement via dual-address transfers: read from source, write to

destination

8

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

• Programmable source and destination addresses and transfer size

• Support for enhanced addressing modes

• 4-channel implementation that performs complex data transfers with minimal

intervention from a host processor

• Internal data buffer, used as temporary storage to support 16- and 32-byte

transfers

• Connections to the crossbar switch for bus mastering the data movement

• Transfer Control Descriptor (TCD) organized to support two-deep, nested transfer

operations

• 32-byte TCD stored in local memory for each channel

• An inner data transfer loop defined by a minor byte transfer count

• An outer data transfer loop defined by a major iteration count

• Channel activation via one of three methods:

• Explicit software initiation

• Initiation via a channel-to-channel linking mechanism for continuous

transfers

• Peripheral-paced hardware requests, one per channel

• Fixed-priority and round-robin channel arbitration

• Channel completion reported via optional interrupt requests

• One interrupt per channel, optionally asserted at completion of major iteration

count

• Optional error terminations per channel and logically summed together to form

one error interrupt to the interrupt controller

• Optional support for scatter/gather DMA processing

• Support for complex data structures

DMA Channel Multiplexer (DMA MUX)

• 4 independently selectable DMA channel routers

• 2 periodic trigger sources available

• Each channel router can be assigned to 1 of the peripheral DMA sources

COP Watchdog Module

• Independent clock source input (independent from CPU/bus clock)

• Choice between two clock sources

• LPO oscillator

• Bus clock

System Clocks

• Both 26 MHz and 32 MHz crystal reference oscillator supported for Bluetooth LE

and Generic FSK modes

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

9

NXP Semiconductors

�Feature Descriptions

• MCU can derive its clock either from the crystal reference oscillator or the

Frequency-locked Loop (FLL)1

• 32.768 kHz crystal reference oscillator used to maintain precise Bluetooth Low

Energy timing in low-power modes

• Multipurpose Clock Generator (MCG)

• Internal reference clocks — Can be used as a clock source for other on-chip

peripherals

• On-chip RC oscillator range of 31.25 kHz to 39.0625 kHz with 2% accuracy

across full temperature range

• On-chip 4 MHz oscillator with 5% accuracy across full temperature range

• Frequency-locked Loop (FLL) controlled by internal or external reference

• 20 MHz to 48 MHz FLL output

Unique Identifiers

• 80-bit Unique ID represents a unique identifier for each chip

• 40-bit unique Media Access Control (MAC) address, which can be used to build a

unique 48-bit Bluetooth Low Energy MAC address

2.5 Peripheral features

16-bit Analog-to-Digital Converter (ADC)

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Linear successive approximation algorithm with 16-bit resolution

Output formatted in differential-ended 16-, 13-, 11-, and 9-bit mode

Output formatted in single-ended 16-, 12-, 10-, and 8-bit mode

Single or continuous conversion

Configurable sample time and conversion speed/power

Conversion rates in 16-bit mode with no averaging up to ~500Ksamples/sec

Input clock selection

Operation in low-power modes for lower noise operation

Asynchronous clock source for lower noise operation

Selectable asynchronous hardware conversion trigger

Automatic compare with interrupt for less-than, or greater than, or equal to

programmable value

Temperature sensor

Battery voltage measurement

Hardware average function

Selectable voltage reverence

Self-calibration mode

1.

Clock options can have restrictions based on the chosen SoC configuration.

10

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

High-Speed Analog Comparator (CMP)

• 6-bit DAC programmable reference generator output

• Up to eight selectable comparator inputs; each input can be compared with any

input by any polarity sequence

• Selectable interrupt on rising edge, falling edge, or either rising or falling edges of

comparator output

• Two performance modes:

• Shorter propagation delay at the expense of higher power

• Low-power, with longer propagation delay

• Operational in all MCU power modes except VLLS0 mode

Voltage Reference(VREF1)

• Programmable trim register with 0.5 mV steps, automatically loaded with factory

trimmed value upon reset

• Programmable buffer mode selection:

• Off

• Bandgap enabled/standby (output buffer disabled)

• High-power buffer mode (output buffer enabled)

• 1.2 V output at room temperature

• VREF_OUT output signal

Low-power Timer (LPTMR)

• One channel

• Operation as timer or pulse counter

• Selectable clock for prescaler/glitch filter

• 1 kHz internal LPO

• External low-power crystal oscillator

• Internal reference clock

• Configurable glitch filter or prescaler

• Interrupt generated on timer compare

• Hardware trigger generated on timer compare

• Functional in all power modes

Timer/PWM (TPM)

•

•

•

•

TPM0: 4 channels, TPM1 and TPM2: 2 channels each

Selectable source clock

Programmable prescaler

16-bit counter supporting free-running or initial/final value, and counting is up or

up-down

• Input capture, output compare, and edge-aligned and center-aligned PWM modes

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

11

NXP Semiconductors

�Feature Descriptions

•

•

•

•

Input capture and output compare modes

Generation of hardware triggers

TPM1 and TPM2: Quadrature decoder with input filters

Global time base mode shares single time base across multiple TPM instances

Programmable Interrupt Timer (PIT)

• Up to 2 interrupt timers for triggering ADC conversions

• 32-bit counter resolution

• Clocked by bus clock frequency

Real-Time Clock (RTC)

• 32-bit seconds counter with 32-bit alarm

• Can be invalidated on detection of tamper detect

• 16-bit prescaler with compensation

• Register write protection

• Hard Lock requires MCU POR to enable write access

• Soft lock requires POR or software reset to enable write/read access

• Capable of waking up the system from low-power modes

Inter-Integrated Circuit (I2C)

•

•

•

•

•

•

•

•

•

•

•

Two channels

Compatible with I2C bus standard and SMBus Specification Version 2 features

Up to 400 kHz operation

Multi-master operation

Software programmable for one of 64 different serial clock frequencies

Programmable slave address and glitch input filter

Interrupt driven byte-by-byte data transfer

Arbitration lost interrupt with automatic mode switching from master to slave

Calling address identification interrupt

Bus busy detection broadcast and 10-bit address extension

Address matching causes wake-up when processor is in low-power mode

LPUART

•

•

•

•

•

•

One channel (2 channels on KW36Z)

Full-duplex operation

Standard mark/space Non-return-to-zero (NRZ) format

13-bit baud rate selection with fractional divide of 32

Programmable 8-bit or 9-bit data format

Programmable 1 or 2 stop bits

12

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Separately enabled transmitter and receiver

Programmable transmitter output polarity

Programmable receive input polarity

13-bit break character option

11-bit break character detection option

Two receiver wake-up methods:

• Idle line wake-up

• Address mark wake-up

Address match feature in receiver to reduce address mark wake-up ISR overhead

Interrupt or DMA driven operation

Receiver framing error detection

Hardware parity generation and checking

Configurable oversampling ratio to support from 1/4 to 1/32 bit-time noise

detection

Operation in low-power modes

Hardware Flow Control RTS\CTS

Functional in Stop/VLPS modes

Break detect supporting LIN

Serial Peripheral Interface (SPI)

•

•

•

•

•

•

•

•

•

•

Two independent SPI channels

Master and slave mode

Full-duplex, three-wire synchronous transfers

Programmable transmit bit rate

Double-buffered transmit and receive data registers

Serial clock phase and polarity options

Slave select output

Control of SPI operation during wait mode

Selectable MSB-first or LSB-first shifting

Support for both transmit and receive by DMA

Carrier Modulator Timer (CMT)

• Four modes of operation

• Time; with independent control of high and low times

• Baseband

• Frequency shift key (FSK)

• Direct software control of CMT_IRO signal

• Extended space operation in time, baseband, and FSK modes

• Selectable input clock divider

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

13

NXP Semiconductors

�Feature Descriptions

• Interrupt on end of cycle

• Ability to disable CMT_IRO signal and use as timer interrupt

General Purpose Input/Output (GPIO)

•

•

•

•

•

Hysteresis and configurable pull up device on all input pins

Independent pin value register to read logic level on digital pin

All GPIO pins can generate IRQ and wake-up events

Configurable drive strength on some output pins

GPIO can be configured to function as a interrupt driven keyboard scanning matrix

• In the 48-pin package there are a total of 25 digital pins

• In the 40-pin package there are a total of 18 digital pins

FlexCAN (for KW36Z only)

• Full implementation of the CAN with Flexible Data Rate (CAN FD) protocol

specification and CAN protocol specification, Version 2.0 B

• Flexible Message Buffers (MBs); there are total 32 MBs of 8 bytes data length

each, configurable as Rx or Tx, all supporting standard and extended messages

• Programmable clock source to the CAN Protocol Interface, either peripheral clock

or oscillator clock

• Capability to select priority between mailboxes and Rx FIFO during matching

process

• Powerful Rx FIFO ID filtering, capable of matching incoming IDs against either

128 extended, 256 standard, or 512 partial (8 bit) IDs, with up to 32 individual

masking capability

2.6 Security Features

Advanced Encryption Standard Accelerator(AES-128 Accelerator)

The Advanced Encryption Standard Accelerator (AESA) module is a standalone

hardware coprocessor capable of accelerating the 128-bit advanced encryption standard

(AES) cryptographic algorithms.

The AESA engine supports the following cryptographic features.

LTC includes the following features:

• Cryptographic authentication

• Message Authentication Codes (MAC)

14

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Feature Descriptions

• Cipher-based MAC (AES-CMAC)

• Extended cipher block chaining message authentication code (AESXCBC-MAC)

• Auto padding

• Integrity Check Value(ICV) checking

• Authenticated encryption algorithms

• Counter with CBC-MAC (AES-CCM)

• Symmetric key block ciphers

• AES (128-bit keys)

• Cipher modes:

• AES-128 modes

• Electronic Codebook (ECB)

• Cipher Block Chaining (CBC)

• Counter (CTR)

• Secure scan

True Random Number Generator (TRNG)

True Random Number Generator (TRNG) is a hardware accelerator module that

constitutes a high-quality entropy source.

• TRNG generates a 512-bit (4x 128-bit) entropy as needed by an entropyconsuming module, such as a deterministic random number generator.

• TRNG output can be read and used by a deterministic pseudo-random number

generator (PRNG) implemented in software.

• TRNG-PRNG combination achieves NIST-compliant true randomness and

cryptographic-strength random numbers using the TRNG output as the entropy

source.

• A fully FIPS 180 compliant solution can be realized using the TRNG together

with a FIPS-compliant deterministic random number generator and the SoC-level

security.

Flash Memory Protection

The on-chip flash memory controller enables the following useful features:

• Program flash protection scheme prevents accidental program or erase of stored

data.

• Automated, built-in, program and erase algorithms with verify.

• Read access to one program flash block is possible while programming or erasing

data in the other program flash block.

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

15

NXP Semiconductors

�Transceiver Description

3 Transceiver Description

•

•

•

•

•

Direct Conversion Receiver (Zero IF)

Constant Envelope Transmitter

2.36 GHz to 2.483 GHz PLL Range

Low Transmit and Receive Current Consumption

Low BOM

3.1 Key Specifications

KW36Z/35Z meets or exceeds all Bluetooth Low Energy version 5.0 performance

specifications. The key specifications for the KW36Z/35Z are:

Frequency Band:

• ISM Band: 2400 to 2483.5 MHz

• MBAN Band: 2360 to 2400 MHz

Bluetooth Low Energy version 5.0 modulation scheme:

•

•

•

•

Symbol rate: 1000 kbit/s

Modulation: GFSK

Receiver sensitivity: –95 dBm, typical

Programmable transmitter output power: –30 dBm to +5 dBm

Generic FSK modulation scheme:

• Symbol rate: 250, 500 and 1000 kbit/s

• Modulation(s): GFSK (modulation index = 0.32, 0.5, 0.7 and 1.0, BT =0.3, 0.5, and

0.7), FSK and MSK

• Receiver Sensitivity: Mode and data rate dependent. –99 dBm typical for GFSK

(r=250 kbit/s, BT = 0.5, h = 0.5)

3.2 Channel Map Frequency Plans

16

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Transceiver Description

3.2.1 Channel Plan for Bluetooth Low Energy

This section describes the frequency plan / channels associated with 2.4 GHz ISM and

MBAN bands for Bluetooth Low Energy.

2.4 GHz ISM Channel numbering:

• Fc=2402 + k * 2 MHz, k=0,.........,39.

MBAN Channel numbering:

• Fc=2360 + k in MHz, for k=0,.....,39

where k is the channel number.

Table 1. 2.4 GHz ISM and MBAN frequency plan and channel designations

2.4 GHz ISM1

Channel

Freq (MHz)

MBAN2

2.4GHz ISM + MBAN

Channel

Freq (MHz)

Channel

Freq (MHz)

0

2402

0

2360

28

2390

1

2404

1

2361

29

2391

2

2406

2

2362

30

2392

3

2408

3

2363

31

2393

4

2410

4

2364

32

2394

5

2412

5

2365

33

2395

6

2414

6

2366

34

2396

7

2416

7

2367

35

2397

8

2418

8

2368

36

2398

9

2420

9

2369

0

2402

10

2422

10

2370

1

2404

11

2424

11

2371

2

2406

12

2426

12

2372

3

2408

13

2428

13

2373

4

2410

14

2430

14

2374

5

2412

15

2432

15

2375

6

2414

16

2434

16

2376

7

2416

17

2436

17

2377

8

2418

18

2438

18

2378

9

2420

19

2440

19

2379

10

2422

20

2442

20

2380

11

2424

21

2444

21

2381

12

2426

22

2446

22

2382

13

2428

23

2448

23

2383

14

2430

Table continues on the next page...

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

17

NXP Semiconductors

�Transceiver Description

Table 1. 2.4 GHz ISM and MBAN frequency plan and channel designations (continued)

2.4 GHz ISM1

MBAN2

2.4GHz ISM + MBAN

Channel

Freq (MHz)

Channel

Freq (MHz)

Channel

Freq (MHz)

24

2450

24

2384

15

2432

25

2452

25

2385

16

2434

26

2454

26

2386

17

2436

27

2456

27

2387

18

2438

28

2458

28

2388

19

2440

29

2460

29

2389

20

2442

30

2462

30

2390

21

2444

31

2464

31

2391

22

2446

32

2466

32

2392

23

2448

33

2468

33

2393

24

2450

34

2470

34

2394

25

2452

35

2472

35

2395

26

2454

36

2474

36

2396

27

2456

37

2476

37

2397

37

2476

38

2478

38

2398

38

2478

39

2480

39

2399

39

2480

1. ISM frequency of operation spans from 2400.0 MHz to 2483.5 MHz

2. Per FCC guideline rules, Bluetooth Low Energy single mode operation is allowed in these channels.

3.2.2 Other Channel Plans

The RF synthesizer can be configured to use any channel frequency between 2.36 and

2.487 GHz.

3.3 Transceiver Functions

Receive

The receiver architecture is Zero IF (ZIF) where the received signal after passing

through RF front end is down-converted to a baseband signal. The signal is filtered and

amplified before it is fed to analog-to-digital converter. The digital signal then

decimates to a baseband clock frequency before it digitally processes, demodulates and

passes on to packet processing/link-layer processing.

18

NXP Semiconductors

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

�Transceiver Electrical Characteristics

Transmit

The transmitter transmits GFSK/FSK modulation having power and channel selection

adjustment per user application. After the channel of operation is determined, coarse

and fine-tuning is executed within the Frac-N PLL to engage signal lock. After signal

lock is established, the modulated buffered signal is routed to a multi-stage amplifier

for transmission..

4 Transceiver Electrical Characteristics

4.1 Radio operating conditions

Table 2. Radio operating conditions

Characteristic

Symbol

Min

Input Frequency

fin

Ambient Temperature Range

TA

Pmax

Maximum RF Input Power

Crystal Reference Oscillator Frequency

Typ

Max

Unit

2.360

—

2.480

GHz

–40

25

105

°C

—

—

10

dBm

fref

26 MHz or 32 MHz

1

1. The recommended crystal accuracy is ±40 ppm including initial accuracy, mechanical, temperature, and aging factors.

4.2 Receiver Feature Summary

Table 3. Top-Level Receiver Specifications (TA=25 °C, nominal process unless otherwise

noted)

Characteristic1

Symbol

Min.

Typ.

Max.

Unit

Supply current power down on VDD_RFx supplies

Ipdn

—

200

1000

nA

Supply current Rx On with DC-DC converter enable

(Buck; VDCDC_IN = 3.6 V, VDD_1P5_buck=1.5 V) , 2

IRxon

—

6.3

—

mA

Supply current Rx On with DC-DC converter disabled

(Bypass) 2

IRxon

—

17.2

—

mA

fin

2.360

—

2.4835

GHz

SENSGFSK

—

–99

—

dBm

SENSBLE

—

–95

—

dBm

NFHG

—

7.5

—

dB

Input RF Frequency

GFSK Rx Sensitivity(250 kbit/s GFSK-BT=0.5, h=0.5)

Bluetooth LE Rx Sensitivity

3

Noise Figure for maximum gain mode @ typical

sensitivity

Table continues on the next page...

MKW36Z/35Z Data Sheet, Rev. 8, 05/2020

19

NXP Semiconductors

�Transceiver Electrical Characteristics

Table 3. Top-Level Receiver Specifications (TA=25 °C, nominal process unless otherwise

noted) (continued)

Characteristic1

Symbol

Min.

Typ.

Max.

Unit

RSSIRange

–100

—

55

dBm

RSSIRes

—

1

—

dB

Typical RSSI variation over frequency

–2

—

2

dB

Typical RSSI variation over temperature

–2

—

2

dB

–3

—

3

dB

Receiver Signal Strength Indicator Range4

Receiver Signal Strength Indicator Resolution

Narrowband RSSI

accuracy6

RSSIAcc

Bluetooth LE Co-channel Interference (Wanted signal at

–67 dBm, BER