Document Number: MPC8306SEC

Rev. 1, 09/2011

Freescale Semiconductor

Technical Data

MPC8306S

PowerQUICC II Pro Integrated

Communications Processor

Family Hardware Specifications

This document provides an overview of the MPC8306S

PowerQUICC II Pro processor features. The MPC8306S is

a cost-effective, highly integrated communications

processor that addresses the requirements of several

networking applications, including residential gateways,

modem/routers, industrial control, and test and measurement

applications. The MPC8306S extends current PowerQUICC

offerings, adding higher CPU performance, additional

functionality, and faster interfaces, while addressing the

requirements related to time-to-market, price, power

consumption, and board real estate. This document describes

the electrical characteristics of MPC8306S.

To locate published errata or updates for this document, refer

to the MPC8306S product summary page on our website

listed on the back cover of this document or contact your

local Freescale sales office.

© 2011 Freescale Semiconductor, Inc. All rights reserved.

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

Contents

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . 6

Power Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 10

Clock Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 11

RESET Initialization . . . . . . . . . . . . . . . . . . . . . . . . . 12

DDR2 SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Local Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Ethernet and MII Management . . . . . . . . . . . . . . . . . 21

TDM/SI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

HDLC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

DUART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

IPIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

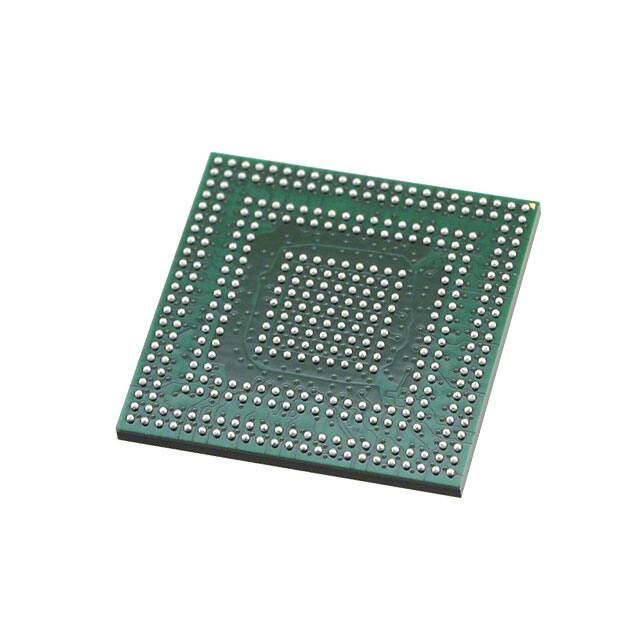

Package and Pin Listings . . . . . . . . . . . . . . . . . . . . . 44

Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Thermal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

System Design Information . . . . . . . . . . . . . . . . . . . 64

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 67

Document Revision History . . . . . . . . . . . . . . . . . . . 69

�Overview

1

Overview

The MPC8306S incorporates the e300c3 (MPC603e-based) core built on Power Architecture®

technology, which includes 16 Kbytes of each L1 instruction and data caches, dual integer units, and

on-chip memory management units (MMUs). The MPC8306S also includes two DMA engines and a

16-bit DDR2 memory controller.

A new communications complex based on QUICC Engine technology forms the heart of the networking

capability of the MPC8306S. The QUICC Engine block contains several peripheral controllers and a

32-bit RISC controller. Protocol support is provided by the main workhorses of the device—the unified

communication controllers (UCCs). A block diagram of the MPC8306S is shown in the following figure.

2 x DUART

I2C

Timers

GPIO

SPI

RTC

e300c3 Core with Power

Management

16-KB

I-Cache

Interrupt

Controller

16-KB

D-Cache

FPU

DDR2

Controller

16 KB Multi-User RAM

48 KB Instruction RAM

UCC7

UCC5

UCC3

UCC2

Single 32-bit RISC CP Serial DMA

UCC1

Baud Rate

Generators

Enhanced Local

USB 2.0 HS

Host/Device/OTG Bus Controller

DMA

Engine

QUICC Engine™ Block

Accelerators

ULPI

Time Slot Assigner

Serial Interface

2x TDM Ports

3 RMII/MII

2x HDLC

Figure 1. MPC8306S Block Diagram

Each of the five UCCs can support a variety of communication protocols such as 10/100 Mbps MII/RMII

Ethernet, HDLC and TDM.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

2

Freescale Semiconductor

�Overview

In summary, the MPC8306S provides users with a highly integrated, fully programmable communications

processor. This helps to ensure that a low-cost system solution can be quickly developed and offers

flexibility to accommodate new standards and evolving system requirements.

1.1

Features

The major features of the device are as follows:

• e300c3 Power Architecture processor core

— Enhanced version of the MPC603e core

— High-performance, superscalar processor core with a four-stage pipeline and low interrupt

latency times

— Floating-point, dual integer units, load/store, system register, and branch processing units

— 16-Kbyte instruction cache and 16-Kbyte data cache with lockable capabilities

— Dynamic power management

— Enhanced hardware program debug features

— Software-compatible with Freescale processor families implementing Power Architecture

technology

— Separate PLL that is clocked by the system bus clock

— Performance monitor

• QUICC Engine block

— 32-bit RISC controller for flexible support of the communications peripherals with the

following features:

– One clock per instruction

– Separate PLL for operating frequency that is independent of system’s bus and e300 core

frequency for power and performance optimization

– 32-bit instruction object code

– Executes code from internal IRAM

– 32-bit arithmetic logic unit (ALU) data path

– Modular architecture allowing for easy functional enhancements

– Slave bus for CPU access of registers and multiuser RAM space

– 48 Kbytes of instruction RAM

– 16 Kbytes of multiuser data RAM

– Serial DMA channel for receive and transmit on all serial channels

— Five unified communication controllers (UCCs) supporting the following protocols and

interfaces:

– 10/100 Mbps Ethernet/IEEE Std. 802.3® through MII and RMII interfaces.

– HDLC/Transparent (bit rate up to QUICC Engine operating frequency / 8)

– HDLC Bus (bit rate up to 10 Mbps)

– Asynchronous HDLC (bit rate up to 2 Mbps)

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

3

�Overview

•

•

•

– Two TDM interfaces supporting up to 128 QUICC multichannel controller channels, each

running at 64 kbps

For more information on QUICC Engine sub-modules, see QUICC Engine Block Reference

Manual with Protocol Interworking.

DDR SDRAM memory controller

— Programmable timing supporting DDR2 SDRAM

— Integrated SDRAM clock generation

— 16-bit data interface, up to 266-MHz data rate

— 14 address lines

— The following SDRAM configurations are supported:

– Up to two physical banks (chip selects), 256-Mbyte per chip select for 16 bit data interface.

– 64-Mbit to 2-Gbit devices with x8/x16 data ports (no direct x4 support)

– One 16-bit device or two 8-bit devices on a 16-bit bus,

— Support for up to 16 simultaneous open pages for DDR2

— One clock pair to support up to 4 DRAM devices

— Supports auto refresh

— On-the-fly power management using CKE

Enhanced local bus controller (eLBC)

— Multiplexed 26-bit address and 8-/16-bit data operating at up to 66 MHz

— Eight chip selects supporting eight external slaves

– Four chip selects dedicated

– Four chip selects offered as multiplexed option

— Supports boot from parallel NOR Flash and parallel NAND Flash

— Supports programmable clock ratio dividers

— Up to eight-beat burst transfers

— 16- and 8-bit ports, separate LWE for each 8 bit

— Three protocol engines available on a per chip select basis:

– General-purpose chip select machine (GPCM)

– Three user programmable machines (UPMs)

– NAND Flash control machine (FCM)

— Variable memory block sizes for FCM, GPCM, and UPM mode

— Default boot ROM chip select with configurable bus width (8 or 16)

— Provides two Write Enable signals to allow single byte write access to external 16-bit eLBC

slave devices

Integrated programmable interrupt controller (IPIC)

— Functional and programming compatibility with the MPC8260 interrupt controller

— Support for external and internal discrete interrupt sources

— Programmable highest priority request

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

4

Freescale Semiconductor

�Overview

•

•

•

•

•

•

— Six groups of interrupts with programmable priority

— External and internal interrupts directed to host processor

— Unique vector number for each interrupt source

Universal serial bus (USB) dual-role controller

— Designed to comply with Universal Serial Bus Revision 2.0 Specification

— Supports operation as a stand-alone USB host controller

— Supports operation as a stand-alone USB device

— Supports high-speed (480-Mbps), full-speed (12-Mbps), and low-speed (1.5-Mbps) operations.

Low speed is only supported in host mode.

Dual I2C interfaces

— Two-wire interface

— Multiple-master support

— Master or slave I2C mode support

— On-chip digital filtering rejects spikes on the bus

— I2C1 can be used as the boot sequencer

DMA Engine

— Support for the DMA engine with the following features:

– Sixteen DMA channels

– All data movement via dual-address transfers: read from source, write to destination

– Transfer control descriptor (TCD) organized to support two-deep, nested transfer operations

– Channel activation via one of two methods (for both the methods, one activation per

execution of the minor loop is required):

– Explicit software initiation

– Initiation via a channel-to-channel linking mechanism for continuous transfers

(independent channel linking at end of minor loop and/or major loop)

– Support for fixed-priority and round-robin channel arbitration

– Channel completion reported via optional interrupt requests

— Support for scatter/gather DMA processing

DUART

— Two 2-wire interfaces (RxD, TxD)

– The same can be configured as one 4-wire interface (RxD, TxD, RTS, CTS)

— Programming model compatible with the original 16450 UART and the PC16550D

Serial peripheral interface (SPI)

— Master or slave support

Power managemnt controller (PMC)

— Supports core doze/nap/sleep/ power management

— Exits low power state and returns to full-on mode when

– The core internal time base unit invokes a request to exit low power state

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

5

�Electrical Characteristics

•

•

•

•

2

– The power management controller detects that the system is not idle and there are

outstanding transactions on the internal bus or an external interrupt.

Parallel I/O

— General-purpose I/O (GPIO)

– 56 parallel I/O pins multiplexed on various chip interfaces

– Interrupt capability

System timers

— Periodic interrupt timer

— Software watchdog timer

— Eight general-purpose timers

Real time clock (RTC) module

— Maintains a one-second count, unique over a period of thousands of years

— Two possible clock sources:

– External RTC clock (RTC_PIT_CLK)

– CSB bus clock

IEEE Std. 1149.1™ compliant JTAG boundary scan

Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the

MPC8306S. The MPC8306S is currently targeted to these specifications. Some of these specifications are

independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer

design specifications.

2.1

Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

2.1.1

Absolute Maximum Ratings

The following table provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings1

Characteristic

Symbol

Max Value

Unit

Notes

Core supply voltage

VDD

–0.3 to 1.26

V

—

PLL supply voltage

AVDD1

AVDD2

AVDD3

–0.3 to 1.26

V

—

GVDD

–0.3 to 1.98

V

—

OVDD

–0.3 to 3.6

V

2

DDR2 DRAM I/O voltage

Local bus, DUART, system control and power management,

SPI, MII, RMII, MII management, USB and JTAG I/O voltage

I2C,

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

6

Freescale Semiconductor

�Electrical Characteristics

Table 1. Absolute Maximum Ratings1 (continued)

Characteristic

Input voltage

DDR2 DRAM signals

DDR2 DRAM reference

Local bus, DUART, SYS_CLK_IN,

system control and power

management, I2C, SPI, and JTAG

signals

Storage temperature range

Symbol

Max Value

Unit

Notes

MVIN

–0.3 to (GVDD + 0.3)

V

3

MVREF

–0.3 to (GVDD + 0.3)

V

3

OVIN

–0.3 to (OVDD + 0.3)

V

4

TSTG

–55 to 150

C

—

Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and

functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause

permanent damage to the device.

2. OVDD here refers to NVDDA, NVDDB, NVDDC, NVDDF, NVDDG, and NVDDH from the ball map.

3. Caution: MVIN must not exceed GVDD by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during

power-on reset and power-down sequences.

4. Caution: OVIN must not exceed OVDD by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during

power-on reset and power-down sequences.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

7

�Electrical Characteristics

2.1.2

Power Supply Voltage Specification

The following table provides the recommended operating conditions for the MPC8306S. Note that these

values are the recommended and tested operating conditions. Proper device operation outside of these

conditions is not guaranteed.

Table 2. Recommended Operating Conditions

Symbol

Recommended

Value

Unit

Note

Core supply voltage

VDD

1.0 V ± 50 mV

V

1

PLL supply voltage

AVDD1

AVDD2

AVDD3

1.0 V ± 50 mV

V

1

GVDD

1.8 V ± 100 mV

V

1

OVDD

3.3 V ± 300 mV

V

1, 3

TA/TJ

0 to 105

C

2

Characteristic

DDR2 DRAM I/O voltage

Local bus, DUART, system control and power management, I

SPI, MII, RMII, MII management, USB and JTAG I/O voltage

Junction temperature

2C,

Notes:

1. GVDD, OVDD, AVDD, and VDD must track each other and must vary in the same direction—either in the positive or negative

direction.

2. Minimum temperature is specified with TA(Ambient Temperature); maximum temperature is specified with TJ(Junction

Temperature).

3. OVDD here refers to NVDDA, NVDDB, NVDDC, NVDDF, NVDDG, and NVDDH from the ball map.

The following figure shows the undershoot and overshoot voltages at the interfaces of the MPC8306S

G/OVDD + 20%

G/OVDD + 5%

VIH

G/OVDD

GND

GND – 0.3 V

VIL

GND – 0.7 V

Not to Exceed 10%

of tinterface1

Note:

1. tinterface refers to the clock period associated with the bus clock interface.

Figure 2. Overshoot/Undershoot Voltage for GVDD/OVDD

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

8

Freescale Semiconductor

�Electrical Characteristics

2.1.3

Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

Output Impedance

()

Supply Voltage (V)

Local bus interface utilities signals

42

OVDD = 3.3

DDR2 signal

18

GVDD = 1.8

DUART, system control, I2C, SPI, JTAG

42

OVDD = 3.3

GPIO signals

42

OVDD = 3.3

Driver Type

2.1.4

Input Capacitance Specification

The following table describes the input capacitance for the SYS_CLK_IN pin in the MPC8306S.

Table 4. Input Capacitance Specification

Parameter/Condition

Input capacitance for all pins except SYS_CLK_IN and

QE_CLK_IN

Input capacitance for SYS_CLK_IN and QE_CLK_IN

Symbol

Min

Max

Unit

Note

CI

6

8

pF

—

CICLK_IN

10

—

pF

1

Note:

1. The external clock generator should be able to drive 10 pF.

2.2

Power Sequencing

The device does not require the core supply voltage (VDD) and I/O supply voltages (GVDD and OVDD) to

be applied in any particular order. Note that during power ramp-up, before the power supplies are stable

and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input

and output pins are actively driven and cause contention and excessive current. In order to avoid actively

driving the I/O pins and to eliminate excessive current draw, apply the core voltage (VDD) before the I/O

voltage (GVDD and OVDD) and assert PORESET before the power supplies fully ramp up. In the case

where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before

the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are

stable, wait for a minimum of 32 clock cycles before negating PORESET.

NOTE

There is no specific power down sequence requirement for the device. I/O

voltage supplies (GVDD and OVDD) do not have any ordering requirements

with respect to one another.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

9

�Power Characteristics

I/O Voltage (GVDD and OVDD)

V

Core Voltage (VDD)

0.7 V

90%

0

t

PORESET

>= 32 tSYS_CLK_IN

Figure 3. MPC8306S Power-Up Sequencing Example

3

Power Characteristics

The typical power dissipation for this family of MPC8306S devices is shown in the following table.

Table 5.

MPC8306S Power Dissipation

Core

Frequency (MHz)

QUICC Engine

Frequency (MHz)

CSB

Frequency (MHz)

Typical

Maximum

Unit

Note

133

133

133

0.272

0.618

W

1, 2, 3

200

233

133

0.291

0.631

W

1, 2, 3

266

233

133

0.451

0.925

W

1, 2, 3

333

233

133

0.471

0.950

W

1, 2, 3

Notes:

1. The values do not include I/O supply power (OVDD and GVDD), but it does include VDD and AVDD power. For I/O power

values, see Table 6.

2. Typical power is based on a nominal voltage of VDD = 1.0 V, ambient temperature, and the core running a Dhrystone

benchmark application. The measurements were taken on the evaluation board using WC process silicon.

3. Maximum power is based on a voltage of VDD = 1.05 V, WC process, a junction TJ = 105C, and a smoke test code.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

10

Freescale Semiconductor

�Clock Input Timing

The following table shows the estimated typical I/O power dissipation for the device.

Table 6. Typical I/O Power Dissipation

Interface

Parameter

DDR I/O

65% utilization

1.8 V

Rs = 20

Rt = 50

1 pair of clocks

266 MHz, 1 16 bits

Local bus I/O load = 25 pF

1 pair of clocks

66 MHz, 26 bits

QUICC Engine block and other I/Os

TDM serial, HDLC/TRAN serial,

DUART, MII, RMII, Ethernet

management, USB, SPI, Timer

output,

GVDD

(1.8 V)

OVDD

(3.3 V)

Unit

Comments

0.141

—

W

—

—

0.150

W

1

Note:

1. Typical I/O power is based on a nominal voltage of VDD = 3.3V, ambient temperature, and the core running a Dhrystone

benchmark application. The measurements were taken on the evaluation board using WC process silicon.

4

Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8306S.

NOTE

The rise/fall time on QUICC Engine input pins should not exceed 5 ns. This

should be enforced especially on clock signals. Rise time refers to signal

transitions from 10% to 90% of OVDD; fall time refers to transitions from

90% to 10% of OVDD.

4.1

DC Electrical Characteristics

The following table provides the clock input (SYS_CLK_IN) DC specifications for the MPC8306S. These

specifications are also applicable for QE_CLK_IN.

Table 7. SYS_CLK_IN DC Electrical Characteristics

Parameter

Condition

Symbol

Min

Max

Unit

Input high voltage

—

VIH

2.4

OVDD + 0.3

V

Input low voltage

—

VIL

–0.3

0.4

V

SYS_CLK_IN input current

0 V VIN OVDD

IIN

—

±5

A

SYS_CLK_IN input current

0 V VIN 0.5 V or

OVDD – 0.5 V VIN OVDD

IIN

—

±5

A

SYS_CLK_IN input current

0.5 V VIN OVDD – 0.5 V

IIN

—

±50

A

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

11

�RESET Initialization

4.2

AC Electrical Characteristics

The primary clock source for the MPC8306S is SYS_CLK_IN. The following table provides the clock

input (SYS_CLK_IN) AC timing specifications for the MPC8306S. These specifications are also

applicable for QE_CLK_IN.

Table 8. SYS_CLK_IN AC Timing Specifications

Parameter/Condition

Symbol

Min

Typical

Max

Unit

Note

SYS_CLK_IN frequency

fSYS_CLK_IN

24

—

66.67

MHz

1

SYS_CLK_IN cycle time

tSYS_CLK_IN

15

—

41.6

ns

—

tKH, tKL

1.1

—

2.8

ns

2

tKHK/tSYS_CLK_

40

—

60

%

3

—

—

±150

ps

4, 5

SYS_CLK_IN rise and fall time

SYS_CLK_IN duty cycle

IN

SYS_CLK_IN jitter

—

Notes:

1. Caution: The system, core and QUICC Engine block must not exceed their respective maximum or minimum operating

frequencies.

2. Rise and fall times for SYS_CLK_IN are measured at 0.33 and 2.97 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter—short term and long term—and is guaranteed by design.

5. The SYS_CLK_IN driver’s closed loop jitter bandwidth should be < 500 kHz at –20 dB. The bandwidth must be set low to

allow cascade-connected PLL-based devices to track SYS_CLK_IN drivers with the specified jitter.

6. Spread spectrum is allowed up to 1% down-spread @ 33kHz (max rate).

5

RESET Initialization

This section describes the AC electrical specifications for the reset initialization timing requirements of

the MPC8306S. The following table provides the reset initialization AC timing specifications for the reset

component(s).

Table 9. RESET Initialization Timing Specifications

Parameter/Condition

Min

Max

Unit

Note

Required assertion time of HRESET to activate reset flow

32

—

tSYS_CLK_IN

1

Required assertion time of PORESET with stable clock applied to

SYS_CLK_IN

32

—

tSYS_CLK_IN

1

HRESET assertion (output)

512

—

tSYS_CLK_IN

1

Input setup time for POR configuration signals

(CFG_RESET_SOURCE[0:3]) with respect to negation of PORESET

4

—

tSYS_CLK_IN

1, 2

Input hold time for POR config signals with respect to negation of

HRESET

0

—

ns

1, 2

Notes:

1. tSYS_CLK_IN is the clock period of the input clock applied to SYS_CLK_IN. For more details, see the MPC8306S PowerQUICC

II Pro Integrated Communications Processor Family Reference Manual.

2. POR configuration signals consist of CFG_RESET_SOURCE[0:3].

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

12

Freescale Semiconductor

�DDR2 SDRAM

The following table provides the PLL lock times.

Table 10. PLL Lock Times

Parameter/Condition

Min

Max

Unit

Note

—

100

s

—

PLL lock times

5.1

Reset Signals DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S reset signals mentioned

in Table 9.

Table 11. Reset Signals DC Electrical Characteristics

Characteristic

Symbol

Condition

Min

Max

Unit

Note

Output high voltage

VOH

IOH = –6.0 mA

2.4

—

V

1

Output low voltage

VOL

IOL = 6.0 mA

—

0.5

V

1

Output low voltage

VOL

IOL = 3.2 mA

—

0.4

V

1

Input high voltage

VIH

—

2.0

OVDD + 0.3

V

1

Input low voltage

VIL

—

–0.3

0.8

V

—

Input current

IIN

0 V VIN OVDD

—

±5

A

—

Note:

1. This specification applies when operating from 3.3 V supply.

6

DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR2 SDRAM interface of the

MPC8306S. Note that DDR2 SDRAM is GVDD(typ) = 1.8 V.

6.1

DDR2 SDRAM DC Electrical Characteristics

The following table provides the recommended operating conditions for the DDR2 SDRAM component(s)

of the MPC8306S when GVDD(typ) = 1.8 V.

Table 12. DDR2 SDRAM DC Electrical Characteristics for GVDD(typ) = 1.8 V

Parameter/Condition

Symbol

Min

Max

Unit

Note

GVDD

1.7

1.9

V

1

MVREF

0.49 GVDD

0.51 GVDD

V

2

I/O termination voltage

VTT

MVREF – 0.04

MVREF + 0.04

V

3

Input high voltage

VIH

MVREF+ 0.125

GVDD + 0.3

V

—

Input low voltage

VIL

–0.3

MVREF – 0.125

V

—

Output leakage current

IOZ

–9.9

9.9

A

4

I/O supply voltage

I/O reference voltage

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

13

�DDR2 SDRAM

Table 12. DDR2 SDRAM DC Electrical Characteristics for GVDD(typ) = 1.8 V (continued)

Parameter/Condition

Symbol

Min

Max

Unit

Note

Output high current (VOUT = 1.35 V)

IOH

–13.4

—

mA

—

Output low current (VOUT = 0.280 V)

IOL

13.4

—

mA

—

Notes:

1. GVDD is expected to be within 50 mV of the DRAM GVDD at all times.

2. MVREF is expected to be equal to 0.5 GVDD, and to track GVDD DC variations as measured at the receiver. Peak-to-peak

noise on MVREF may not exceed ±2% of the DC value.

3. VTT is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be

equal to MVREF. This rail should track variations in the DC level of MVREF.

4. Output leakage is measured with all outputs disabled, 0 V VOUT GVDD.

The following table provides the DDR2 capacitance when GVDD(typ) = 1.8 V.

Table 13. DDR2 SDRAM Capacitance for GVDD(typ) = 1.8 V

Parameter/Condition

Symbol

Min

Max

Unit

Note

Input/output capacitance: DQ, DQS

CIO

6

8

pF

1

Delta input/output capacitance: DQ, DQS

CDIO

—

0.5

pF

1

Note:

1. This parameter is sampled. GVDD = 1.8 V ± 0.100 V, f = 1 MHz, TA = 25 °C, VOUT = GVDD 2,

VOUT (peak-to-peak) = 0.2 V.

6.2

DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR2 SDRAM interface.

6.2.1

DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM (GVDD(typ) = 1.8 V).

Table 14. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with GVDD of 1.8 V± 100mV.

Parameter

Symbol

Min

Max

Unit

Note

AC input low voltage

VIL

—

MVREF – 0.25

V

—

AC input high voltage

VIH

MVREF + 0.25

—

V

—

The following table provides the input AC timing specifications for the DDR2 SDRAM interface.

Table 15. DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions with GVDD of 1.8V ± 100mV.

Parameter

Controller skew for MDQS—MDQ/MDM

Symbol

tCISKEW

Min

Max

Unit

Note

ps

1, 2

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

14

Freescale Semiconductor

�DDR2 SDRAM

Table 15. DDR2 SDRAM Input AC Timing Specifications (continued)

At recommended operating conditions with GVDD of 1.8V ± 100mV.

Parameter

Symbol

266 MHz

Min

Max

–750

750

Unit

Note

Notes:

1. tCISKEW represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that

is captured with MDQS[n]. This should be subtracted from the total timing budget.

2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called tDISKEW. This can be

determined by the equation: tDISKEW = ±(T/4 – abs(tCISKEW)) where T is the clock period and abs(tCISKEW) is the absolute

value of tCISKEW.

The following figure shows the input timing diagram for the DDR controller.

MCK[n]

MCK[n]

tMCK

MDQS[n]

MDQ[x]

D0

D1

tDISKEW

tDISKEW

Figure 4. DDR Input Timing Diagram

6.2.2

DDR2 SDRAM Output AC Timing Specifications

The following table provides the output AC timing specifications for the DDR2 SDRAM interfaces.

Table 16. DDR2 SDRAM Output AC Timing Specifications

At recommended operating conditions with GVDD of 1.8V ± 100mV.

Parameter

MCK cycle time, (MCK/MCK crossing)

ADDR/CMD output setup with respect to MCK

Symbol1

Min

Max

Unit

Note

tMCK

5.988

8

ns

2

ns

3

2.5

—

ns

3

2.5

—

ns

3

tDDKHAS

266 MHz

ADDR/CMD output hold with respect to MCK

tDDKHAX

266 MHz

MCS output setup with respect to MCK

tDDKHCS

266 MHz

2.5

—

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

15

�DDR2 SDRAM

Table 16. DDR2 SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions with GVDD of 1.8V ± 100mV.

Symbol1

Parameter

MCS output hold with respect to MCK

Min

Max

2.5

—

–0.6

0.6

tDDKHCX

266 MHz

MCK to MDQS Skew

tDDKHMH

MDQ/MDM output setup with respect to MDQS

tDDKHDS,

tDDKLDS

266 MHz

MDQ/MDM output hold with respect to MDQS

0.9

Note

ns

3

ns

4

ns

5

ps

5

—

tDDKHDX,

tDDKLDX

266 MHz

Unit

1100

—

MDQS preamble start

tDDKHMP

0.75 x tMCK

—

ns

6

MDQS epilogue end

tDDKHME

0.4 x tMCK

0.6 x tMCK

ns

6

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing

(DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example,

tDDKHAS symbolizes DDR timing (DD) for the time tMCK memory clock reference (K) goes from the high (H) state until outputs

(A) are setup (S) or output valid time. Also, tDDKLDX symbolizes DDR timing (DD) for the time tMCK memory clock reference

(K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MDM/MDQS. For the ADDR/CMD

setup and hold specifications, it is assumed that the Clock Control register is set to adjust the memory clocks by 1/2 applied

cycle.

4. Note that tDDKHMH follows the symbol conventions described in note 1. For example, tDDKHMH describes the DDR timing (DD)

from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). tDDKHMH can be modified through control

of the DQSS override bits in the TIMING_CFG_2 register. This is typically set to the same delay as the clock adjusts in the

CLK_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same

adjustment value. See the MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference

Manual for a description and understanding of the timing modifications enabled by use of these bits.

5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), or data

mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

6. tDDKHMP follows the symbol conventions described in note 1.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

16

Freescale Semiconductor

�DDR2 SDRAM

The following figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement

(tDDKHMH).

MCK

MCK

tMCK

tDDKHMH(max) = 0.6 ns

MDQS

tDDKHMH(min) = –0.6 ns

MDQS

Figure 5. Timing Diagram for tDDKHMH

The following figure shows the DDR2 SDRAM output timing diagram.

MCK[n]

MCK[n]

tMCK

tDDKHAS ,tDDKHCS

tDDKHAX ,tDDKHCX

ADDR/CMD

Write A0

NOOP

tDDKHMP

tDDKHMH

MDQS[n]

tDDKHME

tDDKHDS

tDDKLDS

MDQ[x]/

MECC[x]

D0

D1

tDDKLDX

tDDKHDX

Figure 6. DDR2 SDRAM Output Timing Diagram

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

17

�Local Bus

7

Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the

MPC8306S.

7.1

Local Bus DC Electrical Characteristics

The following table provides the DC electrical characteristics for the local bus interface.

Table 17. Local Bus DC Electrical Characteristics

Parameter

Symbol

Min

Max

Unit

High-level input voltage

VIH

2

OVDD + 0.3

V

Low-level input voltage

VIL

–0.3

0.8

V

High-level output voltage, IOH = –100 A

VOH

OVDD – 0.2

—

V

Low-level output voltage, IOL = 100 A

VOL

—

0.2

V

IIN

—

±5

A

Input current

7.2

Local Bus AC Electrical Specifications

The following table describes the general timing parameters of the local bus interface of the MPC8306S.

Table 18. Local Bus General Timing Parameters

Symbol1

Min

Max

Unit

Note

tLBK

15

—

ns

2

Input setup to local bus clock (LCLKn)

tLBIVKH

7

—

ns

3, 4

Input hold from local bus clock (LCLKn)

tLBIXKH

1.0

—

ns

3, 4

Local bus clock (LCLKn) to output valid

tLBKHOV

—

3

ns

3

Local bus clock (LCLKn) to output high impedance for LAD/LDP

tLBKHOZ

—

4

ns

5

Parameter

Local bus cycle time

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tLBIXKH1 symbolizes local bus

timing (LB) for the input (I) to go invalid (X) with respect to the time the tLBK clock reference (K) goes high (H), in this case

for clock one(1).

2. All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of

LCLK0 (for all other inputs).

3. All signals are measured from OVDD/2 of the rising/falling edge of LCLK0 to 0.4 OVDD of the signal in question for 3.3-V

signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered

through the component pin is less than or equal to the leakage current specification.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

18

Freescale Semiconductor

�Local Bus

The following figure provides the AC test load for the local bus.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 7. Local Bus AC Test Load

The following figures show the local bus signals. These figures has been given indicate timing parameters

only and do not reflect actual functional operation of interface.

LCLK[n]

tLBIVKH

Input Signals:

LAD[0:15]

tLBIXKH

tLBIVKH

Input Signal:

LGTA

tLBIXKH

tLBIXKH

tLBKHOV

Output Signals:

LBCTL/LBCKE/LOE

tLBKHOV

tLBKHOZ

Output Signals:

LAD[0:15]

tLBOTOT

LALE

Figure 8. Local Bus Signals

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

19

�Local Bus

LCLK

T1

T3

tLBKHOV

tLBKHOZ

GPCM Mode Output Signals:

LCS[0:3]/LWE

tLBIVKH

tLBIXKH

UPM Mode Input Signal:

LUPWAIT

tLBIXKH

tLBIVKH

Input Signals:

LAD[0:15]/LDP[0:3]

tLBKHOV

tLBKHOZ

UPM Mode Output Signals:

LCS[0:3]/LBS[0:1]/LGPL[0:5]

Figure 9. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

20

Freescale Semiconductor

�Ethernet and MII Management

LCLK

T1

T2

T3

T4

tLBKHOZ

tLBKHOV

GPCM Mode Output Signals:

LCS[0:3]/LWE

tLBIVKH

tLBIXKH

UPM Mode Input Signal:

LUPWAIT

tLBIVKH

tLBIXKH

Input Signals:

LAD[0:15]

tLBKHOV

tLBKHOZ

UPM Mode Output Signals:

LCS[0:3]/LBS[0:1]/LGPL[0:5]

Figure 10. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4

8

Ethernet and MII Management

This section provides the AC and DC electrical characteristics for Ethernet interfaces.

8.1

Ethernet Controller (10/100 Mbps)—MII/RMII Electrical

Characteristics

The electrical characteristics specified here apply to all MII (media independent interface) and RMII

(reduced media independent interface), except MDIO (management data input/output) and MDC

(management data clock). The MII and RMII are defined for 3.3 V. The electrical characteristics for MDIO

and MDC are specified in Section 8.3, “Ethernet Management Interface Electrical Characteristics.”

8.1.1

DC Electrical Characteristics

All MII and RMII drivers and receivers comply with the DC parametric attributes specified in The

following table.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

21

�Ethernet and MII Management

Table 19. MII and RMII DC Electrical Characteristics

Parameter

Symbol

Conditions

Min

Max

Unit

Supply voltage 3.3 V

OVDD

—

3

3.6

V

Output high voltage

VOH

IOH = –4.0 mA

OVDD = Min

2.40

OVDD + 0.3

V

Output low voltage

VOL

IOL = 4.0 mA

OVDD = Min

GND

0.50

V

Input high voltage

VIH

—

—

2.0

OVDD + 0.3

V

Input low voltage

VIL

—

—

–0.3

0.90

V

Input current

IIN

0 V VIN OVDD

—

±5

A

8.2

MII and RMII AC Timing Specifications

The AC timing specifications for MII and RMII are presented in this section.

8.2.1

MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

8.2.1.1

MII Transmit AC Timing Specifications

The following table provides the MII transmit AC timing specifications.

Table 20. MII Transmit AC Timing Specifications

At recommended operating conditions with OVDD of 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

TX_CLK clock period 10 Mbps

tMTX

—

400

—

ns

TX_CLK clock period 100 Mbps

tMTX

—

40

—

ns

tMTXH/tMTX

35

—

65

%

tMTKHDX

1

5

15

ns

TX_CLK data clock rise VIL(min) to VIH(max)

tMTXR

1.0

—

4.0

ns

TX_CLK data clock fall VIH(max) to VIL(min)

tMTXF

1.0

—

4.0

ns

Parameter/Condition

TX_CLK duty cycle

TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay

Note:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tMTKHDX symbolizes MII transmit

timing (MT) for the time tMTX clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general,

the clock reference symbol representation is based on two to three letters representing the clock of a particular functional.

For example, the subscript of tMTX represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is

used with the appropriate letter: R (rise) or F (fall).

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

22

Freescale Semiconductor

�Ethernet and MII Management

The following figure provides the AC test load.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 11. AC Test Load

The following figure shows the MII transmit AC timing diagram.

tMTXR

tMTX

TX_CLK

tMTXH

tMTXF

TXD[3:0]

TX_EN

TX_ER

tMTKHDX

Figure 12. MII Transmit AC Timing Diagram

8.2.1.2

MII Receive AC Timing Specifications

The following table provides the MII receive AC timing specifications.

Table 21. MII Receive AC Timing Specifications

At recommended operating conditions with OVDD of 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

RX_CLK clock period 10 Mbps

tMRX

—

400

—

ns

RX_CLK clock period 100 Mbps

tMRX

—

40

—

ns

tMRXH/tMRX

35

—

65

%

RXD[3:0], RX_DV, RX_ER setup time to RX_CLK

tMRDVKH

10.0

—

—

ns

RXD[3:0], RX_DV, RX_ER hold time to RX_CLK

tMRDXKH

10.0

—

—

ns

RX_CLK clock rise VIL(min) to VIH(max)

tMRXR

1.0

—

4.0

ns

RX_CLK clock fall time VIH(max) to VIL(min)

tMRXF

1.0

—

4.0

ns

Parameter/Condition

RX_CLK duty cycle

Note:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tMRDVKH symbolizes MII receive

timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the tMRX clock reference (K)

going to the high (H) state or setup time. Also, tMRDXKL symbolizes MII receive timing (GR) with respect to the time data input

signals (D) went invalid (X) relative to the tMRX clock reference (K) going to the low (L) state or hold time. Note that, in general,

the clock reference symbol representation is based on three letters representing the clock of a particular functional. For

example, the subscript of tMRX represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used

with the appropriate letter: R (rise) or F (fall).

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

23

�Ethernet and MII Management

The following figure shows the MII receive AC timing diagram.

tMRXR

tMRX

RX_CLK

tMRXF

tMRXH

RXD[3:0]

RX_DV

RX_ER

Valid Data

tMRDVKH

tMRDXKH

Figure 13. MII Receive AC Timing Diagram

8.2.2

RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

8.2.2.1

RMII Transmit AC Timing Specifications

The following table provides the RMII transmit AC timing specifications.

Table 22. RMII Transmit AC Timing Specifications

At recommended operating conditions with OVDD of 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

tRMX

—

20

—

ns

tRMXH/tRMX

35

—

65

%

REF_CLK to RMII data TXD[1:0], TX_EN delay

tRMTKHDX

2

—

13

ns

REF_CLK data clock rise VIL(min) to VIH(max)

tRMXR

1.0

—

4.0

ns

REF_CLK data clock fall VIH(max) to VIL(min)

tRMXF

1.0

—

4.0

ns

Parameter/Condition

REF_CLK clock

REF_CLK duty cycle

Note:

1. The symbols used for timing specifications follow the pattern of t(first three letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tRMTKHDX symbolizes RMII

transmit timing (RMT) for the time tRMX clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in

general, the clock reference symbol representation is based on two to three letters representing the clock of a particular

functional. For example, the subscript of tRMX represents the RMII(RM) reference (X) clock. For rise and fall times, the latter

convention is used with the appropriate letter: R (rise) or F (fall).

The following figure provides the AC test load.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 14. AC Test Load

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

24

Freescale Semiconductor

�Ethernet and MII Management

The following figure shows the RMII transmit AC timing diagram.

tRMXR

tRMX

REF_CLK

tRMXH

tRMXF

TXD[1:0]

TX_EN

tRMTKHDX

Figure 15. RMII Transmit AC Timing Diagram

8.2.2.2

RMII Receive AC Timing Specifications

The following table provides the RMII receive AC timing specifications.

Table 23. RMII Receive AC Timing Specifications

At recommended operating conditions with OVDD of 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

tRMX

—

20

—

ns

tRMXH/tRMX

35

—

65

%

RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK

tRMRDVKH

4.0

—

—

ns

RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK

tRMRDXKH

2.0

—

—

ns

REF_CLK clock rise VIL(min) to VIH(max)

tRMXR

1.0

—

4.0

ns

REF_CLK clock fall time VIH(max) to VIL(min)

tRMXF

1.0

—

4.0

ns

Parameter/Condition

REF_CLK clock period

REF_CLK duty cycle

Note:

1. The symbols used for timing specifications follow the pattern of t(first three letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tRMRDVKH symbolizes RMII

receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the tRMX clock

reference (K) going to the high (H) state or setup time. Also, tRMRDXKL symbolizes RMII receive timing (RMR) with respect

to the time data input signals (D) went invalid (X) relative to the tRMX clock reference (K) going to the low (L) state or hold

time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a

particular functional. For example, the subscript of tRMX represents the RMII (RM) reference (X) clock. For rise and fall times,

the latter convention is used with the appropriate letter: R (rise) or F (fall).

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

25

�Ethernet and MII Management

The following figure shows the RMII receive AC timing diagram.

tRMXR

tRMX

REF_CLK

tRMXF

tRMXH

RXD[1:0]

CRS_DV

RX_ER

Valid Data

tRMRDVKH

tRMRDXKH

Figure 16. RMII Receive AC Timing Diagram

8.3

Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO

(management data input/output) and MDC (management data clock). The electrical characteristics for

MII, and RMII are specified in Section 8.1, “Ethernet Controller (10/100 Mbps)—MII/RMII Electrical

Characteristics.”

8.3.1

MII Management DC Electrical Characteristics

MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for

MDIO and MDC are provided in the following table.

Table 24. MII Management DC Electrical Characteristics When Powered at 3.3 V

Parameter

Supply voltage (3.3 V)

Symbol

Conditions

Min

Max

Unit

OVDD

—

3

3.6

V

Output high voltage

VOH

IOH = –1.0 mA

OVDD = Min

2.40

OVDD + 0.3

V

Output low voltage

VOL

IOL = 1.0 mA

OVDD = Min

GND

0.50

V

Input high voltage

VIH

—

2.00

—

V

Input low voltage

VIL

—

—

0.80

V

Input current

IIN

0 V VIN OVDD

—

±5

A

8.3.2

MII Management AC Electrical Specifications

The following table provides the MII management AC timing specifications.

Table 25. MII Management AC Timing Specifications

At recommended operating conditions with OVDD is 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

Note

MDC frequency

fMDC

—

2.5

—

MHz

—

MDC period

tMDC

—

400

—

ns

—

MDC clock pulse width high

tMDCH

32

—

—

ns

—

Parameter/Condition

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

26

Freescale Semiconductor

�Ethernet and MII Management

Table 25. MII Management AC Timing Specifications (continued)

At recommended operating conditions with OVDD is 3.3 V ± 300mV.

Symbol1

Min

Typical

Max

Unit

Note

MDC to MDIO delay

tMDKHDX

10

—

70

ns

—

MDIO to MDC setup time

tMDDVKH

8.5

—

—

ns

—

MDIO to MDC hold time

tMDDXKH

0

—

—

ns

—

MDC rise time

tMDCR

—

—

10

ns

—

MDC fall time

tMDHF

—

—

10

ns

—

Parameter/Condition

Note:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tMDKHDX symbolizes

management data timing (MD) for the time tMDC from clock reference (K) high (H) until data outputs (D) are invalid (X) or data

hold time. Also, tMDDVKH symbolizes management data timing (MD) with respect to the time data input signals (D) reach the

valid state (V) relative to the tMDC clock reference (K) going to the high (H) state or setup time. For rise and fall times, the

latter convention is used with the appropriate letter: R (rise) or F (fall).

The following figure shows the MII management AC timing diagram.

tMDC

tMDCR

MDC

tMDCH

tMDCF

MDIO

(Input)

tMDDVKH

tMDDXKH

MDIO

(Output)

tMDKHDX

Figure 17. MII Management Interface Timing Diagram

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

27

�TDM/SI

9

TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial

interface of the MPC8306S.

9.1

TDM/SI DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S TDM/SI.

Table 26. TDM/SI DC Electrical Characteristics

Characteristic

Symbol

Condition

Min

Max

Unit

Output high voltage

VOH

IOH = –2.0 mA

2.4

—

V

Output low voltage

VOL

IOL = 3.2 mA

—

0.5

V

Input high voltage

VIH

—

2.0

OVDD + 0.3

V

Input low voltage

VIL

—

–0.3

0.8

V

Input current

IIN

0 V VIN OVDD

—

±5

A

9.2

TDM/SI AC Timing Specifications

The following table provides the TDM/SI input and output AC timing specifications.

Table 27. TDM/SI AC Timing Specifications1

Symbol2

Min

Max

Unit

TDM/SI outputs—External clock delay

tSEKHOV

2

14

ns

TDM/SI outputs—External clock High Impedance

tSEKHOX

2

10

ns

TDM/SI inputs—External clock input setup time

tSEIVKH

5

—

ns

TDM/SI inputs—External clock input hold time

tSEIXKH

2

—

ns

Characteristic

Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE_CLK_IN to the 50% level of the signal.

Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tSEKHOX symbolizes the TDM/SI

outputs external timing (SE) for the time tTDM/SI memory clock reference (K) goes from the high state (H) until outputs (O)

are invalid (X).

The following figure provides the AC test load for the TDM/SI.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 18. TDM/SI AC Test Load

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

28

Freescale Semiconductor

�HDLC

The following figure represents the AC timing from Table 27. Note that although the specifications

generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge

is the active edge.

TDM/SICLK (Input)

tSEIXKH

tSEIVKH

Input Signals:

TDM/SI

(See Note)

tSEKHOV

Output Signals:

TDM/SI

(See Note)

tSEKHOX

Note: The clock edge is selectable on TDM/SI.

Figure 19. TDM/SI AC Timing (External Clock) Diagram

10 HDLC

This section describes the DC and AC electrical specifications for the high level data link control (HDLC),

of the MPC8306S.

10.1

HDLC DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S HDLC protocol.

Table 28. HDLC DC Electrical Characteristics

Characteristic

Symbol

Condition

Min

Max

Unit

Output high voltage

VOH

IOH = –2.0 mA

2.4

—

V

Output low voltage

VOL

IOL = 3.2 mA

—

0.5

V

Input high voltage

VIH

—

2.0

OVDD + 0.3

V

Input low voltage

VIL

—

–0.3

0.8

V

Input current

IIN

0 V VIN OVDD

—

±5

A

10.2

HDLC AC Timing Specifications

The following table provides the input and output AC timing specifications for HDLC protocol.

Table 29. HDLC AC Timing Specifications1

Symbol2

Min

Max

Unit

Outputs—Internal clock delay

tHIKHOV

0

9

ns

Outputs—External clock delay

tHEKHOV

1

12

ns

Outputs—Internal clock high impedance

tHIKHOX

0

5.5

ns

Characteristic

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

29

�HDLC

Table 29. HDLC AC Timing Specifications1 (continued)

Symbol2

Min

Max

Unit

tHEKHOX

1

8

ns

Inputs—Internal clock input setup time

tHIIVKH

9

—

ns

Inputs—External clock input setup time

tHEIVKH

4

—

ns

Inputs—Internal clock input hold time

tHIIXKH

0

—

ns

Inputs—External clock input hold time

tHEIXKH

1

—

ns

Characteristic

Outputs—External clock high impedance

Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE_CLK_IN to the 50% level of the signal.

Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tHIKHOX symbolizes the outputs

internal timing (HI) for the time tserial memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

The following figure provides the AC test load.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 20. AC Test Load

Figure 21 and Figure 22 represent the AC timing from Table 29. Note that although the specifications

generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge

is the active edge.

The following figure shows the timing with external clock.

Serial CLK (Input)

tHEIVKH

tHEIXKH

Input Signals:

(See Note)

tHEKHOV

Output Signals:

(See Note)

tHEKHOX

Note: The clock edge is selectable.

Figure 21. AC Timing (External Clock) Diagram

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

30

Freescale Semiconductor

�USB

The following figure shows the timing with internal clock.

Serial CLK (Output)

tHIIVKH

tHIIXKH

Input Signals:

(See Note)

tHIKHOV

Output Signals:

(See Note)

Note: The clock edge is selectable.

tHIKHOX

Figure 22. AC Timing (Internal Clock) Diagram

11 USB

11.1

USB Controller

This section provides the AC and DC electrical specifications for the USB (ULPI) interface.

11.1.1

USB DC Electrical Characteristics

The following table provides the DC electrical characteristics for the USB interface.

Table 30. USB DC Electrical Characteristics

Parameter

Symbol

Min

Max

Unit

High-level input voltage

VIH

2.0

OVDD + 0.3

V

Low-level input voltage

VIL

–0.3

0.8

V

Input current

IIN

—

±5

A

High-level output voltage, IOH = –100 A

VOH

OVDD – 0.2

—

V

Low-level output voltage, IOL = 100 A

VOL

—

0.2

V

11.1.2

USB AC Electrical Specifications

The following table describes the general timing parameters of the USB interface.

Table 31. USB General Timing Parameters

Symbol1

Min

Max

Unit

Note

tUSCK

15

—

ns

—

Input setup to USB clock—all inputs

tUSIVKH

4

—

ns

—

input hold to USB clock—all inputs

tUSIXKH

1

—

ns

—

USB clock to output valid—all outputs (except

USBDR_STP_USBDR_STP)

tUSKHOV

—

7

ns

—

Parameter

USB clock cycle time

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

31

�USB

Table 31. USB General Timing Parameters (continued)

Symbol1

Min

Max

Unit

Note

USB clock to output valid—USBDR_STP

tUSKHOV

—

7.5

ns

—

Output hold from USB clock—all outputs

tUSKHOX

2

—

ns

—

Parameter

Note:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tUSIXKH symbolizes USB timing

(USB) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, tUSKHOX

symbolizes us timing (USB) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or

output hold time.

The following figures provide the AC test load and signals for the USB, respectively.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 23. USB AC Test Load

USBDR_CLK

tUSIVKH

tUSIXKH

Input Signals

tUSKHOV

tUSKHOX

Output Signals

Figure 24. USB Signals

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

32

Freescale Semiconductor

�DUART

12 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8306S.

12.1

DUART DC Electrical Characteristics

The following table provides the DC electrical characteristics for the DUART interface of the MPC8306S.

Table 32. DUART DC Electrical Characteristics

Parameter

Symbol

Min

Max

Unit

High-level input voltage

VIH

2

OVDD + 0.3

V

Low-level input voltage OVDD

VIL

–0.3

0.8

V

High-level output voltage, IOH = –100 A

VOH

OVDD – 0.2

—

V

Low-level output voltage, IOL = 100 A

VOL

—

0.2

V

IIN

—

±5

A

Input current (0 V VIN OVDD

)1

Note:

1. Note that the symbol VIN, in this case, represents the OVIN symbol referenced in Table 1 and Table 2.

12.2

DUART AC Electrical Specifications

The following table provides the AC timing parameters for the DUART interface of the MPC8306S.

Table 33. DUART AC Timing Specifications

Parameter

Value

Unit

Note

Minimum baud rate

256

baud

—

Maximum baud rate

>1,000,000

baud

1

16

—

2

Oversample rate

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8th sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are

sampled each 16th sample.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

33

�I2 C

13 I2C

This section describes the DC and AC electrical characteristics for the I2C interface of the MPC8306S.

13.1

I2C DC Electrical Characteristics

The following table provides the DC electrical characteristics for the I2C interface of the MPC8306S.

Table 34. I2C DC Electrical Characteristics

At recommended operating conditions with OVDD of 3.3 V ± 300mV.

Parameter

Symbol

Min

Max

Unit

Notes

Input high voltage level

VIH

0.7 OVDD

OVDD + 0.3

V

—

Input low voltage level

VIL

–0.3

0.3 OVDD

V

—

Low level output voltage

VOL

0

0.4

V

1

Output fall time from VIH(min) to VIL(max) with a bus

capacitance from 10 to 400 pF

tI2KLKV

20 + 0.1 CB

250

ns

2

Pulse width of spikes which must be suppressed by the

input filter

tI2KHKL

0

50

ns

3

Capacitance for each I/O pin

CI

—

10

pF

—

Input current (0 V VIN OVDD)

IIN

—

±5

A

4

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. CB = capacitance of one bus line in pF.

3. Refer to the MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual for information

on the digital filter used.

4. I/O pins obstructs the SDA and SCL lines if OVDD is switched off.

13.2

I2C AC Electrical Specifications

The following table provides the AC timing parameters for the I2C interface of the MPC8306S.

Table 35. I2C AC Electrical Specifications

All values refer to VIH (min) and VIL (max) levels (see Table 34).

Symbol1

Min

Max

Unit

SCL clock frequency

fI2C

0

400

kHz

Low period of the SCL clock

tI2CL

1.3

—

s

High period of the SCL clock

tI2CH

0.6

—

s

Setup time for a repeated START condition

tI2SVKH

0.6

—

s

Hold time (repeated) START condition (after this period, the first clock

pulse is generated)

tI2SXKL

0.6

—

s

Data setup time

tI2DVKH

100

—

ns

Parameter

2

Data hold time: I C bus devices

Rise time of both SDA and SCL signals

3

tI2DXKL

300

0.9

s

tI2CR

20 + 0.1 CB4

300

ns

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

34

Freescale Semiconductor

�I2 C

Table 35. I2C AC Electrical Specifications (continued)

All values refer to VIH (min) and VIL (max) levels (see Table 34).

Symbol1

Min

Max

Unit

tI2CF

20 + 0.1 CB4

300

ns

Setup time for STOP condition

tI2PVKH

0.6

—

s

Bus free time between a STOP and START condition

tI2KHDX

1.3

—

s

Noise margin at the LOW level for each connected device (including

hysteresis)

VNL

0.1 OVDD

—

V

Noise margin at the HIGH level for each connected device (including

hysteresis)

VNH

0.2 OVDD

—

V

Parameter

Fall time of both SDA and SCL signals

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tI2DVKH symbolizes I2C timing (I2)

with respect to the time data input signals (D) reach the valid state (V) relative to the tI2C clock reference (K) going to the high

(H) state or setup time. Also, tI2SXKL symbolizes I2C timing (I2) for the time that the data with respect to the start condition

(S) went invalid (X) relative to the tI2C clock reference (K) going to the low (L) state or hold time. Also, tI2PVKH symbolizes I2C

timing (I2) for the time that the data with respect to the stop condition (P) reaching the valid state (V) relative to the tI2C clock

reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate

letter: R (rise) or F (fall).

2. MPC8306S provides a hold time of at least 300 ns for the SDA signal (referred to the VIH(min) of the SCL signal) to bridge the

undefined region of the falling edge of SCL.

3. The maximum tI2DVKL has only to be met if the device does not stretch the LOW period (tI2CL) of the SCL signal.

4. CB = capacitance of one bus line in pF.

The following figure provides the AC test load for the I2C.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 25. I2C AC Test Load

The following figure shows the AC timing diagram for the I2C bus.

SDA

tI2CF

tI2DVKH

tI2CL

tI2KHKL

tI2SXKL

tI2CF

tI2CR

SCL

tI2SXKL

S

tI2DXKL

tI2CH

tI2SVKH

Sr

tI2PVKH

P

S

Figure 26. I2C Bus AC Timing Diagram

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Freescale Semiconductor

35

�Timers

14 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8306S.

14.1

Timer DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S timer pins, including

TIN, TOUT, TGATE, and RTC_PIT_CLK.

Table 36. Timer DC Electrical Characteristics

Characteristic

Symbol

Condition

Min

Max

Unit

Output high voltage

VOH

IOH = –6.0 mA

2.4

—

V

Output low voltage

VOL

IOL = 6.0 mA

—

0.5

V

Output low voltage

VOL

IOL = 3.2 mA

—

0.4

V

Input high voltage

VIH

—

2.0

OVDD + 0.3

V

Input low voltage

VIL

—

–0.3

0.8

V

Input current

IIN

0 V VIN OVDD

—

±5

A

14.2

Timer AC Timing Specifications

The following table provides the timer input and output AC timing specifications.

Table 37. Timer Input AC Timing Specifications1

Characteristic

Timers inputs—minimum pulse width

Symbol2

Min

Unit

tTIWID

20

ns

Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS_CLK_IN.

Timings are measured at the pin.

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by any

external synchronous logic. Timer inputs are required to be valid for at least tTIWID ns to ensure proper operation.

The following figure provides the AC test load for the timers.

Output

Z0 = 50

RL = 50

OVDD/2

Figure 27. Timers AC Test Load

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

36

Freescale Semiconductor

�GPIO

15 GPIO

This section describes the DC and AC electrical specifications for the GPIO of the MPC8306S.

15.1

GPIO DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S GPIO.

Table 38. GPIO DC Electrical Characteristics

Characteristic

Symbol

Condition

Min

Max

Unit

Notes

Output high voltage

VOH

IOH = –6.0 mA

2.4

—

V

1

Output low voltage

VOL

IOL = 6.0 mA

—

0.5

V

1

Output low voltage

VOL

IOL = 3.2 mA

—

0.4

V

1

Input high voltage

VIH

—

2.0

OVDD + 0.3

V

1

Input low voltage

VIL

—

–0.3

0.8

V

—

Input current

IIN

0 V VIN OVDD

—

±5

A

—

Note:

1. This specification applies when operating from 3.3-V supply.

15.2

GPIO AC Timing Specifications

The following table provides the GPIO input and output AC timing specifications.

Table 39. GPIO Input AC Timing Specifications1

Characteristic

GPIO inputs—minimum pulse width

Symbol2

Min

Unit

tPIWID

20

ns

Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of SYS_CLK_IN.

Timings are measured at the pin.