Freescale Semiconductor

Technical Data

Document Number: MPC8544EEC

Rev. 8, 09/2015

MPC8544E PowerQUICC III

Integrated Processor

Hardware Specifications

1

MPC8544E Overview

This section provides a high-level overview of MPC8544E

features. Figure 1 shows the major functional units within

the device.

1.1

Key Features

The following list provides an overview of the device feature

set:

• High-performance, 32-bit core enhanced by

resources for embedded cores defined by the Power

ISA, and built on Power Architecture® technology:

— 32-Kbyte L1 instruction cache and 32-Kbyte L1

data cache with parity protection. Caches can be

locked entirely or on a per-line basis, with

separate locking for instructions and data.

— Signal-processing engine (SPE) APU (auxiliary

processing unit). Provides an extensive

instruction set for vector (64-bit) integer and

fractional operations. These instructions use both

the upper and lower words of the 64-bit GPRs as

they are defined by the SPE APU.

Freescale reserves the right to change the detail specifications as may be required

to permit improvements in the design of its products.

© 2008-2011, 2014-2015 Freescale Semiconductor, Inc. All rights reserved.

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

Contents

MPC8544E Overview . . . . . . . . . . . . . . . . . . . . . . . . . 1

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . 8

Power Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 13

Input Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

RESET Initialization . . . . . . . . . . . . . . . . . . . . . . . . . 16

DDR and DDR2 SDRAM . . . . . . . . . . . . . . . . . . . . . 16

DUART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Enhanced Three-Speed Ethernet (eTSEC),

MII Management 23

Ethernet Management Interface Electrical

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Local Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Programmable Interrupt Controller . . . . . . . . . . . . . 55

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

High-Speed Serial Interfaces (HSSI) . . . . . . . . . . . . 63

PCI Express . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Package Description . . . . . . . . . . . . . . . . . . . . . . . . . 81

Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Thermal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

System Design Information . . . . . . . . . . . . . . . . . . 105

Device Nomenclature . . . . . . . . . . . . . . . . . . . . . . . 114

Document Revision History . . . . . . . . . . . . . . . . . . 116

�MPC8544E Overview

— Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit)

floating-point instructions that use the 64-bit GPRs.

— 36-bit real addressing

— Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set

for single-precision (32-bit) floating-point instructions.

— Memory management unit (MMU). Especially designed for embedded applications. Supports

4-Kbyte–4-Gbyte page sizes.

— Enhanced hardware and software debug support

— Performance monitor facility that is similar to, but separate from, the device performance

monitor

The e500 defines features that are not implemented on this device. It also generally defines some features

that this device implements more specifically. An understanding of these differences can be critical to

ensure proper operations.

• 256-Kbyte L2 cache/SRAM

— Flexible configuration

— Full ECC support on 64-bit boundary in both cache and SRAM modes

— Cache mode supports instruction caching, data caching, or both.

— External masters can force data to be allocated into the cache through programmed memory

ranges or special transaction types (stashing).

– 1, 2, or 4 ways can be configured for stashing only.

— Eight-way set-associative cache organization (32-byte cache lines)

— Supports locking entire cache or selected lines. Individual line locks are set and cleared through

Book E instructions or by externally mastered transactions.

— Global locking and flash clearing done through writes to L2 configuration registers

— Instruction and data locks can be flash cleared separately.

— SRAM features include the following:

– I/O devices access SRAM regions by marking transactions as snoopable (global).

– Regions can reside at any aligned location in the memory map.

– Byte-accessible ECC is protected using read-modify-write transaction accesses for

smaller-than-cache-line accesses.

• Address translation and mapping unit (ATMU)

— Eight local access windows define mapping within local 36-bit address space.

— Inbound and outbound ATMUs map to larger external address spaces.

– Three inbound windows plus a configuration window on PCI and PCI Express

– Four outbound windows plus default translation for PCI and PCI Express

• DDR/DDR2 memory controller

— Programmable timing supporting DDR and DDR2 SDRAM

— 64-bit data interface

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

2

Freescale Semiconductor

�MPC8544E Overview

—

—

—

—

•

•

Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

DRAM chip configurations from 64 Mbits to 4 Gbits with x8/x16 data ports

Full ECC support

Page mode support

– Up to 16 simultaneous open pages for DDR

– Up to 32 simultaneous open pages for DDR2

— Contiguous or discontiguous memory mapping

— Sleep mode support for self-refresh SDRAM

— On-die termination support when using DDR2

— Supports auto refreshing

— On-the-fly power management using CKE signal

— Registered DIMM support

— Fast memory access via JTAG port

— 2.5-V SSTL_2 compatible I/O (1.8-V SSTL_1.8 for DDR2)

Programmable interrupt controller (PIC)

— Programming model is compliant with the OpenPIC architecture.

— Supports 16 programmable interrupt and processor task priority levels

— Supports 12 discrete external interrupts

— Supports 4 message interrupts with 32-bit messages

— Supports connection of an external interrupt controller such as the 8259 programmable

interrupt controller

— Four global high resolution timers/counters that can generate interrupts

— Supports a variety of other internal interrupt sources

— Supports fully nested interrupt delivery

— Interrupts can be routed to external pin for external processing.

— Interrupts can be routed to the e500 core’s standard or critical interrupt inputs.

— Interrupt summary registers allow fast identification of interrupt source.

Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec,

IKE, WTLS/WAP, SSL/TLS, and 3GPP

— Four crypto-channels, each supporting multi-command descriptor chains

– Dynamic assignment of crypto-execution units via an integrated controller

– Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

— PKEU—public key execution unit

– RSA and Diffie-Hellman; programmable field size up to 2048 bits

– Elliptic curve cryptography with F2m and F(p) modes and programmable field size up to

511 bits

— DEU—Data Encryption Standard execution unit

– DES, 3DES

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

3

�MPC8544E Overview

•

•

•

•

– Two key (K1, K2, K1) or three key (K1, K2, K3)

– ECB and CBC modes for both DES and 3DES

— AESU—Advanced Encryption Standard unit

– Implements the Rijndael symmetric key cipher

– ECB, CBC, CTR, and CCM modes

– 128-, 192-, and 256-bit key lengths

— AFEU—ARC four execution unit

– Implements a stream cipher compatible with the RC4 algorithm

– 40- to 128-bit programmable key

— MDEU—message digest execution unit

– SHA with 160- or 256-bit message digest

– MD5 with 128-bit message digest

– HMAC with either algorithm

— KEU—Kasumi execution unit

– Implements F8 algorithm for encryption and F9 algorithm for integrity checking

– Also supports A5/3 and GEA-3 algorithms

— RNG—random number generator

— XOR engine for parity checking in RAID storage applications

Dual I2C controllers

— Two-wire interface

— Multiple master support

— Master or slave I2C mode support

— On-chip digital filtering rejects spikes on the bus

Boot sequencer

— Optionally loads configuration data from serial ROM at reset via the I2C interface

— Can be used to initialize configuration registers and/or memory

— Supports extended I2C addressing mode

— Data integrity checked with preamble signature and CRC

DUART

— Two 4-wire interfaces (SIN, SOUT, RTS, CTS)

— Programming model compatible with the original 16450 UART and the PC16550D

Local bus controller (LBC)

— Multiplexed 32-bit address and data bus operating at up to 133 MHz

— Eight chip selects support eight external slaves

— Up to eight-beat burst transfers

— The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

— Two protocol engines available on a per chip select basis:

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

4

Freescale Semiconductor

�MPC8544E Overview

•

– General-purpose chip select machine (GPCM)

– Three user programmable machines (UPMs)

— Parity support

— Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

Two enhanced three-speed Ethernet controllers (eTSECs)

— Three-speed support (10/100/1000 Mbps)

— Two IEEE Std 802.3™, IEEE 802.3u, IEEE 802.3x, IEEE 802.3z, IEEE 802.3ac, and

IEEE 802.3ab-compliant controllers

— Support for various Ethernet physical interfaces:

– 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, SGMII, and RGMII.

– 10/100 Mbps full- and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII.

— Flexible configuration for multiple PHY interface configurations.

— TCP/IP acceleration and QoS features available

– IP v4 and IP v6 header recognition on receive

– IP v4 header checksum verification and generation

– TCP and UDP checksum verification and generation

– Per-packet configurable acceleration

– Recognition of VLAN, stacked (queue in queue) VLAN, 802.2, PPPoE session, MPLS

stacks, and ESP/AH IP-security headers

– Supported in all FIFO modes

— Quality of service support:

– Transmission from up to eight physical queues

– Reception to up to eight physical queues

— Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

– IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or

software-programmed PAUSE frame generation and recognition)

— Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and

IEEE Std 802.1™ virtual local area network (VLAN) tags and priority

— VLAN insertion and deletion

– Per-frame VLAN control word or default VLAN for each eTSEC

– Extracted VLAN control word passed to software separately

— Retransmission following a collision

— CRC generation and verification of inbound/outbound frames

— Programmable Ethernet preamble insertion and extraction of up to 7 bytes

— MAC address recognition:

– Exact match on primary and virtual 48-bit unicast addresses

– VRRP and HSRP support for seamless router fail-over

– Up to 16 exact-match MAC addresses supported

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

5

�MPC8544E Overview

•

•

•

– Broadcast address (accept/reject)

– Hash table match on up to 512 multicast addresses

– Promiscuous mode

— Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet

programming models

— RMON statistics support

— 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

— MII management interface for control and status

— Ability to force allocation of header information and buffer descriptors into L2 cache

OCeaN switch fabric

— Full crossbar packet switch

— Reorders packets from a source based on priorities

— Reorders packets to bypass blocked packets

— Implements starvation avoidance algorithms

— Supports packets with payloads of up to 256 bytes

Integrated DMA controller

— Four-channel controller

— All channels accessible by both the local and remote masters

— Extended DMA functions (advanced chaining and striding capability)

— Support for scatter and gather transfers

— Misaligned transfer capability

— Interrupt on completed segment, link, list, and error

— Supports transfers to or from any local memory or I/O port

— Selectable hardware-enforced coherency (snoop/no snoop)

— Ability to start and flow control each DMA channel from external 3-pin interface

— Ability to launch DMA from single write transaction

PCI controller

— PCI 2.2 compatible

— One 32-bit PCI port with support for speeds from 16 to 66 MHz

— Host and agent mode support

— 64-bit dual address cycle (DAC) support

— Supports PCI-to-memory and memory-to-PCI streaming

— Memory prefetching of PCI read accesses

— Supports posting of processor-to-PCI and PCI-to-memory writes

— PCI 3.3-V compatible

— Selectable hardware-enforced coherency

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

6

Freescale Semiconductor

�MPC8544E Overview

•

•

•

•

•

•

Three PCI Express interfaces

— Two ×4 link width interfaces and one ×1 link width interface

— PCI Express 1.0a compatible

— Auto-detection of number of connected lanes

— Selectable operation as root complex or endpoint

— Both 32- and 64-bit addressing

— 256-byte maximum payload size

— Virtual channel 0 only

— Traffic class 0 only

— Full 64-bit decode with 32-bit wide windows

Power management

— Supports power saving modes: doze, nap, and sleep

— Employs dynamic power management, which automatically minimizes power consumption of

blocks when they are idle

System performance monitor

— Supports eight 32-bit counters that count the occurrence of selected events

— Ability to count up to 512 counter-specific events

— Supports 64 reference events that can be counted on any of the 8 counters

— Supports duration and quantity threshold counting

— Burstiness feature that permits counting of burst events with a programmable time between

bursts

— Triggering and chaining capability

— Ability to generate an interrupt on overflow

System access port

— Uses JTAG interface and a TAP controller to access entire system memory map

— Supports 32-bit accesses to configuration registers

— Supports cache-line burst accesses to main memory

— Supports large block (4-Kbyte) uploads and downloads

— Supports continuous bit streaming of entire block for fast upload and download

IEEE Std 1149.1™-compliant, JTAG boundary scan

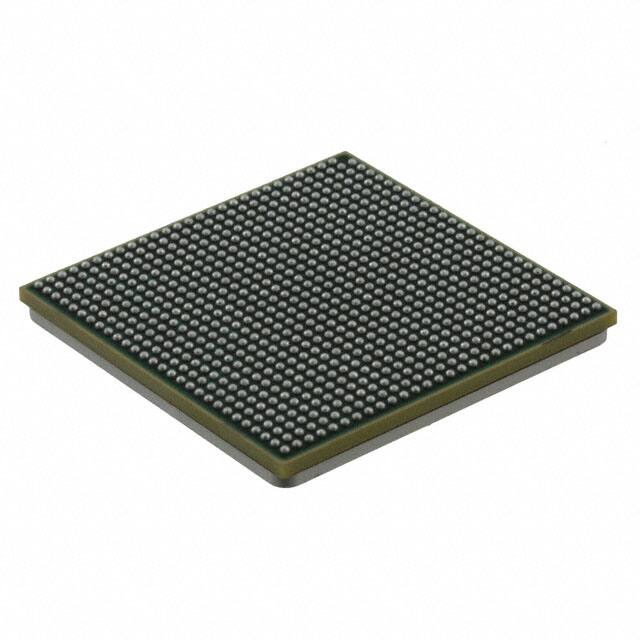

783 FC-PBGA package

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

7

�Electrical Characteristics

Figure 1 shows the MPC8544E block diagram.

MPC8544E

e500 Core

32-Kbyte

I-Cache

XOR

Acceleration

Local

Bus

Security

Acceleration

Performance

Monitor

DUART

2x I2C

32-Kbyte

D-Cache

e500

Coherency

Module

OpenPIC

Gigabit

Ethernet

SGMII

256-Kbyte

L2

Cache

64-Bit

DDR/DDR2

SDRAM

Controller

32-Bit

PCI

PCI

Express

x4/x2/x1

PCI

Express

x1

PCI

Express

x4/x2/x1

DMA

Figure 1. MPC8544E Block Diagram

2

Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the

MPC8544E. This device is currently targeted to these specifications. Some of these specifications are

independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer

design specifications.

2.1

Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

2.1.1

Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings1

Characteristic

Symbol

Max Value

Unit

Notes

Core supply voltage

VDD

–0.3 to 1.1

V

—

PLL supply voltage

AVDD

–0.3 to 1.1

V

—

Core power supply for SerDes transceivers

SVDD

–0.3 to 1.1

V

—

Pad power supply for SerDes transceivers

XVDD

–0.3 to 1.1

V

—

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

8

Freescale Semiconductor

�Electrical Characteristics

Table 1. Absolute Maximum Ratings1 (continued)

Characteristic

Symbol

Max Value

Unit

Notes

GVDD

–0.3 to 2.75

–0.3 to 1.98

V

—

LVDD (eTSEC1)

–0.3 to 3.63

–0.3 to 2.75

V

—

TVDD (eTSEC3)

–0.3 to 3.63

–0.3 to 2.75

V

—

PCI, DUART, system control and power management, I2C, and

JTAG I/O voltage

OVDD

–0.3 to 3.63

V

—

Local bus I/O voltage

BVDD

–0.3 to 3.63

–0.3 to 2.75

–0.3 to 1.98

V

—

Input voltage

MVIN

–0.3 to (GVDD + 0.3)

V

2

DDR/DDR2 DRAM reference

MVREF

–0.3 to (GVDD + 0.3)

V

2

Three-speed Ethernet signals

LVIN

TVIN

–0.3 to (LVDD + 0.3)

–0.3 to (TVDD + 0.3)

V

2

Local bus signals

BVIN

–0.3 to (BVDD + 0.3)

V

—

DUART, SYSCLK, system control and power

management, I2C, and JTAG signals

OVIN

–0.3 to (OVDD + 0.3)

V

2

PCI

OVIN

–0.3 to (OVDD + 0.3)

V

2

TSTG

–55 to 150

°C

—

DDR and DDR2 DRAM I/O voltage

Three-speed Ethernet I/O, MII management voltage

DDR/DDR2 DRAM signals

Storage temperature range

Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and

functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause.

2. (M,L,O)VIN, and MVREF may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

2.1.2

Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are

the recommended and tested operating conditions. Proper device operation outside these conditions is not

guaranteed.

Table 2. Recommended Operating Conditions

Symbol

Recommended

Value

Unit

Notes

Core supply voltage

VDD

1.0 ± 50 mV

V

—

PLL supply voltage

AVDD

1.0 ± 50 mV

V

1

Core power supply for SerDes transceivers

SVDD

1.0 ± 50 mV

V

—

Pad power supply for SerDes transceivers

XVDD

1.0 ± 50 mV

V

—

DDR and DDR2 DRAM I/O voltage

GVDD

2.5 V ± 125 mV

1.8 V ± 90 mV

V

2

Characteristic

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

9

�Electrical Characteristics

Table 2. Recommended Operating Conditions (continued)

Symbol

Recommended

Value

LVDD

(eTSEC1)

3.3 V ± 165 mV

2.5 V ± 125 mV

TVDD

(eTSEC3)

3.3 V ± 165 mV

2.5 V ± 125 mV

PCI, DUART, PCI Express, system control and power management, I2C,

and JTAG I/O voltage

OVDD

Local bus I/O voltage

Input voltage

Characteristic

Unit

Notes

V

4

3.3 V ± 165 mV

V

3

BVDD

3.3 V ± 165 mV

2.5 V ± 125 mV

1.8 V ± 90 mV

V

5

MVIN

GND to GVDD

V

2

MVREF

GND to GVDD/2

V

2

Three-speed Ethernet signals

LVIN

TVIN

GND to LVDD

GND to TVDD

V

4

Local bus signals

BVIN

GND to BVDD

V

5

PCI, Local bus, DUART, SYSCLK, system control

and power management, I2C, and JTAG signals

OVIN

GND to OVDD

V

3

Tj

0 to 105

°C

—

Three-speed Ethernet I/O voltage

DDR and DDR2 DRAM signals

DDR and DDR2 DRAM reference

Junction temperature range

Notes:

1. This voltage is the input to the filter discussed in Section 21.2, “PLL Power Supply Filtering,” and not necessarily the voltage

at the AVDD pin, which may be reduced from VDD by the filter.

2. Caution: MVIN must not exceed GVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during

power-on reset and power-down sequences.

3. Caution: OVIN must not exceed OVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during

power-on reset and power-down sequences.

4. Caution: T/LVIN must not exceed T/ LVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during

power-on reset and power-down sequences.

5. Caution: BVIN must not exceed BVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during

power-on reset and power-down sequences.

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

10

Freescale Semiconductor

�Electrical Characteristics

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8544E.

B/G/L/OVDD + 20%

B/G/L/OVDD + 5%

B/G/L/OVDD

VIH

GND

GND – 0.3 V

VIL

GND – 0.7 V

Not to Exceed 10%

of tCLOCK1

Notes:

1. tCLOCK refers to the clock period associated with the respective interface:

For I2C and JTAG, tCLOCK references SYSCLK.

For DDR, tCLOCK references MCLK.

For eTSEC, tCLOCK references EC_GTX_CLK125.

For LBIU, tCLOCK references LCLK.

For PCI, tCLOCK references PCI_CLK or SYSCLK.

2. Please note that with the PCI overshoot allowed (as specified above), the device

does not fully comply with the maximum AC ratings and device protection

guideline outlined in Section 4.2.2.3 of the PCI 2.2 Local Bus Specifications.

Figure 2. Overshoot/Undershoot Voltage for GVDD/OVDD/LVDD/BVDD/TVDD

The core voltage must always be provided at nominal 1.0 V (see Table 2 for actual recommended core

voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must

be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the

associated I/O supply voltage. OVDD and LVDD based receivers are simple CMOS I/O circuits and satisfy

appropriate LVCMOS type specifications. The DDR2 SDRAM interface uses a single-ended differential

receiver referenced the externally supplied MVREF signal (nominally set to GVDD/2) as is appropriate for

the SSTL2 electrical signaling standard.

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

11

�Electrical Characteristics

2.1.3

Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

Driver Type

Local bus interface utilities signals

PCI signals

Programmable

Output Impedance

(Ω)

Supply

Voltage

25

35

BVDD = 3.3 V

BVDD = 2.5 V

45 (default)

45 (default)

125

BVDD = 3.3 V

BVDD = 2.5 V

BVDD = 1.8 V

25

OVDD = 3.3 V

2

Notes

1

42 (default)

DDR signal

20

GVDD = 2.5 V

—

DDR2 signal

16

32 (half strength mode)

GVDD = 1.8 V

—

TSEC signals

42

LVDD = 2.5/3.3 V

—

DUART, system control, JTAG

42

OVDD = 3.3 V

—

I2C

150

OVDD = 3.3 V

—

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI_GNT1 signal at reset.

2.2

Power Sequencing

The device requires its power rails to be applied in specific sequence in order to ensure proper device

operation. These requirements are as follows for power up:

1. VDD, AVDD_n, BVDD, LVDD, SVDD, OVDD, TVDD, XVDD

2. GVDD

Note that all supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines

must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before

the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for GVDD is required. If there is

no concern about any of the DDR signals being in an indeterminate state during power up, then the

sequencing for GVDD is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD core supply, the I/Os

associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be

drawn by the device.

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

12

Freescale Semiconductor

�Power Characteristics

3

Power Characteristics

The estimated typical core power dissipation for the core complex bus (CCB) versus the core frequency

for this family of PowerQUICC III devices is shown in Table 4.

Table 4. MPC8544ECore Power Dissipation

Power Mode

Core Frequency

(MHz)

Platform Frequency

(MHz)

VDD

(V)

Junction

Temperature (°C)

Power

(W)

Notes

667

333

1.0

65

2.6

1, 2

105

4.5

1, 3

7.15

1, 4

65

2.9

1, 2

105

4.8

1, 3

7.35

1, 4

65

3.6

1, 2

105

5.3

1, 3

7.5

1, 4

3.9

1, 2

6.0

1, 3

7.7

1, 4

Typical

Thermal

Maximum

Typical

800

400

1.0

Thermal

Maximum

Typical

1000

400

1.0

Thermal

Maximum

Typical

1067

533

1.0

65

Thermal

105

Maximum

Notes:

1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and

configurations. The values do not include power dissipation for I/O supplies.

2. Typical power is an average value measured at the nominal recommended core voltage (VDD) and 65°C junction temperature

(see Table 2) while running the Dhrystone 2.1 benchmark.

3. Thermal power is the average power measured at nominal core voltage (VDD) and maximum operating junction temperature

(see Table 2) while running the Dhrystone 2.1 benchmark.

4. Maximum power is the maximum power measured at nominal core voltage (VDD) and maximum operating junction

temperature (see Table 2) while running a smoke test which includes an entirely L1-cache-resident, contrived sequence of

instructions which keep the execution unit maximally busy.

4

Input Clocks

This section contains the following subsections:

• Section 4.1, “System Clock Timing”

• Section 4.2, “Real-Time Clock Timing”

• Section 4.3, “eTSEC Gigabit Reference Clock Timing”

• Section 4.4, “Platform to FIFO Restrictions”

• Section 4.5, “Other Input Clocks”

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Freescale Semiconductor

13

�Input Clocks

4.1

System Clock Timing

Table 5 provides the system clock (SYSCLK) AC timing specifications for the MPC8544E.

Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with OVDD = 3.3 V ± 165 mV.

Parameter/Condition

Symbol

Min

Typical

Max

Unit

Notes

SYSCLK frequency

fSYSCLK

33

—

133

MHz

1

SYSCLK cycle time

tSYSCLK

7.5

—

30.3

ns

—

SYSCLK rise and fall time

tKH, tKL

0.6

1.0

2.1

ns

2

tKHK/tSYSCLK

40

—

60

%

—

—

—

—

±150

ps

3, 4

SYSCLK duty cycle

SYSCLK jitter

Notes:

1. Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting

SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum

operating frequencies. Refer to Section 19.2, “CCB/SYSCLK PLL Ratio,” and Section 19.3, “e500 Core PLL Ratio,” for ratio

settings.

2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

3. This represents the total input jitter—short- and long-term.

4. The SYSCLK driver’s closed loop jitter bandwidth should be