PTN36502/PTN36502A

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Rev. 3 — 28 September 2018

1

Product data sheet

General description

PTN36502/PTN36502A is a Type-C USB 3.1 Gen 1/ DP1.2 combo redriver that is

optimized for USB 3.1 Gen 1 and DisplayPort applications on either the Downstream

Facing Port (DFP) or Upstream Facing Port (UFP) by following the four high-speed

differential data flows to extend the signal reach.

PTN36502/PTN36502A addresses high-speed signal quality enhancement requirements

for implementation of a USB Type-C interface in a platform that supports the VESA

DisplayPort Alt Mode Standard v1.0a, includes a DisplayPort Branch or Sink function.

PTN36502/PTN36502A has three ternary (3-level) configuration pins (SCL/C1, SDA/

C2 and EN), and depending on the state of EN pin during Power-On Reset (POR),

2

the device gets into GPIO mode or I C mode. When EN is driven LOW during POR,

PTN36502/PTN36502A operates under GPIO mode, and these three ternary pins are

used to configure DFP/UFP configuration followed by mode setting (USB 3.1 Gen 1 and

DisplayPort TX and RX function selection), as well as selecting receive equalization,

transmit de-emphasis and output swing level. To support applications that require greater

2

level of configurability, PTN36502/PTN36502A can operate in I C mode when EN pin is

left open (OPEN/NC) during POR.

For DisplayPort (DP) operation, PTN36502/PTN36502A has a built-in internal crossbar

function that can swap AUXP and AUXN signals for supporting plug orientation.

PTN36502/PTN36502A monitors the AUX transactions and adjusts the DisplayPort

transmitter’s output swing and emphasis setting during DP Link training accordingly.

PTN36502/PTN36502A has built-in advanced power management capability that enables

significant power saving under USB 3.1 Gen 1 Low power modes (U2/U3). It can detect

LFPS signaling and link electrical conditions and can dynamically activate/deactivate

internal circuitry and logic. The device performs these actions without host software

intervention and conserves power. The host processor keeps PTN36502/PTN36502A in

deep power saving or USB operation mode until DP Alt mode is entered.

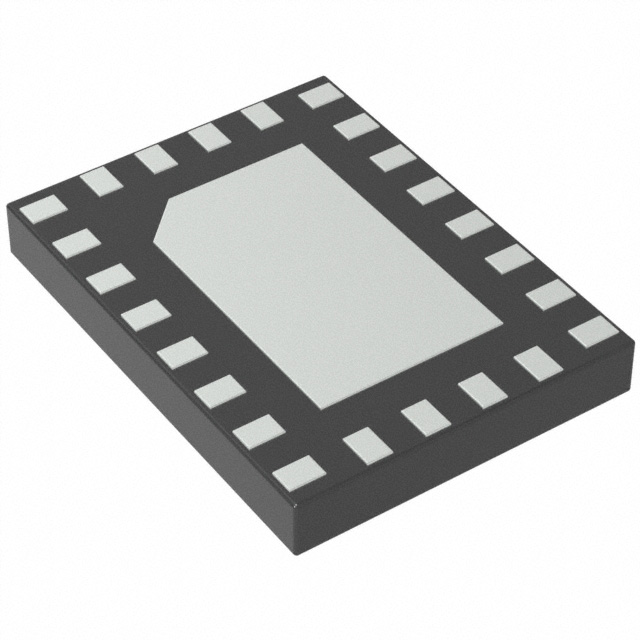

PTN36502/PTN36502A is powered from a 1.8 V supply and it is available in an extremely

thin HX2QFN24 package with 2.4 mm x 3.2 mm x 0.35 mm and 0.4 mm pitch.

�NXP Semiconductors

PTN36502/PTN36502A

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

2

Features and benefits

• Flexible Type-C USB/DP combo redriver supports four signaling combinations specified

2

in USB Type-C and VESA DisplayPort Alt Mode Standards through either I C slave

interface or ternary GPIO pins

– Mode 1: One USB 3.1 Gen 1 port only

– Mode 2: One USB 3.1 Gen 1 port + 2 lane DP + AUX channel

– Mode 3: 4 lane DP + AUX channel

• Supports USB 3.1 Gen 1 data rate of 5 Gbps, and DisplayPort data rates at 1.62 Gbps,

2.7 Gbps and 5.4 Gbps (HBR2), AUX at 1 Mbps

• Compliant to SuperSpeed USB 3.1 Gen 1 standard

• Compliant to DisplayPort v1.2 standard for DFP applications

• Compliant to VESA DisplayPort Alt mode on USB Type-C standard

• Implements USB Type-C Safe state conditions on all connector facing pins

2

• Configurable via ternary GPIO or I C interface (operating up to 1 MHz)

2

• PTN36502 7-bit I C address = 001 1010

2

• PTN36502A 7-bit I C address = 001 0010

• Integrated termination resistors provide impedance matching on both transmit and

receive sides

• RX equalizers on all inputs to compensate for high speed signal attenuation in PCB

and cable channels

• Active TX De-emphasis and Output swing on all outputs to assure high frequency boost

• Automatic Receiver Termination Detection in USB 3.1 Gen 1 mode

• Supports auto power saving modes during USB 3.1 Gen 1 operation

• DP AUX sideband crossbar switch for Type-C plug orientation

• DP AUX monitoring during DP link training to control DP TX output driver adjustment

• Flow-through pinout to ease PCB layout and minimize crosstalk effects

– Low crosstalk: DDNEXT < -45 dB at 2.7 GHz

• Low active current consumption

– USB 3.1 Gen 1 only (Mode 1) active power: 115 mA (typ) for VOS = 1Vpp and

DE=-3.5 dB

– 2-lane DP HBR2 level 0 (Mode 3): 75 mA (Level 0 : 400 mV with no Pre-emphasis)

– 1-lane DP HBR2 level 0 (Mode 3): 38 mA (Level 0 : 400 mV with no Pre-emphasis)

– 4-lane DP only HBR2 level 0 (Mode 3): 150 mA

• Power-saving states:

– USB 3.1 Gen 1 mode (mode 1):

– 1.16 mA (typ) when in USB 3.1 Gen 1 U2/U3 states

– 0.77 mA (typ) when no connection detected (USB Rx detection enabled) (when a

USB Type-C to USB Type-A adapter is connected to a USB Type-C port, but no

USB Type-A device is attached to the adapter)

– DP sleep D3 mode (Mode 2/3): 0.5 mA (typ)

– 3 μA (typ) when in deep power-saving state

• Excellent Differential and Common return loss performance

• Hot Plug capable

• Single Power Supply 1.8 V

• Extremely thin HX2QFN24 package

– 2.4 mm x 3.2 mm x 0.35 mm with 0.4 mm pitch

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

2 / 58

�NXP Semiconductors

PTN36502/PTN36502A

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

• ESD HBM 8 kV CDM 1 kV on high speed pins and HBM 4 kV CDM 500 V on control

pins

• Supports IEC61000-4-5 8/20 μs ±16 V Surge test performance with external 4.7 Ω

series resistors on the DRX1P/N, DRX2P/N and DAUXP/N pins

• Operating temperature range -40 to +85 ℃

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

3 / 58

�NXP Semiconductors

PTN36502/PTN36502A

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

3

Applications

• For USB Type-C Host/Source application

– Smartphones and Tablets

– Notebooks, AIO and Desktop Computers

– Hub or Dock Devices

• For USB Type-C Device/Sink application

– Docking Stations

– Display units

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

4 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

4

Ordering information

Table 1. Ordering information

Type number

PTN36502HQ

Topside Package

marking

Name

[1]

[2]

PTN36502AHQ

[1]

[2]

Description

Version

502

HX2QFN24

plastic, thermal enhanced super thin quad flat

SOT1903-1

package; no leads; 24 terminals; 0.4 mm pitch, 2.4

mm x 3.2 mm x 0.35 mm body

52A

HX2QFN24

plastic, thermal enhanced super thin quad flat

SOT1903-1

package; no leads; 24 terminals; 0.4 mm pitch, 2.4

mm x 3.2 mm x 0.35 mm body

2

PTN36502 7-bit I C address = 001 1010

2

PTN36502A 7-bit I C address = 001 0010

4.1 Ordering options

Table 2. Ordering options

Type number

PTN36502HQ

[1]

[2]

PTN36502AHQ

[1]

[2]

Orderable part

number

Package

Packing method

Minimum

order quantity

Temperature

PTN36502HQX

HX2QFN24

REEL 7" Q1/T1

*STANDARD MARK

SMD

3000

Tamb = -40 ℃ to 85 ℃

PTN36502AHQX

HX2QFN24

REEL 7" Q1/T1

*STANDARD MARK

SMD

3000

Tamb = -40 ℃ to 85 ℃

2

PTN36502 7-bit I C address = 001 1010

2

PTN36502A 7-bit I C address = 001 0010

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

5 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

5

Functional diagram

VDD18

GND

D_IOP

DRX1P

D_ION

DRX1N

C_IP

DTX1P

C_IN

DTX1N

A_IP

DTX2P

A_IN

DTX2N

B_IOP

DRX2P

B_ION

DRX2N

UAUXP

DAUXP

UAUXN

DAUXN

PTN36502/PTN36502A CONTROLS

SCL

SDA

EN

aaa-026905

Figure 1. Functional diagram

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

6 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

6

Pinning information

6.1 Pinning

D_IOP D_ION DRX1P DRX1N

SCL/C1

1

SDA/C2

24

23

22

21

20

EN

2

19

VDD18

C_INP

3

18

DTX1N

C_INN

4

A_INP

5

PTN36502/

PTN36502A

A_INN

6

GND

UAUXP

7

UAUXN

8

9

B_IOP

10

11

12

B_ION DRX2P DRX2N

17

DTX1P

16

DTX2P

15

DTX2N

14

DAUXP

13

DAUXN

aaa-026906

Figure 2. PTN36502/PTN36502A pinning (transparent top view)

6.2 Pin description

Table 3. Pin description

Symbol

Pin

Type

Description

1

SCL/C1

Ternary open drain input/

output

When PTN36502/PTN36502A is operating in I C mode, this pin is

2

slave I C clock pin, and external pull-up resistor to 1.8 V or 3.3 V is

required.

When PTN36502/PTN36502A is operating in GPIO mode, this

pin has multiple functions depending on EN pin state, and is 1.8 V

tolerant. Refer to Section 7.6 for more details.

2

SDA/C2

Ternary open drain input/

output

When PTN36502/PTN36502A is operating in I C mode, this pin is

2

slave I C data pin, and external pull-up resistor to 1.8 V or 3.3 V is

required.

When PTN36502/PTN36502A is operating in GPIO mode, this

pin has multiple functions depending on EN pin state, and is 1.8 V

tolerant. Refer to Section 7.6 for more details.

3

C_INP

Self-biasing differential input

4

C_INN

Differential signal from high speed RX path. C_IP makes a

differential pair with C_IN. The associated TX output pair is DTX1P

and DTX1N

5

A_INP

Self-biasing differential input

6

A_INN

Differential signal from high speed RX path. A_IP makes a

differential pair with A_IN. The associated TX output pair is DTX2P

and DTX2N

7

UAUXP

I/O

8

UAUXN

Upstream AUX Channel I/O. When PTN36502/PTN36502A is

placed in DFP application, these signals should be AC coupled as

per DP spec

PTN36502_PTN36502A

Product data sheet

2

2

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

7 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Symbol

Pin

Type

9

B_IOP

10

B_ION

Self-biasing differential input/ Differential signal high speed input/output. B_IOP makes a

output

differential pair with B_ION. The associated output/input pair is

DRX2P and DRX2N. The I/O configuration is controlled by mode

setting

11

DRX2P

12

DRX2N

13

DAUXN

14

DAUXP

15

DTX2N

16

DTX2P

17

DTX1P

18

DTX1N

19

VDD18

20

EN

Ternary input

21

DRX1N

22

DRX1P

Self-biasing differential input/ Differential signal high speed input/output. DRX1P makes a

output

differential pair with DRX1N. The associated output/input pair is D_

IOP and D_ION. The I/O configuration is controlled by mode setting

23

D_ION

24

D_IOP

Center

pad

GND

PTN36502_PTN36502A

Product data sheet

Description

Self-biasing differential input/ Differential signal high speed input/output. DRX2P makes a

output

differential pair with DRX2N. The associated output/input pair is B_

IOP and B_ION. The I/O configuration is controlled by mode setting

I/O

Downstream AUX Channel I/O. When PTN36502/PTN36502A is

placed in UFP application, these signals should be AC coupled as

per DP spec

Self-biasing differential

output

Differential signal of high speed TX path. DTX2P makes a

differential pair with DTX2N. The associated RX input pair is A_IP

and A_IN

Self-biasing differential

output

Differential signal of high speed TX path. DTX1P makes a

differential pair with DTX1N. The associated RX input pair is C_IP

and C_IN

1.8 V Supply

3 level mode configuration pin. When power is applied on VDD18

pin

• If EN = 0, PTN36502/PTN36502A is operating in GPIO mode

2

• If EN = OPEN, PTN36502/PTN36502A is operating in I C mode

Self-biasing differential input/ Differential signal high speed input/output. D_IOP makes a

output

differential pair with D_ION. The associated output/input pair is

DRX1P and DRX1N. The I/O configuration is controlled by mode

setting

The center pad must be connected to GND plane for both electrical

grounding and thermal relief

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

8 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

7

Functional description

7.1 USB 3.1 Gen 1 operation

PTN36502/PTN36502A supports USB redriver operation at 5 Gbps. The receive

equalization, transmit output swing and de-emphasis settings are configured via GPIO or

2

I C register settings.

PTN36502/PTN36502A has implemented an advanced power management scheme

that operates in tune with USB 3.1 Gen 1 Bus electrical condition. Though the device

does not decode USB power management commands (related to USB 3.1 Gen 1 U1/

U2/U3 transitions) exchanged between USB Host and Peripheral/Device, it relies on

bus electrical conditions and control pins/register settings to decide to be in one of the

following states:

• Active state wherein device is fully operational. In this state, USB connection exists and

the Receive Termination remains active.

• Power-saving state wherein some portions of the TX and RX channels are kept

enabled. In this state, squelching, LFPS detection and/or Receive termination detection

circuitry are active. Based on USB connection, there are two possibilities:

– No USB connection (also called Rx-detect state)

– Receive Termination detection circuitry keeps polling periodically

– RX and TX signal paths (including squelch detector) are not enabled

– Receive Termination is not active

– DC Common mode voltage level is not maintained

– When USB connection exists and when the link is in USB U2/U3 mode,

– Receive Termination detection circuitry keeps polling periodically

– RX and TX signal paths are not enabled; squelch detector is enabled

– Receive Termination is active

– DC Common mode voltage level is maintained

7.2 DisplayPort v1.2 operation

PTN36502/PTN36502A supports DisplayPort redriver operation at 1.62 Gbps, 2.7 Gbps

and 5.4 Gbps, with 2-tap pre-emphasis, pre-emphasis levels 0 to 3 and output swing

levels 0 to 3.

The DisplayPort mode is selected only when DP Alternate mode has been entered by

the host controller. Until then, PTN36502/PTN36502A stays in deep power saving or

USB 3.1 Gen 1 only mode. The DisplayPort source can activate power down via AUX

command.

The DisplayPort link rate, lane count, transmit output swing and pre-emphasis settings

are configured autonomously during DisplayPort link training phase based on AUX

communication exchanges between Source and Sink. In addition, the host can configure

2

these settings via I C interface.

Table 4 illustrates the various combinations allowed and supported in DisplayPort modes.

The host AP shall configure the settings only based on valid combinations listed in this

table. Note PTN36502/PTN36502A does not check if combination is valid while being

configured.

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

9 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Table 4. Allowed output swing and pre-emphasis combinations in DisplayPort mode

Output swing level

Pre-emphasis level

0 (0 dB)

1 (3.5 dB)

2 (6 dB)

3 (8.8 dB)

0 (400 mV)

Supported

Supported

Supported

Supported

1 (600 mV)

Supported

Supported

Supported

Not allowed

2 (800 mV)

Supported

Supported

Not allowed

Not allowed

3 (1100 mV)

Supported

Not allowed

Not allowed

Not allowed

It is possible that only a subset of lanes gets selected during DP Link training and

remaining lanes are not active. Depending on the number of lanes selected, PTN36502/

PTN36502A is configured to operate with the selected lane count thereby saving power

consumption on unused lanes.

7.2.1 AUX crossbar switch

PTN36502/PTN36502A implements AUX crossbar switch with low insertion loss and

RON. All AUX traffic is passively passed through from one side to another. The switch

can be configured for ‘pass through’ mode or ‘pass through with cross’ mode. The host

2

processor can configure the switch via GPIO or I C-bus interface. By default, the switch

is in Hi-Z state at power-on reset.

7.2.2 AUX monitoring and configuration

PTN36502/PTN36502A monitors DP AUX communication exchanges that occur between

DP source and DP sink and passes the AUX data in either direction (Source to sink and

Sink to source). In particular, it detects for AUX communication involving DPCD register

controls – Lane count, Link rate, Transmit output swing, Transmit pre-emphasis level,

Sleep, Wake, etc. and configures its operation suitably. It also performs inversion as

required for plug orientation in DFP configurations. At DP AUX PHY level, the required

local biasing and AC coupling capacitance are implemented.

When PTN36502/PTN36502A is placed in DFP mode, the polarity of internal AUX

monitoring signal follows the orientation of the cable connector plugged in. For example,

if the orientation is reversed on the Type-C connector, signals presented on DAUXP and

DAUXN pins will be interpreted as AUXN and AUXP signals internally.

When PTN36502/PTN36502A is placed in UFP mode, the polarity of internal AUX

monitoring signal is fixed regardless of orientation of cable connector plugged in. Signals

presented on DAUXP and DAUXN pins are interpreted as AUXP and AUXN signals

internally.

The list of DPCD registers (with only the relevant bit fields) supported are as follows:

• LINK_BW_SET

• LANE_COUNT_SET

• TRAINING_LANEx_SET (x=0-3) (the DP source issues this command after sending

the specific training pattern and so, the redriver must target very small delay)

• SET POWER

2

• Other DPCD registers and I C over AUX transactions are not decoded

The applied values are expected to be within the capabilities of PTN36502/PTN36502A.

In case GPU sends out LANE_COUNT_SET =0 during AUX training, it is necessary to

2

program I C register 0x06 to value of 0x06 after entering DP modes (either mode 2 or 3).

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

10 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

This will ensure the PTN36502/PTN36502A DisplayPort starts up properly. Please follow

PTN36502/PTN36502A programming guide.

7.3 USB Type-C DFP receptacle application

1.8 V

0.1

F

Crossbar switch can

be integrated in

AP, or an external

component

DP1

DP2

APPLICATION PROCESSOR

DP3

SSTX

SSRX

GND

USB Type-C

receptacle

DP4 LANE/USB 3.1 GEN 1 CROSSBAR SWITCH

DP0

VDD18

D_IOP

DRX1P

(1)

D_ION

DRX1N

(1)

C_IP

DTX1P

(2)

C_IN

DTX1N

(2)

A_IP

DTX2P

A_IN

DTX2N

B_IOP

DRX2P

B_ION

DRX2N

A11/RX2+

A10/RX2-

B2/TX2+

B3/TX2-

A2/TX1+

A3/TX1-

B11/RX1+

B10/RX1A7/D1A6/D1+

100 k

AUX+

UAUXP

DAUXP

A8/SBU1

A4/VBUS

A9/VBUS

UAUXN

AUX3.3 V

DAUXN

100 k

PTN36502/PTN36502A CONTROLS

SCL

SDA

B6/D+

B7/D-

B9/VBUS

B4/VBUS

B8/SBU2

A5/CC1

A12/GND

B5/CC2

B1/GND

A1/GND

B12/GND

EN

aaa-026909

Figure 3. Connection illustration when PTN36502/PTN36502A in DFP receptacle application

(1): 0.33μF capacitors are recommended on Type-C's receiver pins based on latest USB specification.

(2): 0.22μF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 3 for using PTN36502/PTN36502A in USB Type-C DFP receptacle

application. In this configuration, upstream (left) side of PTN36502/PTN36502A is

connected to application processor with integrated or on-board crossbar switch function,

and downstream (right) side is connected to Type-C receptacle.

Each pin on the downstream side of PTN36502/PTN36502A connecting to the Type-C

connector has specific input/output configuration, and must match the signal assignments

on the upstream side accordingly. Table 5 shows the downstream pin connection to

Type-C receptacle.

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

11 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Table 5. Downstream pin connection to Type-C receptacle in DFP application

PTN36502/PTN36502A pins

USB Type-C receptacle pins

Symbol

Pin name

Symbol

Pin name

22

DRX1P

A11

RX2+

21

DRX1N

A10

RX2-

18

DTX1N

B3

TX2-

17

DTX1P

B2

TX2+

16

DTX2P

A2

TX1+

15

DTX2N

A3

TX1-

12

DRX2N

B10

RX1-

11

DRX2P

B11

RX1+

14

DAUXP

A8

SBU1

13

DAUXN

B8

SBU2

The upstream pins of PTN36502/PTN36502A are connected to the application

processor, with specific functions assigned to each differential signal. For each pin

assignment configuration below, PTN36502/PTN36502A controls which transmitters or

receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or DisplayPort

mode according to the mode setting.

Table 6. Upstream pin connection to application processor in DFP receptacle application

PTN36502/

PTN36502A

pins

Application processor signal names

Symbol

Pin name

USB 3.1 Gen 1

Normal

USB 3.1 Gen 1 and

DP2Lane

DP4Lane

Reversed

Normal

Reversed

Normal

Reversed

23

D_ION

SSRX-

ML0-

SSRX-

ML0-

ML3-

24

D_IOP

SSRX+

ML0+

SSRX+

ML0+

ML3+

3

C_INP

SSTX+

ML1+

SSTX+

ML1+

ML2+

4

C_INN

SSTX-

ML1-

SSTX-

ML1-

ML2-

5

A_INP

SSTX+

SSTX+

ML1+

ML2+

ML1+

6

A_INN

SSTX-

SSTX-

ML1-

ML2-

ML1-

9

B_IOP

SSRX+

SSRX+

ML0+

ML3+

ML0+

10

B_ION

SSRX-

SSRX-

ML0-

ML3-

ML0-

7

UAUXP

AUX+

AUX+

AUX+

AUX+

8

UAUXN

AUX-

AUX-

AUX-

AUX-

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

12 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

7.4 USB Type-C UFP receptacle application

1.8 V

VDD18

GND

Crossbar switch can

be integrated in

hub, or an external

component

USB Type-C

receptacle

B2/TX2+

A10/RX2-

B11/RX1+

B10/RX1-

A2/TX1+

A3/TX1B6/D+

B7/D-

(2)

B_ION

DRX2N

(1)

A_IP

DTX2P

(1)

A_IN

DTX2N

C_IP

DTX1P

C_IN

DTX1N

D_IOP

DRX1P

D_ION

DRX1N

UAUXN

DAUXN

UAUXP

DAUXP

DP0

DP1

DP2

DP3

SSTX

SSRX

A7/D1A6/D1+

A8/SBU1

B9/VBUS

B4/VBUS

DRX2P

USB 3.1 GEN 1 AND/OR DISPLAYPORT HUBS

A11/RX2+

B_IOP

DP4 LANE/USB3 CROSSBAR SWITCH

B3/TX2-

(2)

AUX-

A4/VBUS

A9/VBUS

B8/SBU2

B5/CC2

B1/GND

A5/CC1

A12/GND

B12/GND

A1/GND

PTN36502/PTN36502A CONTROLS

SCL

SDA

AUX+

3.3 V

EN

aaa-026910

Figure 4. Connection illustration when PTN36502/PTN36502A in UFP receptacle application

(1): 0.33μF capacitors are recommended on Type-C's receiver pins based on latest USB specification.

(2): 0.22μF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 4 for using PTN36502/PTN36502A in USB Type-C UFP receptacle

application. In this configuration, downstream (right) side of PTN36502/PTN36502A

is connected to USB 3.1 Gen 1 and/or DisplayPort hubs with integrated or on-board

crossbar switch function, and upstream (left) side is connected to Type-C receptacle.

Each pin on the upstream side of PTN36502/PTN36502A connecting to the Type-C

connector has specific input/output configuration, and must match the signal assignments

on the downstream side accordingly. Table 7 shows the upstream pin connection to

Type-C receptacle.

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

13 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Table 7. Upstream pin connection to Type-C receptacle in UFP application

PTN36502/PTN36502A pins

USB Type-C receptacle pins

Symbol

Pin name

Symbol

Pin name

23

D_ION

A3

TX1-

24

D_IOP

A2

TX1+

3

C_INP

B11

RX1+

4

C_INN

B10

RX1-

5

A_INP

A11

RX2+

6

A_INN

A10

RX2-

9

B_IOP

B2

TX2+

10

B_ION

B3

TX2-

7

UAUXP

B8

SBU2

8

UAUXN

A8

SBU1

The downstream pins of PTN36502/PTN36502A are connected to the USB 3.1 Gen

1 and/or DisplayPort hubs, with specific functions assigned to each differential signal.

For each pin assignment configuration below, PTN36502/PTN36502A controls which

transmitters or receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or

DisplayPort mode according to the mode setting.

Table 8. Downstream pin connection to USB 3.1 Gen 1/DisplayPort hubs in UFP receptacle application

PTN36502/PTN36502A

pins

Hub signal names

Symbol

Pin name

USB 3.1 Gen 1

USB 3.1 Gen 1 and

DP2Lane

DP4Lane

Normal

Normal

Reversed

Normal

Reversed

Reversed

22

DRX1P

SSTX+

SSTX+

ML0+

ML3+

ML0+

21

DRX1N

SSTX-

SSTX-

ML0-

ML3-

ML0-

18

DTX1N

SSRX-

SSRX-

ML1-

ML2-

ML1-

17

DTX1P

SSRX+

SSRX+

ML1+

ML2+

ML1+

16

DTX2P

SSRX+

ML1+

SSRX+

ML1+

ML2+

15

DTX2N

SSRX-

ML1-

SSRX-

ML1-

ML2-

12

DRX2N

SSTX-

ML0-

SSTX-

ML0-

ML3-

11

DRX2P

SSTX+

ML0+

SSTX+

ML0+

ML3+

14

DAUXP

AUX+

AUX+

AUX+

AUX+

13

DAUXN

AUX-

AUX-

AUX-

AUX-

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

14 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

7.5 USB Type-C UFP_Dongle application

1.8 V

VDD18

GND

Crossbar switch can

be integrated in

hub, or an external

component

USB Type-C

plug/pigtail

B11/RX1+

A2/TX1+

B2/TX2+

B3/TX2-

A11/RX2+

A10/RX2B6/D+

B7/D-

(2)

B_ION

DRX2N

(1)

A_IP

DTX2P

(1)

A_IN

DTX2N

C_IP

DTX1P

C_IN

DTX1N

D_IOP

DRX1P

D_ION

DRX1N

UAUXN

DAUXN

UAUXP

DAUXP

DP0

DP1

DP2

DP3

SSTX

SSRX

A7/D1A6/D1+

B8/SBU2

B9/VBUS

B4/VBUS

DRX2P

USB3 AND/OR DISPLAYPORT HUBS

A3/TX1-

B_IOP

DP4 LANE/USB3 CROSSBAR SWITCH

B10/RX1-

(2)

AUX-

A4/VBUS

A9/VBUS

A8/SBU1

B5/CC2

B1/GND

A5/CC1

A12/GND

B12/GND

A1/GND

PTN36502/PTN36502A CONTROLS

SCL

SDA

AUX+

3.3 V

EN

aaa-026914

Figure 5. Connection illustration when PTN36502/PTN36502A in UFP_Dongle application

(1): 0.33μF capacitors are recommended on Type-C's receiver pins based on latest USB specification.

(2): 0.22μF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 5 for using PTN36502/PTN36502A in USB Type-C UFP_Dongle

application. In this configuration, downstream (right) side of PTN36502/PTN36502A

is connected to USB 3.1 Gen 1 and/or DisplayPort hubs with integrated or on-board

crossbar switch function, and upstream (left) side is connected to Type-C plug.

Each pin on the upstream side of PTN36502/PTN36502A connecting to the Type-C

connector has specific input/output configuration, and must match the signal assignments

on the downstream side accordingly. Table 9 shows the upstream pin connection to

Type-C plug.

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

15 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

Table 9. Upstream pin connection to Type-C plug UFP_Dongle application

PTN36502/PTN36502A pins

USB Type-C receptacle pins

Symbol

Pin name

Symbol

Pin name

23

D_ION

A10

RX2-

24

D_IOP

A11

RX2+

3

C_INP

B2

TX2+

4

C_INN

B3

TX2-

5

A_INP

A2

TX1+

6

A_INN

A3

TX1-

9

B_IOP

B11

RX1+

10

B_ION

B10

RX1-

7

UAUXP

A8

SBU1

8

UAUXN

B8

SBU2

The downstream pins of PTN36502/PTN36502A are connected to the USB 3.1 Gen

1 and/or DisplayPort hubs, with specific functions assigned to each differential signal.

For each pin assignment configuration below, PTN36502/PTN36502A controls which

transmitters or receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or

DisplayPort mode according to the mode setting.

A typical dongle has a fixed orientation design, usually the normal orientation. Therefore,

only one CC line is connected on the USB Type-C plug, and the other CC line is being

used for VCONN purpose. PTN36502/PTN36502A offers both normal and reversed

orientation pin outs, and can be adapted to different layout requirements. However, in a

typical dongle use case, only one orientation is necessary.

Table 10. Downstream pin connection to USB 3.1 Gen 1/DisplayPort hubs in UFP_Dongle application

PTN36502/

PTN36502A

pins

Hub signal names

Symbol

Pin name

USB 3.1 Gen 1

Normal

USB 3.1 Gen 1 and

DP2Lane

DP4Lane

Reversed

Normal

Reversed

Normal

Reversed

22

DRX1P

SSTX+

ML0+

SSTX+

ML0+

ML3+

21

DRX1N

SSTX-

ML0-

SSTX-

ML0-

ML3-

18

DTX1N

SSRX-

ML1-

SSRX-

ML1-

ML2-

17

DTX1P

SSRX+

ML1+

SSRX+

ML1+

ML2+

16

DTX2P

SSRX+

SSRX+

ML1+

ML2+

ML1+

15

DTX2N

SSRX-

SSRX-

ML1-

ML2-

ML1-

12

DRX2N

SSTX-

SSTX-

ML0-

ML3-

ML0-

11

DRX2P

SSTX+

SSTX+

ML0+

ML3+

ML0+

14

DAUXP

AUX+

AUX+

AUX+

AUX+

13

DAUXN

AUX-

AUX-

AUX-

AUX-

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

16 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

7.6 Control and programmability

PTN36502/PTN36502A implements ternary control IO logic on EN, C1/SCL, C2/SDA

control pins to detect HIGH (connected to VDD), LOW (connected to GND) or left

2

unconnected condition (OPEN/NC). These pins are 3.3 V tolerant in I C mode, and 1.8 V

tolerant in GPIO mode.

The following sections describe the individual block functions and capabilities of the

device in more detail. In general, depending on the EN transition, there are specific

functions for each transition state. Figure 6 and Figure 7 illustrate transitions described

above. Hi-Z and OPEN/NC are used interchangeably in these figures.

VDD=1.8 V

Factory Test Mode

1

EN=?

Hi-Z

I2C Mode

0

Chip Power Down

EN=?

0→1

Mode Configuration

1→0

EN=?

Monitor C1/C2 (SCL/SDA) for channel settings

1→Hi-Z

Mode

Reconfiguration

Mode Reconfiguration

Applied

EN=Hi-Z→1

aaa-026915

Figure 6. GPIO mode control flow chart

VDD18

tsetup3

thold1

EN

Hi-Z

thold3

thold2

Mode

Config

DFP/UFP/UFP_Dongle

SCL/SDA

C1/C2

C1/C2

New Mode

Config

C1/C2

thold4

Function

DFP /UFP/UFP_Dongle configured.

Enter GPIO Mode. Deep Power Saving

Mode

Configuration

Set C1/C2

Channel Conditions

Mode Reconfiguration

Set C1/C2 Channel

Conditions

Chip Disabled,

Deep Power Saving

aaa-026916

Figure 7. GPIO mode control sequence diagram illustration

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

17 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

2

7.6.1 Operating mode selection (I C mode or GPIO mode)

Upon POR, PTN36502/PTN36502A starts to detect the state of EN pin. If EN is

not driven (or left OPEN) during POR, PTN36502/PTN36502A defaults to operate

2

2

2

in I C mode, and EN pin has no function after entering I C mode. In I C mode,

PTN36502/PTN36502A is highly programmable. For more information, please reference

2

Section 7.6.6 for I C register details.

If EN is driven LOW during POR (through a GPIO from host processor or external

pull down resistor), the PTN36502/PTN36502A will be placed in GPIO mode. At the

same time, PTN36502/PTN36502A is configured in DFP, UFP, or UFP_Dongle modes

depending on SCL/C1 and SDA/C2 pins’ status (refer to Table 11 below). By default, the

chip is disabled in deep power saving mode after DFP/UFP/UFP_Dongle configuration

is detected. In the deep power saving mode, all PTN36502/PTN36502A line drivers and

input receive paths are terminated to ground with hi-ohmic resistors and AUX switches

are tri-stated, and mode configuration remains undetermined.

VDD=1.8 V

Factory Test Mode

1

EN=?

Hi-Z

I2C Mode

0

DFP/UFP/UFP_Dongle

Set Chip Power Down

aaa-026917

Figure 8. EN control flow diagram

Table 11. EN control for various mode setting during POR

EN

SCL/C1

SDA/C2

Mode

OPEN

X

X

I C Mode

0

0

0

GPIO Mode – DFP Configuration, without external 4.7 Ω resistors on

the DRXn pins.

0

1

GPIO Mode – DFP Configuration, with external 4.7 Ω resistors added

on the DRXn pins for higher level surge protection.

1

0

GPIO Mode – UFP Configuration.

0

0

GPIO Mode – UFP_Dongle Configuration.

X

X

Reserved Operation Mode

1

2

7.6.2 Mode configuration through GPIO mode

Table 12, Table 13, and Table 14 show seven possible modes in which PTN36502/

PTN36502A can be configured while operating in DFP, UFP, or UFP plug modes

respectively. Note that mode configuration setting is latched when EN transition from 0

to 1. When the mode needs to be reconfigured (for example, change from USB 3.1 Gen

1+DP2Lane mode to DP4Lane mode) after EN is 1, a GPIO controller can toggle EN

pin to Hi-Z first and back to high again with new mode presented on SCL/C1 and SDA/

PTN36502_PTN36502A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

© NXP B.V. 2018. All rights reserved.

18 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

C2 pins. New mode value is latched when EN transition from Hi-Z to 1, and may take up

to 0.2 milliseconds to take effect. When EN is toggled back to 0, mode configuration is

cleared, and the PTN36502/PTN36502A is placed in deep power saving mode.

• C1/SCL indicates the orientation, 0 = normal orientation, 1 = reversed orientation

• C2/SDA indicates different mode configurations

– OPEN=USB 3.1 Gen 1 only, no AUX support

– 0 = USB 3.1 Gen 1 + DP 2Lane + AUX

– 1 = DP 4Lane + AUX

Definitions of different lane TX and RX paths in the tables are illustrated in Figure 9.

Lane D RX path

D_IOP

DRX1P

D_ION

DRX1N

C_IP

DTX1P

C_IN

DTX1N

A_IP

DTX2P

A_IN

DTX2N

B_IOP

DRX2P

B_ION

DRX2N

Lane D TX path

Lane C TX path

Lane A TX path

Lane B TX path

Lane B RX path

UAUXP

DAUXP

AUX path

UAUXN

DAUXN

aaa-026918

Figure 9. Different lane TX and RX paths definitions

Table 12. PTN36502/PTN36502A DFP mode configuration

EN

SCL/C1

Transition 0

from 0 to

1

1

PTN36502_PTN36502A

Product data sheet

SDA/ C2 Lane A

TX

Lane B

TX

Lane B

RX

Lane C

TX

Lane D

TX

Lane D

RX

OPEN

SSTX

SSRX

[1]

[1]

OPEN

[1]

[1]

SSTX

SSRX

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

AUX

Path

Mode

Type-C

orientat

ion

USB

3.1 Gen

1 Only

(M=1)

Normal

(Or=0)

Reversed

(Or=1)

© NXP B.V. 2018. All rights reserved.

19 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

EN

[1]

SCL/C1

SDA/ C2 Lane A

TX

Lane B

TX

Lane B

RX

Lane C

TX

Lane D

TX

SSRX

ML1

ML0

Lane D

RX

0

0

SSTX

1

0

ML1

ML0

SSTX

0

1

ML2

ML3

ML1

ML0

Thru

1

1

ML1

ML0

ML2

ML3

Cross

Lane B

RX

Lane C

TX

Lane D

TX

SSRX

AUX

Path

Mode

Type-C

orientat

ion

Thru

USB 3.1

Gen 1

& DP2

Lane

(M=2)

Normal

(Or=0)

DP4

Lane

(M=3)

Normal

(Or=0)

Mode

Type-C

orientat

ion

USB

3.1 Gen

1 Only

(M=1)

Normal

(Or=0)

USB 3.1

Gen 1

& DP2

Lane

(M=2)

Normal

(Or=0)

Cross

Reversed

(Or=1)

Reversed

(Or=1)

Unused TX and RX pins are terminated to ground with hi-ohmic resistors

Table 13. PTN36502/PTN36502A UFP mode configuration

EN

SCL/C1

Lane B

TX

Lane D

RX

OPEN

[1]

[1]

SSRX

SSTX

OPEN

SSRX

SSTX

[1]

[1]

0

0

ML1

SSRX

SSTX

1

0

SSRX

0

1

ML1

1

1

ML2

Transition 0

from 0 to

1

1

[1]

SDA/ C2 Lane A

TX

ML0

SSTX

AUX

Path

Thru

ML1

ML0

Cross

ML0

ML2

ML3

Thru

ML3

ML1

ML0

Cross

Reversed

(Or=1)

Reversed

(Or=1)

DP4Lane Normal

(M=3)

(Or=0)

Reversed

(Or=1)

Unused TX and RX pins are terminated to ground with hi-ohmic resistors

Table 14. PTN36502/PTN36502A UFP_Dongle mode configuration

EN

SCL/C1

SDA/ C2 Lane A

TX

Lane B

TX

Lane B

RX

Lane C

TX

Lane D

TX

Lane D

RX

OPEN

SSRX

SSTX

[1]

[1]

OPEN

[1]

[1]

SSRX

SSTX

0

0

SSRX

SSTX

ML1

1

0

ML1

Transition 0

from 0 to

1

1

PTN36502_PTN36502A

Product data sheet

ML0

ML0

SSRX

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 28 September 2018

AUX

Path

Thru

SSTX

Cross

Mode

Type-C

orientat

ion

USB

3.1 Gen

1 Only

(M=1)

Normal

(Or=0)

USB 3.1

Gen 1

& DP2

Lane

(M=2)

Normal

(Or=0)

Reversed

(Or=1)

Reversed

(Or=1)

© NXP B.V. 2018. All rights reserved.

20 / 58

�PTN36502/PTN36502A

NXP Semiconductors

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

EN

[1]

SCL/C1

SDA/ C2 Lane A

TX

Lane B

TX

0

1

ML2

1

1

ML1

Lane B

RX

Lane C

TX

Lane D

TX

ML3

ML1

ML0

ML2

Lane D

RX

AUX

Path

Mode

Type-C

orientat

ion

ML0

Thru

Normal

(Or=0)

ML3

Cross

DP4

Lane

(M=3)

Reversed

(Or=1)

In USB 3.1 Gen 1 only mode, unused line drivers (TX) and input receivers (RX) are terminated to common mode (