TJA1085

FlexRay active star coupler

Rev. 2 — 7 March 2016

Product data sheet

1. General description

The TJA1085 is a FlexRay active star coupler that can connect up to 4 branches of a

FlexRay network. The TJA1085 is compliant with the FlexRay electrical physical layer

specification V3.0.1/ISO17458-4 (see Ref. 1 and Ref. 2).

Several TJA1085 devices can be connected via their TRXD0/1 interfaces to increase the

number of branches in the network. A dedicated Communication Controller (CC) interface

allows for integration into an ECU. The TJA1085 supports low-power management by

offering bus wake-up capability along with battery supply and voltage regulator control.

The TJA1085 meets industry standards for EMC/ESD performance and provides

enhanced bus error detection, low current consumption and unmatched asymmetric delay

performance.

The TJA1085 also fulfills the JASPAR requirements as defined by the Japanese car

industry.

2. Features and benefits

2.1 General

Compliant with FlexRay Electrical Physical Layer specification V3.0.1/ISO17458-4

Fulfills JASPAR requirements

Automotive product qualification in accordance with AEC-Q100

Data transfer rates from 2.5 Mbit/s to 10 Mbit/s

Supports 60 ns minimum bit time at 400 mV differential voltage

Low-power management for battery-supplied ECUs

Very low current consumption in AS_Sleep mode

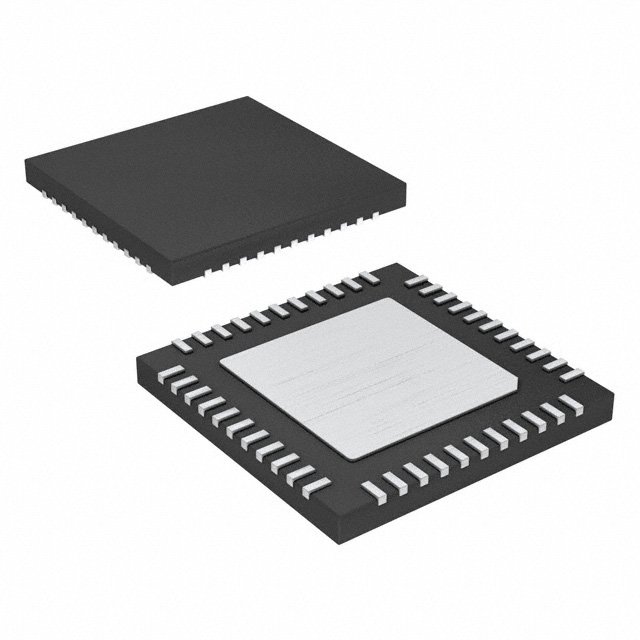

Leadless HVQFN44 package with improved Automated Optical Inspection (AOI)

capability

2.2 Functional

Supports autonomous active star operation independent of the host ensuring the

TJA1085 remains active even if the host fails or is switched off

Branches can be independently configured

Branch extension via TRXD0/1 inner star interface

16-bit bidirectional SPI interface up to 2 Mbit/s for host communication

Full host control over branch status

Enhanced wake-up capability:

Remote wake-up via wake-up pattern and dedicated FlexRay data frames

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Local wake-up via pin LWU

Wake-up source recognition

configurable per branch

Enhanced supply voltage monitoring on VIO, VCC, VBUF and VBAT

Auto I/O level adaptation to host controller supply voltage VIO

Can be used in 14 V, 24 V and 48 V powered systems

Enhanced bus error detection - detects short-circuit conditions on the bus

Instant transmitter shut-down interface (BGE pin)

Selective branch shut-down (partial networking)

2.3 Robustness

Bus pins protected against 8 kV ESD pulses according to HBM and 6 kV ESD

pulses according to IEC61000-4-2

All pins protected against 1000 V ESD according to CDM

All pins protected against 200 V ESD according to MM

No reverse currents from the digital input pins to VIO or VCC when the TJA1085 is not

powered up

Bus pins short-circuit proof to battery voltage (14 V, 24 V or 48 V) and ground

Overtemperature detection and protection

Bus pins protected against transients in automotive environment (according to ISO

7637 class C)

2.4 Active star functional classes

Active star - communication controller interface

Active star - bus guardian interface

Active star - voltage regulator control

Active star - logic level adaptation

Active star - host interface

Active star - increased voltage amplitude transmitter

3. Ordering information

Table 1.

Ordering information

Type number

Package

Name

TJA1085HN

TJA1085

Product data sheet

Description

Version

HVQFN44 plastic thermal enhanced very thin quad flat package; no leads; 44 terminals; SOT1113-1

body 9 9 0.85 mm

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

2 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

4. Block diagram

VIO

VBAT

VCC1

VCC2

VBUF1

VBUF2

7

17

34

22

35

21

TJA1085

INH

INTN

RSTN

15

WAKE-UP

TRANSMITTER

BUS ERROR

RECEIVER

WAKE-UP

TRANSMITTER

BUS ERROR

RECEIVER

WAKE-UP

TRANSMITTER

BUS ERROR

RECEIVER

WAKE-UP

TRANSMITTER

BUS ERROR

RECEIVER

33

BP_1

5

44

32

BM_1

STATE

MACHINE

SCSN

SCLK

SDI

SDO

LWU

TRXD1

TRXD0

BGE

1

2

3

SPI

TXD

RXD

BP_2

4

16

29

BM_2

ROUTING

13

12

27

BP_3

8

&

TXEN

30

26

BM_3

10

9

11

6

37

19

GND1

GND2

24

23

BP_4

BM_4

015aaa152

GNDD

Fig 1.

Block diagram

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

3 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

5. Pinning information

34 VCC1

35 VBUF1

36 n.c.

37 GND1

38 RES6

39 RES5

40 RES4

41 RES3

42 RES2

43 RES1

44 RSTN

5.1 Pinning

SCSN

1

33 BP_1

SCLK

2

32 BM_1

SDI

3

31 n.c.

SDO

4

30 BP_2

INTN

5

GNDD

6

VIO

7

27 BP_3

BGE

8

26 BM_3

TXD

9

25 n.c.

29 BM_2

TJA1085

28 n.c.

VCC2 22

VBUF2 21

n.c. 20

GND2 19

n.c. 18

VBAT 17

LWU 16

INH 15

n.c. 14

23 BM_4

TRXD1 13

24 BP_4

RXD 11

TRXD0 12

TXEN 10

015aaa150

Transparent top view

Fig 2.

Pin configuration

5.2 Pin description

Table 2.

TJA1085

Product data sheet

Pin description

Symbol Pin

Type[1]

Description

SCSN

I

SPI chip select input; internal pull-up

1

SCLK

2

I

SPI clock signal; internal pull-down

SDI

3

I

SPI data input; internal pull-down

SDO

4

O

SPI data output; 3-state output

INTN

5

O

interrupt output; open-drain output, low-side driver

GNDD

6

G

ground for digital circuits[2]

VIO

7

P

supply voltage for VIO voltage level adaptation

BGE

8

I

bus guardian enable input; internal pull-down

TXD

9

I

transmit data input; internal pull-down

TXEN

10

I

transmitter enable input; internal pull-up

RXD

11

O

receive data output

TRXD0

12

IO

data bus line 0 for inner star connection

TRXD1

13

IO

data bus line 1 for inner star connection

n.c.

14

-

not connected; to be connected to GND in application

INH

15

O

inhibit output; for switching external voltage regulator

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

4 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Table 2.

TJA1085

Product data sheet

Pin description …continued

Symbol Pin

Type[1]

Description

LWU

16

I

local wake-up input; internal pull-up or pull-down (depends on

voltage at pin LWU)

VBAT

17

P

battery supply voltage

n.c.

18

-

not connected; to be connected to GND in application

GND2

19

G

ground connection for branches 3 and 4[2]

n.c.

20

-

not connected; to be connected to GND in application

VBUF2

21

P

buffer supply voltage for branches 3 and 4[3]

VCC2

22

P

supply voltage for branches 3 and 4[4]

BM_4

23

IO

bus line minus for branch 4[5]

BP_4

24

IO

bus line plus for branch 4[6]

n.c.

25

-

not connected; to be connected to GND in application

BM_3

26

IO

bus line minus for branch 3[5]

BP_3

27

IO

bus line plus for branch 3[6]

n.c.

28

-

not connected; to be connected to GND in application

BM_2

29

IO

bus line minus for branch 2[5]

BP_2

30

IO

bus line plus for branch 2[6]

n.c.

31

-

not connected; to be connected to GND in application

BM_1

32

IO

bus line minus for branch 1[5]

BP_1

33

IO

bus line plus for branch 1[6]

VCC1

34

P

supply voltage for branches 1 and 2[4]

VBUF1

35

P

buffer supply voltage for branches 1 and2[3]

n.c.

36

-

not connected; to be connected to GND in application

GND1

37

G

ground connection for branches 1 and 2[2]

RES6

38

-

reserved; to be connected to GND in application

RES5

39

-

reserved; to be connected to GND in application

RES4

40

-

reserved; to be connected to GND in application

RES3

41

-

reserved; to be connected to GND in application

RES2

42

-

reserved; to be connected to GND in application

RES1

43

-

reserved; to be connected to GND in application

RSTN

44

I

reset input; internal pull-up

[1]

IO: input/output; O: output; I: input; P: power supply; G: ground.

[2]

GND1, GND2, GNDD and the exposed center pad of HVQFN44 package must be connected together on

the PCB; references in the data sheet to GND can be assumed to encompass GND1, GND2, GNDD and

the exposed center pad of HVQFN4 unless stated otherwise.

[3]

VBUF1 and VBUF2 must be connected together on the PCB; note that references in the data sheet to VBUF

can be assumed to encompass VBUF1 and VBUF2 unless stated otherwise.

[4]

VCC1 and VCC2 must be connected together on the PCB; note that references in the data sheet to VCC can

be assumed to encompass VCC1 and VCC2 unless stated otherwise.

[5]

References in the data sheet to BM (e.g. pin BM or VBM) can be assumed to encompass BM_1, BM_2,

BM_3 and BM_4 unless stated otherwise.

[6]

References in the data sheet to BP (e.g. pin BP or VBP) can be assumed to encompass BP_1, BP_2, BP_3

and BP_4 unless stated otherwise.

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

5 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6. Functional description

6.1 Supply voltage

The TJA1085 state machine is adequately supplied if at least one of VBAT, VCC or VBUF is

available. The internal supply voltage to the state machine is denoted by VDIG. VBUF is an

auxiliary supply and is only needed for forwarding the wake-up pattern when VCC is not

available.

6.2 Host Control (HC) and Autonomous Power (AP) modes - APM flag

The APM flag determines whether the TJA1085 is host-controlled or is operating in

Autonomous Power mode. It is in AP mode by default.

The TJA1085 sets the APM flag:

•

•

•

•

at power-on

when a wake-up event is detected (on TXRD0/1, local or remote)

when a VCC undervoltage event is detected in AS_Normal mode

when a VIO undervoltage event lasts longer than tto(uvd)(VIO)

The host can set or reset the APM flag at any time.

6.3 Signal router

The signal router transfers data received on an input channel to all channels configured as

outputs. If data is being received on more than one input channel at the same time, the

channel that was first to signal activity is selected and data on the other channel/s is

ignored. Whether or not the data on an output channel is transmitted depends on whether

the output channel is enabled or disabled.

The TJA1085 contains the following data input channels:

• Branches 1 to 4

• TRXD0/1 interface (inner star interface)

• TXD/TXEN interface

The TJA1085 contains the following data output channels:

• Branches 1 to 4

• TRXD0/1 interface

• RXD pin

6.3.1 TRXD collision

When the TRXD0/1 interface is configured as an output channel, a TRXD collision is

detected (COLL_TRXD = 1) if pins TRXD0 and TRXD1 are both LOW for longer than

tdet(col)(TRXD), generating a CLAMP_ERROR interrupt.

When a TRXD collision is detected, the TJA1085 transmits a DATA_0 to all other active

output channels (irrespective of the actual data on the selected input channel), until the

selected input channel detects idle state.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

6 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.4 Wake-up

The TJA1085 supports the following wake-up mechanisms:

• Remote wake-up via the bus (wake-up pattern or dedicated wake-up frame)

• Local wake-up via pin LWU

• Activity on the inner star interface (pins TRXD0 and TRXD1)

Any wake-up event will generate a WU interrupt. A remote wake-up on a branch will

generate an EVENT_BRx interrupt to indicate the branch where the wake-up pattern or

dedicated data frame was detected.

The host can identify the wake-up source by polling the General Status register

(WU_TRXD = 1 for a TRXD0/1 wake-up; WU_LOCAL = 1 for a local wake-up) and the

Branch Status register (WU_BRx = 1 for a remote wake-up).

6.4.1 Remote wake-up

When the TJA1085 is in AS_Standby or AS_Sleep, all branches are monitored for

wake-up events. When a valid wake-up pattern or data frame is detected on a branch, the

relevant WU_BRx status bit is set and the wake-up pattern/data frame is forwarded to all

other enabled branches.

A remote wake-up event occurring during an AS_Normal-to-AS_Standby or

AS_Normal-to-AS_Sleep transition will also be detected, setting the relevant WU_BRx

status bit and generating WU and EVENT_BRx interrupts.

6.4.1.1

Bus wake-up via wake-up pattern

A wake-up pattern consists of at least two consecutive wake-up symbols. A wake-up

symbol consists of a DATA_0 phase lasting longer than tdet(wake)DATA_0, followed by an idle

phase lasting longer than tdet(wake)idle, provided both wake-up symbols occur within a time

span of tdet(wake)tot (see Figure 3). The transceiver also wakes up if the idle phases are

replaced by DATA_1 phases.

A wake-up event is not detected if an invalid wake-up pattern is received. See Ref. 1 for

more details on invalid wake-up patterns.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

7 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

ZDNH�XS

��WGHW�ZDNH�WRW

9GLI

�P9�

!�WGHW�ZDNH�LGOH

!�WGHW�ZDNH�LGOH

�

����

!�WGHW�ZDNH�'$7$B�

!�WGHW�ZDNH�'$7$B�

!�WGHW�ZDNH�LGOH

!�WGHW�ZDNH�LGOH

����

�

����

!�WGHW�ZDNH�'$7$B�

!�WGHW�ZDNH�'$7$B�

ZDNH�XS�V\PERO

ZDNH�XS�V\PERO

ZDNH�XS�SDWWHUQ

���DDD���

Fig 3. Bus wake-up timing

See Ref. 1 for more details of the wake-up mechanism.

6.4.1.2

Bus wake-up via dedicated FlexRay data frame

The TJA1085 detects a wake-up event when a dedicated data frame emulating a valid

wake-up pattern, as shown in Figure 4, is received.

The Data_0 and Data_1 phases of the emulated wake-up symbol are interrupted by the

Byte Start Sequence (BSS) preceding each byte in the data frame. With a data rate of

10 Mbit/s, the interruption has a maximum duration of 130 ns and does not prevent the

transceiver from recognizing the wake-up pattern in the payload.

For longer interruptions at lower data rates (5 Mbit/s and 2.5 Mbit/s), the wake-up pattern

should be used (see Section 6.4.1.1).

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

8 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Vdif

130 ns

wake-up

870 ns 870 ns

+2000

0V

-2000

770 870 870

ns ns

ns

130 130

ns

ns

5 µs

5 µs

5 µs

5 µs

015aaa343

The duration of each interruption is 130 ns.

The transition time from DATA_0 to DATA_1 and vice versa is about 20 ns.

The TJA1085 wake-up flag is set on receipt of the following frame payload:

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x00, 0x00, 0x00, 0x00,

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF

Fig 4.

Minimum bus pattern for bus wake-up via dedicated FlexRay data frame

6.4.2 Local wake-up via pin LWU

Local wake-up is detected when the voltage on pin LWU is lower than Vth(wake)(LWU) for

longer than tdet(wake)(LWU) (falling edge on pin LWU). When local wake-up is detected, the

WU_LOCAL status bit is set and a WU interrupt is generated. At the same time, the

internal biasing of this pin is switched to pull-down.

If the voltage on pin LWU rises and remains above Vth(wake)(LWU) for longer than

tdet(wake)(LWU) (rising edge on pin LWU), local wake-up is not detected and the biasing on

pin LWU is switched to pull-up.

pull-up

tdet(wake)(LWU)

pull-up

pull-down

tdet(wake)(LWU)

VBAT

LWU

0V

td(LWUwake-INHH)

INH

VBAT

0V

015aaa178

Fig 5. Local wake-up timing on pin LWU

6.4.3 Wake-up via the TRXD0/1 interface

If the voltage on pin TRXD0 or pin TRXD1 is LOW for longer than tdet(wake)(TRXD), a WU

interrupt is generated and the WU_TRXD status bit is set.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

9 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.5 Communication controller interface

6.5.1 Bus activity and idle detection

The following mechanisms for activity and idle detection are valid in normal power modes:

• If the absolute differential voltage on the bus lines is higher than Vi(dif)det(act) for

tdet(act)(bus), activity is detected on the bus lines

• If, after bus activity detection, the differential voltage on the bus lines is higher than

VIH(dif), pin RXD will go HIGH

• If, after bus activity detection, the differential voltage on the bus lines is lower than

VIL(dif), pin RXD will go LOW

• If the absolute differential voltage on the bus lines is lower than Vi(dif)det(act) for

tdet(idle)(bus), then idle is detected on the bus lines (pin RXD is switched HIGH or

remains HIGH)

Additionally, activity and idle can be detected:

• if pin TXEN is LOW for longer than tdet(act)(TXEN), activity is detected on pin TXEN

• if pin TXEN is HIGH for longer than tdet(idle)(TXEN), idle is detected on pin TXEN

• if pin TRXD0 or TRXD1 is LOW for longer than tdet(act)(TRXD), activity is detected on the

TRXD0/1 interface

• if pins TRXD0 and TRXD1 are both HIGH for longer than tdet(idle)(TRXD), idle is

detected on the TRXD0/1 interface

Transmitter input signals: TXD, TXEN and BGE[1]

Table 3.

TXD

TXEN

BGE

VIO UV

detected

RXD

Bus

TRXD0

X

H

X

no

HIGH

idle

high ohmic[2] high ohmic[2] AS_Normal

X

X

L

no

HIGH

idle

high ohmic[2] high ohmic[2] AS_Normal

L

L

H

no

LOW

DATA_0

LOW

H

L

H

no

HIGH

DATA_1

high ohmic[2] LOW

ohmic[2]

TRXD1

Operating mode

high ohmic[2] AS_Normal

high

ohmic[2]

AS_Normal

AS_Standby,[3] AS_Sleep[3]

X

X

X

no

HIGH

idle

high

X

X

X

yes

LOW

idle

high ohmic[2] high ohmic[2] AS_Normal,

AS_Standby,[3] AS_Sleep[3]

X

X

X

X

HIGH

float

high ohmic[2] high ohmic[2] AS_PowerOff, AS_Reset

[1]

The transmitter is activated by a falling edge on pin TXD while TXEN is LOW and BGE is HIGH.

[2]

Internal pull-up resistor (Rpu) to VBUF.

[3]

BP and BM biased to GND.

Table 4.

Bus

VIO UV

detected

RXD

TRXD0

TRXD1

Operating mode

DATA_0

no

LOW

LOW

high ohmic[1]

AS_Normal

DATA_1

no

HIGH

high ohmic[1]

LOW

AS_Normal

idle

no

HIGH

high ohmic[1]

high ohmic[1]

AS_Normal

HIGH

ohmic[1]

ohmic[1]

X

TJA1085

Product data sheet

Bus as input

no

high

high

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

AS_Standby, AS_Sleep

© NXP Semiconductors N.V. 2016. All rights reserved.

10 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Table 4.

Bus as input

Bus

VIO UV

detected

RXD

TRXD0

TRXD1

Operating mode

DATA_0

yes

LOW

LOW

high ohmic[1]

AS_Normal

LOW

AS_Normal

DATA_1

yes

LOW

high

ohmic[1]

ohmic[1]

high

ohmic[1]

idle

yes

LOW

high

X

yes

LOW

high ohmic[1]

high ohmic[1]

HIGH

ohmic[1]

ohmic[1]

X

[1]

X

high

high

AS_Normal

AS_Standby, AS_Sleep

AS_PowerOff, AS_Reset

Internal pull-up resistor (Rpu) to VBUF.

Table 5.

TRXD0/1 interface configured as input

TRXD0

TRXD1

X

RXD

Bus

Operating mode

falling edge no

HIGH

DATA_1

AS_Normal[1]

HIGH

HIGH

no

HIGH

idle

AS_Normal

falling edge

X

X

LOW

DATA_0

AS_Normal[1]

X

falling edge yes

LOW

DATA_1

AS_Normal[1]

HIGH

HIGH

yes

LOW

idle

AS_Normal

LOW

LOW

X

LOW

DATA_0

collision detected on TRXD0/1

[1]

VIO UV

detected

Activity detected on TRXD0/TRXD1.

6.6 Bus error detection

The TJA1085 provides bus error detection on each branch during data transmission.

When a transmit error (TxE_BRx = 1) is detected on a branch, an EVENT_BRx interrupt is

generated to notify the host.

The following conditions trigger bus error detection:

•

•

•

•

•

Short circuit BP to BM

Short-circuit BP to GND

Short-circuit BM to GND

Short-circuit BP to VCC or VBAT

Short-circuit BM to VCC or VBAT

6.7 Interrupt generation

Interrupts are generated when specific events take place or associated status bits in the

General or Branch X status registers are set. When an interrupt is generated, the relevant

interrupt status bit is set in the Interrupt Status register (see Table 9) and pin INTN is

forced LOW.

Some interrupt status bits (PWON, WU, SPI_ERROR and HC_ERROR) are reset

immediately after the Interrupt Status register has been read successfully (i.e. a rising

edge on SCSN with no SPI_ERROR).

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

11 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

The UV_ERROR, CLAMP_ERROR, TEMP_ERROR and EVENT_BRx status bits are

reset after the flag (or flags) that triggered the interrupt has been reset and a successful

read operation had been performed (these two events can occur in any order). Resetting

these bits triggers a further falling edge on INTN to indicate to the host that the issue that

triggered the interrupt has been resolved (except in the case of EVENT_BRx if a branch

wake-up event triggered the interrupt). See Section 6.10.2.3 for further details.

INTN signaling conforms to the FlexRay Electrical Physical Layer specification V3.0.1

(see Ref. 1).

6.8 Operating modes

The TJA1085 features five operating modes.

AS_PowerOff, AS_Sleep and AS_Standby are low-power modes in which the transceiver

is unable to transmit or receive data streams on the bus. In AS_PowerOff mode, only

power-on reset detection is active. The SPI, the low-power receiver and wake-up

detection are active in AS_Sleep mode. Undervoltage detection is enabled on VCC, VBAT

and VBUF in AS_Standby and AS_Normal modes. VIO undervoltage detection is always

enabled, except when the TJA1085 is in AS_PowerOff mode.

In AS_Normal mode, the TJA1085 can transmit and receive data streams on the bus.

Pin INH is HIGH in AS_Normal, AS_Standby and AS_Reset, and floating in AS_PowerOff

and AS_Sleep.

The dStarGoToSleep timer is started when the TJA1085 switches to AS_Standby or

AS_Normal, or when idle is detected on the bus. The timer is halted and reset when

activity is detected on the bus.

6.8.1 Operating mode transitions

6.8.1.1

AS_PowerOff

The TJA1085 switches to AS_PowerOff from any mode if the internal supply to the state

machine, VDIG, falls below the power-on detection threshold voltage (Vth(det)POR). It

remains in AS_PowerOff until VDIG rises above the power-on recovery threshold voltage

(Vth(rec)POR), when it switches to AS_Standby. Pins INTN and SDO are switched to a

high-impedance state in AS_PowerOff mode.

6.8.1.2

AS_Reset

The TJA1085 switches to AS_Reset from any mode if pin RSTN goes LOW with no

undervoltage detected on VIO. It remains in AS_Reset until pin RSTN goes HIGH, when it

switches to AS_Standby.

6.8.1.3

AS_Standby

The TJA1085 switches to AS_Standby:

- from AS_PowerOff when VDIG rises above the power-on recovery threshold voltage

(Vth(rec)POR)

- from AS_Reset when pin RSTN goes HIGH

- from AS_Normal when a VCC undervoltage event is detected (VCC < Vuvd(VCC) for

longer than tdet(uv)(VCC))

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

12 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

- from AS_Normal in response to a host ‘AS_Standby’ command (HC mode)

- from AS_Sleep in response to a host ‘AS_Standby’ command (HC mode)

- from AS_Sleep when a wake-up event is detected

The TJA1085 switches from AS_Standby:

- to AS_Normal when a wake-up event is detected, provided VBUF > Vuvr(VBUF)

- to AS_Normal when a VCC undervoltage recovery event is detected (VCC > Vuvr(VCC)

for longer than trec(uv)(VCC)), provided VBUF > Vuvr(BUF)

- to AS_Normal in response to a host ‘AS_Normal’ command (HC mode)

- to AS_Sleep if the dStarGoToSleep timer expires (AP mode)

- to AS_Sleep if a VCC undervoltage event lasts longer than tto(uvd)(VCC) (HC mode)

- to AS_Sleep in response to a host ‘AS_Sleep’ command (HC mode)

6.8.1.4

AS_Sleep

A wake-up event will trigger a transition to AS_Standby (followed by a transition to

AS_Normal if VBUF > Vuvr(VBUF)).

The TJA1085 switches to AS_Sleep:

- from AS_Standby in response to a host ‘AS_Sleep’ command (HC mode)

- from AS_Standby if the dStarGoToSleep timer expires (AP mode)

- from AS_Standby if a VCC undervoltage event lasts longer than tto(uvd)(VCC) (HC mode)

- from AS_Normal in response to a host ‘AS_Sleep’ command (HC mode)

- from AS_Normal if the dStarGoToSleep timer expires (AP mode)

The TJA1085 switches from AS_Sleep:

- to AS_Standby in response to a host ‘AS_Standby’ command (HC mode)

- to AS_Standby when a wake-up event is detected.

- to AS_Normal in response to a host ‘AS_Normal’ command (HC mode)

6.8.1.5

AS_Normal

The TJA1085 switches to AS_Normal:

- from AS_Standby if a VCC undervoltage recovery event is detected (VCC > Vuvr(VCC) for

longer than trec(uv)(VCC)), provided VBUF > Vuvr(BUF)

- from AS_Standby if a wake-up event is detected, provided VBUF > Vuvr(VBUF) for longer

than trec(uv)(VBUF)

- from AS_Standby or AS_Sleep in response to a host ‘AS_Normal’ command

The TJA1085 switches from AS_Normal:

- to AS_Standby when a VCC undervoltage event is detected (VCC < Vuvd(VCC) for longer

than tdet(uv)(VCC))

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

13 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

- if the TJA1085 is in HC mode, it will switch from AS_Standby to AS_Sleep if the

VCC undervoltage persists for longer than tto(uvd)(VCC)

- if the TJA1085 is in AP mode, it will switch to AS_Sleep when the dStarGoToSleep

timer expires

- to AS_Standby in response to a host ‘AS_Standby’ command (HC mode)

- to AS_Sleep in response to a host ‘AS_Sleep’ command (HC mode)

- to AS_Sleep if the dStarGoToSleep timer expires (AP mode)

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

14 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.8.1.6

Operating mode transition diagram

from any mode

if VDIG < Vth(det)POR

AS_PowerOff

AS_Reset

from any mode if

RSTN goes LOW with

no VIO undervoltage

VDIG > Vth(rec)POR

RSTN goes HIGH

AS_Standby

VCC undervoltage >

tto(uvd)(VCC) OR

host command ('Sleep')

VCC undervoltage detected OR

host command ('Standby')

(wake-up event AND VBUF > Vuvr(VBUF)) OR

(VCC undervoltage recovery

AND VBUF > Vuvr(VBUF))

AS_Normal

dStarGoToSleep time-out

host command ('Normal')

wake-up event OR

host command ('Standby')

AS_Sleep

host command ('Sleep')

dStarGoToSleep time-out

Host-control mode only

Autonomous-control mode only

Fig 6.

015aaa170

Mode transition diagram

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

15 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.9 Branch operating modes

Each of the four branches in the TJA1085 features six branch operating modes:

• Branch_Off

All branches are in Branch_Off mode when the TJA1085 is in AS_PowerOff or

AS_Reset mode. The transmitter, normal receiver, low-power receiver and bus error

detection are disabled. The bus pins are floating.

• Branch_LowPower

All branches are in Branch_LowPower mode when the TJA1085 is in AS_Standby or

AS_Sleep mode. The transmitter, the normal receiver and bus error detection are

disabled. The low-power receiver is active (i.e. remote wake-up is possible). The bus

pins are biased to ground.

• Branch_Disabled

The TJA1085 switches to Branch_Disabled if an overtemperature is detected. The

‘Branch_Disabled’ and ‘Branch_Normal’ commands allow the host to enable/disable a

branch without affecting the remaining branches. The transmitter, normal receiver and

bus error detection are disabled. Only the low-power receiver is active (remote

wake-up is possible). The bus pins are biased to Vo(idle)(BP) and Vo(idle)(BM).

• Branch_Normal

When a branch is in Branch_Normal, the TJA1085 will be in AS_Normal. The

transmitter, normal receiver and bus error detection are active. The bus pins are

biased to Vo(idle)(BP) and Vo(idle)(BM).

• Branch_TxOnly1

In Branch_TxOnly1 mode, the receiver is disabled, i.e. the received data is not

forwarded to the signal router. The transmitter is active and bus error detection is

active. The bus pins are biased to Vo(idle)(BP) and Vo(idle)(BM).

• Branch_TxOnly2

This mode is host-controlled only and is operationally identical to Branch_TxOnly1. It

allows the host to switch off the receiver in response to error conditions.

• Branch_FailSilent

The transmitter, the low-power receiver and bus error detection are disabled. Only the

receiver remains active to monitor the branch for idle or activity. Received data is not

forwarded to the signal router. The bus pins are biased to Vo(idle)(BP) and Vo(idle)(BM).

6.9.1 Branch operating mode transitions

Branch-related host commands can only be issued when the TJA1085 is in AS_Normal

mode.

6.9.1.1

Branch_Off

When the TJA1085 enters AS_PowerOff or AS_Reset, all four branches switch to

Branch-Off. When the TJA1085 subsequently switches to AS_Standby, all four branches

switch to Branch_LowPower.

6.9.1.2

Branch_LowPower

All four branches switch to Branch_LowPower when the TJA1085 enters AS_Standby or

AS_Sleep. All branches remain in this mode until the TJA1085 enters AS_Normal. When

this transition happens, branches that were in Branch_Disabled before switching to

Branch_LowPower return to Branch_Disabled. The remaining branches switch to

Branch_Normal.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

16 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.9.1.3

Branch_Disabled

An overtemperature event (TEMP_HIGH flag set) triggers a transition from

Branch_Normal to Branch_Disabled in all branches.

If an overtemperature event triggered the transition from Branch_Normal to

Branch_Disabled, all branches return to Branch_Normal when the overtemperature

problem has been resolved (TEMP_WARN flag reset).

The ‘Branch_Disabled’ and ‘Branch_Normal’ commands can be used to enable/disable

individual branches. A host command is also available to trigger a transition from

Branch_Disabled to Branch_TxOnly1 (‘Branch_TxOnly').

If a branch switches from Branch_Disabled to Branch_LowPower because the TJA1085

has entered AS_Standby or AS_Sleep, it will return to Branch_Disabled when the

TJA1085 enters AS_Normal.

6.9.1.4

Branch_FailSilent

A branch switches to Branch_FailSilent:

- from Branch_Normal if a branch is clamped (Clamp_BRx flag set), provided

clamp-detection is enabled (bit CLAMP_DET set; see Table 8)

- from Branch_Normal if a transmit error (TxE_BRx = 1) is detected, provided

autonomous error confinement is enabled (bit AEC set; see Table 8)

- from Branch_TxOnly1 if a transmit error (TxE_BRx = 1) is detected.

The branch remains in Branch_FailSilent until idle is detected on all branches, when it

switches to Branch_TxOnly1 (a ‘Branch_TxOnly’ command is needed in HC mode).

6.9.1.5

Branch_TxOnly1

A branch switches to Branch_TxOnly1:

- from Branch_Disabled in response to a ‘Branch_TxOnly’ command (HC mode)

- from Branch_FailSilent in response to a ‘Branch_TxOnly’ command when all branches

are idle (HC mode)

- from Branch_FailSilent when all branches are idle (AP mode)

A branch switches from Branch_TxOnly1:

- to Branch_Normal when a transmission ends without error

- to Branch_FailSilent if a transmit error is detected (TxE_BRx = 1)

6.9.1.6

Branch_TxOnly2

This mode is purely host controlled. A branch switches to Branch_TxOnly2 only in

response to a ‘Branch_TxOnly’ command issued in Branch_Normal mode. The branch

remains in Branch_TxOnly2 mode until a ‘Branch_Normal’ command is received.

6.9.1.7

Branch_Normal

A branch switches to Branch_Normal:

- from Branch_LowPower when the TJA1085 enters AS_Normal mode (provided it was

not in Branch_Disabled before the transition to Branch_LowPower mode)

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

17 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

- from Branch_TxOnly2 in response to a host ‘Branch_Normal’ command

- from Branch_TxOnly1 when a transmission ends without error

- from Branch_Disabled in response to a host ‘Branch_Normal’ command

- from Branch_Disabled when an overtemperature is resolved (TEMP_WARN = 0),

provided the overtemperature triggered the earlier transition to Branch_Disabled.

A branch switches from Branch_Normal:

- to Branch_FailSilent if a branch is clamped, provided clamp-detection is enabled

(CLAMP_DET = 1)

- to Branch_FailSilent if a transmit error is detected, provided bit AEC = 1

- to Branch_TxOnly2 if a host ‘Branch_TxOnly’ command is received

- to Branch_Disabled if an overtemperature event is detected (TEMP_HIGH = 1)

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

18 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.9.1.8

Branch operating mode transition diagram

active star switches to

AS_Standby or AS_Sleep

Branch_LowPower

Branch_Off

active star switches to

AS_Normal

active star switches to

AS_PowerOff or AS_Reset

Active Star Coupler in

AS_Normal mode

previous state was

Branch_Disabled

previous state not

Branch_Disabled

Branch_Disabled

overtemperature detected

Branch_TxOnly2

host command

('Branch_Normal')

overtemperature warning inactive

host command

('Branch_TxOnly')

host command

('Branch_Disabled')

host command

('Branch_Normal')

Branch_Normal

clamp detected OR

transmit error

with AEC = 1

host command

('Branch_TxOnly')

Branch_FailSilent

transmission ends

without error

transmit error

Branch_TxOnly1

all active branches idle AND

(APM flag set OR

host command

('Branch_TxOnly'))

015aaa171

Fig 7.

Branch mode transition diagram

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

19 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10 SPI interface

The TJA1085 contains a bidirectional 16-bit Serial Peripheral Interface (SPI) for

communicating with a host. The SPI allows the host to configure the TJA1085 and to

access error and status information.

6.10.1 Register access

The SPI supports full duplex data transfer, so status information is read out on pin SDO

while control data is being shifted in on pin SDI. Bit sampling is performed on the falling

edge of the clock signal on pin SCLK and data is shifted on the rising edge (MSB first; see

Figure 8).

The clock signal must be LOW when SCSN goes LOW to initiate an SPI register access

cycle.

SCSN

SCLK

01

02

03

04

15

16

sampled

SDI

SDO

X

floating

X

MSB

14

13

12

01

LSB

MSB

14

13

12

01

LSB

X

floating

015aaa154

Fig 8.

SPI register access

6.10.2 SPI registers

The SPI register structure in the TJA1085 is illustrated in Figure 9. The three MSBs

(bits15 to 13) contain the 3-bit register address. Bit 12 defines the selected register

access as read/write or read only. If bit 12 is 1, the SPI data transfer will be read only and

all data on the SDI pin will be ignored. If bit 12 is 0, data bits 11 to 0 will be written to the

selected register.

Bits 15 to 13: register address

Bit 12: 1 = R/O (read only), 0 = R/W (read/write)

15

0

Register Select

Fig 9.

TJA1085

Product data sheet

Data Bits

015aaa155

SPI register structure

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

20 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

The assignment of control and status register addresses is detailed in Table 6. Data can

only be written to the Control and Configuration registers (status registers are read-only

by definition). Therefore the state of bit 12 is only evaluated when these registers are

being accessed.

Table 6.

Register map

Address bits 15, 14 and 13

Write access bit 12[1]

Register

000

0 =R/W, 1 = R/O

Control register; see Table 7

001

1 = R/O

Interrupt status register; see Table 9

010

1 = R/O

General status register; see Table 10

011

1 = R/O

Branch 1 status register; see Table 11

100

1 = R/O

Branch 2 status register; see Table 11

101

1 = R/O

Branch 3 status register; see Table 11

110

1 = R/O

Branch 4 status register; see Table 11

111

0 =R/W, 1 = R/O

Configuration register; see Table 8

[1]

Bit 12 is assumed to be 1 for status registers

The following subsections provide details of the bits in these registers and the control and

status functionality assigned to each.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

21 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10.2.1

Control register

The read/write Control register allows the host controller to set the operating modes and

to switch the TJA1085 between HC and AP modes.

Table 7.

Bit

Control register bit description

Symbol

11:10 OPM

Access

Default

Description

R/W

00

operating mode:

00: no change

01: AS_Standby

10: AS_Sleep

11: AS_Normal

9:8

CTRL_BR1

R/W

00

branch 1 control:

00: no change

01: Branch_Normal

10: Branch_TxOnly

11: Branch_Disabled

7:6

CTRL_BR2

R/W

00

branch 2 control:

00: no change

01: Branch_Normal

10: Branch_TxOnly

11: Branch_Disabled

5:4

CTRL_BR3

R/W

00

branch 3 control:

00: no change

01: Branch_Normal

10: Branch_TxOnly

11: Branch_Disabled

3:2

CTRL_BR4

R/W

00

branch 4 control:

00: no change

01: Branch_Normal

10: Branch_TxOnly

11: Branch_Disabled

1

APM[1]

R/W

1

Autonomous Power mode

0: disabled

1: enabled

0

RESET_ERROR[2]

R/W

0

reset error flags and status bits

0: no change

1: reset flags/bits

TJA1085

Product data sheet

[1]

The TJA1085 sets the APM flag at power-on, in response to a wake-up event (local, remote or TRXD), if a

VCC undervoltage is detected in AS_Normal or a VIO undervoltage is detected for longer than tto(uvd)(VIO).

[2]

Setting the RESET_ERROR bit resets all error status bits in the General Status (bits 8 to 1) and Branch

Status registers (bits 7 to 4).

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

22 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10.2.2

Configuration register

The read/write Configuration register allows the host controller to configure a number of

TJA1085 parameters and functions.

Table 8.

Configuration register bit description

Bit

Symbol

Access

Default

Description

11

AEC

R/W

0

Autonomous error confinement:

0: disabled

1: enabled

10

BFT

R/W

1

Bus failure timer

0: disabled

1: enabled

9

WUD_BR1

R/W

1

wake-up detection on branch 1:

0: disabled

1: enabled

8

WUD_BR2

R/W

1

wake-up detection on branch 2:

0: disabled

1: enabled

7

WUD_BR3

R/W

1

wake-up detection on branch 3:

0: disabled

1: enabled

6

WUD_BR4

R/W

1

wake-up detection on branch 4:

0: disabled

1: enabled

5

CC_EN

R/W

0

CC interface enable (TXD and TXEN inputs;

RXD output):

0: disabled

1: enabled

4

TRXD_EN

R/W

1

TRXD interface enable:

0: disabled

1: enabled

3

reserved

always 0

2

CLAMP_DET

R/W

1

clamping detection:

0: disabled

1: enabled

1

BIT_LATCHING

R/W

0

status bit latching:

0: disabled

1: enabled

0

TJA1085

Product data sheet

PARITY

R

-

parity bit - odd parity (including parity bit)

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

23 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Autonomous Error Confinement (AEC):

Setting the AEC bit enables the autonomous error confinement feature of the TJA1085.

When AEC is enabled, a bus error (TxE_BRx = 1) triggers a transition from

Branch_Normal to Branch_FailSilent. AEC is disabled by default.

Bus Failure Timer (BFT):

Setting the BFT bit enables the bus failure timer.

When the BFT is enabled, pulses shorter than tto(BFT) are ignored, resulting in more robust

bus error detection. The BFT is enabled by default.

Wake-up detection on branch x (WUD_BRx):

Setting the WUD_BRx bit enables wake-up detection on the specified branch.

Each branch in a TJA1085 star network contains a low-power receiver for detecting

remote wake-up events. These events can be enabled and disabled individually. This

feature makes it possible to minimize quiescent current consumption, especially in

AS_Sleep mode. Wake-up detection is enabled by default on all branches.

Communication Controller interface Enable (CC_EN):

Setting bit CC_EN enables the communication controller interface.

A communication controller can be connected to the TJA1085 when CC_EN = 1. If

CC_EN = 0, the RXD output driver is switched off to minimize current consumption in

AS_Normal mode. The CC interface is disabled by default.

TRXD0/1 interface Enable (TRXD_EN):

Setting bit TRXD_EN enables the TRXD0 and TRXD1 interfaces.

When the TRXD0/1 interfaces are enabled, several TJA1085 devices can be connected

together to form a single active star. If only one TJA1085 is needed at any time, the

TRXD0/1 interfaces can be disabled to minimize current consumption in AS_Normal

mode. The TRXD0 and TRXD1 interfaces are enabled by default.

Clamp detection (CLAMP_DET):

Setting bit CLAMP_DET enables clamp detection on TXEN, TRXD and on the four

branches.

When clamp detection is enabled, a CLAMP_ERROR interrupt is generated if clamping is

detected on TXEN (CLAMP_TXEN = 1), TRXD (CLAMP_TRXD = 1) or on a branch

(CLAMP_BRx). Clamp detection is enabled by default.

Bit latching (BIT_LATCHING):

When bit latching is enabled (BIT_LATCHING = 1), the status bits in the General and

Branch X status registers reflect the latched state until the register is read. Once the

register has been read, latching is released and the bits then reflect the current ‘live’

status. When bit latching is disabled, the status bits reflect the ‘live’ status at all times. Bit

latching is disabled by default.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

24 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10.2.3

Interrupt Status register

The Interrupt Status register is read-only. When the TJA1085 sets a bit in this register, it

triggers a falling edge on pin INTN. Bits PWON, WU, SPI_ERROR and HC_ERROR are

reset after a successful read operation. The remaining bits are reset after the flag (or

flags) that triggered the interrupt has been reset and a successful read operation has

been performed (see Section 6.7).

Table 9.

Interrupt status register

Bit

Symbol

Description

11

PWON

power-on detection:

0: no power-on detected

1: power-on detected

10

WU

wake-up event detection (any):

0: no wake-up event detected

1: wake-up event detected

9

EVENT_BR1

wake-up or bus error detection on branch 1:

0: no wake-up or bus error detected

1: wake-up or bus error detected

8

EVENT_BR2

wake-up or bus error detection on branch 2:

0: no wake-up or bus error detected

1: wake-up or bus error detected

7

EVENT_BR3

wake-up or bus error detection on branch 3:

0: no wake-up or bus error detected

1: wake-up or bus error detected

6

EVENT_BR4

wake-up or bus error detection on branch 4:

0: no wake-up or bus error detected

1: wake-up or bus error detected

5

undervoltage detected on VBAT, VCC or VIO:

UV_ERROR

0: no undervoltage detected

1: undervoltage detected

4

CLAMP_ERROR

clamp error on TRXD, TXEN or branch or collision on TRXD:

0: no clamping error detected

1: clamping error detected

3

SPI_ERROR

SPI communication error:

0: not detected

1: detected

2

HC_ERROR

host command error:

0: not detected

1: detected

1

TEMP_ERROR

overtemperature error:

0: not detected

1:detected

0

TJA1085

Product data sheet

PARITY

parity bit - odd parity (including parity bit)

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

25 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

PWON: A PWON interrupt is generated to signal a power-on event.

The PWON interrupt status bit is set when the TJA1085 leaves AS_PowerOff or

AS_Reset. It is reset after a successful read operation on the Interrupt Status register.

WU: A WU interrupt indicates the occurrence of a wake-up event.

The WU interrupt status bit is set when a wake-up event is detected on a branch

(WU_BRx = 1), on TRXD0/1 (WU_TRXD = 1), or on LWU (WU_LOCAL = 1). It is reset

after a successful read operation on the Interrupt Status register.

EVENT_BRx: An EVENT_BRx interrupt signals the occurrence of a significant event on

the relevant branch.

The EVENT_BRx interrupt status bit is set when any of the following events is detected on

a branch:

- a wake-up event (WU_BRx = 1)

- a bus error (TxE_BRx = 1)

- clamping (CLAMP_BRx = 1)

It is reset after the flag (or flags) that triggered the interrupt has been reset and the

Interrupt Status register has been read successfully. Resetting EVENT_BRx will trigger a

falling edge on INTN to indicate to the host that the event that triggered the interrupt has

been resolved (except when the interrupt was triggered by a branch wake-up event).

UV_ERROR: A UV_ERROR interrupt indicates that an undervoltage has occurred.

The UV_ERROR interrupt status bit is set when a VBAT (UV_VBAT = 1), VCC

(UV_VCC = 1) or VIO (UV_VIO = 1) undervoltage is detected. It is reset after the flag (or

flags) that triggered the interrupt has been reset and the Interrupt Status register has been

read successfully. Resetting UV_ERROR triggers a falling edge on INTN to indicate to the

host that the undervoltage condition is no longer present.

CLAMP_ERROR: A CLAMP_ERROR interrupt indicates that an input channel has

become clamped or a collision has occurred on the TRXDO/1 interface.

The CLAMP_ERROR interrupt status bit is set when clamping is detected on TRXD

(CLAMP_TRXD = 1), on TXEN (CLAMP_TXEN = 1) or on a branch (CLAMP_BRx = 1) or

if a collision is detected on TRXD0/TRXD1 (COLL_TRXD = 1). It is reset after the flag (or

flags) that triggered the interrupt has been reset and the Interrupt Status register has been

read successfully. Resetting CLAMP_ERROR triggers a falling edge on INTN to indicate

to the host that the clamp or collision error has been corrected.

SPI_ERROR: An SPI_ERROR interrupt indicates that an error has occurred during SPI

communications.

The SPI_ERROR interrupt status bit is set if the number of SCLK cycles generated during

a LOW phase on SCSN does not equal 16. It is reset after a successful read operation on

the Interrupt Status register.

HC_ERROR: A HC_ERROR interrupt indicates that an invalid host command has been

received.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

26 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

The HC_ERROR interrupt status bit is set when the host requests an illegal mode

transition (as defined in the Section 6.8.1 and Section 6.9.1). It is reset after a successful

read operation on the Interrupt Status register.

TEMP_ERROR: A TEMP_ERROR interrupt signals the presence of an overtemperature

condition.

The TEMP_ERROR interrupt status bit is set when the temperature warning level

(TEMP_WARN = 1) or temperature high level (TEMP_HIGH = 1) is exceeded. It is reset

after the flag (or flags) that triggered the interrupt has been reset and the Interrupt Status

register has been read successfully. Resetting TEMP_ERROR triggers a falling edge on

INTN to indicate to the host that the overtemperature condition is no longer present.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

27 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10.2.4

General Status register

The read-only General Status register contains status information not included in the

Interrupt status register.

Table 10.

General status register

Bit

Symbol

Description

11

WU_LOCAL

local wake-up on pin LWU:

0: no wake-up detected

1: wake-up detected

10

WU_TRXD

wake-up via TRXD0/TRXD1

0: no wake-up detected

1: wake-up detected

9

BGE_FB

BGE status feedback:

0: if BGE is LOW

1: if BGE is HIGH

8

UV_VBAT

VBAT undervoltage

0: no undervoltage detected

1: undervoltage detected

7

UV_VCC

VCC undervoltage

0: no undervoltage detected

1: undervoltage detected

6

UV_VIO

VIO undervoltage

0: no undervoltage detected

1: undervoltage detected

5

TEMP_WARN

temperature warning level

0: not exceeded

1: exceeded

4

TEMP_HIGH

temperature high level

0: not exceeded

1: exceeded

3

CLAMP_TRXD

clamping detection on TRXD:

0: not detected

1: detected

2

CLAMP_TXEN

clamping detection on TXEN:

0: not detected

1: detected

1

COLL_TRXD

collision detection on TRXDO and TRXD1:

0: not detected

1:detected

0

TJA1085

Product data sheet

PARITY

parity bit - odd parity (including parity bit)

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

28 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

WU_LOCAL:

WU_LOCAL is set when a local wake-up event is detected. A WU interrupt is generated.

WU_LOCAL is reset after the General Status register has been read successfully or when

the TJA1085 switches from AS_Normal to AS_Standby or AS_Sleep. This ensures that a

new wake-up event will be detected.

WU_TRXD:

WU_TRXD is set when a wake-up event is detected on the TRXD0/1 interface. A WU

interrupt is generated.

WU_TRXD is reset after the General Status register has been read successfully or when

the TJA1085 switches from AS_Normal to AS_Standby or AS_Sleep. This ensures that a

new wake-up event will be detected.

BGE_FB:

Bit BGE_FB provides information about the voltage level on pin BGE.

BGE_FB is set when the voltage on BGE is HIGH and reset when the voltage on BGE is

LOW.

UV_VBAT:

UV_VBAT is set when a VBAT undervoltage is detected, generating a UV_ERROR

interrupt.

If bit latching is enabled (BIT_LATCHING = 1), UV_BAT will remain set until the General

Status register has been read, after which it will reflect the current ‘live’ situation (set if

VBAT < Vuvd(VBAT) for longer than tdet(uv)(VBAT) and reset if VBAT > Vuvr(VBAT) for longer than

trec(uv)(VBAT)). If bit latching is not enabled, UV_BAT will reflect the ‘live’ situation at all

times.

UV_VCC:

UV_VCC is set when a VCC undervoltage is detected, generating a UV_ERROR interrupt.

If bit latching is enabled (BIT_LATCHING = 1), UV_VCC will remain set until the General

Status register has been read, after which it will reflect the current ‘live’ situation (set if

VCC < Vuvd(VCC) for longer than tto(uvd)(VCC) and reset if VCC > Vuvr(VCC) for longer than

tto(uvr)(VCC)). If bit latching is not enabled, UV_VCC will reflect the ‘live’ situation at all

times.

UV_VIO:

UV_VIO is set when a VIO undervoltage is detected, generating a UV_ERROR interrupt.

If bit latching is enabled (BIT_LATCHING = 1), UV_VIO will remain set until the General

Status register has been read, after which it will reflect the current ‘live’ situation (set if

VIO < Vuvd(VIO) for longer than tto(uvd)(VIO) and reset if VIO > Vuvr(VIO) for longer than

tto(uvr)(VIO)). If bit latching is not enabled, UV_VIO will reflect the ‘live’ situation at all times.

When a VIO undervoltage is active, the digital inputs are disabled and the TJA1085 is

unable to accept Host commands. If the VIO undervoltage persists for longer than

tto(uvd)(VIO), the APM flag is set and the TJA1085 switches from Host control to

Autonomous control.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

29 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

TEMP_WARN:

TEMP_WARN is set when the junction temperature rises above the temperature warning

level, generating a TEMP_ERROR interrupt.

If bit latching is enabled (BIT_LATCHING = 1), TEMP_WARN will remain set until the

General Status register has been read, after which it will reflect the current ‘live’ situation

(set when Tj > Tj(warn) and reset when Tj < Tj(warn) with no activity on the bus or on the CC

and TRXD0/1 interfaces). If bit latching is not enabled, TEMP_WARN will reflect the ‘live’

situation at all times.

TEMP_HIGH:

TEMP_HIGH is set when the junction temperature rises above the temperature high level.

The output driver on the TRXD0/1 interface is disabled along with the branch transmitters

(all branches switch to Branch_Disabled). A TEMP_ERROR interrupt is generated.

If bit latching is enabled (BIT_LATCHING = 1), TEMP_HIGH will remain set until the

General Status register has been read, after which it will reflect the current ‘live’ situation

(set when Tj > Tj(high) and reset when Tj < Tj(high) with no activity on the bus or on the CC

and TRXD0/1 interfaces). If bit latching is not enabled, TEMP_HIGH will reflect the ‘live’

situation at all times.

CLAMP_TRXD:

CLAMP_TRXD is set when the TRXD0/1 interface is configured as an input and TRXD0

or TRXD1 is clamped LOW for longer than tdetCL(TRXD). The output driver on the TRXD0/1

interface is disabled and data on the inputs is ignored. A CLAMP_ERROR interrupt is

generated.

If bit latching is enabled, CLAMP_TRXD will remain set until the General Status register

has been read, after which it will reflect the current ‘live’ situation (set when TRXD0 or

TRXD1 clamped LOW and reset when TRXD0 and TRXD1 are HIGH). If bit latching is not

enabled, CLAMP_TRXD will reflect the ‘live’ situation at all times.

CLAMP_TXEN:

CLAMP_TXEN is set when the TXEN is clamped LOW for longer than tdetCL(TXEN). Data

on TXD/TXEN is ignored and a CLAMP_ERROR interrupt is generated.

If bit latching is enabled, CLAMP_TXEN will remain set until the General Status register

has been read, after which it will reflect the current ‘live’ situation (set when TXEN

clamped LOW and reset when TXEN is HIGH). If bit latching is not enabled,

CLAMP_TXEN will reflect the ‘live’ situation at all times.

COLL_TRXD:

COLL_TRXD is set when a collision is detected on the TRXD0/1 interface (TRXD0 and

TRXD1 LOW for longer than tdet(col)(TRXD)). A CLAMP_ERROR interrupt is generated.

COLL_TRXD is reset once the General Status register has been read.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

30 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

6.10.2.5

Branch X status registers

There is a dedicated read-only status register for each branch, i.e. there are four Branch X

status registers in total. Each register contains relevant status information of a branch.

Table 11.

Branch X status register

Bit

Symbol

Description

11-9

STATE_BRx

state of active branch:

000: Branch_Normal mode

001: Branch_Disabled mode

010: Branch_LowPower mode

011: Branch_TxOnly_2 mode

100: Branch_FailSilent mode

101: Branch_TxOnly_1 mode

8

WU_BRx

wake-up status

0: no wake-up detected

1: wake-up detected

7

reserved

always 0

6

TxE_BRx

transmit error on branch

0: not detected

1: detected

5

reserved

always 0

4

CLAMP_BRx

clamp detection on branch

0: not detected

1: detected

TJA1085

Product data sheet

3

reserved

always 0

2

reserved

always 1

1

reserved

always 0

0

PARITY

parity bit - odd parity (including parity bit)

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

31 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

STATE_BRx:

Bits STATE_BRx indicate the current branch operating mode.

WU_BRx:

WU_BRx is set when a remote wake-up event is detected on a branch. A WU interrupt is

generated along with an EVENT_BRx interrupt to indicate the branch where the wake-up

pattern or dedicated data frame was detected.

WU_BRx is reset after the Branch Status register has been read successfully or when the

TJA1085 switches from AS_Normal to AS_Standby or AS_Sleep. This ensures that a new

wake-up event will be detected.

TxE_BRx:

TxE_BRx is set when a transmit error is detected on a branch, generating an

EVENT_BRx interrupt. A transmit error is detected when there is a mismatch between the

transmitted and received signals.

If bit latching is enabled (BIT_LATCHING = 1), TxE_BRx will remain set until the register

has been read, after which it is reset if no mismatch is found between transmitted and

received signals or the branch leaves Branch_Normal. If bit latching is not enabled,

TxE_BRx is reset if no mismatch is found in a data frame or the branch leaves

Branch_Normal.

CLAMP_BRx:

CLAMP_BRx is set when a branch is clamped for longer than tdetCL(bus), generating a

CLAMP_ERROR interrupt along with an EVENT_BRx interrupt to indicate the branch.

If bit latching is enabled (BIT_LATCHING = 1), CLAMP_BRx will remain set until the

register has been read, after which it is reset when idle is detected on the branch. If bit

latching is not enabled, CLAMP_BRx is reset when idle is detected on the branch.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

32 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

7. Limiting values

Table 12. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are referenced to GND.

Symbol

Parameter

Conditions

[1]

Min

Max

Unit

0.3

+48

V

VBAT

battery supply voltage

during load dump (400 ms max.)

0.3

+60

V

IINH

current on pin INH

AS_Normal, AS_Standby or AS_Reset

1

0

mA

Vx

voltage on pin x[1]

on pins VCC, VBUF, VIO, TRXD0, TRXD1, BGE,

TXD, TXEN, RSTN, INTN, SCSN, SCLK, SDI,

SDO

0.3

+5.5

V

on pins INH, LWU

0.3

VBAT + 0.3

V

on pin RXD

0.3

min(VIO +

0.3, 5.5)

V

on any BM/BP pin with respect to other BP/BM

pins and GND

60

+60

V

IO(LWU)

transient voltage

Vtrt

Tamb

15

-

mA

[2]

100

-

V

[3]

-

75

V

[4]

150

-

V

[5]

-

100

V

40

+125

C

output current on pin LWU

on pins LWU, VBAT, BP and BM

ambient temperature

Tvj

virtual junction temperature

Tstg

storage temperature

VESD

electrostatic discharge

voltage

[6]

IEC 61000-4-2 (150 pF, 330 )

40

+150

C

55

+150

C

[7]

6.0

+6.0

kV

on pin LWU to GND

[8]

6.0

+6.0

kV

on pin VBAT to GND

[9]

6.0

+6.0

kV

8.0

+8.0

kV

6.0

+6.0

kV

4.0

+4.0

kV

200

+200

V

1000

+1000

V

on pins BP and BM to GND

Human Body Model (HBM); 100 pF, 1.5 k

[10]

on pins BP and BM to GND

on pins LWU and VBAT to GND

[11]

on any other pin

Machine Model (MM); 200 pF, 0.75 H, 10

[12]

on any pin

Charged Device Model (CDM); field Induced

charge; 4 pF

on any pin

[13]

[1]

The device can sustain voltages up to the specified values over the product lifetime, provided applied voltages (including transients)

never exceed these values.

[2]

According to ISO7637, test pulse 1, class C; verified by an external test house.

[3]

According to ISO7637, test pulse 2a, class C; verified by an external test house.

[4]

According to ISO7637, test pulse 3a, class C; verified by an external test house.

[5]

According to ISO7637, test pulse 3b, class C; verified by an external test house.

[6]

In accordance with IEC 60747-1. An alternative definition of Tvj is: Tvj = Tamb + P Rth(j-a), where Rth(j-a) is a fixed value used in the

calculation of Tvj. The rating for Tvj limits the allowable combinations of power dissipation (P) and ambient temperature (Tamb).

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

33 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

[7]

According to IEC TS 62228 (2007), Section 4.3; DIN EN 61000-4-2; verified by an external test house. The test result is equal to or

better than 6 kV (unaided).

[8]

With 3.3 k in series.

[9]

With 100 nF from VBAT to GND.

[10] According to AEC-Q100-002.

[11] Guaranteed only when all n.c. pins are connected to GND.

[12] According to AEC-Q100-003.

[13] According to AEC-Q100-011 Rev-C1. The classification level is C6.

8. Thermal characteristics

Table 13.

Symbol

Thermal characteristics

Parameter

Rth(j-a)

thermal resistance from junction to ambient

Rth(j-c)

thermal resistance from junction to case

[1]

[1]

Conditions

Typ

Unit

in free air

24

K/W

in free air

2.5

K/W

TJA1085 mounted on a JEDEC 2s2p board with 36 vias between layer 1 and layer 2; via diameter: 0.5 mm, wall thickness: 18 m.

TJA1085

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

34 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

9. Static characteristics

Table 14. Static characteristics

All parameters are guaranteed for VBAT = 4.45 V to 60 V; VCC = 4.45 V to 5.25 V; VBUF = 4.45 V to 5.25 V;VIO = 2.55 V to

5.25 V; Tvj = 40 C to +150 C; Cbus = 100 pF; Rbus = 40 to 55 ; CRXD = 15 pF and CTRXD0 = CTRXD1 = 50 pF unless

otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Power-on reset for VDIG

Vth(det)POR

power-on reset detection

threshold voltage

of internal digital circuitry

3

-

3.4

V

Vth(rec)POR

power-on reset recovery

threshold voltage

of internal digital circuitry

3.1

-

3.5

V

Vhys(POR)

power-on reset hysteresis

voltage

of internal digital circuitry

100

500

mV

V(VCC-VDIG)

voltage difference between

VCC and VDIG

VCC = 4.45 V; VBAT = VBUF = 0 V

-

-

1.0

V

V(VBAT-VDIG)

voltage difference between

VBAT and VDIG

VBAT = 4.45 V; VCC = VBUF = 0 V

-

-

1.0

V

V(VBUF-VDIG)

voltage difference between

VBUF and VDIG

VBUF = 4.45 V; VCC = VBAT = 0 V

-

-

1.0

V

Supply: pin VBAT

VBAT

battery supply voltage

operating range

4.75

-

60

V

IBAT

battery supply current

AS_Normal; no load on INH

-

0.1

1

mA

AS_Standby; no load on INH;

wake-up enabled on all branches

-

50

100

A

AS_Sleep; wake-up enabled on all

branches

-

50

100

A

AS_Sleep; wake-up enabled on all

branches; Tvj 85 C

-

50

90

A

AS_Sleep; wake-up disabled on all

branches

-

25

55

A

AS_Sleep; wake-up disabled on all

branches; Tvj 85 C

-

25

45

A

Vuvd

undervoltage detection

voltage

4.45

-

4.715

V

Vuvr

undervoltage recovery

voltage

4.475

-

4.74

V

Vuvhys

undervoltage hysteresis

voltage

25

-

290

mV

4.75

-

5.25

V

Supply: pins VCC1 and VCC2 (connected on the PCB)

VCC

TJA1085

Product data sheet

supply voltage

operating range

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 7 March 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

35 of 61

�TJA1085

NXP Semiconductors

FlexRay active star coupler

Table 14. Static characteristics …continued

All parameters are guaranteed for VBAT = 4.45 V to 60 V; VCC = 4.45 V to 5.25 V; VBUF = 4.45 V to 5.25 V;VIO = 2.55 V to

5.25 V; Tvj = 40 C to +150 C; Cbus = 100 pF; Rbus = 40 to 55 ; CRXD = 15 pF and CTRXD0 = CTRXD1 = 50 pF unless

otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

Symbol

ICC

Parameter

Conditions

supply current

Min

Typ

Max

Unit

AS_Normal; VTXEN = 0 V;

VBGE = VIO; Rbus = 45 ;

all branches in Branch_Normal

[1]

-

180

210

mA

AS_Normal; VTXEN = VIO;

VBGE = 0 V; Rbus = 45 ;

all branches in Branch_Normal

and/or Branch_Disabled

[1]

-

-

80

mA

AS_Standby

[1][2]

-

4

35

A

AS_Standby; Tvj 85 C

[1][2]

-

4

15

A

AS_Sleep, AS_Reset

[1][2]

-

0

30

A

AS_Sleep, AS_Reset; Tvj 85 C

[1][2]

-

0

10

A

Vuvd

undervoltage detection

voltage

4.45

-

4.715

V

Vuvr

undervoltage recovery

voltage

4.475

-

4.74

V

Vuvhys

undervoltage hysteresis

voltage

25

-

290

mV

5.5 V VBAT 60 V;

VCC Vuvd(VCC)

4.5

-

5.25

V

4.5 V VBAT 5.5 V;

VCC Vuvd(VCC)

3.5

-

5.25

V

Supply: pins VBUF1 and VBUF2 (connected on the PCB)

VBUF

supply voltage on pin VBUF

V(VCC-VBUF)

voltage difference between

VCC and VBUF