Is Now Part of

To learn more about ON Semiconductor, please visit our website at

www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers

will need to change in order to meet ON Semiconductor’s system requirements. Since the ON Semiconductor

product management systems do not have the ability to manage part nomenclature that utilizes an underscore

(_), the underscore (_) in the Fairchild part numbers will be changed to a dash (-). This document may contain

device numbers with an underscore (_). Please check the ON Semiconductor website to verify the updated

device numbers. The most current and up-to-date ordering information can be found at www.onsemi.com. Please

email any questions regarding the system integration to Fairchild_questions@onsemi.com.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number

of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right

to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON

Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON

Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s

technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA

Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended

or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out

of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor

is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

�FL7921R

Integrated Critical-Mode PFC and Quasi-Resonant

Current-Mode PWM Lighting Controller

Features

Description

Integrated PFC and Flyback Controller

The highly integrated FL7921R combines a Power

Factor Correction (PFC) controller and a QuasiResonant PWM controller. Integration provides costeffect design and allows for fewer external components.

Auto Recovery VDD Pin and Output Voltage OVP

Critical-Mode PFC Controller

Zero-Current Detection for PFC Stage

Quasi-Resonant Operation for PWM Stage

Internal Minimum tOFF 8 µs for QR PWM Stage

Internal 10 ms Soft-Start for PWM

Brownout Protection

High / Low Line Over-Power Compensation

Auto Recovery Over-Current Protection

Auto Recovery Open-Loop Protection

Auto Recovery Over-Temperature Protection

Adjustable Over-Temperature with external NTC

through the RT pin

Applications

Medium to High Power LED Lighting Driver

Application

For PFC, FL7921R uses a controlled on-time technique

to provide a regulated DC output voltage and to perform

natural power factor correction. An innovative THD

optimizer reduces input current distortion at zerocrossing duration to improve THD performance. The

PFC function is always on regardless of the PWM stage

load condition to ensure that high PF can be achieved at

light load condition.

For PWM, FL7921R provides several functions to

enhance power system performance: valley detection,

green-mode operation, high / low line over-power

compensation. Protection functions include secondaryside open-loop and over-current with auto-recovery

protection, external recovery triggering, adjustable overtemperature protection through the RT pin and external

NTC resistor, internal over-temperature shutdown, VDD

pin OVP, DET pin over-voltage for output OVP, and

brown-in / out for AC input voltage UVP. All protections

are auto recovery mode except PWM current sense pin

open protection.

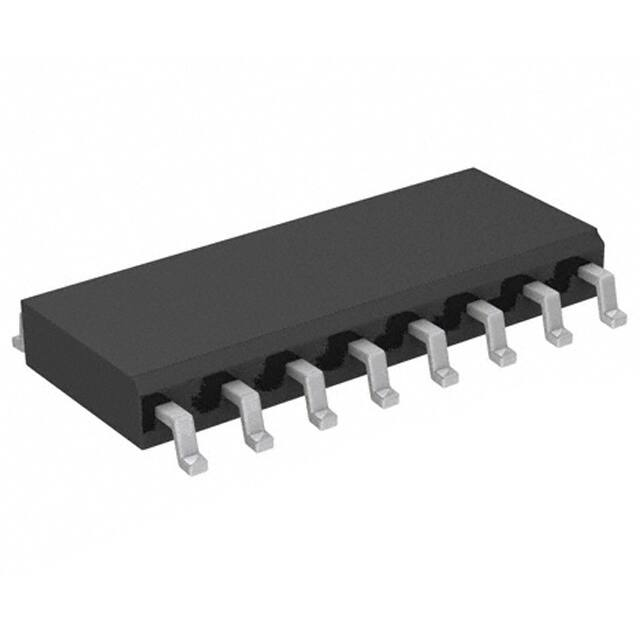

The FL7921R controller is available in a 16-pin, smalloutline package (SOP).

Ordering Information

Part Number

Protection

Mode

Operating

Temperature Range

Package

Packing

Method

FL7921RMX

Recovery

-40 °C to +125°C

16-Pin, Small-Outline Package (SOP)

Tape & Reel

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

www.fairchildsemi.com

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

October 2015

�BCM Boost PFC

Quasi-resonant Flyback

NBOOST

CCLAMP

RCLAMP NP

NS

VO

+

QPFC

CINF2

RINV1

NCZD

CPFC_Vo

RG1

-

RHV

RCS1

RCZD

RRANGE

CINF1

CCOMP

RVIN1

RINV2

QPWM

1 RANGE

HV 16

2

NC 15

COMP

3 INV

ZCD 14

4 CSPFC

VIN 13

5 CSPWM

RT 12

6 OPFC

FB 11

7 VDD

DET 10

8 OPWM

GND 9

FL7921R

RG2

RRT

RCS2

CRT

NTC

CFB

VAC

RVIN2

CVIN

NA

RDET1

CDD1

CDD2

RDET2

Figure 1. Typical Application

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Application Diagram

www.fairchildsemi.com

2

�COMP

HV

VDD

2

16

7

RANGE

Multi-Vector Amp.

2.65V

2.75V

RANGE

OVP

2.75V

2.9V

24V

Recovery

S

2.5V

CSPFC

R

Disable

Function

PFC

Current Limit

CLR

Q

2.1V/1.75V

Inhibit

Timer

14

FB OLP

Timer

50ms

11

2.25ms

28µs

2R

Soft-Start

10ms

IZCD

ZCD

10V

Recovery

VB

2.1V

Starter

DRV

R

Latched

3V

OPFC

0.2V

4.2V

FB

6

PFC Zero Current

Detector

Blanking

Circuit

4

Q

Restarter

Sawtooth

Generator

/tON-max

THD

Optimizer

SET

15.5V

Latched or

Recovery

Brownout

3

0.82V

NC

DRV

Debounce

70µs

0.45V

15

Two Steps

UVLO

18V/10V/7.5V

UVP

2.35V

INV

Internal

Bias

OVP

IHV

S

SET

Q

8

OPWM

1

RANGE

CS OVP

17.5V

CSPWM

Blanking

Circuit

5

R

PWM

Current Limit

Over0Power

Compensation

IDET

Latched or

Recovery

tOFF-MIN

(8µs/37µs/2.25ms)

IDET

Valley

Detector

1st

Valley

tOFF

Blanking

(4µs)

S/H

DET pin OVP

VDD pin OVP

RT Pin Prog OTP

RT Pin Externally Triggering

tOFF-MIN

+9µs

Startup

VB & clamp

Vcomp to

1.6V

Debounce

Time

IRT

Debounce

100ms

1.2V

0.8V

100µA

VINV

1V/1.3V

Brownout

comparator

1V

Internal

OTP

0.5V

Recovery

Debounce

100ms

110µs

10ms

Prog. OTP

/ Externally Triggering

2.1V/2.45V

9

12

13

GND

RT

VIN

Figure 2. Functional Block Diagram

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

Recovery

Output Short Circuit (FB pin)

Output Open-loop (FB pin)

Output Over Power/ Overload (FB pin)

Recovery

2.5V

10

Q

Recovery

VDET

DET OVP

DET

CLR

PFC RANGE Ccontrol

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Internal Block Diagram

www.fairchildsemi.com

3

�16

- Fairchild Logo

Z - Plant Code

X - 1-Digit Year Code

Y - 1-Digit Week Code

TT–Die-Run Code

T - Package Type (M=SOP)

M - Manufacture Flow Code

ZXYTT

FL7921R

TM

1

Figure 3. Marking Diagram

Pin Configuration

RANGE

1

16

HV

COMP

2

15

NC

3

14

ZCD

CSPFC

4

13

VIN

CSPWM

5

12

RT

OPFC

6

11

FB

VDD

7

10

DET

OPWM

8

9

GND

INV

Figure 4. Pin Configuration

Pin Definitions

Pin #

1

Name

Description

RANGE pin’s impedance changes according to the VIN pin voltage level. When the input voltage

RANGE detected by the VIN pin is lower than a threshold voltage, it sets to high impedance; whereas it

sets to low impedance if input voltage is at a high level.

2

COMP

3

INV

Output pin of the error amplifier. It’s a Trans-conductance-type error amplifier for PFC output

voltage feedback. Proprietary multi-vector current is built-in to this amplifier. Therefore, the

compensation for PFC voltage feedback loop allows a simple compensation circuit between this

pin and GND.

Inverting input of the error amplifier. This pin is used to receive PFC voltage level by a voltage

divider and provides PFC output over- and under-voltage protections.

4

Input to the PFC over-current protection comparator that provides cycle-by-cycle current limiting

CSPFC protection. When the sensed voltage across the PFC current-sensing resistor reaches the internal

threshold (0.82 V typical), the PFC switch is turned off to activate cycle-by-cycle current limiting.

5

Input to the comparator of the PWM over-current protection and performs PWM current-mode

control with FB pin voltage. A resistor is used to sense the switching current of the PWM switch

CSPWM and the sensing voltage is applied to the CSPWM pin for the cycle-by-cycle current limit, currentmode control, and high / low line over-power compensation according to the DET pin source

current during PWM tON time.

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Marking Information

Continued on the following page…

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

www.fairchildsemi.com

4

�Pin #

Name

6

OPFC

7

VDD

8

OPWM

9

GND

The power ground and signal ground.

DET

This pin is connected to an auxiliary winding of the PWM transformer through a resistor divider for

the following purposes:

Producing an offset voltage to compensate the threshold voltage of PWM current limit for

providing over-power compensation. The offset is generated in accordance with the input

voltage when the PWM switch is on.

Detecting the valley voltage signal of drain voltage of the PWM switch to achieve the valley

voltage switching and minimize the switching loss on the PWM switch.

Providing output over-voltage protection. A voltage comparator is built-in to the DET pin. The

DET pin detects the flat voltage through a voltage divider paralleled with auxiliary winding. This

flat voltage is reflected to the secondary winding during PWM inductor discharge time. If output

OVP and this flat voltage is higher than 2.5 V, the controller enters auto recovery mode.

10

Description

Totem-pole driver output to drive the external power MOSFET. The clamped gate output voltage

is 15.5 V.

Power supply. The threshold voltages for startup and turn-off are 18 V and 7.5 V, respectively.

The startup current is less than 30 µA and the operating current is lower than 10 mA.

Totem-pole output generates the PWM signal to drive the external power MOSFET. The clamped

gate output voltage is 17.5 V.

11

FB

Feedback voltage pin. This pin is used to receive the output voltage / current level signal to

determine PWM gate duty for regulating output voltage / current. The FB pin voltage can also

activate open-loop, overload, and output-short circuit protection if the FB pin voltage is higher

than a threshold of around 4.2 V for more than 50 ms. The input impedance of this pin is a 5 kΩ

equivalent resistance. A one-third attenuator is connected between the FB pin and the input of

the CSPWM/FB comparator.

12

RT

Adjustable over-temperature protection. A constant current is flowed out of the RT pin. When the

RT pin voltage is lower than 0.8 V (typical), the controller stops all PFC and PWM switching

operation and enters auto recovery protection mode.

13

VIN

Line-voltage detection for brown-in / out protections. This pin can receive the AC input voltage

level through a voltage divider. The voltage level of the VIN pin is not only used to control

RANGE pin’s status; (ZCD) can also perform brown-in / out protection for AC input voltage UVP.

14

ZCD

Zero-current detection for the PFC stage. This pin is connected to an auxiliary winding coupled to

PFC inductor winding to detect the ZCD voltage signal once the PFC inductor current discharges

to zero. When the ZCD voltage signal is detected, the controller starts a new PFC switching

cycle. When the ZCD pin voltage is pulled to under 0.2 V (typical), it disables the PFC stage and

the controller stops PFC switching. This can be achieved with an external circuit if disabling the

PFC stage is desired.

15

NC

No connection

16

HV

High-voltage startup. HV pin is connected to the AC line voltage through a resistor

100 kΩtypical) for providing a high charging current to VDD capacitor.

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Pin Definitions (Continued)

www.fairchildsemi.com

5

�Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol

Parameter

Min.

Max.

Unit

25

V

VDD

DC Supply Voltage

VHV

HV Pin Voltage

500

V

VH

OPFC, OPWM Pin Voltage

-0.3

25.0

V

VL

Other Pins (INV, COMP, CSPFC, DET, FB, CSPWM, RT)

-0.3

7.0

V

Input Voltage to ZCD Pin

-0.3

12.0

V

VZCD

PD

Power Dissipation

800

mW

JA

Thermal Resistance (Junction-to-Air)

104

°C/W

JC

Thermal Resistance (Junction-to-Case)

41

°C/W

TJ

Operating Junction Temperature

-40

+150

°C

Storage Temperature Range

-55

+150

°C

+260

°C

TSTG

TL

ESD

Lead Temperature (Soldering 10 Seconds)

Human Body Model, JESD22-A114 (All Pins Except HV Pin)

(3)

Charged Device Model, JESD22-C101 (All Pins Except HV Pin)

5

(3)

2

kV

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. All voltage values, except differential voltages, are given with respect to GND pin.

3. All pins including HV pin: CDM=0.5 kV, HBM=1 kV.

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Absolute Maximum Ratings

www.fairchildsemi.com

6

�VDD=15 V, TJ=-40°C ~125°C, unless otherwise specified.

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

25

V

VDD Section

VOP

Continuously Operating Voltage

VDD-ON

Turn-On Threshold Voltage

16.5

18.0

19.5

V

VDD-PWM-OFF

PWM-Off Threshold Voltage

9

10

11

V

VDD-OFF

Turn-Off Threshold Voltage

TA=25°C

6.5

7.5

8.5

V

IDD-ST

Startup Current

VDD=VDD-ON - 0.16 V,

Gate Open

20

30

µA

IDD-OP

Operating Current

VDD=15 V;

OPFC, OPWM=100 kHz;

CL-PFC, CL-PWM=2 nF

10

mA

IDD-GREEN

Green-Mode Operating Supply

Current (Average)

VDD=15 V,

OPWM=450 Hz,

CL-PWM=2 nF

IDD-PWM-OFF

Operating Current at PWM-Off

Phase

VDD=VDD-PWM-OFF - 0.5 V

5.5

mA

70

120

170

µA

VDD-OVP

VDD Over-Voltage Protection

(Auto Recovery)

23

24

25

V

tVDD-OVP

VDD OVP De-bounce Time

100

150

200

µs

IDD-LATCH

CSPWM Pin Open Protection

Latch-Up Holding Current

VDD=7.5 V

μA

120

HV Startup Current Source Section

VHV-MIN

IHV

Minimum Startup Voltage on HV

Pin

Supply Current Drawn from HV Pin

50

VAC=90 V (VDC=120 V),

VDD=0 V

1.3

HV=500 V,

VDD= VDD-OFF +1 V

V

mA

1

µA

VIN and RANGE Section

VVIN-UVP

Threshold Voltage for AC Input

Under-Voltage Protection

0.95

1.00

1.05

V

VVIN-RE-UVP

Under-Voltage Protection Reset

Voltage (for Startup)

VVIN-UVP

+0.25 V

VVIN-UVP

+0.30 V

VVIN-UVP

+0.35 V

V

70

100

130

ms

tVIN-UVP

Under-Voltage Protection

Debounce Time (No Need at

Startup and Hiccup Mode)

VVIN-RANGE-H

High VVIN Threshold for RANGE

Comparator

2.40

2.45

2.50

V

VVIN-RANGE-L

Low VVIN Threshold for RANGE

Comparator

2.05

2.10

2.15

V

70

100

130

ms

tRANGE

Range Enable / Disable Debounce

Time

VRANGE-OL

Output Low Voltage of RANGE Pin IO=1 mA

0.5

V

IRANGE-OH

Output High Leakage Current of

RANGE Pin

200

nA

28

µs

tON-MAX-PFC

RANGE=5 V

PFC Maximum On-Time

22

25

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Electrical Characteristics

Continued on the following page…

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

www.fairchildsemi.com

7

�VDD=15 V, TJ=-40°C ~125°C, unless otherwise specified.

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

100

125

150

µmho

2.465

2.500

2.535

V

RANGE=Open

2.70

2.75

2.80

RANGE=Ground

2.60

2.65

2.70

VINVH / VREF,

RANGE=Open

1.06

1.14

VINVH / VREF,

RANGE=Ground

1.04

1.08

PFC Stage

Voltage Error Amplifier Section

(4)

Gm

Transconductance

VREF

Feedback Comparator Reference

Voltage

VINV-H

Clamp High Feedback Voltage

VRATIO

VINV-L

Clamp High Output Voltage Ratio

(4)

Clamp Low Feedback Voltage

V

V/V

2.35

2.45

RANGE=Open

2.25

2.90

2.95

V

RANGE=Ground

2.75

2.80

50

70

90

µs

0.35

0.45

0.55

V

50

70

90

µs

VINV-OVP

Over-Voltage Protection for INV

Input

tINV-OVP

Over-Voltage Protection Debounce

Time

VINV-UVP

Under-Voltage Protection for INV

Input

tINV-UVP

Under-Voltage Protection

Debounce Time

VINV-BO

PWM and PFC Off Threshold for

Brownout Protection

1.15

1.20

1.25

V

VCOMP-BO

Limited Voltage on COMP Pin for

Brownout Protection

1.55

1.60

1.65

V

VCOMP

Comparator Output High Voltage

6.0

V

VOZ

TA=25°C

Zero Duty Cycle Voltage on COMP

Pin

Comparator Output Source

Current

ICOMP

Comparator Output Sink Current

4.8

V

1.10

1.25

1.40

V

15

30

45

µA

0.50

0.75

1.00

mA

RANGE=Open,

VINV=2.75 V, VCOMP=5 V,

TA=25°C

20

30

40

RANGE=Ground,

VINV=2.65 V, VCOMP=5 V

20

VINV=2.3 V, VCOMP=1.5 V

VINV=1.5 V, TA=25°C

µA

30

40

PFC Current-Sense Section

VCSPFC

Threshold Voltage for Peak

Current Cycle-by-Cycle Limit

tPD

Propagation Delay

tBNK

Leading-Edge Blanking Time

AV

CSPFC Compensation Ratio for

THD

VCOMP=5 V

0.82

V

110

200

ns

110

180

250

ns

0.90

0.95

1.00

V/V

FL7921R — Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Lighting Controller

Electrical Characteristics (Continued)

Continued on the following page…

© 2015 Fairchild Semiconductor Corporation

FL7921R • Rev. 1.1

www.fairchildsemi.com

8

�VDD=15 V, TJ=-40°C ~125°C, unless otherwise specified.

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

14.0

15.5

17.0

V

1.5

V

PFC Output Section

VZ

PFC Gate Output Clamping

Voltage

VDD=25 V

VOL

PFC Gate Output Voltage Low

VDD=15 V, IO=100 mA

VOH

PFC Gate Output Voltage High

VDD=15 V, IO=100 mA

8

tR

PFC Gate Output Rising Time

VDD=12 V, CL=3 nF,

20~80%

30

65

100

ns

tF

PFC Gate Output Falling Time

VDD=12 V, CL=3 nF,

80~20%

30

50

70

ns

Input Threshold Voltage Rising

Edge

VZCD Increasing

1.9

2.1

2.3

V

VZCD-HYST

Threshold Voltage Hysteresis

VZCD Decreasing

0.25

0.35

0.45

V

VZCD-HIGH

Upper Clamp Voltage

IZCD=3 mA

8

10

VZCD-LOW

Lower Clamp Voltage

0.40

0.65

0.90

V

VZCD-SSC

Starting Source Current

Threshold Voltage

1.3

1.4

1.5

V

200

ns

V

PFC Zero-Current Detection Section

VZCD

tDELAY

tRESTART-PFC

Maximum Delay from ZCD to

Output Turn-On

VCOMP=5 V, fS=60 kHz

50

V

Restart Time

300

500

700

µs

Inhibit Time (Maximum Switching

VCOMP=5 V

Frequency Limit)

1.5

2.5

3.5

µs

VZCD-DIS

PFC Enable / Disable Function

Threshold Voltage

0.14

0.20

0.26

V

tZCD-DIS

PFC Enable / Disable Function

Debounce Time

100

150

200

µs

1/2.75

1/3.00

1/3.25

V/V

tINHIB

VZCD=100 mV

PWM STAGE

Feedback Input Section

AV

Input-Voltage to Current-Sense

(4)

Attenuation

AV=△VCSPWM /△VFB,

0