3.3�V/5�V ECL JK Flip‐Flop

MC100EP35

Description

The MC100EP35 is a higher speed/low voltage version of the EL35

JK flip-flop. The J/K data enters the master portion of the flip-flop

when the clock is LOW and is transferred to the slave, and thus the

outputs, upon a positive transition of the clock. The reset pin is

asynchronous and is activated with a logic HIGH.

The 100 Series contains temperature compensation.

www.onsemi.com

8

1

Features

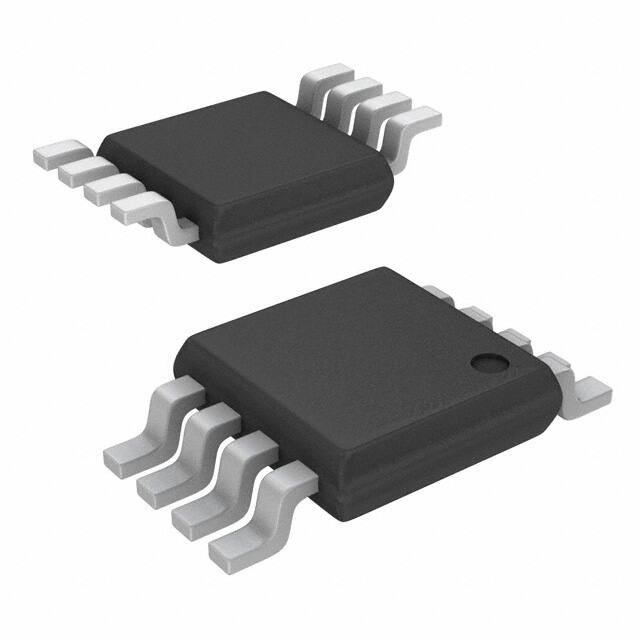

TSSOP−8

DT SUFFIX

CASE 948R−02

• 410 ps Propagation Delay

• Maximum Frequency > 3 GHz Typical

• PECL Mode Operating Range:

•

MARKING DIAGRAM*

VCC = 3.0 V to 5.5 V with VEE = 0 V

NECL Mode Operating Range:

♦ VCC = 0 V with VEE = −3.0 V to −5.5 V

Open Input Default State

♦

8

•

• Q Output Will Default LOW with Inputs Open or at VEE

• These Devices are Pb-Free, Halogen Free and are RoHS Compliant

1

K

A

L

Y

W

G

KP35

ALYWG

G

= MC100

= Assembly Location

= Wafer Lot

= Year

= Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

*For additional marking information, refer to

Application Note AND8002/D.

ORDERING INFORMATION

Device

MC100EP35DTG

Package

Shipping†

TSSOP−8

(Pb-Free)

100 Units /

Tube

MC100EP35DTR2G TSSOP−8

(Pb-Free)

2500 / Tape &

Reel

†For information on tape and reel specifications,

including part orientation and tape sizes, please refer

to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2016

April, 2021 − Rev. 9

1

Publication Order Number:

MC100EP35/D

�MC100EP35

Table 1. PIN DESCRIPTION

J

K

1

2

8

J

7

K

VCC

Q

Flip Flop

CLK

3

6

Q

4

FUNCTION

CLK*

ECL Clock Inputs

J*, K*

ECL Signal Inputs

RESET*

ECL Asynchronous Reset

Q, Q

ECL Data Outputs

VCC

Positive Supply

VEE

Negative Supply

* Pins will default LOW when left open.

R

RESET

PIN

Table 2. TRUTH TABLE

5

VEE

Figure 1. 8-Lead Pinout (Top View) and Logic Diagram

J

K

RESET

CLK

Qn+1

L

L

H

H

X

L

H

L

H

X

L

L

L

L

H

Z

Z

Z

Z

X

Qn

L

H

Qn

L

Z = LOW to HIGH Transition

Table 3. ATTRIBUTES

Characteristics

Value

Internal Input Pulldown Resistor

75 kW

Internal Input Pullup Resistor

N/A

ESD Protection

Human Body Model

Machine Model

Charged Device Model

> 4 kV

> 200 V

> 2 kV

Moisture Sensitivity, Indefinite Time Out of Drypack (Note 1)

TSSOP−8

Pb-Free Pkg

Level 3

Flammability Rating

Oxygen Index: 28 to 34

UL−94 V−0 @ 0.125 in

Transistor Count

77 Devices

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

1. For additional information, see Application Note AND8003/D.

www.onsemi.com

2

�MC100EP35

Table 4. MAXIMUM RATINGS

Symbol

Parameter

Condition 1

Condition 2

Rating

Unit

VCC

PECL Mode Power Supply

VEE = 0 V

6

V

VEE

NECL Mode Power Supply

VCC = 0 V

−6

V

VI

PECL Mode Input Voltage

NECL Mode Input Voltage

VEE = 0 V

VCC = 0 V

6

−6

V

Iout

Output Current

Continuous

Surge

50

100

mA

TA

Operating Temperature Range

−40 to +85

°C

Tstg

Storage Temperature Range

−65 to +150

°C

qJA

Thermal Resistance (Junction-to-Ambient)

0 lfpm

500 lfpm

TSSOP−8

185

140

°C/W

qJC

Thermal Resistance (Junction-to-Case)

Standard Board

TSSOP−8

41 to 44

°C/W

Tsol

Wave Solder (Pb-Free)

3

Typ

410

80

150

150

150

50

50

550

400

70

85°C

Max

Min

>3

200

Cycle-to-Cycle Jitter

(See Figure 2. Fmax/JITTER)

Output Rise/Fall Times

Q, Q (20% − 80%)

25°C

480

0.2

3

GHz

200

420

90

150

100

ps

150

150

50

50

150

150

80

80

ps

550

400

550

400

ps

80

490

Unit

0.2

很抱歉,暂时无法提供与“MC100EP35DTG”相匹配的价格&库存,您可以联系我们找货

免费人工找货