NC7WZ14

TinyLogic® UHS Dual Inverter with Schmitt Trigger

Inputs

Features

Description

Ultra-High Speed: tPD 3.2ns (Typical) into 50pF at

5V VCC

High Output Drive: ±24mA at 3V VCC

Power Down High Impedance Inputs/Outputs

The NC7WZ14 is a dual inverter with Schmitt trigger input

from Fairchild's Ultra-High Speed (UHS) Series of

TinyLogic. The device is fabricated with advanced CMOS

technology to achieve ultra-high speed with high output

drive while maintaining low static power dissipation over a

very broad VCC operating range. The device is specified to

operate over the 1.65V to 5.5V VCC range. The inputs and

outputs are high-impedance when VCC is 0V. Inputs

tolerate voltages up to 7V independent of VCC operating

voltage. Schmitt trigger inputs achieve typically 1V

hysteresis between the positive-and negative-going input

threshold voltage at 5V.

Proprietary Noise/EMI Reduction Circuitry

Broad VCC Operating Range: 1.65V to 5.5V

Matches Performance of LCX when Operated at

3.3V VCC

Over-Voltage Tolerance Inputs Facilitate 5V to 3V

Translation

Ultra-Small MicroPak™ Packages

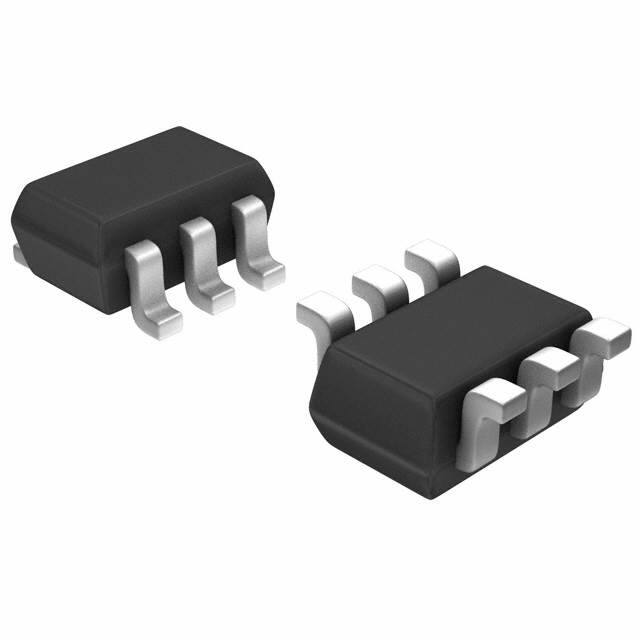

Space-Saving SC70 Package

Ordering Information

Operating

Temperature

Top

Mark

NC7WZ14P6X

-40 to +85°C

Z14

6-Lead SC70, EIAJ SC-88a, 1.25mm Wide

3000 Units on

Tape & Reel

NC7WZ14EP6X

-40 to +125°C

Z14

6-Lead SC70, EIAJ SC-88a, 1.25mm Wide

3000 Units on

Tape & Reel

NC7WZ14L6X

-40 to +85°C

A9

6-Lead MicroPak™, 1.00mm Wide

5000 Units on

Tape & Reel

NC7WZ14FHX

-40 to +85°C

A9

6-Lead, MicroPak2, 1x1mm Body, .35mm Pitch

5000 Units on

Tape & Reel

Part Number

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

Package

Packing

Method

www.fairchildsemi.com

NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

June 2011

�IEEC/IEC

Figure 1. Logic Symbol

Pin Configurations

Figure 2. SC70 (Top View)

A1

1

6

Y1

GND

2

5

VCC

A2

3

4

Y2

Figure 3. MicroPak (Top Through View)

AAA

Pin One

Notes:

1. AAA represents Product Code Top Mark (see ordering code).

2. Orientation of Top Mark determines Pin One location. Read the top product code mark left to right.

Pin One is the lower left pin.

Figure 4. SC70 Pin 1 Orientation

NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

Connection Diagrams

Pin Definitions

Pin # SC70

Pin # MicroPak

Name

Description

1

1

A1

2

2

GND

3

3

A2

Input

4

4

Y2

Output

5

5

VCC

Supply Voltage

6

6

Y1

Output

Input

Ground

Function Table

Y= /A

Inputs

Output

A

Y

L

H

H

L

H = HIGH Logic Level

L = LOW Logic Level

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

www.fairchildsemi.com

2

�Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol

Parameter

Min.

Max.

Unit

VCC

Supply Voltage

-0.5

7.0

V

VIN

DC Input Voltage

-0.5

7.0

V

VOUT

7.0

V

IIK

DC Input Diode Current

VIN < -0.5V

-50

mA

IOK

DC Output Diode Current

VOUT < -0.5V

-50

mA

IOUT

DC Output Current

±100

mA

DC VCC or Ground Current

±50

mA

+150

°C

+150

°C

+260

°C

ICC or IGND

TSTG

DC Output Voltage

-0.5

Storage Temperature Range

-65

TJ

Junction Temperature Under Bias

TL

Junction Lead Temperature (Soldering, 10 Seconds)

SC70-6

PD

ESD

Power Dissipation

TA=85°C

170

TA=125°C

104

MicroPak-6

130

MicroPak2-6

120

Human Body Model, JEDEC:JESD22-A114

4000

Charge Device Model, JEDEC:JESD22-C101

2000

mW

V

Recommended Operating Conditions(3)

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol

VCC

VIN

VOUT

TA

JA

Parameter

Conditions

Min.

Max.

Supply Voltage Operating

1.65

5.50

Supply Voltage Data Retention

1.5

5.5

0

5.5

V

V

Input Voltage

Output Voltage

Operating Temperature

Thermal Resistance

0

VCC

SC70-6

-40

+125

MicroPak-6

-40

+85

MicroPak2-6

-40

+85

SC70-6

390

MicroPak-6

500

MicroPak2-6

560

NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

Absolute Maximum Ratings

Unit

V

°C

°C/W

Note:

3. Unused inputs must be held HIGH or LOW. They may not float.

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

www.fairchildsemi.com

3

�Symbol

Parameter

VCC (V)

TA=-40 to

+85°C

TA=+25°C

Conditions

Min. Typ. Max.

VP

VN

VH

Positive Threshold

Voltage

Negative Threshold

Voltage

Hysteresis Voltage

0.60

1.40

0.60

1.40

0.60

1.40

1.50

0.70

1.50

0.70

1.50

2.30

1.00

1.80

1.00

1.80

1.00

1.80

3.00

1.30

2.20

1.30

2.20

1.30

2.20

4.50

1.90

3.10

1.90

3.10

2.00

3.20

5.50

2.20

3.60

2.20

3.60

2.30

3.70

1.65

0.20

0.50

0.80

0.20

0.80

0.30

0.90

1.80

0.25

0.56

0.90

0.25

0.90

0.35

1.00

2.30

0.40

0.75

1.15

0.40

1.15

0.50

1.20

3.00

0.60

0.98

1.50

0.60

1.50

0.70

1.60

4.50

1.00

1.42

2.00

1.00

2.00

1.10

2.20

5.50

1.20

1.68

2.30

1.20

2.30

1.40

2.50

1.65

0.10

0.48

0.90

0.10

0.90

0.10

0.90

1.80

0.15

0.51

1.00

0.15

1.00

0.15

1.00

2.30

0.25

0.62

1.10

0.25

1.10

0.25

1.10

3.00

0.40

0.76

1.20

0.40

1.20

0.40

1.20

4.50

0.60

1.01

1.50

0.60

1.50

0.60

1.50

1.70

0.70

1.70

0.70

1.70

5.50

0.70

1.20

1.65

1.55

1.65

1.55

1.55

1.70

1.80

1.70

1.70

2.20

2.30

2.20

2.20

2.90

3.00

2.90

2.90

VIN=VIL,

IOH=-100µA

4.50

4.40

4.50

4.40

4.40

1.65

IOH=-4mA

1.29

1.52

1.29

1.26

2.30

IOH=-8mA

1.90

2.14

1.90

1.80

3.00

IOH=-16mA

2.40

2.75

2.40

2.30

3.00

IOH=-24mA

2.30

2.62

2.30

2.20

4.50

IOH=-32mA

3.80

4.13

0.10

0.10

0.10

1.80

0.00

0.10

0.10

0.10

0.00

0.10

0.10

0.10

0.00

0.10

0.10

0.10

3.00

IIN

Input Leakage

Current

IOFF

Power Off Leakage

Current

ICC

Quiescent Supply

Current

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

4.50

1.65

IOL=4mA

V

V

3.70

0.00

VIN=VIH,

IOL=100µA

V

V

1.65

2.30

LOW Level Output

Voltage

3.80

Units

Max.

0.70

3.00

VOL

Min.

1.65

2.30

HIGH Level Output

Voltage

Max.

1.80

1.80

VOH

Min.

TA=-40 to

+125°C

0.00

0.10

0.10

0.10

0.08

0.24

0.24

0.26

V

2.30

IOL=8mA

0.10

0.30

0.30

0.32

3.00

IOL=16mA

0.16

0.40

0.40

0.43

3.00

IOL=24mA

0.24

0.55

0.55

0.60

4.50

IOL=32mA

0.25

0.55

0.55

0.60

±0.1

±1.0

±2.0

µA

1

10

20

µA

1.0

10

20

µA

0 to 5.5

0

1.65 to

5.50

VIN=5.5V, GND

VIN or

VOUT=5.5V

VIN=5.5V, GND

NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

DC Electrical Characteristics

www.fairchildsemi.com

4

�Symbol

Parameter

VCC (V)

TA=+25°C

Conditions

TA=-40 to

+85°C

TA=-40 to

+125°C

Units Figure

Min. Typ. Max. Min. Max. Min. Max.

1.65

2.5

7.6

13.1

2.5

14.5

2.5

14.7

1.80

2.5

6.3

10.9

2.5

12.0

2.5

12.3

1.8

4.3

7.4

1.8

8.1

1.8

8.4

3.30 ± 0.30

1.5

3.3

5.0

1.5

5.5

1.5

5.8

5.00 ± 0.50

1.0

2.7

4.1

1.0

4.5

1.0

4.8

3.30 ± 0.30 CL=50pF,

5.00 ± 0.50 RL=500

1.8

4.0

6.0

1.8

6.6

1.8

6.9

1.2

3.2

4.9

1.2

5.4

1.2

5.7

2.50 ± 0.20

tPLH, tPHL

CIN

CPD

Propagation Delay

CL=15pF,

RL=1M

Input Capacitance

0.00

2.5

Power Dissipation

(4)

Capacitance

3.30

11.0

5.00

12.5

Figure 5

Figure 6

ns

Figure 5

Figure 6

pF

pF

Figure 7

Note:

4. CPD is defined as the value of the internal equivalent capacitance which is derived from dynamic operating

current consumption (ICCD) at no output loading and operating at 50% duty cycle. CPD is related to ICCD dynamic

operating current by the expression: ICCD=(CPD)(VCC)(fIN)+(ICCstatic).

Note:

5. CL includes load and stray capacitance;

Input PRR=1.0MHz; tW =500ns

Figure 5. AC Test Circuit

NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

AC Electrical Characteristics

Figure 6. AC Waveforms

Note:

6. Input=AC Waveform; tr=tf=1.8ns; PRR=variable; Duty Cycle =50%.

Figure 7. ICCD Test Circuit

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

www.fairchildsemi.com

5

�NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

Physical Dimensions

SYMM

C

L

2.00±0.20

0.65

A

0.50 MIN

6

4

B

PIN ONE

1.25±0.10

1

1.90

3

0.30

0.15

(0.25)

0.40 MIN

0.10

0.65

A B

1.30

LAND PATTERN RECOMMENDATION

1.30

1.00

0.80

SEE DETAIL A

1.10

0.80

0.10 C

0.10

0.00

C

2.10±0.30

SEATING

PLANE

NOTES: UNLESS OTHERWISE SPECIFIED

GAGE

PLANE

(R0.10)

0.25

0.10

0.20

A) THIS PACKAGE CONFORMS TO EIAJ

SC-88, 1996.

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE BURRS

OR MOLD FLASH.

D) DRAWING FILENAME: MKT-MAA06AREV6

30°

0°

0.46

0.26

DETAIL A

SCALE: 60X

Figure 8. 6-Lead, SC70, EIAJ SC-88a, 1.25mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the

warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

Tape and Reel Specification

Please visit Fairchild Semiconductor’s online packaging area for the most recent tape and reel specifications:

http://www.fairchildsemi.com/products/analog/pdf/sc70-6_tr.pdf.

Package Designator

P6X

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

Tape Section

Cavity Number

Cavity Status Cover Type Status

Leader (Start End)

125 (Typical)

Empty

Sealed

Carrier

3000

Filled

Sealed

Trailer (Hub End)

75 (Typical)

Empty

Sealed

www.fairchildsemi.com

6

�NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

Physical Dimensions

2X

0.05 C

1.45

B

2X

(1)

0.05 C

(0.254)

(0.49)

5X

1.00

(0.75)

PIN 1 IDENTIFIER

5

(0.52)

1X

A

TOP VIEW

0.55MAX

(0.30)

6X

PIN 1

0.05 C

0.05

0.00

RECOMMENED

LAND PATTERN

0.05 C

C

0.25

0.15 6X

1.0

DETAIL A

0.10

0.05

0.45

0.35

0.10

0.00 6X

C B A

C

0.40

0.30

0.35 5X

0.25

0.40 5X

0.30

0.5

(0.05)

6X

BOTTOM VIEW

DETAIL A

PIN 1 TERMINAL

0.075 X 45

CHAMFER

(0.13)

4X

Notes:

1. CONFORMS TO JEDEC STANDARD M0-252 VARIATION UAAD

2. DIMENSIONS ARE IN MILLIMETERS

3. DRAWING CONFORMS TO ASME Y14.5M-1994

4. FILENAME AND REVISION: MAC06AREV4

5. PIN ONE IDENTIFIER IS 2X LENGTH OF ANY

OTHER LINE IN THE MARK CODE LAYOUT.

Figure 9. 6-Lead, MicroPak™, 1.0mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the

warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

Tape and Reel Specification

Please visit Fairchild Semiconductor’s online packaging area for the most recent tape and reel specifications:

http://www.fairchildsemi.com/products/logic/pdf/micropak_tr.pdf.

Package Designator

L6X

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

Tape Section

Cavity Number

Cavity Status Cover Type Status

Leader (Start End)

125 (Typical)

Empty

Sealed

Carrier

5000

Filled

Sealed

Trailer (Hub End)

75 (Typical)

Empty

Sealed

www.fairchildsemi.com

7

�NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

Physical Dimensions

0.89

0.35

0.05 C

1.00

2X

B

A

5X 0.40

PIN 1

MIN 250uM

0.66

1.00

1X 0.45

6X 0.19

0.05 C

TOP VIEW

RECOMMENDED LAND PATTERN

FOR SPACE CONSTRAINED PCB

2X

0.90

0.05 C

0.35

0.55MAX

C

5X 0.52

SIDE VIEW

0.73

(0.08) 4X

1

DETAIL A

2

1X 0.57

0.09

0.19 6X

3

0.20 6X

ALTERNATIVE LAND PATTERN

FOR UNIVERSAL APPLICATION

(0.05) 6X

5X 0.35

0.25

6

5

4

0.35

0.60

(0.08)

4X

0.10

.05 C

C B A

0.40

0.30

BOTTOM VIEW

NOTES:

A. COMPLIES TO JEDEC MO-252 STANDARD

B. DIMENSIONS ARE IN MILLIMETERS.

C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

D. LANDPATTERN RECOMMENDATION IS BASED ON FSC

DESIGN.

E. DRAWING FILENAME AND REVISION: MGF06AREV3

0.075X45°

CHAMFER

DETAIL A

PIN 1 LEAD SCALE: 2X

Figure 10. 6-Lead, MicroPak2, 1x1mm Body, .35mm Pitch

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the

warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

Tape and Reel Specification

Please visit Fairchild Semiconductor’s online packaging area for the most recent tape and reel specifications:

http://www.fairchildsemi.com/packaging/MicroPAK2_6L_tr.pdf.

Package Designator

FHX

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

Tape Section

Cavity Number

Cavity Status Cover Type Status

Leader (Start End)

125 (Typical)

Empty

Sealed

Carrier

5000

Filled

Sealed

Trailer (Hub End)

75 (Typical)

Empty

Sealed

www.fairchildsemi.com

8

�NC7WZ14 — TinyLogic® UHS Dual Inverter with Schmitt Trigger Inputs

© 1999 Fairchild Semiconductor Corporation

NC7WZ14 • Rev. 1.0.7

www.fairchildsemi.com

9

�

很抱歉,暂时无法提供与“NC7WZ14P6X”相匹配的价格&库存,您可以联系我们找货

免费人工找货- 国内价格

- 10+0.38504

- 100+0.31438