Buck Converter - DC-DC,

High Efficiency, Adjustable

Output Voltage, Low Ripple

1.7 MHz, 1 A

NCP1529

The NCP1529 step−down DC−DC converter is a monolithic

integrated circuit for portable applications powered from one cell

Li−ion or three cell Alkaline/NiCd/NiMH batteries. The device is able

to deliver up to 1.0 A on an output voltage range externally adjustable

from 0.9 V to 3.9 V or fixed at 1.2 V or 1.35 V. It uses synchronous

rectification to increase efficiency and reduce external part count. The

device also has a built−in 1.7 MHz (nominal) oscillator which reduces

component size by allowing a small inductor and capacitors. Automatic

switching PWM/PFM mode offers improved system efficiency.

Additional features include integrated soft−start, cycle−by−cycle

current limiting and thermal shutdown protection.

The NCP1529 is available in a space saving, low profile

2x2x0.5 mm UDFN6 package and TSOP−5 package.

www.onsemi.com

MARKING

DIAGRAM

5

5

1

DXJAYWG

G

1

DXJ

= Specific Device Code

A

= Assembly Location

Y

= Year

W

= Work Week

G

= Pb−Free Package

(Note: Microdot may be in either location)

Features

•

•

•

•

•

•

•

•

•

•

•

•

•

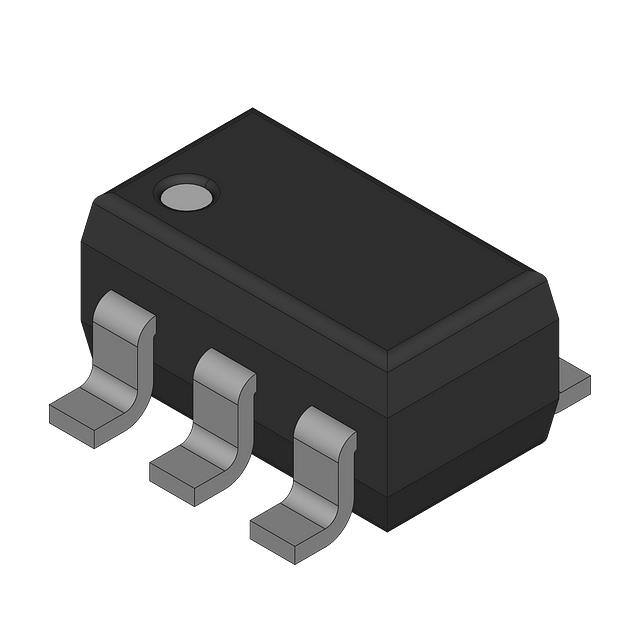

TSOP−5

SN SUFFIX

CASE 483

Up to 96% Efficiency

Best In Class Ripple, including PFM mode

Source up 1.0 A

1.7 MHz Switching Frequency

Adjustable from 0.9 V to 3.9 V or Fixed at 1.2 V or 1.35 V

Synchronous rectification for higher efficiency

2.7 V to 5.5 V Input Voltage Range

Low Quiescent Current 28 mA

Shutdown Current Consumption of 0.3 mA

Thermal Limit Protection

Short Circuit Protection

All Pins are Fully ESD Protected

These are Pb−Free Devices

UDFN6

MU SUFFIX

CASE 517AB

1

2

3

6

XXMG 5

G

4

XX

= Specific Device Code

M

= Date Code

G

= Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 14 of this data sheet.

Typical Applications

•

•

•

•

•

•

Cellular Phones, Smart Phones and PDAs

Digital Still Cameras

MP3 Players and Portable Audio Systems

Wireless and DSL Modems

USB Powered Devices

Portable Equipment

VIN

VIN

SW

CIN

OFF ON

L

VOUT

VIN

R1

Cff

R2

Figure 1. Typical Application for Adjustable Version

© Semiconductor Components Industries, LLC, 2010

August, 2020− Rev. 6

SW

CIN

COUT

EN

FB

GND

VIN

OFF ON

L

VOUT

COUT

EN

FB

GND

Figure 2. Typical Application for Fixed Version

1

Publication Order Number:

NCP1529/D

�NCP1529

PIN FUNCTION DESCRIPTION

Pin

TSOP−5

Pin

UDFN6

Pin Name

Type

1

6

EN

Analog Input

2

2,4,7

(Note 1)

GND

Analog /

Power Ground

This pin is the GND reference for the NFET power stage and the analog

section of the IC. The pin must be connected to the system ground.

3

5

SW

Analog Output

Connection from power MOSFETs to the Inductor.

4

3

VIN

Analog /

Power Input

Power supply input for the PFET power stage, analog and digital blocks. The

pin must be decoupled to ground by a 4.7 mF ceramic capacitor.

5

1

FB

Analog Input

Feedback voltage from the output of the power supply. This is the input to the

error amplifier.

Description

Enable for switching regulators. This pin is active HIGH and is turned off by

logic LOW on this pin.

1. Exposed pad for UDFN6 package, named Pin 7, must be connected to system ground.

PIN CONNECTIONS

EN

1

GND

2

SW

3

5

FB

4 VIN

FB

1

GND

2

VIN

3

7

6

EN

5

SW

4

GND

(Top View)

(Top View)

Figure 3. Pin Connections − TSOP−5

Figure 4. Pin Connections − UDFN6

PERFORMANCES

100

90

EFFICIENCY (%)

80

70

60

50

40

30

20

10

0

0

500

IOUT (mA)

Figure 5. Efficiency vs Output Current

VIN = 3.6 V, VOUT = 3.3 V

www.onsemi.com

2

1000

�NCP1529

FUNCTIONAL BLOCK DIAGRAM

Q1

Vbattery

Q2

VIN

2.2 mH

SW

PWM/PFM

CONTROL

10 mF

4.7 mF

GND

Enable

EN

R1

ILIMIT

LOGIC

CONTROL

& THERMAL

SHUTDOWN

FB

REFERENCE

VOLTAGE

R2

Figure 6. Simplified Block Diagram

www.onsemi.com

3

18 pF

�NCP1529

MAXIMUM RATINGS

Symbol

Value

Unit

Minimum Voltage All Pins

Rating

Vmin

−0.3

V

Maximum Voltage All Pins (Note 2)

Vmax

7.0

V

Maximum Voltage EN

Vmax

VIN + 0.3

V

Thermal Resistance, Junction−to−Air (TSOP−5 Package)

Thermal Resistance using TSOP−5 Recommended Board Layout (Note 9)

RqJA

300

110

°C/W

Thermal Resistance, Junction−to−Air (UDFN6 Package)

Thermal Resistance using UDFN6 Recommended Board Layout (Note 9)

RqJA

220

40

°C/W

Operating Ambient Temperature Range (Notes 7 and 8)

TA

−40 to 85

°C

Storage Temperature Range

Tstg

−55 to 150

°C

Junction Operating Temperature (Notes 7 and 8)

Tj

−40 to 150

°C

Latchup Current Maximum Rating (TA = 85°C) (Note 5) Other Pins

Lu

$100

mA

2.0

200

kV

V

1

per IPC

ESD Withstand Voltage (Note 4)

Human Body Model

Machine Model

Vesd

Moisture Sensitivity Level (Note 6)

MSL

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

2. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at TA = 25°C.

3. According to JEDEC standard JESD22−A108B.

4. This device series contains ESD protection and exceeds the following tests:

Human Body Model (HBM) per JEDEC standard: JESD22−A114.

Machine Model (MM) per JEDEC standard: JESD22−A115.

5. Latchup current maximum rating per JEDEC standard: JESD78.

6. JEDEC Standard: J−STD−020A.

7. In applications with high power dissipation (low VIN, high IOUT), special care must be paid to thermal dissipation issues. Board design

considerations − thermal dissipation vias, traces or planes and PCB material − can significantly improve junction to air thermal resistance

RqJA (for more information, see design and layout consideration section). Environmental conditions such as ambient temperature TA brings

thermal limitation on maximum power dissipation allowed.

The following formula gives calculation of maximum ambient temperature allowed by the application:

TA MAX = TJ MAX − (RqJA x Pd)

Where: TJ is the junction temperature,

Pd is the maximum power dissipated by the device (worst case of the application),

and RqJA is the junction−to−ambient thermal resistance.

8. To prevent permanent thermal damages, this device include a thermal shutdown which engages at 180°C (typ).

9. Board recommended TSOP−5 and UDFN6 layouts are described on Layout Considerations section.

1200

IOUTmax, MAXIMUM OUTPUT CURRENT (mA)

PD, POWER DISSIPATION (mW)

1200

UDFN6

1000

800

1000

TSOP−5

600

400

200

0

−40

−20

0

20

40

60

800

TSOP−5

600

400

200

0

2.7

80

UDFN6

TA, AMBIENT TEMPERATURE (°C)

3.7

4.2

4.7

VIN, INPUT VOLTAGE (V)

Figure 8. Power Derating

Figure 7. Maximum Output Current, TA = 455C

www.onsemi.com

4

3.2

5.2

�NCP1529

ELECTRICAL CHARACTERISTICS (Typical values are referenced to TA = +25°C, Min and Max values are referenced −40°C to

+85°C ambient temperature, unless otherwise noted, operating conditions VIN = 3.6 V, VOUT = 1.2 V, unless otherwise noted.)

Rating

Conditions

Symbol

Min

Typ

Max

Vin

IQ

Unit

2.7

−

5.5

V

−

28

39

mA

INPUT VOLTAGE

Input Voltage Range

Quiescent Current

No Switching, No load

Standby Current

EN Low

Under Voltage Lockout

VIN Falling

Under Voltage Hysteretis

ISTB

−

0.3

1.0

mA

VUVLO

2.2

2.4

2.55

V

VUVLOH

−

100

−

mV

VIH

1.2

−

−

V

ANALOG AND DIGITAL PIN

Positive going Input High Voltage Threshold

Negative going Input High Voltage Threshold

VIL

−

−

0.4

V

VENH

−

100

−

mV

EN = 3.6 V

IENH

−

1.5

−

mA

Adjustable Version

Fixed Version at 1.2 V

Fixed Version at 1.35 V

VFB

−

−

−

0.6

1.2

1.35

−

−

−

V

VOUT

0.9

0.9

−

−

3.3

3.9

V

DVOUT

−

−3

$1

$2

−

+3

%

IOUTMAX

1

−

−

A

EN Threshold Hysteresis

EN High Input Current

OUTPUT

Feedback Voltage Level

Output Voltage Range (Notes 10, 11)

Output Voltage Accuracy

USB or 5 V Rail Powered Applications

(VIN from 4.3 V to 5.5 V) (Note 12)

Room Temperature (Note 13)

Overtemperature Range

Maximum Output Current (Note 10)

Output Voltage Load Regulation

Overtemperature

Load = 100 mA to 1000 mA (PWM Mode)

Load = 0 mA to 100 mA (PFM Mode)

VLOADR

−

−

−0.9

1.1

−

−

%

Load Transient Response

Rise/Fall Time 1 ms

10 mA to 100 mA Load Step

(PFM to PWM Mode)

200 mA to 600 mA Load Step

(PWM to PWM Mode)

VLOADT

−

40

−

mV

−

85

−

VLINER

−

0.05

−

%

Output Voltage Line Regulation Load = 100 mA VIN = 2.7 V to 5.5 V

Line Transient Response Load = 100 mA

3.6 V to 3.2 V Line Step (Fall Time = 50 ms)

VLINET

−

6.0

−

mVPP

Output Voltage Ripple

IOUT = 0 mA

IOUT = 300 mA

VRIPPLE

−

−

8.0

3.0

−

−

mVPP

FSW

1.2

1.7

2.2

MHz

Switching Frequency

Duty Cycle

D

−

−

100

%

tSTART

−

310

500

ms

High−Side MOSFET On−Resistance

RONHS

−

400

−

mW

Low−Side MOSFET On−Resistance

RONLS

−

300

−

mW

High−Side MOSFET Leakage Current

ILEAKHS

−

0.05

−

mA

Low−Side MOSFET Leakage Current

ILEAKLS

−

0.01

−

mA

IPK

−

1.6

−

A

Thermal Shutdown Threshold

TSD

−

180

−

°C

Thermal Shutdown Hysteresis

TSDH

−

40

−

°C

Soft−Start Time

Time from EN to 90% of Output Voltage

POWER SWITCHES

PROTECTION

DC−DC Short Circuit Protection

Peak Inductor Current

10. Functionality guaranteed per design and characterization.

11. Whole output voltage range is available for adjustable versions only. By topology, the maximum output voltage will be equal or lower than

the input voltage.

12. See chapter ”USB or 5 V Rail Powered Applications”.

13. For adjustable versions only, the overall output voltage tolerance depends upon the accuracy of the external resistor (R1 and R2). Specified

value assumes that external resistor have 0.1% tolerance.

www.onsemi.com

5

�NCP1529

TABLE OF GRAPHS

Typical Characteristics for Step−down Converter

Figure

Efficiency

vs. Output Current

Iq ON

Quiescent Current, PFM no load

vs. Input Voltage

9

Iq OFF

Standby Current, EN Low

vs. Input Voltage

8

Switching Frequency

vs. Ambient Temperature

13

VLOADR

Load Regulation

vs. Load Current

14

VLOADT

Load Transient Response

VLINER

Line Regulation

VLINET

Line Transient Response

tSTART

Soft Start

20

Short Circuit Protection

21

h

FSW

IPK

10, 11, 12

16, 17

vs. Output Current

15

18, 19

VUVLO

Under Voltage Lockout Threshold

vs. Ambient Temperature

22

VIL, VIH

Enable Threshold

vs. Ambient Temperature

23

P, G

Phase & Gain Performance

24

www.onsemi.com

6

�NCP1529

31

Iq, QUIESCENT CURRENT (mA)

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

2.5

3.0

3.5

4.0

4.5

5.5

29

28

27

2.5

4.0

4.5

5.0

5.5

Figure 10. Quiescent Current vs. Input Voltage

(Open Loop, Feedback = 1,

Temperature = 255C)

90

90

80

−40°C

70

60

25°C

50

85°C

40

30

60

50

10

600

800

1000

3.3 V

30

10

400

VBAT = 2.7 V

40

20

200

5.5 V

70

20

0

0

200

400

600

800

IOUT, OUTPUT CURRENT (mA)

IOUT, OUTPUT CURRENT (mA)

Figure 11. Efficiency vs. Output Current

(VIN = 3.3 V, VOUT = 1.2 V)

Figure 12. Efficiency vs. Output Current

(Vout = 1.2 V, Temperature = 255C)

1000

2.2

3.3 V

90

80

1.2 V

70

60

VOUT = 0.9 V

50

40

30

20

10

0

200

400

600

800

IOUT, OUTPUT CURRENT (mA)

SWITCHING FREQUENCY (MHz)

100

0

3.5

Figure 9. Standby Current vs. Input Voltage

(Enable = 0, Temperature = 255C)

100

0

3.0

VIN, INPUT VOLTAGE (V)

100

0

EFFICIENCY (%)

30

VIN, INPUT VOLTAGE (V)

80

EFFICIENCY (%)

5.0

EFFICIENCY (%)

Istb, STANDBY CURRENT (mA)

1.0

1000

2.1

2

1.9

VIN = 2.7 V

1.8

1.7

1.6

3.6 V

1.5

1.4

5.5 V

1.3

1.2

−60

Figure 13. Efficiency vs. Output Current

(VIN = 3.6 V, Temperature = 255C)

−20

20

60

TA, AMBIENT TEMPERATURE (°C)

100

Figure 14. Switching Frequency vs. Ambient

Temperature (Vout = 1.2 V, Iout = 200 mA)

www.onsemi.com

7

�3.0

3.0

2.0

2.0

LINE REGULATION (%)

LOAD REGULATION (%)

NCP1529

1.0

−40°C

0.0

−1.0

25°C

−2.0

−3.0

0

200

400

85°C

600

800

1000

1.0

100 mA

0

−1.0

1 mA

IOUT = 800 mA

−2.0

−3.0

2.7

3.2

3.7

4.2

4.7

5.2

IOUT, OUTPUT CURRENT (mA)

VIN, INPUT VOLTAGE (V)

Figure 15. Load Regulation vs. Output Current

(VIN = 5.5 V, VOUT = 1.2 V)

Figure 16. Line Regulation vs. Input Voltage

(VOUT = 1.2 V, Temperature = 255C)

Figure 17. 10 mA to 100 mA Load Transient in 1 ms

(VIN = 3.6 V, VOUT = 1.2 V, Temperature = 255C)

Figure 18. 200 mA to 600 mA Load Transient in 1 ms

(VIN = 3.6 V, VOUT = 1.2 V, Temperature = 255C)

Figure 19. 3.0 V to 3.6 V Line Transient, Rise = 50 ms

(VIN = 1.2 V, IOUT = 100 mA, Temperature = 255C)

Figure 20. 3.6 V to 3.0 V Line Transient, Fall = 50 ms

(VIN = 1.2 V, IOUT = 100 mA, Temperature = 255C)

www.onsemi.com

8

�NCP1529

Figure 22. Short−Circuit Protection (VIN = 3.6 V,

VOUT = 1.2 V, IOUT = CC, Temperature = 255C)

1.2

2.55

ENABLE THRESHOLD VOLTAGES (V)

2.60

UVLOrise

2.50

2.45

UVLOfall

2.40

2.35

2.30

2.25

−25

0

25

50

75

100

125

1.1

1.0

0.9

VIH

0.8

0.7

VIL

0.6

0.5

0.4

−40

−15

10

35

60

TA, AMBIENT TEMPERATURE (°C)

TA, AMBIENT TEMPERATURE (°C)

Figure 23. Undervoltage Lockout Threshold

vs. Ambient Temperature

Figure 24. Enable Threshold Voltages vs.

Ambient Temperature

70

200

160

50

120

30

Phase

40

10

0

Gain

−10

−40

−80

−30

−50

10

80

PHASE (°)

2.20

−50

GAIN (dB)

UNDERVOLTAGE LOCKOUT THRESHOLD (V)

Figure 21. Typical Soft−Start (VIN = 3.6 V, VOUT = 1.2 V,

IOUT = 100 mA, Temperature = 255C)

−120

100

1000

10000

100000

−160

1000000

FREQUENCY (Hz)

Figure 25. Phase and Gain Performance

(VIN = 3.6 V, VOUT = 1.2 V, IOUT = 200 mA, Temperature = 255C)

www.onsemi.com

9

85

�NCP1529

DC/DC OPERATION DESCRIPTION

Detailed Description

VOUT

The NCP1529 uses a constant frequency, current mode

step−down architecture. Both the main (P−channel

MOSFET) and synchronous (N−channel MOSFET)

switches are internal.

The output voltage is set by an external resistor divider in

the range of 0.9 V to 3.9 V and can source at least 1A.

The NCP1529 works with two modes of operation;

PWM/PFM depending on the current required. In PWM

mode, the device can supply voltage with a tolerance of

$3% and 90% efficiency or better. Lighter load currents

cause the device to automatically switch into PFM mode to

reduce current consumption and extended battery life.

Additional features include soft−start, undervoltage

protection, current overload protection and thermal

shutdown protection. As shown on Figure 1, only six

external components are required. The part uses an internal

reference voltage of 0.6 V. It is recommended to keep

NCP1529 in shutdown mode until the input voltage is 2.7 V

or higher.

ISW

VSW

Figure 26. PWM Switching Waveforms

(VIN = 3.6 V, VOUT = 1.2 V, IOUT = 600 mA,

Temperature = 255C)

PFM Operating Mode

Under light load conditions, the NCP1529 enters in low

current PFM mode of operation to reduce power

consumption. The output regulation is implemented by

pulse frequency modulation. If the output voltage drops

below the threshold of PFM comparator a new cycle will be

initiated by the PFM comparator to turn on the switch Q1.

Q1 remains ON during the minimum on time of the structure

while Q2 is in its current source mode. The peak inductor

current depends upon the drop between input and output

voltage. After a short dead time delay where Q1 is switched

OFF, Q2 is turned in its ON state. The negative current

detector will detect when the inductor current drops below

zero and sends a signal to turn Q2 to current source mode to

prevent a too large deregulation of the output voltage. When

the output voltage falls below the threshold of the PFM

comparator, a new cycle starts immediately.

PWM Operating Mode

In this mode, the output voltage of the device is regulated

by modulating the on−time pulse width of the main switch

Q1 at a fixed 1.7 MHz frequency.

The switching of the PMOS Q1 is controlled by a flip−flop

driven by the internal oscillator and a comparator that

compares the error signal from an error amplifier with the

sum of the sensed current signal and compensation ramp.

The driver switches ON and OFF the upper side transistor

(Q1) while the lower side transistor is switched OFF then

ON.

At the beginning of each cycle, the main switch Q1 is

turned ON by the rising edge of the internal oscillator clock.

The inductor current ramps up until the sum of the current

sense signal and compensation ramp becomes higher than

the error amplifier’s voltage. Once this has occurred, the

PWM comparator resets the flip−flop, Q1 is turned OFF

while the synchronous switch Q2 is turned ON. Q2 replaces

the external Schottky diode to reduce the conduction loss

and improve the efficiency. To avoid overall power loss, a

certain amount of dead time is introduced to ensure Q1 is

completely turned OFF before Q2 is being turned ON.

VOUT

VSW

ISW

Figure 27. PFM Switching Waveforms

(VIN = 3.6 V, VOUT = 1.2 V, IOUT = 0 mA,

Temperature = 255C)

www.onsemi.com

10

�NCP1529

Soft−Start

temperature exceeds 180°C, the device shuts down. In this

mode all power transistors and control circuits are turned

off. The device restarts in soft−start after the temperature

drops below 140°C. This feature is provided to prevent

catastrophic failures from accidental device overheating.

The NCP1529 uses soft−start to limit the inrush current

when the device is initially powered up or enabled. Soft start

is implemented by gradually increasing the reference

voltage until it reaches the full reference voltage. During

startup, a pulsed current source charges the internal

soft−start capacitor to provide gradually increasing

reference voltage. When the voltage across the capacitor

ramps up to the nominal reference voltage, the pulsed

current source will be switched off and the reference voltage

will switch to the regular reference voltage.

Short Circuit Protection

When the output is shorted to ground, the device limits the

inductor current. The duty−cycle is minimum and the

consumption on the input line is 550 mA (typ). When the

short circuit condition is removed, the device returns to the

normal mode of operation.

Cycle−by−cycle Current Limitation

USB or 5 V Rail Powered Applications

From the block diagram, an ILIM comparator is used to

realize cycle−by−cycle current limit protection. The

comparator compares the SW pin voltage with the reference

voltage, which is biased by a constant current. If the inductor

current reaches the limit, the ILIM comparator detects the

SW voltage falling below the reference voltage and releases

the signal to turn off the switch Q1. The cycle−by−cycle

current limit is set at 1600 mA (nom).

For USB or 5 V rail powered applications, NCP1529 is

able to supply voltages up to 3.9 V, 600 mA, operating in

PWM mode only, with high efficiency (Figure 28), low

output voltage ripple and good load regulation results over

all current range (Figure 29).

100

95

90

Low Dropout Operation

ǒ

V out + V OUT(max) ) I OUTǒR DS(on)_R INDUCTORǓ

•

•

•

•

Ǔ

EFFICIENCY (%)

The NCP1529 offers a low input to output voltage

difference. The NCP1529 can operate at 100% duty cycle.

In this mode the PMOS (Q1) remains completely ON. The

minimum input voltage to maintain regulation can be

calculated as:

(eq. 1)

VOUT: Output Voltage (V)

IOUT: Max Output Current

RDS(on): P−Channel Switch RDS(on)

RINDUCTOR: Inductor Resistance (DCR)

−40°C

85

80

75

70

65

60

55

50

45

40

25°C

85°C

0

200

400

600

800

1000

IOUT, OUTPUT CURRENT (mA)

Figure 28. Efficiency vs. Output Current

(VIN = 5.0 V, VOUT = 3.9 V)

Undervoltage Lockout

3.0

The Input voltage VIN must reach 2.4 V (typ) before the

NCP1529 enables the DC/DC converter output to begin the

start up sequence (see soft−start section). The UVLO

threshold hysteresis is typically 100 mV.

LOAD REGULATION (%)

2.5

2.0

Shutdown Mode

Forcing this pin to a voltage below 0.4 V will shut down

the IC. In shutdown mode, the internal reference, oscillator

and most of the control circuitries are turned off. Therefore,

the typical current consumption will be 0.3 mA (typical

value). Applying a voltage above 1.2 V to EN pin will enable

the DC/DC converter for normal operation. The device will

go through soft−start to normal operation.

1.5

1.0

0.5

−40°C

0.0

−0.5

−1.0

−1.5

25°C

85°C

−2.0

−2.5

−3.0

Thermal Shutdown

0

200

400

600

800

1000

IOUT, OUTPUT CURRENT (mA)

Internal Thermal Shutdown circuitry is provided to

protect the integrated circuit in the event that the maximum

junction Temperature is exceeded. If the junction

Figure 29. Load Regulation vs. Output Current

(VIN = 5.0 V, VOUT = 3.9 V)

www.onsemi.com

11

�NCP1529

APPLICATION INFORMATION

Output Voltage Selection

Input Capacitor Selection

In case of adjustable versions, the output voltage is

programmed through an external resistor divider connected

from VOUT to FB then to GND.

For low power consumption and noise immunity, the

resistor from FB to GND (R2) should be in the [100k−600k]

range. If R2 is 200 k given the VFB is 0.6 V, the current

through the divider will be 3.0 mA.

The formula below gives the value of VOUT, given the

desired R1 and the R1 value:

In PWM operating mode, the input current is pulsating

with large switching noise. Using an input bypass capacitor

can reduce the peak current transients drawn from the input

supply source, thereby reducing switching noise

significantly. The capacitance needed for the input bypass

capacitor depends on the source impedance of the input

supply.

The maximum RMS current occurs at 50% duty cycle

with maximum output current, which is IO, max/2.

For NCP1529, a low profile ceramic capacitor of 4.7 mF

should be used for most of the cases. For effective bypass

results, the input capacitor should be placed as close as

possible to the VIN Pin

V out + V FB

•

•

•

•

(1 ) R1ńR2)

(eq. 2)

VOUT: Output Voltage (V)

VFB: Feedback Voltage = 0.6 V

R1: Feedback Resistor from VOUT to FB

R2: Feedback Resistor from FB to GND

Table 1. LIST OF INPUT CAPACITORS

Manufacturer

Part Number

Case Size

Value

(mF)

DC Bias

(V)

Technology

MURATA

GRM15 series

0402

4.7

6.3

X5R

MURATA

GRM18 series

0603

4.7

10

X5R

TDK

C1608 series

0603

4.7

6.3

X5R

TDK

C1608 series

0603

4.7

10

X5R

Output L−C Filter Design Considerations

Inductor Selection

The NCP1529 operates at 1.7 MHz frequency and uses

current mode architecture. The correct selection of the

output filter ensures good stability and fast transient

response.

Due to the nature of the buck converter, the output L−C

filter must be selected to work with internal compensation.

For NCP1529, the internal compensation is internally fixed

and it is optimized for an output filter of L = 2.2 mH and

COUT = 10 mF.

The corner frequency is given by:

The inductor parameters directly related to device

performances are saturation current and DC resistance and

inductance value. The inductor ripple current (DIL)

decreases with higher inductance:

f+

1

2p ǸL

C OUT

+

1

2p Ǹ2.2 mH

10 mF

DI L +

The device operates with inductance value of 2.2 mH. If

the corner frequency is moved, it is recommended to check

the loop stability depending of the accepted output ripple

voltage and the required output current. Take care to check

the loop stability. The phase margin is usually higher than

45°.

I L(max) + I O(max) )

10 mF

4.7 mH

4.7 mF

Ǔ

V OUT

V IN

DI L

2

• IL(max): Maximum inductor current

• IO(max): Maximum Output current

(eq. 4)

(eq. 5)

The inductor’s resistance will factor into the overall

efficiency of the converter. For best performances, the DC

resistance should be less than 0.3 W for good efficiency.

Table 2. L−C FILTER EXAMPLE

2.2 mH

f SW

1*

The saturation current of the inductor should be rated

higher than the maximum load current plus half the ripple

current:

(eq. 3)

Output Capacitor (COUT)

L

ǒ

• DIL: Peak to peak inductor ripple current

• L: Inductor value

• fSW: Switching frequency

+ 34 kHz

Inductance (L)

V OUT

www.onsemi.com

12

�NCP1529

Table 3. LIST OF INDUCTORS

Manufacturer

Part Number

Case

Size

(mm)

Height

Max

(mm)

L

(mH)

DCR

Typ

(W)

DCR

Max

(W)

Rated

Current (mA)

Inductance

Drop

Rated

Current (mA)

Temperature

Drop

Structure

COILCRAFT

DO1605T-222

5.5 x 4.2

1.8

2.2

NA

0.070

1800 (-10%)

1700 (+40°C)

Wire Wound

COILCRAFT

EPL3015-222

3.0 x 3.0

1.5

2.2

0.082

0.094

1600 (-30%)

2000 (+40°C)

Wire Wound

COILCRAFT

EPL2014-222

2.0 x 2.0

1.4

2.2

0.120

0.132

1300 (-30%)

1810 (+40°C)

Wire Wound

MURATA

LQM2HPN2R2

2.5 x 2.0

1.0

2.2

0.080

0.100

NA

1300 (+40°C)

Multilayer

MURATA

LQH3NPN2R2

3.0 x 3.0

1.2

2.2

0.065

0.085

1150 (-30%)

1460 (+40°C)

Wire Wound

MURATA

LQH44PN2R2

4.0 x 4.0

1.8

2.2

0.049

0.059

2500 (-30%)

1800 (+40°C)

Wire Wound

TDK

MLP2520S2R2L

2.5 x 2.0

1.0

2.2

0.080

0.104

1300 (-30%)

NA

Multilayer

TDK

VLS252010T2R2

2.0 x 1.6

1.2

2.2

0.158

0.190

1400 (-30%)

1100 (+40°C)

Wire Wound

744 029 002

2.8 x 2.8

1.35

2.2

0.088

0.105

1150 (-35%)

1700 (+40°C)

Wire Wound

WURTH ELEC

Output Capacitor Selection

The output ripple voltage in PWM mode is given by:

Selecting the proper output capacitor is based on the

desired output ripple voltage. Ceramic capacitors with low

ESR values will have the lowest output ripple voltage and

are strongly recommended. The output capacitor requires

either an X7R or X5R dielectric.

DV OUT + DI L

ǒ

1

4

f SW

C OUT

) ESR

Ǔ

(eq. 6)

Table 4. LIST OF OUTPUT CAPACITORS

Manufacturer

Part Number

Case Size

Value

(mF)

DC Bias

(V)

Technology

MURATA

GRM15 series

0402

4.7

6.3

X5R

MURATA

GRM18 series

0603

4.7

10

X5R

MURATA

GRM18 series

0603

10

6.3

X5R

TDK

C1608 series

0603

4.7

6.3

X5R

TDK

C1608 series

0603

4.7

10

X5R

TDK

C1608 series

0603

10

6.3

X5R

Feed−Forward Capacitor Selection (Adjustable Only)

Having feed-forward capacitor of 1 nF or higher can

increase soft−start time and reduce inrush current. Choose a

small ceramic capacitor X7R or X5R or COG dielectric.

The feed-forward capacitor sets the feedback loop

response and acts on soft-start time. A minimum 18 pF

feed-forward capacitor is needed to ensure loop stability.

www.onsemi.com

13

�NCP1529

LAYOUT CONSIDERATIONS

Electrical Layout Considerations

capacitor is recommended to meet compensation

requirements.

A four layer PCB with a ground plane and a power plane

will help NCP1529 noise immunity and loop stability.

Implementing a high frequency DC−DC converter

requires respect of some rules to get a powerful portable

application. Good layout is key to prevent switching

regulators to generate noise to application and to

themselves.

Electrical layout guide lines are:

• Use short and large traces when large amount of current

is flowing.

• Keep the same ground reference for input and output

capacitors to minimize the loop formed by high current

path from the battery to the ground plane.

• Isolate feedback pin from the switching pin and the

current loop to protect against any external parasitic

signal coupling. Add a feed−forward capacitor between

VOUT and FB which adds a zero to the loop and

participates to the good loop stability. A 18 pF

Thermal Layout Considerations

High power dissipation in small package leads to thermal

consideration such as:

• Enlarge VIN trace and added several vias connected to

power plane.

• Connect GND pin to top plane.

• Join top, bottom and each ground plane together using

several free vias in order to increase radiator size.

For high ambient temperature and high power dissipation

requirements, UDFN6 package using exposed pad

connected to main radiator is recommended. Refer to

Notes 7, 8, and 9.

VOUT

Trace

EN Trace

FB Trace

VIN Trace

SW

Trace

SW

Trace

VIN Trace

FB Trace

VOUT

Trace

GND Plane

GND Plane

EN Trace

Figure 30. TSOP−5 Recommended Board Layout

Figure 31. UDFN6 Recommended Board Layout

ORDERING INFORMATION

Nominal

Output Voltage

Marking

Package

Shipping†

NCP1529ASNT1G*

Adj

DXJ

TSOP−5

3000 / Tape & Reel

NCP1529MUTBG*

Adj

TL

NCP1529MU12TBG**

1.2 V

TC

UDFN6

3000 / Tape & Reel

NCP1529MU135TBG

1.35 V

RC

Device

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specifications Brochure, BRD8011/D.

*Not recommended for new designs.

**This device is End of Life. Please contact sales for additional information and assistance with replacement devices.

The product described herein (NCP1529), may be covered by the following U.S. patents: TBD. There may be other patents pending.

www.onsemi.com

14

�MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

TSOP−5

CASE 483

ISSUE N

5

1

SCALE 2:1

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME

Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH

THICKNESS. MINIMUM LEAD THICKNESS IS THE

MINIMUM THICKNESS OF BASE MATERIAL.

4. DIMENSIONS A AND B DO NOT INCLUDE MOLD

FLASH, PROTRUSIONS, OR GATE BURRS. MOLD

FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT

EXCEED 0.15 PER SIDE. DIMENSION A.

5. OPTIONAL CONSTRUCTION: AN ADDITIONAL

TRIMMED LEAD IS ALLOWED IN THIS LOCATION.

TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2

FROM BODY.

D 5X

NOTE 5

2X

DATE 12 AUG 2020

0.20 C A B

0.10 T

M

2X

0.20 T

5

B

1

4

2

B

S

3

K

DETAIL Z

G

A

A

TOP VIEW

DIM

A

B

C

D

G

H

J

K

M

S

DETAIL Z

J

C

0.05

H

C

SIDE VIEW

SEATING

PLANE

END VIEW

GENERIC

MARKING DIAGRAM*

SOLDERING FOOTPRINT*

0.95

0.037

MILLIMETERS

MIN

MAX

2.85

3.15

1.35

1.65

0.90

1.10

0.25

0.50

0.95 BSC

0.01

0.10

0.10

0.26

0.20

0.60

0_

10 _

2.50

3.00

1.9

0.074

5

5

XXXAYWG

G

1

1

Analog

2.4

0.094

XXX = Specific Device Code

A

= Assembly Location

Y

= Year

W = Work Week

G

= Pb−Free Package

1.0

0.039

XXX MG

G

Discrete/Logic

XXX = Specific Device Code

M = Date Code

G

= Pb−Free Package

(Note: Microdot may be in either location)

0.7

0.028

SCALE 10:1

mm Ǔ

ǒinches

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

DOCUMENT NUMBER:

DESCRIPTION:

98ARB18753C

TSOP−5

*This information is generic. Please refer to

device data sheet for actual part marking.

Pb−Free indicator, “G” or microdot “ G”,

may or may not be present.

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

Printed versions are uncontrolled except when stamped “CONTROLLED COPY” in red.

PAGE 1 OF 1

ON Semiconductor and

are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

rights of others.

© Semiconductor Components Industries, LLC, 2018

www.onsemi.com

�MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

UDFN6 2x2, 0.65P

CASE 517AB

ISSUE C

DATE 10 APR 2013

SCALE 4:1

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.15 AND 0.25MM FROM THE TERMINAL TIP.

4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE

TERMINALS.

5. TIE BARS MAY BE VISIBLE IN THIS VIEW AND ARE CONNECTED TO

THE THERMAL PAD.

A B

D

NOTE 5

PIN ONE

REFERENCE

0.10 C

0.10 C

ÍÍ

ÍÍ

ÍÍ

E

END VIEW

TOP VIEW

ÉÉÉ

ÉÉÉ

ÇÇÇ

A3

DETAIL B

0.10 C

EXPOSED Cu

A

6X

0.08 C

A1

NOTE 4

C

SIDE VIEW

DETAIL A

D2

1

SEATING

PLANE

L

3

4

6X

L

DETAIL A

ALTERNATE TERMINAL

CONSTRUCTIONS

b

e

BOTTOM VIEW

0.10

M

C A B

0.05

M

C

A1

GENERIC

MARKING DIAGRAM*

ALTERNATE

CONSTRUCTIONS

L1

6

A3

DETAIL B

L

E2

ÉÉ

ÉÉ

ÇÇ

MOLD CMPD

MILLIMETERS

MIN

MAX

0.45

0.55

0.00

0.05

0.127 REF

0.25

0.35

2.00 BSC

1.50

1.70

2.00 BSC

0.80

1.00

0.65 BSC

0.25

0.35

--0.15

DIM

A

A1

A3

b

D

D2

E

E2

e

L

L1

XXMG

G

XX = Specific Device Code

M = Date Code

G

= Pb−Free Package

(Note: Microdot may be in either location)

*This information is generic. Please refer to

device data sheet for actual part marking.

Pb−Free indicator, “G” or microdot “ G”,

may or may not be present.

RECOMMENDED

SOLDERING FOOTPRINT*

PACKAGE

OUTLINE

1.70

6X

0.47

2.30

0.95

1

0.65

PITCH

6X

0.40

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

DOCUMENT NUMBER:

DESCRIPTION:

98AON22162D

UDFN6 2X2, 0.65P

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

Printed versions are uncontrolled except when stamped “CONTROLLED COPY” in red.

PAGE 1 OF 1

ON Semiconductor and

are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

rights of others.

© Semiconductor Components Industries, LLC, 2019

www.onsemi.com

�onsemi,

, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates

and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property.

A listing of onsemi’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. onsemi reserves the right to make changes at any time to any

products or information herein, without notice. The information herein is provided “as−is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the

information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use

of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products

and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information

provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may

vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license

under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems

or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should

Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of the part. onsemi is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

◊

TECHNICAL SUPPORT

North American Technical Support:

Voice Mail: 1 800−282−9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

�