NCP4586 150 mA, Low Noise, Low Dropout Regulator

The NCP4586 is a CMOS 150 mA low dropout linear with low noise, high ripple rejection, low dropout, high output voltage accuracy and low supply current. The device is available in three configurations: enable high, enable low and enable high plus auto−discharge. Small packages allow mounting on high density PCBs. This is an excellent general purpose regulator, well suited to many applications.

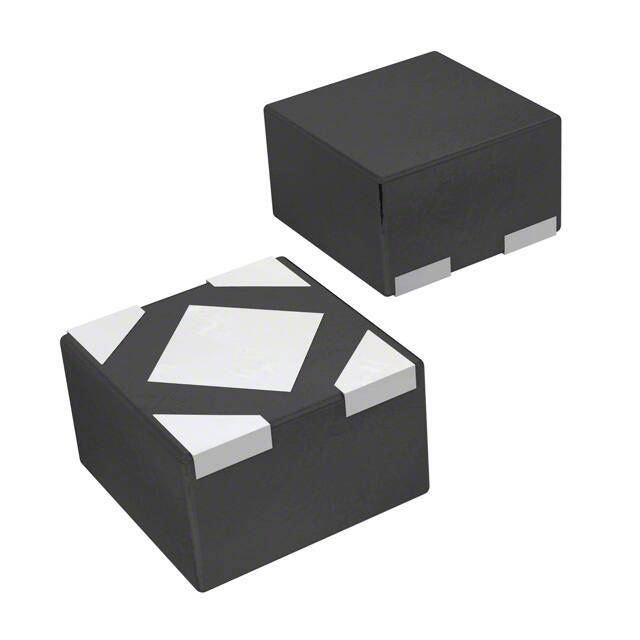

Features http://onsemi.com MARKING DIAGRAMS

1 UDFN4 CASE 517BR XX MM

• • • • • • • • • • • • •

Operating Input Voltage Range: 1.7 V to 6.5 V Output Voltage Range: 1.2 to 5.0 V (available in 0.1 V steps) Very Low Dropout: 320 mV Typ. at 150 mA ±1% Output Voltage Accuracy (VOUT > 2 V, TJ = 25°C) High PSRR: 80 dB at 1 kHz Current Fold Back Protection Stable with a 0.47 mF Ceramic Capacitors Available in 1.0 x 1.0 UDFN, SC−82AB and SOT23−5 Package These are Pb−Free Devices Battery Powered Equipment Portable Communication Equipment Cameras, MP3 Players and Camcorder High Stability Voltage Reference

VIN C1 470 n

1

XX MM SC−82AB CASE 419C 1

Typical Applications

SOT−23−5 CASE 1212

XXX MM

XX, XXX= Specific Product Code MM = Lot Number

NCP4586x

VIN CE GND VOUT

VOUT C2 470 n

ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 15 of this data sheet.

Figure 1. Typical Application Schematic

© Semiconductor Components Industries, LLC, 2011

May, 2011 − Rev. 4

1

Publication Order Number: NCP4586/D

�NCP4586

NCP4586Lxxxxxxxx NCP4586Hxxxxxxxx

VIN

VOUT

VIN

VOUT

Vref

Vref

Current Limit

CE

CE GND

Current Limit

GND

NCP4586Dxxxxxxxx

VIN

VOUT

Vref

CE

Current Limit

GND

Figure 2. Simplified Schematic Block Diagram

PIN FUNCTION DESCRIPTION

Pin No. UDFN4 4 2 3 1 − Pin No. SC82−AB 4 2 1 3 − Pin No. SOT23−5 1 2 3 5 4 Pin Name VIN GND CE/CE VOUT NC Input pin Ground Chip enable pin (“L” active / “H” active) Output pin No connection Description

http://onsemi.com

2

�NCP4586

ABSOLUTE MAXIMUM RATINGS

Rating Input Voltage (Note 1) Output Voltage Chip Enable Input Output Current Power Dissipation UDFN4 Power Dissipation SC−82AB Power Dissipation SOT23−5 Maximum Junction Temperature Operating Ambient Temperature Storage Temperature ESD Capability, Human Body Model (Note 2) ESD Capability, Machine Model (Note 2) TJ(MAX) TA TSTG ESDHBM ESDMM Symbol VIN VOUT VCE IOUT PD Value 7 −0.3 to VIN + 0.3 −0.3 to 7 200 400 380 420 +150 −40 to +85 −55 to +125 2000 200 °C °C °C V V mW Unit V V V mA

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating Area. 2. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC−Q100−002 (EIA/JESD22−A114) ESD Machine Model tested per AEC−Q100−003 (EIA/JESD22−A115) Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

THERMAL CHARACTERISTICS

Rating Thermal Characteristics, UDFN4 Thermal Resistance, Junction−to−Air Thermal Characteristics, SOT23−5 Thermal Resistance, Junction−to−Air Thermal Characteristics, SC 82AB Thermal Resistance, Junction−to−Air Symbol RqJA RqJA RqJA Value 250 238 263 Unit °C/W °C/W °C/W

http://onsemi.com

3

�NCP4586

ELECTRICAL CHARACTERISTICS −40°C ≤ TA ≤ 85°C; VIN = VOUT(NOM) + 1 V or 2.5 V, whichever is greater; IOUT = 1 mA, CIN =

COUT = 0.47 mF, unless otherwise noted. Typical values are at TA = +25 °C. Parameter Operating Input Voltage Output Voltage TA = +25 °C VOUT > 2 V VOUT ≤ 2 V −40°C ≤ TA ≤ 85°C VOUT > 2 V VOUT ≤ 2 V Output Voltage Temp. Coefficient Line Regulation Load Regulation Dropout Voltage TA = −40 to 85°C VIN = VOUT + 0.5 V to 5 V IOUT = 1 mA to 150 mA IOUT = 150 mA 1.2 V ≤ VOUT < 1.5 V 1.5 V ≤ VOUT < 1.7 V 1.7 V ≤ VOUT < 2.0 V 2.0 V ≤ VOUT < 2.5 V 2.5 V ≤ VOUT < 4.0 V 4.0 V ≤ VOUT Output Current Short Current Limit Quiescent Current Standby Current CE/CE Pin Threshold Voltage VOUT = 0 V IOUT = 0 mA VCE = VIN (L version), VCE = 0 V(H and D version), TA = 25°C CE / CE Input Voltage “H” CE / CE Input Voltage “L” CE Pull Down Current Power Supply Rejection Ratio Output Noise Voltage Low Output N−ch Tr. On Resistance H and D version VIN = VOUT + 1 V or 3.0 V whichever is higher, IOUT = 30 mA, f = 1 kHz VOUT = 1.2 V, IOUT = 30 mA, f = 10 Hz to 100 kHz D Version only, VIN = 4 V, VCE = 0 V IOUT ISC IQ ISTB VCEH VCEL IPD PSRR VN RLOW 0.4 80 30 30 1.0 0.4 mA dB mVrms W 150 40 38 0.1 58 1 LineReg LoadReg VDO Test Conditions Symbol VIN VOUT Min 1.7 x0.99 −20 x0.985 −30 ±20 0.02 10 0.67 0.54 0.46 0.41 0.32 0.24 0.10 30 1.00 0.81 0.68 0.60 0.51 0.37 mA mA mA mA V Typ Max 6.5 x1.01 20 x1.015 30 Unit V V mV V mV ppm/°C %/V mV V

http://onsemi.com

4

�NCP4586

TYPICAL CHARACTERISTICS

1.4 1.2 1.0 VOUT (V) 0.8 0.6 0.4 0.2 0.0 0 100 200 300 IOUT (mA) 400 500 VIN = 2.2 V 6.0 V 6.5 V 3.6 V 4.2 V VOUT (V) 3.0 2.5 2.0 1.5 1.0 0.5 0.0

4.2 V 6.0 V

VIN = 6.5 V 3.8 V

0

100

200 300 IOUT (mA)

400

500

Figure 3. Output Voltage vs. Output Current 1.2 V Version (TA = 25 5C)

6 5 4 VOUT (V) 3 2 1 0 0 VIN = 6.5 V 6.0 V VDO (V) 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 100 200 IOUT (mA) 300 400 500 0 0

Figure 4. Output Voltage vs. Output Current 2.8 V Version (TA = 25 5C)

25°C 85°C −40°C

100

200

300

400

500

IOUT (mA)

Figure 5. Output Voltage vs. Output Current 5.0 V version (TA = 255C)

Figure 6. Dropout Voltage vs. Output Current 1.2 V version

0.40 0.35 0.30 VDO (V) 0.25 0.20 0.15 0.10 0.05 0.00 0 100 200 IOUT (mA) 300 400 500 85°C −40°C VDO (V) 25°C

0.30 0.25 0.20 0.15 85°C 0.10 0.05 0.00 0 25 50 75 IOUT (mA) 100 125 150 −40°C

25°C

Figure 7. Dropout Voltage vs. Output Current 2.8 V Version

Figure 8. Dropout Voltage vs. Output Current 5.0 V Version

http://onsemi.com

5

�NCP4586

TYPICAL CHARACTERISTICS

1.25 VIN = 2.2 V 1.23 1.21 1.19 1.17 1.15 −40 2.83 2.81 2.79 2.77 2.75 −40 2.85 VIN = 3.8 V

VOUT (V)

Figure 9. Output Voltage vs. Temperature, 1.2 V Version

5.05 5.04 5.03 5.02 VOUT (V) 5.00 4.99 4.98 4.97 4.96 4.95 −40 −20 0 20 40 60 TJ, JUNCTION TEMPERATURE (°C) 80 IIN (mA) 5.01 50.0 45.0 40.0 35.0 30.0 25.0 20.0 15.0 10.0 5.0 0.0 0

−20 0 20 40 60 TJ, JUNCTION TEMPERATURE (°C)

80

VOUT (V)

Figure 10. Output Voltage vs. Temperature, 2.8 V version

−20 0 20 40 60 TJ, JUNCTION TEMPERATURE (°C)

80

VIN = 6.0 V

1

2

3 VIN (V)

4

5

6

Figure 11. Output Voltage vs. Temperature, 5.0 V Version

50.0 45.0 40.0 35.0 IIN (mA) IIN (mA) 30.0 25.0 20.0 15.0 10.0 5.0 0.0 0 1 2 3 VIN (V) 4 5 6 50.0 45.0 40.0 35.0 30.0 25.0 20.0 15.0 10.0 5.0 0.0 0

Figure 12. Supply Current vs. Input Voltage, 1.2 V Version

1

2

3 VIN (V)

4

5

6

Figure 14. Supply Current vs. Input Voltage, 2.8 V Version

Figure 13. Supply Current vs. Input Voltage, 5.0 V version

http://onsemi.com

6

�NCP4586

TYPICAL CHARACTERISTICS

40.0 39.0 38.0 37.0 IIN (mA) 35.0 34.0 33.0 32.0 31.0 30.0 −40 −20 0 20 40 60 80 IIN (mA) 36.0 VIN = 2.2 V 40.0 39.0 38.0 37.0 36.0 35.0 34.0 33.0 32.0 31.0 30.0 −40 −20 0 20 40 60 80 VIN = 3.8 V

TJ, JUNCTION TEMPERATURE (°C)

TJ, JUNCTION TEMPERATURE (°C)

Figure 15. Supply Current vs. Temperature, 1.2 V Version

45 44 43 42 40 39 38 37 36 35 −40 −20 0 20 40 60 80 VOUT (V) IIN (mA) 41 VIN = 6.0 V 1.4 1.2

Figure 16. Supply Current vs. Temperature, 2.8 V Version

1.0 1 mA 0.8 0.6 0.4 0.2 0.0 0 1 2 3 VIN (V) 4 5 6 7 30 mA IOUT = 50 mA

TJ, JUNCTION TEMPERATURE (°C)

Figure 17. Supply Current vs. Temperature, 5.0 V Version

3.0 2.5 2.0 VOUT (V) 1.5 1.0 0.5 0.0 30 mA IOUT = 50 mA 0 1 2 3 4 VIN (V) 5 6 7 1 mA VOUT (V) 6.0 5.0 4.0 3.0 2.0 1.0 0.0

Figure 18. Output Voltage vs. Input Voltage, 1.2 V Version

1 mA

30 mA IOUT = 50 mA

0

1

2

3 4 VIN (V)

5

6

7

Figure 19. Output Voltage vs. Input Voltage, 2.8 V Version

Figure 20. Output Voltage vs. Input Voltage, 5.0 V Version

http://onsemi.com

7

�NCP4586

TYPICAL CHARACTERISTICS

100 90 80 70 PSRR (dB) 60 50 40 30 20 10 0 0.01 0.1 1 10 FREQUENCY (kHz) 100 1000 30 mA PSRR (dB) IOUT = 150 mA 1 mA 100 90 80 70 60 50 40 30 20 10 0 0.01 0.1 1 10 FREQUENCY (kHz) 100 1000 1 mA 30 mA IOUT = 150 mA

Figure 21. PSRR, 1.2 V Version

100 90 80 70 PSRR (dB) 60 50 40 30 20 10 0 0.01 0.1 1 10 FREQUENCY (kHz) 100 1000 1 mA VN (mVrms/√Hz) 30 mA IOUT = 150 mA

Figure 22. PSRR, 2.8 V Version

1.6 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0 0.01 0.1 1 10 FREQUENCY (kHz) 100 1000

Figure 23. PSRR, 5.0 V Version

Figure 24. Output Voltage Noise, 1.2 V Version

7.0 6.0 VN (mVrms/√Hz) VN (mVrms/√Hz) 0.1 1 10 FREQUENCY (kHz) 100 1000 5.0 4.0 3.0 2.0 1.0 0 0.01

7.0 6.0 5.0 4.0 3.0 2.0 1.0 0 0.01 0.1 1 10 FREQUENCY (kHz) 100 1000

Figure 25. Output Voltage Noise, 2.8 V Version

Figure 26. Output Voltage Noise, 5.0 V Version

http://onsemi.com

8

�NCP4586

TYPICAL CHARACTERISTICS

4 3 2 VOUT (V) VIN (V) VIN (V) 1 1.205 1.200 1.195 1.190 0 10 20 30 40 50 t (ms) 60 70 80 90 100

Figure 27. Line Transients, 1.2 V Version, tR = tF = 5 ms, IOUT = 30 mA

6 5 4 VOUT (V) 3 2.805 2.800 2.795 2.790 0 10 20 30 40 50 t (ms) 60 70 80 90 100

Figure 28. Line Transients, 2.8 V Version, tR = tF = 5 ms, IOUT = 30 mA

7 6 5 VOUT (V) VIN (V) 4 5.005 5.000 4.995 4.990 0 10 20 30 40 50 t (ms) 60 70 80 90 100

Figure 29. Line Transients, 5.0 V Version, tR = tF = 5 ms, IOUT = 30 mA

http://onsemi.com

9

�NCP4586

TYPICAL CHARACTERISTICS

200 150 100 50 IOUT (mA) IOUT (mA) IOUT (mA) VOUT (V) 0 1.23 1.22 1.21 1.20 1.19 1.18

0

10

20

30

40

50 t (ms)

60

70

80

90

100

Figure 30. Load Transients, 1.2 V Version, IOUT = 50 − 100 mA, tR = tF = 0.5 ms, VIN = 2.2 V

200 150 100 50 VOUT (V) 0 2.83 2.82 2.81 2.80 2.79 2.78

0

10

20

30

40

50 t (ms)

60

70

80

90

100

Figure 31. Load Transients, 2.8 V Version, IOUT = 50 − 100 mA, tR = tF = 0.5 ms, VIN = 3.8 V

200 150 100 50 VOUT (V) 0 5.03 5.02 5.01 4.99 4.98 0 10 20 30 40 50 t (ms) 60 70 80 90 100

Figure 32. Load Transients, 5.0 V Version, IOUT = 50 − 100 mA, tR = tF = 0.5 ms, VIN = 6.0 V

http://onsemi.com

10

�NCP4586

TYPICAL CHARACTERISTICS

200 150 100 IOUT (mA) IOUT (mA) IOUT (mA) VOUT (V) 50 0 1.30 1.25 1.20 1.15 1.10 1.05

0

10

20

30

40

50 60 t (ms)

70

80

90

100

Figure 33. Load Transients, 1.2 V Version, IOUT = 1 − 150 mA, tR = tF = 0.5 ms, VIN = 2.2 V

200 150 100 VOUT (V) 50 0 2.90 2.85 2.80 2.75 2.70 2.65

0

10

20

30

40

50 60 t (ms)

70

80

90

100

Figure 34. Load Transients, 2.8 V Version, IOUT = 1 − 150 mA, tR = tF = 0.5 ms, VIN = 3.8 V

200 150 100 VOUT (V) 50 0 5.10 5.05 5.00 4.95 4.90 4.85

0

10

20

30

40

50 t (ms)

60

70

80

90

100

Figure 35. Load Transients, 5.0 V Version, IOUT = 1 − 150 mA, tR = tF = 0.5 ms, VIN = 6.0 V

http://onsemi.com

11

�NCP4586

TYPICAL CHARACTERISTICS

4 Chip Enable 3 2 1 VOUT (V) 2.0 1.5 1.0 0.5 0.0 −0.5 0 2 4 6 8 10 12 t (ms) 14 16 18 20 IOUT = 150 mA IOUT = 1 mA VCE (V) VCE (V) VCE (V) 0

Figure 36. Start−up, 1.2 V Version, VIN = 2.2 V

5 4 3 2 VOUT (V) 1 4 3 2 1 0 −1 0 2 4 6 8 10 t (ms) 12 14 16 18 20 IOUT = 1 mA IOUT = 150 mA

Chip Enable

Figure 37. Start−up, 2.8 V Version, VIN = 3.8 V

10 Chip Enable 8 6 4 VOUT (V) 2 8 6 4 2 0 −2 0 5 10 15 20 25 t (ms) 30 35 40 45 50 IOUT = 1 mA IOUT = 150 mA 0

Figure 38. Start−up, 5.0 V Version, VIN = 6.0 V

http://onsemi.com

12

�NCP4586

TYPICAL CHARACTERISTICS

4 3 2 Chip Enable VOUT (V) 2.0 1.5 1.0 0.5 0.0 −0.5 0 IOUT = 1 mA IOUT = 30 mA IOUT = 150 mA 10 20 30 40 50 60 t (ms) 70 80 90 100 1 VCE (V) VCE (V) VCE (V) 0

Figure 39. Shutdown, 1.2 V Version D, VIN = 2.2 V

5 4 3 VOUT (V) 2 2.0 1.5 1.0 0.5 0.0 −0.5 0 IOUT = 1 mA IOUT = 30 mA IOUT = 150 mA 10 20 30 40 50 t (ms) 60 70 80 90 100 Chip Enable 1

Figure 40. Shutdown, 2.8 V Version D, VIN = 3.8 V

10 8 6 4 VOUT (V) 8 6 4 2 0 −2 0 IOUT = 150 mA 10 20 30 40 50 t (ms) 60 70 80 90 100 IOUT = 1 mA IOUT = 30 mA Chip Enable 2 0

Figure 41. Shutdown, 5.0 V version D, VIN = 6.0 V

http://onsemi.com

13

�NCP4586

APPLICATION INFORMATION A typical application circuit for NCP4586 series is shown in Figure 42.

VIN C1 470n

NCP4586x

VIN CE GND VOUT

VOUT C2 470n

version of IC. Active high or low versions are available; please see the ordering information table. The Enable pin has an internal pull down current source for versions H and D. If the enable function is not needed connect the CE pin to ground for version L or connect the CE pin to VIN for versions H and D.

Output Discharger

The D version includes a transistor between VOUT and GND that is used for faster discharging of the output capacitor. This function is activated when the IC goes into disable mode.

Thermal

Figure 42. Typical Application Schematic Input Decoupling Capacitor (C1)

A 470 nF ceramic input decoupling capacitor should be connected as close as possible to the input and ground pin of the NCP4586. Higher values and lower ESR improves line transient response.

Output Decoupling Capacitor (C2)

A 470 nF or larger ceramic output decoupling capacitor is sufficient to achieve stable operation of the IC. If a tantalum capacitor is used, and its ESR is high, loop oscillation may result. The capacitors should be connected as close as possible to the output and ground pins. Larger values and lower ESR improves dynamic parameters.

Enable Operation

As power across the IC increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and also the ambient temperature affect the rate of temperature rise for the part. That is to say, when the device has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power dissipation applications.

PCB Layout

Make VIN and GND line sufficient. If their impedance is high, noise pickup or unstable operation may result. Connect capacitors C1 and C2 as close as possible to the IC, and make wiring as short as possible.

The Enable pin CE or CE may be used for turning the regulator on and off. Control polarity is dependent on

http://onsemi.com

14

�NCP4586

ORDERING INFORMATION

Device NCP4586DSQ12T1G NCP4586DSQ18T1G NCP4586DSQ28T1G NCP4586DSQ30T1G NCP4586DSQ33T1G NCP4586DSQ50T1G NCP4586DMU12TCG NCP4586DMU14TCG NCP4586DMU15TCG NCP4586DMU18TCG NCP4586DMU25TCG NCP4586DMU28TCG NCP4586DMU30TCG NCP4586DMU33TCG NCP4586DMU50TCG NCP4586DSN12T1G NCP4586DSN18T1G NCP4586DSN28T1G NCP4586DSN30T1G NCP4586DSN33T1G NCP4586DSN50T1G Nominal Output Voltage 1.2 V 1.8 V 2.8 V 3.0 V 3.3 V 5.0 V 1.2 V 1.4 V 1.5 V 1.8 V 2.5 V 2.8 V 3.0 V 3.3 V 5.0 V 1.2 V 1.8 V 2.8 V 3.0 V 3.3 V 5.0 V Enable High, Auto discharge Description Marking LA LG MH NA ND QA VA VC VD VG VQ VT VW VZ WS H2A H2G H2T H2W H2Z J2S SOT−23−5 (Pb−Free) 3000 / Tape & Reel UDFN4 (Pb−Free) 10000 / Tape & Reel SC82AB (Pb−Free) 3000 / Tape & Reel Package Shipping†

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. NOTE: To order other package and voltage variants, please contact your ON Semiconductor sales representative.

http://onsemi.com

15

�NCP4586

PACKAGE DIMENSIONS

UDFN4 1.0x1.0, 0.65P CASE 517BR−01 ISSUE O

D A B L2 DETAIL A

4X

L3

2X 2X

0.05 C

0.05 C 0.05 C

0.05 C

NOTE 4

e

DETAIL A 1 2

D2

45 5 4 3 4X

BOTTOM VIEW

ÉÉ ÉÉ

PIN ONE REFERENCE

c 0.18

typ

E

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS. 3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.20 mm FROM TERMINAL. 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS. DIM A A1 A3 b D D2 E e L L2 L3 MILLIMETERS MIN MAX −−− 0.60 0.00 0.05 0.10 REF 0.20 0.30 1.00 BSC 0.43 0.53 1.00 BSC 0.65 BSC 0.20 0.30 0.27 0.37 0.02 0.12

TOP VIEW (A3) A

3X

0.43

4X

0.23

3X

0.10

SIDE VIEW

A1

C

SEATING PLANE

DETAIL B

e/2

3X

RECOMMENDED MOUNTING FOOTPRINT*

L 0.65 PITCH

DETAIL B 2X

0.52

D2 b 0.05

PACKAGE OUTLINE

1.30

M

CAB

NOTE 3

0.53

4X

0.30

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

http://onsemi.com

16

�NCP4586

PACKAGE DIMENSIONS

SC−82AB CASE 419C−02 ISSUE E

A G D 3 PL N

4 3

C

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. 419C−01 OBSOLETE. NEW STANDARD IS 419C−02. 4. DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. DIM A B C D F G H J K L N S MILLIMETERS MIN MAX 1.8 2.2 1.15 1.35 0.8 1.1 0.2 0.4 0.3 0.5 1.1 1.5 0.0 0.1 0.10 0.26 0.1 −−− 0.05 BSC 0.2 REF 1.8 2.4 INCHES MIN MAX 0.071 0.087 0.045 0.053 0.031 0.043 0.008 0.016 0.012 0.020 0.043 0.059 0.000 0.004 0.004 0.010 0.004 −−− 0.002 BSC 0.008 REF 0.07 0.09

S

1 2

B

K

F L

H J 0.05 (0.002)

SOLDERING FOOTPRINT*

1.30 0.0512

0.65 0.026

0.90 0.035 0.70 0.028

1.90 0.95 0.075 0.037

SCALE 10:1

mm inches

*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

http://onsemi.com

17

�NCP4586

PACKAGE DIMENSIONS

SOT−23 5−LEAD CASE 1212−01 ISSUE A

A A1 L

5X NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSIONS: MILLIMETERS. 3. DATUM C IS THE SEATING PLANE. DIM A A1 A2 b c D E E1 e L L1 MILLIMETERS MIN MAX --1.45 0.00 0.10 1.00 1.30 0.30 0.50 0.10 0.25 2.70 3.10 2.50 3.10 1.50 1.80 0.95 BSC 0.20 --0.45 0.75

A

5 1

D

4 2 3

B

A2 0.05 S

E L1 e

E1 b 0.10

C

M

CB

S

A

S

C

RECOMMENDED SOLDERING FOOTPRINT*

3.30

0.85

5X

0.56

5X

0.95 PITCH

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800−282−9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81−3−5773−3850 ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit For additional information, please contact your local Sales Representative

http://onsemi.com

18

NCP4586/D

�