PE29100

Document Category: Product Specification

UltraCMOS® High-speed FET Driver, 33 MHz

Features

Applications

• DC–DC conversions

• Dead-time control

• AC–DC conversions

LI

FE

• High- and Low-side FET drivers

• Fast propagation delay, 8 ns

• Wireless power

• Tri-state enable mode

• Class D amplifiers

• Sub-nanosecond rise and fall time

• 2A/4A peak source/sink current

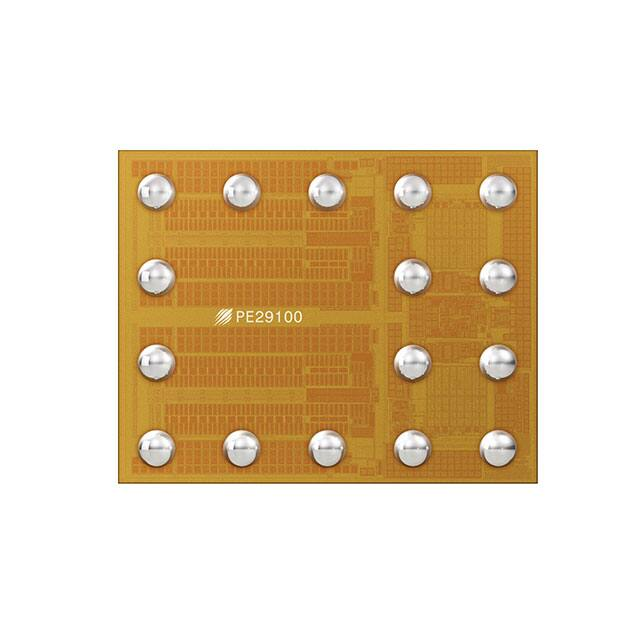

• Package – Flip chip

Product Description

F

The PE29100 integrated high-speed driver is designed to control the gates of external power devices, such as

enhancement mode gallium nitride (eGaN®) FETs. The outputs of the PE29100 are capable of providing

switching transition speeds in the sub-nanosecond range for hard switching applications up to 33 MHz. High

switching speeds result in smaller peripheral components and enable new applications like the Rezence A4WP

wireless power transfer. The PE29100 is available in a flip chip package.

O

The PE29100 is manufactured on Peregrine’s UltraCMOS process, a patented advanced form of silicon-oninsulator (SOI) technology, offering the performance of GaAs with the economy and integration of conventional

CMOS.

Figure 1 • PE29100 Functional Diagram

D

VDD

EN

IN

HSB

UVLO

Dead

Time

Controller

Level

Shifter

Output

Driver

HSGPU

HSGPD

HSS

Logic

LSB

EN

Level

Shifter

RDTL

RDTH

Output

Driver

LSGPU

LSGPD

LSS

GND

LSO

©2015-2017, Peregrine Semiconductor Corporation. All rights reserved. • Headquarters: 9380 Carroll Park Drive, San Diego, CA, 92121

Product Specification

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Absolute Maximum Ratings

Exceeding absolute maximum ratings listed in Table 1 may cause permanent damage. Operation should be

restricted to the limits in Table 2. Operation between operating range maximum and absolute maximum for

extended periods may reduce reliability.

ESD Precautions

Latch-up Immunity

LI

FE

When handling this UltraCMOS device, observe the same precautions as with any other ESD-sensitive devices.

Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to

avoid exceeding the rating specified in Table 1.

Unlike conventional CMOS devices, UltraCMOS devices are immune to latch-up.

Table 1 • Absolute Maximum Ratings for PE29100

Parameter/Condition

Min

Max

Unit

–0.3

6

V

–0.3

6

V

Input signal

–0.3

6

V

HSS to LSS

–1

100

V

25

V

Low-side bias (LSB) to low-side source (LSS)

F

High-side bias (HSB) to high-side source (HSS)

ESD voltage HBM(*), all pins

EN

D

O

Note: * Human body model (MIL-STD 883 Method 3015).

Page 2

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Recommended Operating Conditions

Table 2 lists the recommended operating conditions for the PE29100. Devices should not be operated outside

the recommended operating conditions listed below.

Table 2 • Recommended Operating Conditions for PE29100

Min

Typ

Max

Unit

LI

FE

Parameter

Supply for driver front-end, VDD

Supply for high-side driver, HSB

Supply for low-side driver, LSB

Logic HIGH for control input

Logic LOW for control input

HSS range

Minimum input pulse width

4.0

5.0

5.5

V

3.7

5.0

5.5

V

3.7

5.0

5.5

V

1.6

5.5

V

0

0.5

V

0

80

V

10

Operating temperature

Electrical Specifications

–40

+105

°C

–40

+125

°C

F

Junction temperature

ns

O

Table 3 provides the key electrical specifications @ +25 °C, VDD = 5V, load = 2.2Ω resistor in series with 100 pF

capacitor, HSB and LSB bootstrap diode included, unless otherwise specified.

Table 3 • DC Characteristics

Parameter

DC Characteristics

Min

VDD = 5V

D

VDD quiescent current

Condition

Typ

Max

Unit

3

4.0

mA

HSB quiescent current

VDD = 5V

2.5

3.4

mA

LSB quiescent current

VDD = 5V

2.5

3.4

mA

3.6

4.3

V

EN

Under Voltage Lockout

Under voltage release (rising)

3.1

Under voltage hysteresis

200

mV

HSGPU/LSGPU pull-up resistance

1.2

Ω

HSGPD/LSGPD pull-down resistance

0.5

Ω

Gate Drivers

HSGPU/LSGPU leakage current

HSB–HSGPU = 5.5V/LSB–LSGPU = 5.5V

10

µA

HSGPD/LSGPD leakage current

HSGPD–HSS = 5.5V/LSGPD–HSS = 5.5V

10

µA

Dead-time Control

DOC-66216-5 – (02/2017)

Page 3

www.psemi.com

�PE29100

High-speed FET Driver

Table 3 • DC Characteristics (Cont.)

Parameter

Condition

Min

Typ

Max

Unit

30k to 80 kΩ resistor to GND

1.2

V

Dead-time from HSG going low to

LSG going high

RDHL = 30 kΩ

0.8

ns

RDHL = 80 kΩ

3.4

ns

0.8

ns

3.2

ns

8.4

ns

Dead-time from LSG going low to

HSG going high

LI

FE

Dead-time control voltages

RDLH = 30 kΩ

RDLH = 80 kΩ

Switching Characteristics

LSG turn-off propagation delay

At min dead time

10%–90%

LSG rise time

HSG fall time

LSG fall time

Control Logic

10%–90% with 1000 pF load

2.5

10%–90%

1.0

10%–90% with 1000 pF load

1.8

10%–90%

0.9

10%–90% with 1000 pF load

2.5

10%–90%

0.9

10%–90% with 1000 pF load

1.8

RDHL = RDLH = 80 kΩ

33

O

Max switching frequency @ 50%

duty cycle

1.0

F

HSG rise time

1.2

ns

1.2

ns

1.0

ns

1.0

ns

MHz

Table 4 provides the control logic truth table for the PE29100.

D

Table 4 • Truth Table for PE29100

IN

HSGPU–HSS

HSGPD–HSS

LSGPU–LSS

LSGPD–LSS

L

L

Hi–Z

L

H

Hi–Z

L

H

H

Hi–Z

Hi–Z

L

H

L

Hi–Z

L

Hi–Z

L

H

H

Hi–Z

L

Hi–Z

L

EN

EN

Page 4

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Typical Performance Data

Figure 2–Figure 4 show the typical performance data @ +25 °C, VDD = 5V, load = 2.2Ω resistor in series with

100 pF capacitor, HSB and LSB bootstrap diode included, unless otherwise specified.

VDDA

3.5

3.0

Current (mA)

2.5

2.0

1.5

1.0

0.0

-50

-25

LSB

HSB

F

0.5

LI

FE

Figure 2 • Quiescent Current vs Temperature

0

25

50

75

100

125

EN

D

O

Temperature (°C)

DOC-66216-5 – (02/2017)

Page 5

www.psemi.com

�PE29100

High-speed FET Driver

Figure 3 • UVLO Threshold vs Temperature

UVLO Rising

UVLO Falling

Threshold (V)

3.65

3.60

3.55

3.50

3.45

3.40

-50

-25

0

LI

FE

3.70

25

50

75

100

125

100

125

14

O

Figure 4 • Dead-time vs Temperature

F

Temperature (°C)

TDLH 30K

TDHL 30K

TDLH 80.6K

TDHL 80.6K

TDLH 255K

TDHL 255K

10

8

6

EN

Dead-time (ns)

D

12

4

2

0

-50

-25

0

25

50

75

Temperature (°C)

Page 6

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Test Diagram

Figure 5 • Test Circuit for PE29100

VDD

LI

FE

Figure 5 shows the test circuit used for obtaining measurements. The two bootstrap diodes shown in the

schematic are used for symmetry purposes in characterization. In practice, only the HSB diode is required.

Removing the LSB diode will result in higher low-side supply voltage since the diode drop is eliminated. As a

result, the dead-time resistor can be adjusted to compensate for any changes in propagation delay.

VDD

HSB

UVLO

HSGPU

Level

Shifter

Output

Driver

VIN

HSG

HSGPD

HSS

Dead

Time

Controller

RDTL

RDTH

O

EN

Logic

F

PWM

Level

Shifter

LSB

LSGPU

LSG

Output

Driver

LSGPD

GND

LSO

EN

D

LSS

DOC-66216-5 – (02/2017)

Page 7

www.psemi.com

�PE29100

High-speed FET Driver

Theory of Operation

General

LI

FE

The PE29100 is intended to drive both the high-side (HS) and the low-side (LS) gates of external power FETs,

such as eGaN FETs, for power management applications. The PE29100 favors applications requiring higher

switching speeds due to the reduced parasitic properties of the high resistivity insulating substrate inherent with

Peregrine’s UltraCMOS process.

The driver uses a single-ended pulse width modulation (PWM) input that feeds a dead-time controller, capable

of generating a small and accurate dead-time. The dead-time circuit prevents shoot-through current in the

output stage. The propagation delay of the dead-time controller must be small to meet the fast switching requirements when driving eGaN FETs. The differential outputs of the dead-time controller are then level-shifted from a

low-voltage domain to a high-voltage domain required by the output drivers.

Each of the output drivers includes two separate pull-up and pull-down outputs allowing independent control of

the turn-on and turn-off gate loop resistance. The low impedance output of the drivers improves external power

FETs switching speed and efficiency, and minimizes the effects of the voltage rise time (dv/dt) transients.

Under-voltage Lockout

Dead-time Adjustment

F

An internal under-voltage lockout (UVLO) feature prevents the PE29100 from powering up before input voltage

rises above the UVLO threshold of 3.6V (typ), and 200 mV (typ) of hysteresis is built in to prevent false

triggering of the UVLO circuit. The UVLO must be cleared and the EN pin must be released before the part will

be enabled.

O

The PE29100 features a dead-time adjustment that allows the user to control the timing of the LS and HS gates

to eliminate any large shoot-through currents, which could dramatically reduce the efficiency of the circuit and

potentially damage the eGaN FETs. Two external resistors control the timing of outputs in the dead-time

controller block. The timing waveforms are illustrated in Figure 6.

EN

D

The dead-time resistors only affect the LS output; the HS output will always equal the duty-cycle of the input.

The HS FET gate node will track the duty cycle of the PWM input with a shift in the response, as both rising and

falling edges are shifted in the same direction. The LS FET gate node duty cycle can be controlled with the

dead-time resistors as each resistor will move the rising and falling edges in opposite directions. RDLH will

change the dead-time from low-side gate (LSG) falling to high-side gate (HSG) rising and RDHL will change the

dead-time from HSG falling to LSG rising. Figure 7 shows the resulting dead-time versus the external resistor

values with both HS and LS bias diode/capacitors installed as indicated in Figure 2. The LS bias diode and

capacitor is included for symmetry only and is not required for the part to function. Removing the LS bias diode

will increase the LSG voltage by approximately 0.3V, resulting in a wider separation of the tDHL and tDLH curves in

Figure 7.

Page 8

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Figure 6 and Figure 7 provide the dead-time description for the PE29100.

Figure 6 • Dead-time Description

HSG-HSS

LI

FE

IN

tDLH

LSG-LSS

Figure 7 • Dead-time vs Dead-time Resistor

TDLH

tDHL

TDHL

F

12

O

10

8

6

4

2

D

Dead-time Between HSG & LSG (ns)

14

0

50

100

150

200

250

300

Dead-time Resistance (kΩ)

EN

0

DOC-66216-5 – (02/2017)

Page 9

www.psemi.com

�PE29100

High-speed FET Driver

Application Circuit

LI

FE

Figure 8 shows a typical application diagram of the PE29100 and its external components in a half-bridge

configuration(*). The PE29100 is designed to provide a LS gate driver, referenced to ground, and a floating HS

gate driver referenced to the switch node (HSS). A common technique to generate the floating HS gate drive

uses a bootstrap diode in conjunction with a decoupling capacitor. However, if the LS device conducts currents

through its body diode during the dead-time period, an overvoltage condition across the bootstrap capacitor can

result.

A more elegant approach replaces the HS bootstrap diode with an eGaN FET (Q4). The EPC2038 is used as a

synchronous bootstrap FET to prevent overvoltage of the HS device. The EPC2038 includes an internal diode

and prevents the bootstrap capacitor from overcharging during the dead-time periods. This is accomplished by

synchronously switching Q4 using the LSG signal so that Q4 turns on and charges the bootstrap capacitor when

LSG is high, but turns off as soon as LSG turns low so that no inadvertent bootstrap overcharging occurs during

the dead-time periods.

The external gate resistors are required to de-Q the inductance in the gate loop and dampen any ringing on the

FET gates and the SW node.

Dead-time resistors RDHL and RDLH can be adjusted to compensate for any changes in propagation delay.

EN

D

O

F

Note: * For applications greater than 30V in a half-bridge configuration, the PE29100 can be sensitive to high dv/dt conditions on HSS.

Page 10

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Figure 8 • Applications Diagram for PE29100

VDD

Q4

LI

FE

DGINT

HSB

VDD

UVLO

VIN

HSGPU

Q1

Output

Driver

HSGPD

F

Level

Shifter

HSS

EN

RDTL

VSW

Logic

LSB

O

IN

Dead

Time

Controller

CB

Level

Shifter

LSGPU

Output

Driver

Q5

LSGPD

D

RDTH

LSS

LSO

EN

GND

DOC-66216-5 – (02/2017)

Page 11

www.psemi.com

�PE29100

High-speed FET Driver

Evaluation Board

LI

FE

The PE29100 evaluation board (EVB) was designed to ease customer evaluation of the PE29100 gate driver.

The EVB is assembled with a PE29100 driver and two EPC8009 eGaN FETs in a half-bridge configuration. VDD

is applied at J1 to bias the driver. VIN is applied to the multipin connector, J3, to supply power to the GaN FETs.

A PWM signal with an adjustable duty cycle is applied to J2 as the input. VIN can be monitored at test points E1

and E2, while the DC output can be monitored at test points E3 and E4. The switched output node can be

observed on an oscilloscope at J3.

Because the PE29100 is capable of generating fast switching speeds, the printed circuit board (PCB) layout is a

critical component of the design. The layout should occupy a small area with the power FETs and external

bypass capacitors placed as close as possible to the driver to reduce any resonances associated with the gate

loops, common source and power loop inductances. Since the maximum allowable gate-to-source voltage for

eGaN FETs is 6V, resonance in the gate loops can generate ringing that can degrade the performance and

potentially damage the power devices due to high voltage spikes. Additionally, it is important to keep ground

paths short.

The PCB is fabricated on FR4 material, with a total thickness of 0.062 inches. A minimum copper thickness of 1

ounce or more is recommended on the PCB outer layers to limit resistive losses and improve thermal spreading.

EN

D

O

F

Figure 9 • Evaluation Kit Layout for PE29100

Page 12

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Pin Configuration

Table 5 • Pin Descriptions for PE29100

Figure 10 • Pin Configuration (Bumps Up)

1

HSGPD

2

3

4

5

HSS

HSB

NC

RDLH

6

HSGPU

9

LSGPU

LSGPD

8

IN

10

11

LSO

GND

LSS

LSB

VDD

RDHL

13

14

15

16

Pin

Name

1

HSGPD

2

HSS

High-side source

3

HSB

High-side bias

4

NC

5

RDLH

Dead-time control resistor sets LSG

falling to HSG rising delay (external

resistor to GND)

6

HSGPU

High-side gate drive pull-up

7

EN

Enable active low, tri-state outputs

when high

8

IN

Control input

9

LSGPU

10

LSO

Look ahead for LSGPU. LSO precedes LSGPU and LSGPD by 4 ns.

11

GND

Ground

12

LSGPD

13

LSS

Low-side source

14

LSB

Low-side bias

15

VDD

+5V supply voltage

16

RDHL

Description

High-side gate drive pull-down

No connect (tie to board ground)

Low-side gate drive pull-up

Low-side gate drive pull-down

Dead-time control resistor sets HSG

falling to LSG rising delay (external

resistor to ground)

EN

D

O

F

12

7

EN

Pin No.

LI

FE

This section provides pin information for the

PE29100. Figure 10 shows the pin map of this device

for the available package. Table 5 provides a

description for each pin.

DOC-66216-5 – (02/2017)

Page 13

www.psemi.com

�PE29100

High-speed FET Driver

Die Mechanical Specifications

This section provides the die mechanical specifications for the PE29100.

Table 6 • Die Mechanical Specifications for PE29100

Min

Die size, singulated (x,y)

Typ

Unit

2040 × 1640

Wafer thickness

180

200

Wafer size

Test Condition

Including sapphire,

max tolerance = –20/+30

µm

200

µm

µm

Bump pitch

400

Bump height

85

Bump diameter

110

Pin Name

–800

2

HSS

–400

3

HSB

4

NC

5

RDLH

6

HSGPU

7

EN

1

Y

F

HSGPD

µm

HSGPD

600

600

600

400

600

800

600

–800

200

400

200

D

0

8

IN

800

200

9

LSGPU

–800

–200

10

LSO

400

–200

EN

max tolerance = ±17

11

GND

800

–200

12

LSGPD

–800

–600

13

LSS

–400

–600

14

LSB

0

–600

15

VDD

400

–600

16

RDHL

800

–600

2

3

4

5

HSS

HSB

NC

RDLH

7

8

EN

IN

6

HSGPU

O

1

µm

Figure 11 • Pin Layout for PE29100(1)(2)

Pin Center (µm)

X

µm

9

LSGPU

LSGPD

12

10

11

LSO

GND

LSS

LSB

VDD

RDHL

13

14

15

16

1640 µm (−20 / +30 µm)

Table 7 • Pin Coordinates for PE29100(*)

Pin #

Max

LI

FE

Parameter

2040 µm (−20 / +30 µm)

Notes:

1) Drawings are not drawn to scale.

2) Singulated die size shown, bump side up.

Note: * All pin locations originate from the die center and refer to the

center of the pin.

Page 14

DOC-66216-5 – (02/2017)

www.psemi.com

�PE29100

High-speed FET Driver

Figure 12 • Recommended Land Pattern for PE29100

2.040+0.03

-0.02

1.640+0.03

-0.02

0.20±0.02

Ø0.110±0.017

(x16)

BUMPS DOWN

0.085±0.013

Ø0.090±0.008

(x16)

BUMPS UP

RECOMMENDED LAND PATTERN

EN

D

O

F

SIDE VIEW

0.40

0.22

(x14)

LI

FE

0.40

DOC-66216-5 – (02/2017)

Page 15

www.psemi.com

�PE29100

High-speed FET Driver

Ordering Information

Table 8 lists the available ordering code for the PE29100.

Table 8 • Order Code for PE29100

Description

PE29100 flip chip

PE29100A-Z

PE29100 flip chip

Advance Information

Die on tape and reel

500 units/T&R

Die on tape and reel

3000 units/T&R

O

Document Categories

Shipping Method

F

PE29100A-X

Packaging

LI

FE

Order Codes

The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and

features may change in any manner without notice.

Preliminary Specification

D

The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any

time without notice in order to supply the best possible product.

Product Specification

The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended

changes by issuing a CNF (Customer Notification Form).

EN

Sales Contact

For additional information, contact Sales at sales@psemi.com.

Disclaimers

The information in this document is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be

entirely at the user’s own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party.

Peregrine’s products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to

support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death

might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in

such applications.

Patent Statement

Peregrine products are protected under one or more of the following U.S. patents: patents.psemi.com

Copyright and Trademark

©2015-2017, Peregrine Semiconductor Corporation. All rights reserved. The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

Product Specification

www.psemi.com

DOC-66216-5 – (02/2017)

�