PLC810PG HiperPLC™ Family

Continuous Mode PFC & LLC Controller with Integrated Half-bridge Drivers

Product Highlights

Features • Highly integrated, eliminates external components • Frequency and phase synchronized PFC and LLC • Reduced noise and EMI • Ripple current reduction in PFC output capacitor • Edge collision-avoidance simplifies layout • Comprehensive PFC and LLC fault handling and current limiting • Proprietary continuous conduction mode PFC for high efficiency with low component cost • High efficiency Zero Voltage Switching (ZVS) LLC • Off-time PFC control eliminates AC input sensing components • Configurable, precise dead time control and frequency limit • Prevents hard MOSFET switching • Tight LLC duty cycle symmetry for balanced O/P diode currents • Lead and halogen free Green package Applications • 32” to 60” LCD TV power supplies • Off-line 150 W to 600 W efficiency-optimized power supplies • LED street lighting Description The PLC810PG is a combined PFC and LLC off-line controller with integrated high voltage half-bridge drivers. Figure 1 shows a simplified schematic of a PLC810PG based power supply where the LLC resonant inductor is integrated into the transformer. The PFC section of the PLC810PG is a universal input continuous current mode (CCM) design that does not require a sinusoidal input reference, thereby reducing system cost and external components. The DC-DC controller drives an LLC resonant topology. This variable frequency controller provides high efficiency by switching the power MOSFETs at zero voltage, eliminating most switching losses. The LLC controller is built around a current controlled oscillator with a control range selected to support the traditional frequency of operation found in televisions. To ensure zero voltage switching, the dead time of the LLC switching in the PLC810PG is tightly toleranced and can be adjusted with an external resistor. The highside/lowside duty cycle is also closely matched to provide balanced output currents reducing output diode cost. A typical PLC810PG LLC design operates at 100 kHz (under nominal conditions). Depending on the LLC circuit design, the switching frequency can vary from half to three times the nominal operating frequency as a result of line and load changes. The PFC converter is frequency locked to the LLC to minimize noise and electromagnetic interference. Increasing the PFC frequency in synchronization with the LLC at light loads reduces the current at which the PFC boost converter

Standby Supply AC IN

VCCHB

GATEH HB

VCCL VCC ISP FBP PFC Gate Driver GATEP GATEL ISL VREF

+

DC OUT

PLC810PG

VCOMP

FMAX FBL LLC Feedback Circuit

GNDP GND Link Figure 1. Typical Application Circuit – LCD TV Power Supply. August 2009 GNDL

PI-5044a-121708

www.powerint.com

�PLC810PG

becomes discontinuous improving light load operation and reducing power line harmonics. PFC and LLC primary side fault management is provided. The phase of the PFC PWM output is dynamically adjusted relative to the LLC phase such that the switching edges do not coincide with noise sensitive events in the PWM and LLC timing circuits. This edge-collision avoidance technology simplifies power supply layout and improves performance. Phase synchronization reduces EMI spectral components and reduces ripple current in the PFC capacitor.

2

Rev. F 08/09

www.powerint.com

�PLC810PG

Pin Description

VCC Pins VCC VCC powers the small signal analog circuitry inside the IC. A bypass capacitor must be connected from the VCC pin to the GND pin. This capacitor needs to be a 10 mF ceramic capacitor, or a parallel combination of a 10 mF electrolytic capacitor and a 0.1 mF ceramic capacitor. VCCL VCCL is the supply pin for the LLC low side driver. It powers only the LLC low side MOSFET driver and the communications circuitry between the analog circuitry and the LLC drivers. A 1 mF ceramic bypass capacitor must be connected from the VCCL pin to the GNDL pin. This capacitor provides the instantaneous current for turning on the gate of the LLC low-side MOSFET. VCCHB VCCHB is the floating supply pin for the LLC high-side driver, which is referenced to the HB pin. The HB pin is in turn connected to the LLC MOSFET half-bridge center point. A 1 mF ceramic bypass capacitor must be connected from the VCCHB pin to the HB pin. This capacitor provides the instantaneous current for turning on the gate of the high side LLC MOSFET. In a typical application, VCC is connected to the standby supply. VCCL should be connected to the VCC pin through a 5 W resistor for noise immunity. VCCHB is connected to the standby supply through a series combination of a high voltage diode and a 5 W resistor. This diode plus resistor combination charges the 1 mF decoupling capacitor whenever the LLC lowside MOSFET is on. The resistor limits the peak instantaneous charging current. See R42 and D8 in Figure 4. GND Pins GND GND is the return node for all analog small signals. All small signal pin bypass capacitors must be connected to this pin via short traces. This pin must have a single point connection, via a dedicated trace to the PFC current sense resistor, which in turn must be placed close to the PFC MOSFET. It must not be connected to any other point in the PFC/LLC power train. The VCC bypass capacitor must also be connected to this pin. GNDP GNDP is the return for the PFC gate drive signal only. This pin must be connected on the PCB directly to the GND pin. GNDL GNDL is the return for the LLC low side gate driver only. This pin must be connected to the LLC low side MOSFET Source pin, with a dedicated trace, and a small ferrite bead. This pin must be connected to the GND pin via a 1 W resistor for noise immunity. The VCCL bypass capacitor must also be returned to this pin. Other Pins HB Half-bridge pin. This pin is the return of the LLC high side MOSFET driver. It must be connected to the center of the halfbridge formed by the LLC MOSFETs. The VCCHB bypass capacitor must also be returned to this pin. ISP Current sense, PFC. It is for sensing the negative voltage on the current sense resistor (which describes PFC inductor current). This sense resistor is connected between PFC MOSFET Source and Bridge ‘-’ terminal. The signal must pass through an RC low-pass filter with a time constant between 100 and 200 ns. The resistor must be no greater than 150 W due to internal offset current requirements for the ISP pin. The average inductor current (measured over several switching cycles) is used for the PFC control algorithm. This pin also Implements pulse-by-pulse current limiting. ISL Current sense, LLC. This pin is for sensing transformer primary current, to detect LLC overload. It should be connected to the current sense resistor, which is connected between the LLC low side MOSFET Source pin and the bottom side of the transformer primary. The signal must pass through an RC low-pass filter with a time constant between 200 ns and 1 ms. The capacitor in the low-pass filter must be connected to the GND pin. The current limit has 2 levels, a lower, slow current limit for output overload, and a higher, fast current limit for component failure protection. The series resistor in the low-pass filter should be 1 k W or greater to limit current into the ISL pin. GATEP Gate drive output signal for the PFC MOSFET gate drive circuit. GATEL Gate drive for the low side LLC MOSFET. GATEH Gate drive for the high side LLC MOSFET. VREF 3.3 V reference pin for the LLC feedback circuitry. A 1 mF ceramic decoupling capacitor must be connected from the VREF pin to the GND pin. FBP The Feedback PFC pin is connected to the external resistor divider that senses PFC output voltage. This is a non-inverting input to a transconductance amplifier. The transconductance amplifier output is connected to the VCOMP pin, to which the feedback compensation is also connected. A 10 nF decoupling capacitor must be connected from the FBP pin to the GND pin. VCOMP This pin is the connection point for PFC feedback loop components. The voltage on this pin is used as an input to the PFC controller multiplier. The linear voltage range for this pin is nominally 0.5 V to 2.5 V, where higher voltage signifies less power. FBL LLC Feedback pin. Current entering this pin determines LLC switching frequency. It has a Thevenin equivalent circuit of nominally 0.65 V and 3.3 k W. FBL must be decoupled to the GND pin with a 1 nF capacitor. Note that this capacitor forms a pole with the input resistance.

3

www.powerint.com

Rev. F 08/09

�PLC810PG

FMAX This pin is for programming maximum LLC frequency with a resistor to VREF. If the frequency commanded by the FBL pin current exceeds 95% of the programmed maximum frequency, the LLC high and low side drivers turn both LLC MOSFETs off. This pin must be decoupled to the GND pin with a 1 nF capacitor. RSVD1, RSVD2, and RSVD3 RSVD1 must be connected to VREF. RSVD2 and RSVD3 must be connected to the GND pin.

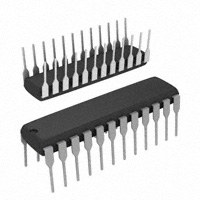

VCOMP GND ISP VREF RSVD1 GATEP VCC GNDP GNDL GATEL NC GATEH

1 2 3 4 5 6 7 8 9 10 11 12

24 23 22 21 20 19 18 17 16 15 14 13

NC FBP ISL FMAX FBL GND RSVD3 RSVD2 VCCL NC HB VCCHB

PI-5040-012709

Figure 2.

Pin Numbering and Designation (Top View).

4

Rev. F 08/09

www.powerint.com

�PLC810PG

ISP (3) VCOMP (1) FBP (23)

INVERSION

PFC FAULT

DVGA and LPF

+

OTA VFBPREF + -

VOVH VIN(H)/VIN(L) GND (2,19) VSD(H)VSD(L)

+ -

+ -

VREF SOFT ONE SHOT 4096 START CYCLES (13) VCCHB OVL FAULT RAMP AND CLOCK GENERATOR DEAD TIME GENERATOR NONOVERLAP GENERATOR

FBL (20) FMAX (21)

LLC CURRENT FEEDBACK

ISL (22) VISL(F)VISL(S)

Figure 3.

Block Diagram of PLC810PG. Reserved Pins are not Shown.

Block Diagram

Figure 3 shows a block diagram of the functional elements that make up the PLC810PG. The reserved pins are not shown in the diagram. Those pins are reserved for PI use during manufacture and testing. The PLC810PG PFC control blocks and circuits are shown on the upper half of the block diagram, while the LLC control blocks are shown on the lower half. Some of the functional blocks are shared. PLC810PG Power Block The PLC810PG is powered through VCC and VCCL pins. The VCCL pin powers the LLC driver while VCC powers the rest of the device. VCC pin must be supplied by a voltage between VUVLO(+)

www.powerint.com

+

-

VOC

OC FAULT

LLC CLOCK PWM

PHASE ALIGNMENT (6) GATEP (7) VCC

OV FAULT

UVLO

RESET

+

PFC INHIBIT INTERNAL REFERENCE GENERATOR LLC OFF

-

VUVLO(+) VUVLO(-)

(8) GNDP

3.3 V LINEAR REGULATOR

(4) VREF

(12) GATEH (14) HB (16) VCCL

+

(10) GATEL CLAMP (9) GNDL LLC FAULT

1.2 V

-

+ -

CLAMP LLC OFF OVL FAULT

PI-5041-112608

and 15 V. The provided supply is continuously compared against the VUVLO(+) and VUVLO(-) thresholds to start/stop the PLC810PG. When VCC is above the VUVLO(+) threshold the PLC810PG deasserts the undervoltage lockout (UVLO) signal allowing the device to start. If VCC falls below VUVLO(-), the UVLO signal is asserted, shutting down the PLC810PG. The VCCL pin powers the LLC driver, and VCCHB provides the charge for the LLC high-side MOSFET for gate drive. An internal linear regulator is used to generate a 3.3 V rail to power the low voltage circuits inside the PLC810PG. The 3.3 V is brought outside on the VREF pin allowing external low voltage circuits to be powered by the PLC810PG.

5

Rev. F 08/09

�PLC810PG

PLC810PG PFC Control Block The PLC810PG PFC is a boost converter which conditions the average input current to make it (typically) sinusoidal and in phase with the input voltage. In normal operation the PFC operates in continuous conduction mode (CCM). Under light load, depending on the PFC inductor value, the converter may enter a discontinuous conduction mode (DCM). The PLC810PG PFC controller does not need to sense the input voltage. The PLC810PG PFC controller exploits the fact that the input voltage (VIN) is effectively constant over a few adjacent switching cycles, because the input is changing at 60 Hz while the switching frequency is 1500 times higher. Using the average input voltage and output voltage values, the off-time for the boost converter is: The voltage developed across the PFC current sense resistor and applied to the ISP pin is compared against an overcurrent threshold (which has built in hysteresis). This implements a pulse-by-pulse current limit to protect the PFC MOSFET against overcurrent. The ISP pin voltage is also averaged (over several switching cycles), and used as an input to the PFC multiplier. The Discrete Variable Gain Amplifier, DVGA/LPF block is responsible for averaging the ISP pin voltage (over several switching cycles) and implementing a multiplier as part of the PFC control loop, under control of the VCOMP signal. Using the feedback voltage on FBP, PFC and LLC circuit protection is provided: • PFC overvoltage protection: The feedback voltage on the FBP pin is compared against an overvoltage threshold (VOV(H)). If the voltage at the FBP pin is greater than VOV(H), the PFC MOSFET gate signal is turned OFF immediately, and held off for at least one cycle. When FBP drops below VOV(H), PFC switching recommences. • Minimum boost voltage detection: The feedback voltage on FBP is compared against a minimum boost voltage threshold (VIN(H)/VIN(L)). The PFC is inhibited if the FBP voltage is below VIN(L). The gate of the PFC MOSFET is driven via GATEP if the FBP voltage is above VIN(H)). This is done to prevent PFC startup in brownout or during AC failure conditions. • Minimum boost voltage for LLC startup: The feedback voltage on FBP is compared against an LLC shutdown voltage threshold (VSD(H))/ VSD(L)). This inhibits LLC startup until the PFC output voltage is close to regulation. The purpose of VSD(L) is to shutdown the LLC when the PFC output voltage is low (~64% of nominal), which may occur during AC dropout, shutdown, or overload conditions. • PFC open-loop protection: The FBP pin includes a highimpedance (5 MW) pull-down resistor to protect against a floating FBP pin resulting in an open-loop condition. PLC810 LLC Control Block The PLC810PG LLC controller supports half-bridge topologies. The LLC circuit relies on two switches in a half-bridge topology driving a resonant tank (LLC) and power transformer. The LLC circuit has two resonant frequencies: the series resonant frequency and the parallel resonant frequency. Typically, an LLC converter is designed to operate at a switching frequency which is slightly higher than the series resonant frequency when at nominal input voltage. In this operating region, the MOSFET switching can be performed at zero voltage, reducing the switching losses. In the normal mode of operation, the LLC controller will vary its switching frequency around a narrow range of frequencies to regulate the output voltage. Feedback and Maximum Frequency Limit The PLC810PG LLC controller has nominal operating frequency of 100 kHz. For voltage regulation, with input voltage and load variations, the operating frequency will vary and may exceed 250 kHz. The maximum frequency set by the resistor on FMAX pin is typically chosen to be two to three times the nominal operating frequency. The appropriate maximum frequency is set

DOFF = ]1 - D g =

VIN VO

The input current is the same as the inductor current (sensed current), thus from the previous equation, it can be deduced that:

V VIN = DOFF # O ISENSE I IN

In order to make the input impedance look resistive, the input current must be proportional to the input voltage:

VIN = RE IN

Thus, Doff has to be controlled by:

DOFF = c

RE m # ISENSE VO

If (DOFF) changes slowly with the input voltage, the average current will be in-phase with the input voltage. The PLC810PG PFC block controls the PFC off-time (DOFF = (1–D)). The output voltage needs to be regulated and RE needs to be adjusted as a function of the load and the input voltage. The PLC810PG PFC has two inputs:

• •

The feed-back PFC output voltage is reduced by a resistor divider and sensed and via the FBP pin. The instantaneous inductor current, sensed via the ISP pin.

The PFC output voltage is sensed at the FBP pin through an external resistive divider so that the desired DC boost voltage (typically 385 V) is reduced to match the internally generated VFBPREF (2.2 V) reference voltage. The FBP input pin and the VFBPREF voltage are inputs to an operational transconductance amplifier (OTA). The output of the OTA drives the VCOMP pin, allowing external compensation of the low frequency voltage loop. The purpose of the phase alignment block is to set the edges of the PFC MOSFET gate drive signal to avoid the LLC converter switching edges. This eliminates switching-noise coupling between LLC and PFC circuits. The compensation components are connected between VCOMP and the analog ground pin (GND). The VCOMP pin is used to apply compensation to the low frequency voltage loop. 6

Rev. F 08/09

www.powerint.com

�PLC810PG

using a resistor connected between the VREF pin and the FMAX pin using the curve in Figure 15. The resistor on the FMAX pin also sets the LLC dead time interval (see Figure 14). The FBL pin provides output voltage regulation. As such the current entering this pin modulates the switching frequency. More current forces a higher switching frequency. The FMAX pin sets an upper limit for the switching frequency to ensure zero voltage switching. Minimum switching frequency is determined by the adjusting minimum bias applied to the FBL pin. If the external feedback circuit attempts to push the LLC controller to a frequency equal to or higher than the maximum frequency limit set by the resistor at FMAX pin, the LLC MOSFET gate driver outputs are turned off until the current into the FBL pin drops below the FMAX pin current. The gate outputs are turned off synchronously with the clock for whole cycles. LLC Soft Start The LLC controller implements a soft start to prevent excessive currents during startup, and to prevent overshoot on the output when the feedback loop comes into operation. The soft start time is determined by external components on the FBL pin. In the event of an LLC fault turning off the LLC circuit, the external circuit is allowed to discharge, initiating a new soft start. When the soft start signal is asserted, the FBL pin is pulled up to VREF (3.3 V), keeping the current applied to the FBL pin to maximum. During the soft start cycle, the LLC outputs turn on and the switching frequency slowly decays from its maximum to the nominal operating point. LLC Overcurrent Detection (ISL Pin) Overcurrent in the LLC converter is detected via a sense resistor in series with the low side of the transformer’s primary winding. When the overcurrent condition is detected, the LLC MOSFETS are turned OFF. The overcurrent detection has two thresholds; fast overcurrent threshold (VISL(F)) and slow overcurrent threshold (VISL(S)). The fast overcurrent threshold is triggered by abnormally high current. The LLC is shutdown immediately if the pulse on the ISL pin exceeds this threshold. The slow overcurrent threshold is lower than the fast overcurrent threshold. The slow overcurrent response is triggered and the LLC is shutdown if the ISL pin voltage exceeds this threshold for eight consecutive clock cycles. Typically the (VISL(F)) threshold is used to detect catastrophic failures such as shorted components, while the slow VISL(S) threshold is used to detect overload conditions. This overcurrent detection circuit prevents the LLC converter from operating in the capacitive region of the LLC, thus avoiding failure of the converter components from overheating. Other LLC Control Blocks The non-overlap (dead time) generator creates two nonoverlapping signals with equal on-times to drive the LLC MOSFETS. The drive signal for the two LLC MOSFETS is symmetrical with a 50% duty cycle. The dead time block is used both by the PFC and LLC to control the dead time of the switching function. The dead time in the PLC810PG is configurable via the FMAX pin. The dead time allows zero voltage switching, reducing the body diode losses in the switching MOSFETs and minimizing the reverse recovery time of the body diodes. Start-up Once the VCC voltages reach the startup voltage (VUVLO(+)), the PLC810PG starts switching the PFC MOSFET and the PFC output ramps to its nominal value. When the PFC boost voltage (sensed through FBP pin) raises the FBP pin voltage above the LLC start threshold (VSD(H)), the LLC circuit is enabled and the LLC soft start begins.

7

www.powerint.com

Rev. F 08/09

�Figure 4.

8

T2 13 Bead 3 Ferrite Bead D9A 16CTT100 C37 1800 µF 35 V TP18 7,8 R42 10 Ω U6 PLC810PG 13 VCCHB GATEP ISP FBP ISL 22 VCCL 16 VREF 4 RSVD1 5 FMAX 21 FBL VCC 7 GNDL GNDP 8 R54 1.8 kΩ D16 LL4148 C36 1 nF 200 V C31 1 µF 25 V 9 U7B LTV817A R53 19.1 kΩ 1% R59 0.1 Ω 2W 20 R52 19.1 kΩ 1% C27 1 µF D9B 6 14 R47 1 kΩ D18 LL4148 C53 1800 µF 35 V C40 100 nF 630 V GATEL 10 R58 10 Ω Q11 IRFIB5N50 LPBF HB 14 5 L6 Ferrite Bead (3.5 × 4.45 mm) 9,10 D17 LL4148 GATEH 6 3 23 1 VCOMP C28 22 nF 200 V 17 RSVD2 RSVD3 GND GND 18 2 19 R49 51.1 kΩ R51 1% 22.1 kΩ 1% 11 NC 15 NC 24 NC D10B 16CTT100 L8 3.3 µH R56 10 Ω C39 TP26 22 nF 1250 V Q10 IRFIB5N50 LPBF GATEL 11,12 TP21 12 V J3-9,10 VR7 2MM5245B-7 15 V VR6 2MM5256B-7 30 V C23 1 µF 25 V 12 R37 4.7 Ω R38 4.7 Ω D10A C38 1800 µF 35 V 24 V J3-1,2,3 D13 LL4148 C52 100 µF 35 V D12 LL4148 R62 3.9 kΩ R63 1 kΩ C45 22 nF 200 V TP24 5 V Main J4-1 Q12 SI4408DY Q13 MMBT3906 R69 10 kΩ R70 10 kΩ R71 100 Ω R60 100 Ω C44 10 µF 25 V Q14 MMBT3906 Q15 MMBT3904 C43 R61 10 µF 10 kΩ 25 V L7 Ferrite Bead (3.5 × 4.45 mm) D11 LL4148 C32 C29 100 nF 10 µF 50 V 50 V C33 1 µF 25 V C30 C34 C35 1 nF 1 nF 1 nF 200 V 200 V 200 V C49 10 nF 200 V OVP U7A LTV817A R72 1 kΩ R65 1 kΩ R64 C46 2.2 nF 162 kΩ 200 V 1% C47 22 nF 200 V R67 470 kΩ R73 10 kΩ C50 220 nF C48 1 µF 50 V U8 LM431AIM R66 82.5 kΩ

Rev. F 08/09

1%

R74 10 kΩ TP27 R68 10 kΩ TP20 TP23 R55 1Ω

PLC810PG

B+

VCC

R39 768 kΩ 1%

R40 768 kΩ 1%

D8 UF4005

R43 768 kΩ 1%

R41 768 kΩ 1%

GATEP

R44 10 Ω

R46 768 kΩ 1%

ISP

R45 150 Ω

C24 1 nF 200 V

R50 22.1 kΩ 1%

C25 10 nF 200 V

R48 2.2 kΩ 1/8 W

Controller GND

C26 10 µF 50 V

Q16 2N3906

PLC810PG LCD TV Power Supply Application Circuit, PFC Circuit Control Inputs and LLC Stage.

1%

R57 10 Ω

PI-5275-061109

5 V_STBY

B-

RTN J3-4,5,6,7,8

www.powerint.com

�PLC810PG

RL1 TP1 L C1 330 pF 250 VAC E C5 330 pF 250 VAC TP3 N RT1 5Ω RV1 320 VAC C3 470 pF 275 VAC

VCC D14-15 1N4007 R1 680 kΩ C4 470 nF 275 VAC R2 680 kΩ R3 680 kΩ C6 330 pF 250 VAC C2 330 pF 250 VAC BR1 GBJ806-F 600 V

F1 5A

B-

t

O

TP2 Brownout Bridge + C7 1 µF 630 V Bridge -

L1 10 mH

L2 10 mH

L3 29 uH

Bridge +

L4 480 µH

D2 STTH8S06D

D1 1N5406

TP4 B+

VCC GATEP

R4 0Ω Q1 FMMT491 C10 1 µF 25 V R7 2.2 Ω Bead 2 Ferrite Bead Q3 FMMT591 R8 0.11 Ω 2W R6 0.11 Ω 2W R9 4.7 kΩ

Bead 1 Ferrite Bead C11 20 nF 500 V C9 220 µF 450 V

Controller GND

D3 1N4007

D4 DL4007

Q2 SPP21N 50C3IN

ISP

Bridge -

BPI-5186-012909

Figure 5.

PLC810PG LCD TV Power Supply Application Circuit, Input Circuit and PFC Power Stage.

B+ R10 220 kΩ 1/2 W C13 20 nF 500 V C12 1 nF 1 kV VR1 P6KE 150A

1

T1

9, 10

D6 SB540 C14 2200 µF 10 V

L5 3.3 µH C15 220 µF 25 V

TP5

5V Standby J4-4

2 NC 6, 7 D7 UF4003 C16 470 µF 35 V

TP6 RTN J4-2,3

D5 UF4007

3

4

R27 33 Ω U3A PC817X4J 5V OVP R33 1 kΩ

R13 470 Ω 5V Regulation U5 LM431AIM 2% C18 R17 1 kΩ 100 nF 50 V R18 10.2 kΩ 1%

TP28 EE25 R12 22 kΩ

5

U1B LTV817A Q4 BST52TA VCC R14 22 kΩ

Remote On/Off R15 330 kΩ

5V OVP U2B LTV817A

U2A LTV817A VR5 ZMM5231B-7 5.1 V C19 10 µF 50 V U1A LTV817A

R11 4.7 MΩ 1/2 W

SW1 Remote On/Off

C51 100 pF 200 V C17 1 µF 25 V VR2 ZMM5245B-7 15 V R20 220 kΩ Q5 MMBT 3906

R16 22 kΩ

D

Remote On/Off

EN BP

R23 10 kΩ 1% OVP

TinySwitch-III U4 TNY275PN

S

R19 1.3 MΩ Q8 MMBT3904

R31 2.2 kΩ Standby R36 1 kΩ R34 3.9 kΩ

PI-5187-061109

VR3 ZMM5232B-7 5.6 V Q6 MMBT3904 R21 100 kΩ R25 3.9 MΩ VR4 ZMM5204B-7 10 V Q7 MMBT3904 C22 100 nF 50 V R26 100 kΩ

R22 470 Ω 5V Regulation C20 100 nF 50 V U3B PC817X4J

TP7

Brownout R28 620 kΩ GATEL

R29 680 kΩ R30 680 kΩ

R24 226 kΩ 1%

C21 1 nF 200 V

Q9 MMBT3904 R35 10 kΩ

R32 10 kΩ

B-

C42 1 nF 250 VAC

Figure 6.

PLC810PG LCD TV Power Supply Application Circuit, Standby Supply.

9

www.powerint.com

Rev. F 08/09

�PLC810PG

Applications Example

Circuit Description Figures 4, 5, and 6 show the schematic of a typical 280 W LCD T V power supply application using HiperPLC and TinySwitch-III. The PSU contains PFC + LLC stage using a PLC810PG which provides the high power outputs, plus a standby power supply using a TNY275PN. The design has 4 outputs: 12 V and 24 V, 5 V main and 5 V standby. The 5 V main and 5 V standby are provided by the TinySwitch-III flyback circuit. See the Typical Application section of the TinySwitch-III data sheet found on the Power Integrations website for a description of a TinySwitch-III flyback converter. The PSU has a standby input signal, which enables the main converter (PLC810PG). EMI Filtering and Rectification Capacitors C42, C1, C5, C3, C4, C2, C6 and common mode chokes L1 and L2 perform EMI filtering. Diode bridge BR1 rectifies the input AC with D14 and D15 providing a separate full-wave rectified signal for the brownout circuit. Inrush Limiting Thermistor RT1 provides inrush limiting. It is bypassed by a relay (RL1) which is driven by the power supply remote-on signal. The use of a relay increases efficiency by approximately 1%. Diode D3 provides an inrush path to the bulk capacitor C9 that bypasses the PFC inductor L4 to prevent it from saturating. PFC Stage The main PFC inductor L4, MOSFET Q2, boost diode D2, and bulk cap C9, form a PFC boost converter. Capacitor C8 and R5 damp reverse recovery ringing on D2. Inductor L4 uses a small low cost Sendust core. Two key advantages of this continuous mode PFC design are that the low ripple current allows the use of: 1. High BSAT material (such as low-cost Sendust), allowing fewer turns which saves copper cost and reduces size. 2. Low-cost magnet wire rather than Litz wire. Diode D2 is a low-cost silicon ultrafast PFC boost diode. Components Q1, Q3, C10 and R7 form the gate drive circuit. See description under “Recommended PFC Gate Drive Circuit“. PFC Current sense resistors R6 and R8 are clamped by D3 and D4 to protect the current sense input of the controller IC during inrush. Capacitor C11 is positioned close to the PFC MOSFET and diode to limit the size of the high frequency loop around components Q2, D2 and C9. This reduces EMI. Low-loss film capacitor C7 functions as the input capacitance to the PFC boost converter, and also filters EMI. LLC Stage LLC Input Stage MOSFETs Q10 and Q11 form the LLC half-bridge. They are driven directly by the PLC810 via gate resistors R56 and R58. Capacitor C39 is the primary resonating capacitor, and should be a low-loss type rated to tolerate the highest RMS current seen at maximum load. Transformer T2 has a large built-in leakage inductance which acts with C39 to form the series resonant tank. Capacitor C40 is used for local bypassing, and is located directly adjacent to Q10 and Q11. Resistor R59 provides primary current sensing to the controller for overload protection. LLC Outputs The secondary ouputs of transformer T2 are rectified and filtered by D9, D10, C38, C39 and C53 to provide the +12 and +24 V outputs. Switched +5 V Main Output MOSFET Q12 is used to switch the output of the +5 V logic supply. The AC signal from one side of the 12 V output rectifier is used to drive Q12 via R60, R61, D11, and C43. Capacitor C44 provides filtering near the output connection. Bias Regulator / Remote On/Off and Brownout Shutdown Circuit Components Q4, U1, C17, and associated components constitute the bias regulator and provide the remote on-off function. Darlington transistor Q4, R14, and VR2 form a simple emitter follower voltage regulator that is switched via optocoupler U1. Capacitor C17 limits the rate of rise of the bias voltage. Transistor Q5 and R20 quickly discharge C17 when optocoupler U1 is turned off. On the secondary, optocoupler U1 is turned on via Q8 when the standby signal is high. This turns on the PFC LLC stages. A brownout shutdown circuit is provided to actively shutdown the PSU when the output turns off due to a brownout condition. This circuit operates by sensing the AC input voltage together with the presence of the GATEL signal from the LLC controller. During a brownout condition, the PFC output voltage will drop until the VFB pin voltage drops to INH, turning off the LLC stage. If at this point the AC voltage is below 82 VAC, the brownout circuit will turn off the PLC810 via the bias regulator, preventing the PFC from charging up the bulk capacitor again, restarting the LLC, and repeating the cycle (and creating output voltage glitches). Resistor R24, R26, R28-30, C21, VR4, and Q7 are used to sense the AC input voltage. The voltage threshold of this circuit is set below the turn-on threshold of the standby/primary bias converter. Sufficient AC voltage turns on Q7, discharging capacitor C22, which is charged via R15. Components R32, R35, and Q9 sense the switching GATEL signal. Transistor Q9 discharges capacitor C22 when the switching signal is present.

10

Rev. F 08/09

www.powerint.com

�PLC810PG

When the AC input voltage is low, Q7 and Q9 turn off, allowing C22 to charge. Transistor Q6, R21, and VR3 sense the voltage on C22. When C22 has charged sufficiently, Q6 turns on, turning off the primary bias supply via Q5, shutting down the PLC810 and thus the PFC and LLC stages. Controller Figure 4 shows the circuitry around the U13 main controller IC, which provides control functions for the input PFC and output LLC stages. PFC Control The PFC boost stage output voltage is fed back to the FBP pin of the PLC810PG via resistors R39-41, R43, R46, and R50. A 10 nF capacitor (C25) filters noise. Capacitor C26, C28 and R48 provide frequency compensation for the PFC. The PFC current sense signal from resistors R6 and R8 is filtered by R45 and C24. The PFC drive signal is routed to the main switching MOSFET via resistor R44, which damps any ringing in the PFC drive signal caused by the trace length from the PLC810PG to the PFC gate drive circuitry. Bypassing/Ground Isolation See “GND Pins” and “VCC Pins” under the section “Pin Description”. Capacitors C29 and C32 provide decoupling for the VCC pin. Capacitor C31 provides decoupling for the VCCL pin. Resistor R37 is an optional resistor that provides additional filtering for the VCC pin. This will help reject any noise picked up by long VCC traces from the standby supply. Capacitors C24, C25, C32, C29, C30, C31, C33, C34, C35 must be connected to the correct ground pins, and be connected with short traces to the PLC810PG. See section “Pin Description”. Resistor R55 separates the GND and GNDL pins. Together with ferrite bead L7, it provides high frequency isolation between GND and GNDL pins. The GATEL output gate drive for the lowside LLC MOSFET Q11 returns to GNDL through ferrite bead L7. The GATEH output gate drive for the high-side LLC MOSFET Q10 returns to HB through ferrite bead L6. This bead is optional, but provides symmetry with L7. LLC Control Feedback from the LLC output sense/error amplifiers circuits is provided by optocoupler U7. Resistor R54 is the optocoupler load. Diode D16 allows the optocoupler to pull up on the LLC feedback pin (FBL) only. See “LLC Controller section” for the description of the functions performed by of R54, C36, R53, R51, R49, and C27. The LLC current sense signal from resistor R59 is filtered by R47 and C35. Capacitor C23, R42, and D8 provide the booststrap supply for the LLC high side MOSFET driver. See “GND Pins” and “VCC Pins” under the section “Pin Description”. LLC Secondary Control Circuits Figure 4 shows the secondary control schematic for the LLC stage. Voltage Feedback The LLC converter 12 V and 24 V outputs are sensed, weighted, and summed by resistors R64, R66, and R68. Resistor R62 is the main gain-setting resistor. Resistor R63 and C45 form a phase-lead compensator which extends the feedback loop’s crossover frequency and increases the phase margin. Resistor R67, C46 and C47, in conjunction with R68 set the lowfrequency compensation. Capacitor C48 is a “soft finish” capacitor that reduces output overshoot at start up, by conducting during the output rise time. It does not affect the main feedback loop characteristics. OVP Zener diodes VR6-7 and D12, D13 sense any overvoltage condition in the 12 V or 24 V outputs. An overvoltage signal from either output is used to trigger a bipolar latch (Q14, Q15, R70, R73), which turns on transistor Q13. This transistor is used to deactivate the remote on-circuit which turns off the primary bias, and hence the PLC810PG.

Power Supply Block Functions and Key Design Details

PFC Control Section The PFC controller uses continuous conduction mode, with an off-duty-cycle control algorithm. This approach removes the requirement for input AC voltage sensing. The off-time is proportional to the product of the average inductor current (averaged over several switching cycles), and the error amp output. This automatically shapes the average input current, to the same shape as the input AC voltage. The PLC810PG PFC circuit is frequency and phase locked to the LLC circuit. PLC810PG employs collision avoidance technology, where the PFC edges straddle those of the LLC so that simultaneous edge transitions in both the PFC and LLC sections are prevented. This reduces interference between PFC and the LLC circuits. The PFC section has 2 input pins: a current sense input (ISP pin), and a voltage feedback input (FBP pin). There are 2 output pins. A VCOMP pin for placing the feedback compensation components, and a MOSFET gate signal output designed to work with an external MOSFET driver. Inductor current is sensed via the ISP pin which monitors the negative voltage developed across the PFC current sense resistor. This resistor is connected to the PFC MOSFET Source pin. The current is averaged over several switching cycles and is used for the PFC control algorithm. This pin also implements a cycle-by-cycle current limit to protect the PFC MOSFET in the event of a short-circuit. The RC filter with 100-200 ns time constant attenuates high frequency switching noise, but must be fast enough to detect a saturating PFC inductor in order to protect the PFC MOSFET. PFC output voltage is sensed by the FBP pin via a resistor voltage divider network. The FBP pin is connected to the input

11

www.powerint.com

Rev. F 08/09

�PLC810PG

of an operational transconductance amplifier (OTA). The output of this OTA is connected to the VCOMP pin. The feedback loop operates to keep the voltage on the FBP pin (and therefore the PFC output voltage) to a fixed value, depending on the resistor divider ratio. When the PFC output voltage is higher than the set point, the transconductance amplifier will source current, raising the voltage on the VCOMP pin. When the PFC output voltage is lower than the set point, the transconductance amplifier will sink current, lowering the voltage on VCOMP pin. The gain of the stage is equal to the product of the OTA gain (GM), and the impedance of the network connected to the VCOMP pin. The PFC controller senses the voltage on the VCOMP pin. A higher voltage tends to reduce the PFC MOSFET’s duty cycle, while a lower voltage tends to increase it. The VCOMP pin has a linear operating range of 0.5 V to 2.5 V, and is scaled and multiplied by the average inductor current to set DOFF, the off-duty-cycle of the PFC gate signal. During closed-loop steady state operation, the VCOMP voltage is a function of the line voltage and the PFC load. A low voltage on VCOMP signifies high power, while a high voltage corresponds to low power. The VCOMP pin is internally connected to an input of a multiplier which is part of the PFC modulator. The linear range of this pin is 0.5 V to 2.5 V. 0.5 V signifies maximum power, and 2.5 V signifies minimum power. The FBP pin has 3 start-up and shutdown voltage thresholds. 1. INH – Inhibits PFC start-up at low AC input voltage. 2. VSD(H) – inhibits LLC start-up after PFC start-up. LLC start-up is delayed until the PFC output voltage is close to its regulation set point. 3. VSD(L) – shuts down the LLC converter when the bulk cap has discharged to a low voltage – typically at the end of holdup time. Before PFC start-up, the voltage on the bulk cap is approximately equal to the peak of the input voltage, and INH acts as an AC undervoltage lockout. After the PFC starts, the PFC output voltage no longer tracks the input voltage and there is no low AC voltage shutdown function. For a typical design with a PFC voltage set point of 385 V, the PFC is inhibited when bulk voltage