DATASHEET

932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

General Description

Features/Benefits

The 932SQ420D is a main clock synthesizer for

Romley-generation Intel based server platforms. The

932SQ420D is driven with a 25 MHz crystal for maximum

performance. It generates CPU outputs of 100 or 133.33

MHz.

• 0.5% down spread capable on CPU/SRC/PCI

Recommended Application

• Cycle to cycle jitter: CPU/SRC/NS_SRC/NS_SAS <

• 64-pin TSSOP and MLF packages/Space Savings

Key Specifications

50ps.

CK420BQ

•

•

•

•

Output Features

•

•

•

•

•

•

•

outputs/Lower EMI

4 - HCSL CPU outputs

4 - HCSL Non-Spread SAS/SRC outputs

Phase jitter: PCIe Gen2 < 3ps rms, Gen3 < 1ps rms

Phase jitter: QPI 9.6GB/s < 0.2ps rms

Phase jitter: NS-SAS < 0.4ps rms using raw phase data

Phase jitter: NS-SAS < 1.3ps rms using Clk Jit Tool 1.6.3

3 - HCSL SRC outputs

1 - HCSL DOT96 output

1 - 3.3V 48M output

5 - 3.3V PCI outputs

1- 3.3V REF output

Block Diagram

CPU(3:0)

X1_25

X2

CPU_SRC_PCI

PLL (SS)

SRC(2:0)

PCI(4:0)

/3

NS_SAS(1:0)

Low Drift non-SS

PLL

200 mV

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

4

2.7

10

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

AC Electrical Characteristics - Differential Current Mode Outputs

TA = TCOM; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

Measured differentially, PLL

Duty Cycle

tD C

45

50.1

Mode

Across all SRC outputs,

tsk3 SRC

13.5

Skew, Output to Output

VT = 50%

Across all CPU outputs,

tsk3 CPU

43

Skew, Output to Output

VT = 50%

CPU, SRC, NS_SAS outputs

35

Jitter, Cycle to cycle

tjcyc-cyc

DOT96 output

75

1

Guaranteed by design and characterization, not 100% tested in production.

2

I REF = V DD /(3xRR ). For RR = 475Ω (1%), IREF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50Ω.

3

MAX

UNITS NOTES

55

%

1

50

ps

1

50

ps

1

50

250

ps

ps

1,3

1,3

Measured from differential waveform

Electrical Characteristics - Phase Jitter Parameters

TA = 0 - 70°C; Supply Voltage VDD/ VDDA = 3.3 V +/-5%,

PARAMETER

SYMBOL

tjphPCIeG1

tjphPCIeG2

tjphPCIeG3

Phase Jitter

t jphQPI_SMI

t jphSAS12G

CONDITIONS

PCIe Gen 1

PCIe Gen 2 Lo Band

10kHz < f < 1.5MHz

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)

PCIe Gen 3

(PLL BW of 2-4MHz, CDR =

10MHz)

QPI & SMI

(100MHz or 133MHz, 4.8Gb/s,

6.4Gb/s 12UI)

QPI & SMI

(100MHz, 8.0Gb/s, 12UI)

QPI & SMI

(100MHz, 9.6Gb/s, 12UI)

SAS12G

(Filtered REFCLK Jitter 20KHz

to 20MHz.)

t jphSAS12G

MIN

SAS 12G

TYP

28

MAX

86

UNITS Notes

ps (p-p) 1,2,3,6

ps

1,2,6

(rms)

ps

1,2,6

(rms)

0.9

3

1.7

3.1

0.4

1

ps

(rms)

1,2,4,6

0.15

0.5

ps

(rms)

1,5,7

0.13

0.3

0.11

0.2

0.34

0.4

ps

(rms)

1,8,9

0.70

1.3

ps

(rms)

1,5,8

ps

(rms)

ps

(rms)

1,5,7

1,5,7

1

Guaranteed by design and characterization, not 100% tested in production.

See http://www.pcisig.com for complete specs

3

Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

4

Subject to final radification by PCI SIG.

2

5

6

Calculated from Intel-supplied Clock Jitter Tool v 1.6.6

Applied to SRC outputs

7

Applies to CPU outputs

8

Applies to NS_SAS, NS_SRC outputs, Spread Off

9

Intel calculation from raw phase noise data

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

11

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Electrical Characteristics - PCI

TA = 0 - 70°C; Supply Voltage V DD /VDD A = 3.3 V +/-5% ,

PARAMETER

Output Impedance

Output High Voltage

Output Low Voltage

SYMBOL

RDSP

VOH

VOL

CONDITIONS

VO = VD D*(0.5)

IOH = -1 mA

IOL = 1 mA

MIN @V OH = 1.0 V

MAX @V OH = 3.135 V

MIN @VOL = 1.95 V

MAX @ V OL = 0.4 V

MIN

12

2.4

TYP

MAX

55

0.55

-33

UNITS NOTES

Ω

1

V

1

V

1

mA

1

mA

1

mA

1

mA

1

Output High Current

IOH

Output Low Current

IOL

Clock High Time

THIGH

1.5V

12

ns

1

Clock Low Time

Edge Rate

Duty Cycle

Group Skew

Jitter, Cycle to cycle

TL OW

tsle wr/ f

dt1

tskew

tjcyc-cyc

1.5V

Rising/Falling edge rate

V T = 1.5 V

V T = 1.5 V

V T = 1.5 V

12

1

45

ns

V/ns

%

ps

ps

1

-33

30

38

1.8

50.5

294

108

4

55

500

500

TYP

MAX

60

1,2

1

1

1

S ee "Sin gle-ended Test Loa ds Page" for termination circuits

1

Guaranteed by desig n and characterization, not 100% tested in production.

2

Measured between 0.8V and 2.0V

Electrical Characteristics - 48MHz

TA = 0 - 70°C; Supply Voltage V DD /VDD A = 3.3 V +/-5% ,

PARAMETER

Output Impedance

Output High Voltage

Output Low Voltage

SYMBOL

RDSP

VOH

VOL

CONDITIONS

VO = VD D*(0.5)

IOH = -1 mA

IOL = 1 mA

MIN @V OH = 1.0 V

MAX @V OH = 3.135 V

MIN @VOL = 1.95 V

MAX @ V OL = 0.4 V

MIN

20

2.4

0.55

-29

UNITS NOTES

Ω

1

V

1

V

1

mA

1

mA

1

mA

1

mA

1

Output High Current

IOH

Output Low Current

IOL

Clock High Time

THIGH

1.5V

8.094

10.036

ns

1

Clock Low Time

Edge Rate

Duty Cycle

Jitter, Cycle to cycle

TL OW

1.5V

Rising/Falling edge rate

V T = 1.5 V

V T = 1.5 V

7.694

1

45

ns

V/ns

%

ps

1

1.5

51

109

9.836

2

55

350

TYP

MAX

380

400

mA

1

16

20

mA

1

tslewr/f_USB

dt1

tjcyc-cyc

-33

29

27

1,2

1

1

S ee "Sin gle-ended Test Loa ds Page" for termination circuits

1

Guaranteed by desig n and characterization, not 100% tested in production.

2

Measured between 0.8V and 2.0V

Electrical Characteristics - Current Consumption

TA = TCOM; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

Operating Supply Current

IDD 3.3OP

Powerdown C urrent

1

IDD 3.3PD Z

CONDITIONS

All outputs active @100MHz, CL

= Full load;

All differential pairs tri-stated

MIN

UNITS NOTES

Guaranteed by design and characterization, not 100% tested in production.

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

12

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Electrical Characteristics - REF

TA = 0 - 70°C; Supply Voltage V DD /VDD A = 3.3 V +/-5% ,

PARAMETER

Output Impedance

Output High Voltage

Output Low Voltage

Output High Current

SYMBOL

RDSP

VOH

VOL

IOH

CONDITIONS

VO = VD D*(0.5)

IOH = -1 mA

IOL = 1 mA

MIN @V OH = 1.0 V

MAX @V OH = 3.135 V

MIN @VOL = 1.95 V

MAX @ V OL = 0.4 V

MIN

12

2.4

TYP

MAX

55

0.55

-33

-33

30

UNITS

Ω

V

V

mA

mA

mA

mA

Notes

1

1

1

1

1

1

1

Output Low Current

IOL

Clock High Time

THIGH

1.5V

27.5

ns

1

Clock Low Time

Edge Rate

Duty Cycle

Jitter, Cycle to cycle

TL OW

tsle wr/ f

dt1

tjcyc-cyc

1.5V

Rising/Falling edge rate

V T = 1.5 V

V T = 1.5 V

27.5

1

45

ns

V/ns

%

ps

1

38

1.9

50.5

75

4

55

1000

1,2

1

1

S ee "Sin gle-ended Test Loa ds Page" for termination circuits

1

Guaranteed by desig n and characterization, not 100% tested in production.

2

Measured between 0.8V and 2.0V

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

13

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Clock AC Tolerances

PPM tolerance

Cycle to Cycle Jitter

Spread

CPU

100

50

-0.50%

SRC,

NS_SAS,

NS_SR C

100

50

-0.50%

PCI

100

500

-0.50%

DOT96

100

250

0

48MHz

100

350

0.00%

REF

100

1000

0.00%

ppm

ps

%

Clock Periods – Outputs with Spread Spectrum Disabled

1 Clock

Measurement Window

1us

0.1s

0.1s

0.1s

-SSC

+ ppm

- ppm

Short-Term Long-Term 0 ppm Period Long-Term

Average

Average

Nominal

Average

Min

Min

Max

9.99900

10.00000

10.00100

7.49925

7.50000

7.50075

SSC ON

Center

Freq.

MHz

CPU

100.00000

133.33333

9.94900

7.44925

100.00000

9.94900

9.99900

10.00000

33.33333

96.00000

48.00000

14.31818

29.49700

10.16563

20.48125

69.78429

29.99700

10.41563

20.83125

69.83429

30.00000

10.41667

20.83333

69.84128

SRC,

NS_SAS,

NS_SRC

PCI

DOT96

48MHz

REF

-c2c jitter

AbsPer

Min

1us

+SSC

Short-Term

Average

Max

1 Clock

+c2c jitter Units Notes

AbsPer

Max

10.05100

7.55075

ns

ns

10.00100

10.05100

ns

30.00300

10.41771

20.83542

69.84826

30.50300

10.66771

21.18542

69.89826

ns

ns

ns

ns

1,2

1,2

1,2

1,2

1,2

1,2

1,2

Clock Periods – Outputs with Spread Spectrum Enabled

SSC ON

CPU

PCI

SRC

1

2

Center

Freq.

MHz

99.75

133.00

33.25

99.75

1 Clock

-c2c jitter

AbsPer

Min

9.94906

7.44930

29.49718

9.94906

Measurement Window

1us

0.1s

0.1s

0.1s

- ppm

-SSC

+ ppm

Short-Term Long-Term 0 ppm Period Long-Term

Average

Average

Nominal

Average

Min

Min

Max

9.99906

10.02406

10.02506

10.02607

7.49930

7.51805

7.51880

7.51955

29.99718

30.07218

30.07519

30.07820

9.99906

10.02406

10.02506

10.02607

1us

+SSC

Short-Term

Average

Max

10.05107

7.53830

30.15320

10.05107

1 Clock

+c2c jitter Units Notes

AbsPer

Max

10.10107

7.58830

30.65320

10.10107

ns

ns

ns

ns

1,2

1,2

1,2

1,2

Guaranteed by design and characterization, not 100% tested in production.

All Long Term Accuracy specifications are guaranteed with the assumption that the REF output is tuned to exactly 14.31818MHz.

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

14

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

General SMBus Serial Interface Information

How to Write

How to Read

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Controller (host) sends a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) sends the byte count = X

IDT clock will acknowledge

Controller (host) starts sending Byte N through Byte

N+X-1

IDT clock will acknowledge each byte one at a time

Controller (host) sends a Stop bit

Index Block Write Operation

Controller (Host)

T

Index Block Read Operation

IDT (Slave/Receiver)

Controller (Host)

starT bit

T

Slave Address

WR

•

•

•

Controller (host) will send a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) will send a separate start bit

Controller (host) sends the read address

IDT clock will acknowledge

IDT clock will send the data byte count = X

IDT clock sends Byte N+X-1

IDT clock sends Byte 0 through Byte X (if X(H) was

written to Byte 8)

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

IDT (Slave/Receiver)

starT bit

Slave Address

WRite

ACK

WR

WRite

ACK

Beginning Byte = N

ACK

Beginning Byte = N

ACK

Data Byte Count = X

ACK

RT

Slave Address

Beginning Byte N

ACK

X Byte

O

O

O

Repeat starT

RD

ReaD

ACK

O

Data Byte Count=X

O

O

ACK

ACK

ACK

Beginning Byte N

Byte N + X - 1

stoP bit

O

O

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

O

O

O

SMBus write address = D2 hex

SMBus read address = D3 hex

O

X Byte

P

Byte N + X - 1

N

Not acknowledge

P

stoP bit

15

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

SMBus Table: Output Enable Register

Byte 0

Pin #

Name

24/25

DOT96 Enable

Bit 7

50/49

NS_SAS1 Enable

Bit 6

48/47

NS_SAS0 Enable

Bit 5

44/43

NS_SRC1 Enable

Bit 4

42/41

NS_SRC0 Enable

Bit 3

36/35

SRC2 Enable

Bit 2

34/33

SRC1 Enable

Bit 1

30/31

SRC0 Enable

Bit 0

SMBus Table: Output Enable Register

Byte 1

Pin #

Name

5

REF14_3x Enable

Bit 7

Bit 6

Bit 5

62/61

CPU3

Bit 4

CPU2

60/59

Bit 3

56/55

CPU1

Bit 2

CPU0

54/53

Bit 1

CPU/SRC/

Spread Spectrum Enable

Bit 0

PCI

Control Function

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

1

Enable

Enable

Enable

Enable

Enable

Enable

Enable

Enable

Default

1

1

1

1

1

1

1

1

Control Function

Output Enable

RESERVED

RESERVED

Output Enable

Output Enable

Output Enable

Output Enable

Type

RW

0

Disable-Low

1

Enable

RW

RW

RW

RW

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Disable-Hi-Z

Enable

Enable

Enable

Enable

Default

1

0

0

1

1

1

1

RW

Spread Off

Spread On

0

Default

0

0

1

1

1

1

1

1

Spread Off/On

SMBus Table: Output Enable Register

Byte 2

Pin #

Name

Bit 7

Bit 6

PCI4 Enable

13

Bit 5

14

PCI3 Enable

Bit 4

PCI2 Enable

15

Bit 3

16

PCI1 Enable

Bit 2

17

PCI0 Enable

Bit 1

21

48MHz Enable

Bit 0

Control Function

RESERVED

RESERVED

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Type

0

1

RW

RW

RW

RW

RW

RW

Disable-Low

Disable-Low

Disable-Low

Disable-Low

Disable-Low

Disable-Low

Enable

Enable

Enable

Enable

Enable

Enable

SMBus Table: Reserved

Pin #

Byte 3

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

Control Function

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Type

0

1

Default

0

0

0

0

0

0

0

0

Name

Control Function

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Type

0

1

Default

0

0

0

0

0

0

0

0

SMBus Table: Reserved

Byte 4

Pin #

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

16

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

SMBus Table: Reserved

Byte 5

Pin #

B it 7

B it 6

B it 5

B it 4

B it 3

B it 2

B it 1

B it 0

Name

FS4

FS3

FS2

FS1

FS0

C ontrol Function

RESERVED

RESERVED

RESERVED

Freq. Sel 4

Freq. Sel 3

Freq. Sel 2

Freq. Sel 1

Freq. Sel 0

Type

RW

RW

RW

RW

RW

0

1

See NS_SAS/NS_SRC

Frequency Table.

Default

0

0

0

0

1

1

1

1

SMBus Table: Test Mode and CPU/SRC/PCI Frequency Select Register

Byte 6

0

1

Default

Pin #

Name

C ontrol Function

Type

Test Mode

Test Mode Type

RW

Hi-Z

REF/N

0

B it 7

Test Select

Select Test Mode

RW

Disable

Enable

0

B it 6

RESERVED

0

B it 5

100M_133M# (See note)

Frequency Select

133MHz

100MHz

Latch

B it 4

R

FS3

Freq. Sel 3

RW

1

B it 3

See CPU/SRC/PCI Frequency

FS2

Freq. Sel 2

RW

0

B it 2

Select Table

FS1

Freq. Sel 1

RW

0

B it 1

B it 0

FS0

Freq. Sel 0

RW

0

Note: Internal Pull up on 100M_133M# pin will result in default CPU frequency of 100 MHz.

SMBus Table: Vendor & Revision ID Register

Byte 7

Pin #

Name

B it 7

R ID3

B it 6

R ID2

B it 5

R ID1

B it 4

R ID0

VID 3

B it 3

VID 2

B it 2

VID 1

B it 1

B it 0

VID 0

SMBus Table: Byte Count R egister

Byte 8

Pin #

Name

BC7

B it 7

B it 6

BC6

B it 5

BC5

B it 4

BC4

B it 3

BC3

B it 2

BC2

B it 1

BC1

BC0

B it 0

SMBus Table: Device ID Register

Byte 9

Pin #

Name

D ID7

B it 7

DID6

B it 6

D ID5

B it 5

DID4

B it 4

D ID3

B it 3

DID2

B it 2

D ID1

B it 1

DID0

B it 0

C ontrol Function

REVISION ID

VENDOR ID

C ontrol Function

Byte Count

Programming b(7:0)

C ontrol Function

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Device ID

(17 hex)

Type

R

R

R

R

R

R

R

R

Type

RW

RW

RW

RW

RW

RW

RW

RW

Type

R

R

R

R

R

R

R

R

17

0

1

0011 for D rev

0001 for ICS/IDT

0

1

Writing to this register will

configure how many bytes will

be read back, default is A

bytes.

(0 to 9

0

-

1

-

932SQ420D

Default

0

0

1

1

0

0

0

1

Default

0

0

0

0

1

0

1

0

Default

0

0

0

1

0

1

1

1

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

CPU/SRC/PCI Frequency Selection Table

Line

Byte 1,

Bit 0

Spread

Enable

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Byte6 Byte6 Byte6 Byte6

Bit3

Bit2

Bit1

Bit0

FS3

FS2

FS1

FS0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

CPU

Speed

for

100MHz

CPU

Speed

for

133MHz

89.97

91.28

92.58

93.75

95.05

96.22

97.53

98.83

100.00

101.30

102.47

103.78

105.08

106.25

107.55

110.03

89.97

91.28

92.58

93.75

95.05

96.22

97.53

98.83

100.00

101.30

102.47

103.78

105.08

106.25

107.55

110.03

119.97

121.70

123.44

125.00

126.73

128.30

130.03

131.77

133.33

135.07

136.63

138.37

140.10

141.67

143.40

146.70

119.97

121.70

123.44

125.00

126.73

128.30

130.03

131.77

133.33

135.07

136.63

138.37

140.10

141.67

143.40

146.70

18

SRC

PCI Spread

(MHz) (MHz)

%

89.97

91.28

92.58

93.75

95.05

96.22

97.53

98.83

100.00

101.30

102.47

103.78

105.08

106.25

107.55

110.03

89.97

91.28

92.58

93.75

95.05

96.22

97.53

98.83

100.00

101.30

102.47

103.78

105.08

106.25

107.55

110.03

29.99

30.43

30.86

31.25

31.68

32.07

32.51

32.94

33.33

33.77

34.16

34.59

35.03

35.42

35.85

36.68

29.99

30.43

30.86

31.25

31.68

32.07

32.51

32.94

33.33

33.77

34.16

34.59

35.03

35.42

35.85

36.68

0%

-0.5%

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

NS_SAS Margining Table

Line

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Byte5

Bit4

FS4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Byte5 Byte5 Byte5 Byte5

Bit3

Bit2

Bit1

Bit0

FS3

FS2

FS1

FS0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

NS_xxx

(MHz)

58.33

61.11

63.89

66.67

69.44

72.22

75.00

77.78

80.56

83.33

86.11

88.89

91.67

94.44

97.22

100.00

102.78

105.56

108.33

111.11

113.89

116.67

119.44

122.22

125.00

127.78

130.56

133.33

136.11

138.89

141.67

144.44

NOTE: Operation at other than the default entry is not

guaranteed. These values are for margining purposes only.

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

19

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

DIF Reference Clock

Common R ecommendations for Differential Routing

L1 length, route as non-coupled 50ohm trace

L2 length, route as non-coupled 50ohm trace

L3 length, route as non-coupled 50ohm trace

Rs

Rt

D imension or Value

0.5 max

0.2 max

0.2 max

33

49.9

Unit

inch

inch

inch

ohm

ohm

Figure

1

1

1

1

1

Down Device Differential Routing

L4 length, route as coupled microstrip 100ohm differential trace

L4 length, route as coupled stripline 100ohm differential trace

2 min to 16 max

1.8 min to 14.4 max

inch

inch

1

1

Differential Routing to PCI Express Connector

L4 length, route as coupled microstrip 100ohm differential trace

L4 length, route as coupled stripline 100ohm differential trace

0.25 to 14 max

0.225 min to 12.6 max

inch

inch

2

2

Figure 1: Down Device Routing

L2

L1

Rs

L4

L4'

L2'

L1'

Rs

HCSL Output Buffer

Rt

Rt

L3'

PCI Express

Down Device

REF_CLK Input

L3

Figure 2: PCI Express Connector Routing

L2

L1

Rs

L4

L4'

L2'

L1'

HCSL Output Buffer

Rs

Rt

Rt

L3'

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

PCI Express

Add-in Board

REF_CLK Input

L3

20

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Alternative Termination for LVDS and other Common Differential Signals (figure 3)

Vdiff

Vp-p

Vcm

R1

R2

R3

R4

Note

0.45v

0.22v

1.08

33

150

100

100

0.58

0.28

0.6

33

78.7

137

100

0.80

0.40

0.6

33

78.7

none

100

ICS874003i-02 input compatible

0.60

0.3

1.2

33

174

140

100

Standard LVDS

R1a = R1b = R1

R2a = R2b = R2

Figure 3

L2

L1

R3

R1a

R4

L4

L4'

L2'

L1'

R1b

HCSL Output Buffer

R2a

R2b

L3'

Down Device

REF_CLK Input

L3

Cable Connected AC Coupled Application (figure 4)

Component

Value

Note

R5a, R5b

8.2K 5%

R6a, R6b

1K 5%

Cc

0.1 µF

Vcm

0.350 volts

Figure 4

3.3 Volts

R5a

R5b

R6a

R6b

Cc

L4

L4'

Cc

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

21

PCIe Device

REF_CLK Input

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Test Clarification Table

Comments

HW

SW

TE ST

TEST_SEL TEST_MODE ENTRY BIT

HW P IN

B6b6

HW PIN

Power-up w/ TEST_SEL = 1 (>2.0V) to enter test mode.

Cycle power to disable test mode.

If TEST_SEL HW pin is 0 during power-up,

test mode can be selected through B6b6.

If test mode is selected by B6b6, then B6b7

is used to select HI-Z or REF/N.

TEST_Mode pin is not used.

Cycle power to disable test mode.

REF/N or

HI-Z

B6b7

0

1

1

1

1

0

X

0

0

1

1

X

0

X

X

X

X

1

X

0

1

0

1

0

OUTPUT

NORMAL

HI-Z

REF/N

REF/N

REF/N

HI-Z

0

X

1

1

REF/N

B6b6: 1= ENTER TEST MODE, Default = 0 (NORMAL OPERATION)

B6b7: 1= REF/N, Default = 0 (HI-Z)

Thermal Characteristics

Parameter

Thermal Resistance Junction to

Ambient

Symbol

Conditions

Min.

Typ.

Max. Units

JA

Still air

68.2

C/W

JA

1 m/s air flow

63.3

C/W

JA

2 m/s air flow

59.6

C/W

Thermal Resistance Junction to Case

JC

32.5

C/W

Thermal Resistance Junction to

Board

JB

51.5

C/W

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

22

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Package Outline and Package Dimensions (64-pin TSSOP)

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

23

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

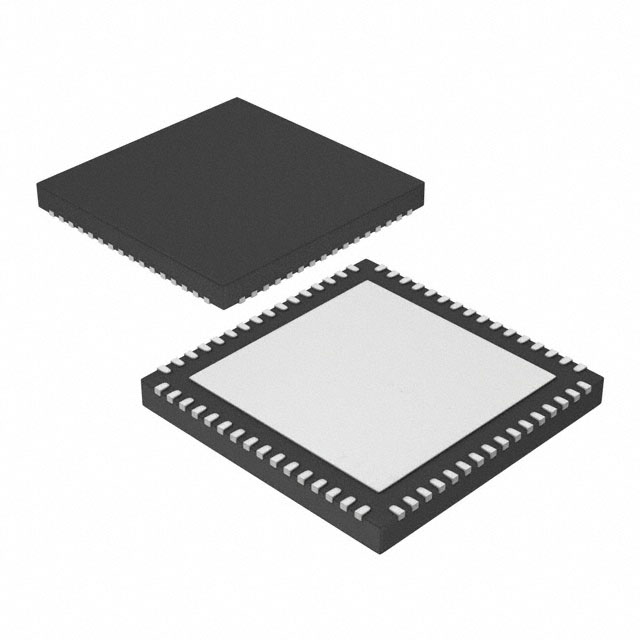

Package Outline and Package Dimensions (64-pin MLF)

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

24

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Package Outline and Package Dimensions, cont. (64-pin MLF)

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

25

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Marking Diagram (TSSOP)

ICS

LOT

YYWW

932SQ420DGLF

Marking Diagram (MLF)

ICS

932SQ420DKL

LOT

COO YYWW

Notes:

1. ’LOT’ denotes lot number.

2. ‘YYWW’ is the date code.

3. ‘COO’ denotes country of origin.

4. ‘L’ or ‘LF’ denotes RoHS compliant package.

Ordering Information

Part / Order Number

932SQ420DGLF

932SQ420DGLFT

932SQ420DKLF

932SQ420DKLFT

Shipping Packaging

Tubes

Tape and Reel

Tray

Tape and Reel

Package

64-pin TSSOP

64-pin TSSOP

64-pin MLF

64-pin MLF

Temperature

0 to +70° C

0 to +70° C

0 to +70° C

0 to +70° C

"LF" suffix to the part number are the Pb-Free configuration, RoHS compliant.

“D” is the device revision designator (will not correlate with the datasheet revision).

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes

no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No

other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications

such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not

recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT

does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

26

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Revision History

Rev.

A

B

C

D

Issue Date

9/20/2010

3/1/2011

3/9/2011

4/28/2011

Who

RDW

RDW

RDW

RDW

E

7/26/2011

RDW

F

9/20/2011

RDW

G

12/8/2011

RDW

H

4/18/2012

RDW

J

1/7/2015

DC

Description

Minor typo corrections

Added rise/fall variation to DC Electrical Characteristics Table

Corrected Line 0 of NS_SAS Margining Table.

Corrected MLF packaging pin description. Pin 37 was missing.

Updated Power Down Functionality table to clarify functionality of singleended outputs in power down.

1. Added "Case Temperature" spec to Abs Max ratings

2. Added Thermal Characteristics

1. Updated Phase Jitter Table to correct typo in "Conditions" column for

SAS.

2. Mark Spec Added.

1. Updated Rp values on Output Terminations Table from 43.2 ohms to

42.2 or 43.2 ohms to be consistent with Intel.

1. Updated package drawing and dimensions from PUNCH to SAWN

version.

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

27

Page #

Various

9

19

7

2

Various

11, 23,

24

8

Various

932SQ420D

REV J 010715

�932SQ420D

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

SYNTHESIZERS

Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

For Tech Support

800-345-7015

408-284-8200

Fax: 408-284-2775

www.idt.com/go/clockhelp

pcclockhelp@idt.com

Corporate Headquarters

Integrated Device Technology, Inc.

www.idt.com

© 2015 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT, ICS, and the IDT logo are trademarks of Integrated

Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or

registered trademarks used to identify products or services of their respective owners.

Printed in USA

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

�