DATASHEET

9FG1901H

Frequency Gearing Clock for CPU, PCIe Gen1 & FBD

Description

Features/Benefits

The 9FG1901H follows the Intel DB1900G Differential Buffer

Specification. This buffer provides 19 output clocks for CPU Host

Bus, PCI-Express, or Fully Buffered DIMM applications. The outputs

are configured with two groups. Both groups, DIF_(16:0) and

DIF_(18:17) can be equal to or have a gear ratio to the input clock.

A differential CPU clock from a CK410B+ main clock generator,

such as the ICS932S421, drives the ICS9FG1901. The 9FG1901H

can provide outputs up to 400MHz.

•

•

Key Specifications

•

•

•

•

•

•

•

•

Power up default is all outputs in 1:1 mode

DIF_(16:0) can be “gear-shifted” from the input CPU Host

Clock

DIF_(18:17) can be “gear-shifted” from the input CPU Host

Clock

Spread spectrum compatible

Supports output clock frequencies up to 400 MHz

8 Selectable SMBus addresses

SMBus address determines PLL or Bypass mode

VDDA controlled power down mode

DIF output cycle-to-cycle jitter < 50ps

DIF output-to-output skew across all outputs in 1:1 mode < 150ps

Functional Block Diagram

OE_17_18#

OE(16:5)#,

OE_01234#

SPREAD

COMPATIBLE

PLL

GEAR

SHIFT

LOGIC

STOP

LOGIC

2

SPREAD

COMPATIBLE

PLL

GEAR

SHIFT

LOGIC

STOP

LOGIC

17

DIF(18:17)

13

CLK_IN

CLK_IN#

DIF(16:0)

HIGH_BW#

FS_A_410

SMB_A0

SMB_A1

SMB_A2_PLLBYP#

SMBDAT

SMBCLK

CONTROL

LOGIC

IREF

IDTTM Frequency Gearing Clock for CPU, PCIe Gen1 & FBD

1386A - 02/02/10

1

�DIF_14

DIF_14#

OE15#

DIF_15

DIF_15#

OE16#

DIF_16

DIF_16#

VDD

GND

DIF_17

DIF_17#

DIF_18

DIF_18#

OE17_18#

CLK_IN

SMB_A2_PLLBYP#

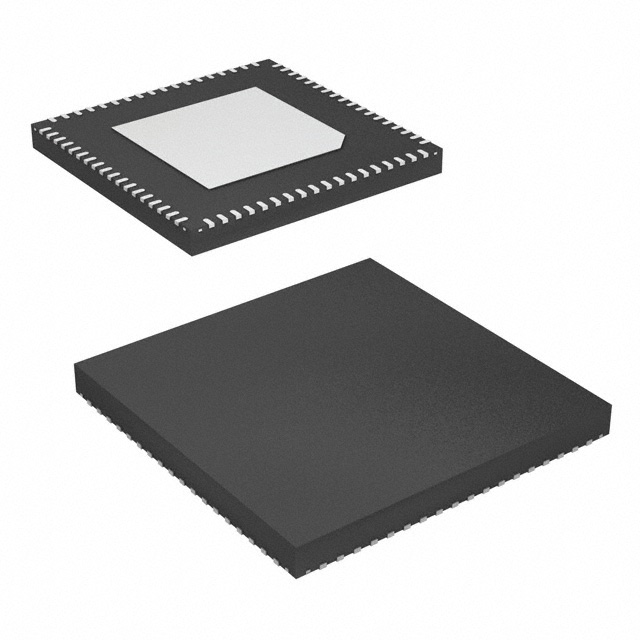

Pin Configuration

CLK_IN#

9FG1901H

Frequency Gearing Clock for CPU, PCIe Gen1 & FBD

72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55

IREF

1

GNDA

2

VDDA/PD#

3

HIGH_BW#

4

FS_A_410

5

DIF_0

6

DIF_0#

7

DIF_1

8

DIF_1#

9

54 OE14#

53 DIF_13#

52 DIF_13

51 OE13#

50 DIF_12#

49 DIF_12

48 OE12#

47 VDD

46 GND

9FG1901

GND 10

45 DIF_11#

44 DIF_11

43 OE11#

VDD 11

DIF_2 12

42 DIF_10#

41 DIF_10

40 OE10#

DIF_2# 13

DIF_3 14

DIF_3# 15

39 DIF_9#

38 DIF_9

37 OE9#

DIF_4 16

DIF_4# 17

OE_01234# 18

19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

SMB_A1

SMB_A0

DIF_8#

DIF_8

OE8#

DIF_7#

DIF_7

OE7#

GND

VDD

DIF_6#

DIF_6

OE6#

DIF_5#

DIF_5

OE5#

SMBDAT

SMBCLK

72-pin MLF

Power Groups

Functionality at Power Up (PLL Mode)

1

FS_A_410

1

0

CLK_IN

(CPU FSB)

MHz

100

很抱歉,暂时无法提供与“9FG1901HKLFT”相匹配的价格&库存,您可以联系我们找货

免费人工找货