DATASHEET

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

9LPRS477D

General Description

Features/Benefits

The 9LPRS477D is a main clock synthesizer chip that

provides all clocks required for ATI RD7xx-based systems

using AMD processors. An SMBus interface allows full

control of the device.

• CPU, ATIG, SB_SRC and SRC outputs are

•

•

•

Recommended Application

ATI RS780/RS790/RD790/RS880 systems using AMD K8

processors

•

•

Output Features

•

•

•

•

•

•

•

•

independently programmable for frequency

Spread Spectrum for EMI reduction

Outputs may be disabled via SMBus

External crystal load capacitors for maximum frequency

accuracy

Meets PCIEX Gen2 specifications

Meets 30kHz to 33kHz SRC modulation rate specification

for USB3.0

Key Specifications

2 - Greyhound compatible K8 CPU pairs

6 - low-power differential SRC pairs

2 - low-power differential SouthBridge SRC pairs

4 - low-power differential ATIG pairs

1 - Selectable low-power differential 100MHz non-spread

SATA/ SRC output

1 - Selectable 100MHz low-power differential/ 66 MHz

single-ended HTT clock

2 - 48MHz USB clocks

3 - 14.318MHz Reference clocks

•

•

•

•

CPU outputs cycle-to-cycle jitter < 85ps

SRC outputs cycle-to-cycle jitter < 125ps

ATIG outputs cycle-to-cycle jitter < 125ps

± 300ppm frequency accuracy on CPU, SRC & ATIG

clocks

CPUKG0C_LPRS

CPUKG0T_LPRS

PD#

RESTORE#

GNDHTT

HTT0C_LPRS/66M

HTT0T_LPRS/66M

VDDHTT

REF2/SEL_OC_MODE**

REF1/SEL_SATA

REF0/SEL_HTT66

VDDREF

GNDREF

X1

X2

VDD48

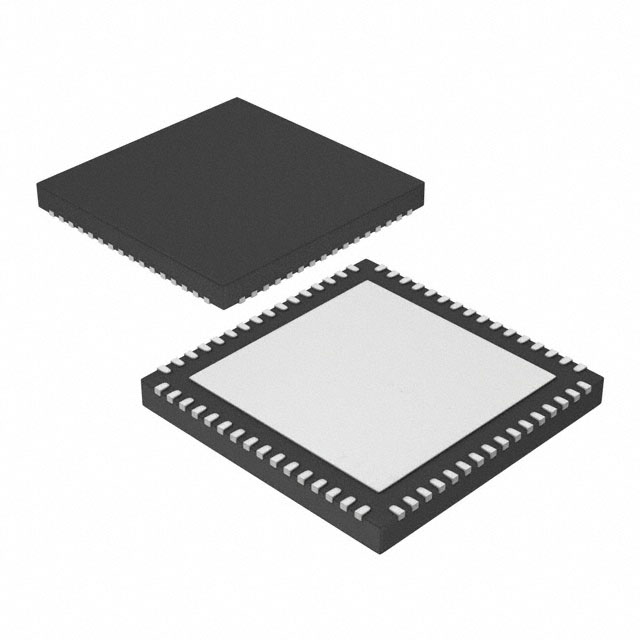

Pin Configuration

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

**SEL_DOC/48MHz_1

**SEL_CPU1#/48MHz_0

GND48

SMBCLK

SMBDAT

**DOC_0/SRC5C_LPRS

**DOC_1/SRC5T_LPRS

SRC4C_LPRS

SRC4T_LPRS

GNDSRC

VDDSRC

SRC3C_LPRS

SRC3T_LPRS

SRC2C_LPRS

SRC2T_LPRS

VDDSRC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

ICS9LPRS477D

VDDCPU

GNDCPU

CPUKG1T_LPRS/SRC7T_LPRS

CPUKG1C_LPRS/SRC7C_LPRS

VDDA

GNDA

GNDSATA

SRC6T/SATAT_LPRS

SRC6C/SATAC_LPRS

VDDSATA

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

VDDATIG

GNDATIG

ATIG2T_LPRS

ATIG2C_LPRS

ATIG3T_LPRS

ATIG3C_LPRS

GNDATIG

SB_SRC0T_LPRS

SB_SRC0C_LPRS

VDDSB_SRC

GNDSB_SRC

SB_SRC1T_LPRS

SB_SRC1C_LPRS

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

GNDSRC

SRC1C_LPRS

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

64-Pin MLF

* Internal Pull-Up Resistor

** Internal Pull-Down Resistor

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

1

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Pin Descriptions

PIN #

PIN NAME

PIN TYPE

1

**SEL_DOC/48MHz _1

I/O

2

**SEL_CPU1#/48MHz_0

I/O

3

4

5

GND48

SMBCLK

SMBDAT

GND

IN

I/O

6

**DOC_0/SRC5C_LPRS

OUT

7

**DOC_1/SRC5T_LPRS

OUT

8

SRC4C_LPRS

OUT

9

SRC4T_LPRS

OUT

10

11

GNDSRC

VDDSRC

GND

PWR

12

SRC3C_LPRS

OUT

13

SRC3T_LPRS

OUT

14

SRC2C_LPRS

OUT

15

SRC2T_LPRS

OUT

16

17

VDDSRC

GNDSRC

PWR

GND

18

SRC1C_LPRS

OUT

19

SRC1T_LPRS

OUT

20

SRC0C_LPRS

OUT

21

SRC0T_LPRS

OUT

22

SB_SRC1C_LPRS

OUT

23

SB_SRC1T_LPRS

OUT

24

25

GNDSB_SRC

VDDSB_SRC

GND

PWR

26

SB_SRC0C_LPRS

OUT

27

SB_SRC0T_LPRS

OUT

28

GNDATIG

GND

29

ATIG3C_LPRS

OUT

30

ATIG3T_LPRS

OUT

31

ATIG2C_LPRS

OUT

32

ATIG2T_LPRS

OUT

DESCRIPTION

SEl_DOC: latched input to s elect pin functionality

1 = DOC input.

0 = SRCCLK5

/ 48MHz cloc k output.

SEL_CPU1 latched input to select pin functionality

1 = SRCCLK7

0 = CPUKG1

/ 48MHz cloc k output.

Ground pin for the 48MHz outputs

Clock pin of SMBus circuitry, 5V tolerant.

Data pin for SMBus circuitry, 5V tolerant.

Dynamic Over Clocking pin: real time frequency selection 0: Normal; 1: Frequency will transition to a

preprogrammed value in the I2c.

/ Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm

s eries resistor needed

Dynamic Over Clocking pin: real time frequency selection 0: Normal; 1: Frequency will transition to a

preprogrammed value in the I2c.

/ True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series

resistor needed

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SRC clock pair. (no 50ohm s hunt res istor to GND and no 33 ohm s eries

resistor needed

Ground pin for the SRC outputs

Supply for SRC core, 3.3V nominal

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SRC clock pair. (no 50ohm s hunt res istor to GND and no 33 ohm s eries

resistor needed

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SRC clock pair. (no 50ohm s hunt res istor to GND and no 33 ohm s eries

resistor needed

Supply for SRC core, 3.3V nominal

Ground pin for the SRC outputs

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SRC clock pair. (no 50ohm s hunt res istor to GND and no 33 ohm s eries

resistor needed

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SRC clock pair. (no 50ohm s hunt res istor to GND and no 33 ohm s eries

resistor needed

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm

s eries resistor needed

Ground pin for the SB_SRC outputs

Supply for SRC core, 3.3V nominal

Complement clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no

33 ohm series resistor needed

True clock of low power differential SouthBridge SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm

s eries resistor needed

Ground pin for the ATIG outputs

Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed)

True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt

resistor to GND and no 33 ohm series resistor needed)

Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed)

True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt

resistor to GND and no 33 ohm series resistor needed)

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

2

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Pin Descriptions (cont.)

PIN #

33 GNDATIG

34 VDDATIG

PIN NAME

PIN TYPE

DESCRIPTION

GND

Ground pin for the ATIG outputs

PWR

Power supply for ATIG core, nominal 3.3V

Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no

OUT

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed)

True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt

OUT

resistor to GND and no 33 ohm series resistor needed)

Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no

OUT

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed)

True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt

OUT

resistor to GND and no 33 ohm series resistor needed)

PWR

Power supply for SATA core logic, nominal 3.3V

Complement clock of low power differential SRC/SATA clock pair. (no 50ohm shunt resistor to GND and no 33 ohm

OUT

s eries resistor needed

True clock of low power differential SRC/SATA cloc k pair. (no 50ohm shunt resistor to GND and no 33 ohm series

OUT

resistor needed

GND

Ground pin for the SRC outputs

GND

Ground for the Analog Core

PWR

3.3V Power for the Analog Core

Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock with integrated series

OUT

resistor.(no 33 ohm series resistor needed) / Complement clock of low power differential SRC clock pair. (no

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed

True signal of low-power differential push-pull AMD K8 "Greyhound" cloc k with integrated series resistor. (no 33

OUT

ohm series resistor needed) / True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND

and no 33 ohm s eries resistor needed

GND

Ground pin for the CPU outputs

PWR

Supply for CPU core, 3.3V nominal

Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock with integrated series resistor.

OUT

(no 33 ohm series resistor needed)

True signal of low-power differential push-pull AMD K8 "Greyhound" c lock with integrated series resistor.(no 33

OUT

ohm series resistor needed)

Enter /Exit Power Down.

IN

0 = Power Down, 1 = normal operation.

Open Drain I/O. As an input it restores the PLL's to power up default s tate. As an output, this signal is driven low

when the internal watchdog hardware timer expires. It is cleared when the internal watchdog hardware timer is reset

I/O

or disabled. The input is falling edge triggered.

0 = Restore Settings, 1 = normal operation.

PWR

Ground pin for the HTT outputs

Complementary signal of low-power differential push-pull hypertransport clock with integrated series resistor. (no

OUT

50ohm shunt res istor to GND and no 33 ohm s eries resistor needed) / 3.3V single ended 66MHz hyper transport

c lock

35

ATIG1C_LPRS

36

ATIG1T_LPRS

37

ATIG0C_LPRS

38

ATIG0T_LPRS

39

VDDSATA

40

SRC6C/SATAC_LPRS

41

SRC6T/SATAT_LPRS

42

43

44

GNDSATA

GNDA

VDDA

45

CPUKG1C_LPRS/SRC7C_LPRS

46

CPUKG1T_LPRS/SRC7T_LPRS

47

48

GNDCPU

VDDCPU

49

CPUKG0C_LPRS

50

CPUKG0T_LPRS

51

PD#

52

RESTORE#

53

GNDHTT

54

HTT0C_LPRS/66M

55

HTT0T_LPRS/66M

OUT

56

VDDHTT

PWR

57

REF2/SEL_OC_MODE**

I/O

58

REF1/SEL_SATA

I/O

59

REF0/SEL_HTT66

I/O

60

61

62

63

64

VDDREF

GNDREF

X1

X2

VDD48

PWR

GND

IN

OUT

PWR

True signal of low-power differential push-pull hypertransport clock with integrated series resistor. (no 50ohm shunt

resistor to GND and no 33 ohm series resistor needed) / 3.3V single ended 66MHz hyper transport clock

Supply for HTT clocks , nominal 3.3V.

14.318 MHz 3.3V reference clock./ SEl_OC_MODE: latched input to select pin functionality

1 = ATIG/SRC PCIE Gen1 Mode with higher overclock ing ability

0 = ATIG/SRC PCIE Gen2 Mode with limited overclocking ability

14.318 MHz 3.3V reference clock./ 3.3V tolerant latched input to select function of SRC6/SATA output

0 = 100MHz differential spreading SRC clock, 1 = 100MHz non-s preading differential SATA clock

14.318 MHz 3.3V reference clock./ 3.3V tolerant latched input to select Hyper Transport Clock Frequency.

0 = 100MHz differential HTT clock, 1 = 66MHz 3.3V single ended HTT clock

Ref, XTAL power supply, nominal 3.3V

Ground pin for the REF outputs.

Crystal input, nominally 14.318MHz

Crystal output, nominally 14.318MHz

Power pin for the 48MHz outputs and core. 3.3V

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

3

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Block Diagram

X1

X2

REF

14.318MHz

OSC

48MHz_(1:0)

Fixed PLL4

EXACT 48MHz

SEL_SATA

100MHz

SRC6/SATA

SS PLL

SB_SRC

(-0.5% DWN SP)

800MHz

100MHz

SB_SRC(1:0)

SS PLL

SB_SRC/SRC

SRC ZDB PLL

400 to 900 MHz

PWD @

600MHz/6

SS PLL

SRC(5:0)

SEL_HTT66

HTT 100MHz

HTT_100T/66

HTT 66MHz

HTT_100C/66

CPUKG(1:0)

200MHz

ATIG(3:0)

ATIG ZDB PLL

SEL_OC_MODE

SEL_DOC

PD#

SEL_HTT66

SEL_SATA

SMBCLK

Control

Logic

SMBDAT

RESTORE#

MODE

Power Groups

Pin Number

Description

V DD

GND

64

11, 1 6

3

10, 17

USB _48 outputs

SRC differential outputs

25

24

SB _SRC differential outputs

39

42

SRC/SATA differential output

34

28,33

ATIG differential outputs

44

43

Analog, P LL

48

47

CPUK G differential outputs

56

53

HTTCLK output

60

61

REF outputs

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

4

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Differential Output Power Management Table

PD#

CLKREQ#

SMBus

Register OE

True output

Complement

Output

Free-Run

True output

Complement

Output

CLKREQ# Selected

1

0

Enable

Running

Running

Running

Running

0

X

X

Low/20K

Low

Low/20K

Low

1

1

Enable

Running

Running

Low/20K

Low

X

X

Disable

Low/20K

Low

Low/20K

Low

Note: 20K means 20Kohm Pull Down

Singled-ended Power Management Table

SMBus

Register OE

USB

REF0, 1

RE F2

1

Enable

Running

Running

Running

0

Enable

Low

Hi-Z

Hi-Z

Table1: CPU and HTT Frequency Selection Table

Byte 3

Bit4

Bit3

Bit2

Bit1

Bit0

CPU

(MHz)

CPU

CPU

CPU

CPU

CPU

FS4

FS3

FS2

FS1

FS0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

200.00

205.00

210.00

215.00

220.00

225.00

230.00

235.00

240.00

245.00

250.00

255.00

260.00

265.00

270.00

200.00

280.00

285.00

290.00

295.00

300.00

305.00

310.00

315.00

320.00

325.00

330.00

335.00

340.00

345.00

350.00

355.00

HTT

Single-ended

HTT

Differential

SEL_HTT66 = 1

SEL_HTT66 = 0

66.67

68.33

70.00

71.67

73.33

75.00

76.67

78.33

80.00

81.67

83.33

85.00

86.67

88.33

90.00

66.67

93.33

95.00

96.67

98.33

100.00

101.67

103.33

105.00

106.67

108.33

110.00

111.67

113.33

115.00

116.67

118.33

100.00

102.50

105.00

107.50

110.00

112.50

115.00

117.50

120.00

122.50

125.00

127.50

130.00

132.50

135.00

100.00

140.00

142.50

145.00

147.50

150.00

152.50

155.00

157.50

160.00

162.50

165.00

167.50

170.00

172.50

175.00

177.50

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Spread

%

(B6b6=1

and

B3b5=1)

CPU

CPU

Output

OverClock %

Divider

0%

2%

5%

8%

10%

13%

15%

18%

20%

23%

25%

28%

30%

33%

35%

0%

40%

43%

45%

48%

50%

53%

55%

58%

60%

63%

65%

68%

70%

73%

75%

78%

Depends on SB_SRC PLL. See Table 4.

PD#

5

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

9LPRS477D

VCO

(MHz)

400.00

410.00

420.00

430.00

440.00

450.00

460.00

470.00

480.00

490.00

500.00

510.00

520.00

530.00

540.00

400.00

560.00

570.00

580.00

590.00

600.00

610.00

620.00

630.00

640.00

650.00

660.00

670.00

680.00

690.00

700.00

710.00

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Table 2: SRC Frequency Selection Table

Byte 4

SRC

Spread

B12b3

SRC

Bit3 Bit2 Bit1 Bit0

OverClock

%

(MHz)

OC

SB

SB

SB

SB

%

(B6b5=1)

Latch FS3 FS2 FS1 FS0

0

0

0

0

0

100.00

0%

0

0

0

0

1

101.00

1%

0

0

0

1

0

102.00

2%

0

0

0

1

1

103.00

3%

0

0

1

0

0

104.00

4%

0

0

1

0

1

105.00

5%

0

0

1

1

0

106.00

6%

1

OFF

0

0

1

1

1

107.00

7%

0

1

0

0

0

108.00

8%

0

1

0

0

1

109.00

9%

0

1

0

1

0

110.00

10%

0

1

0

1

1

111.00

11%

0

1

1

0

0

112.00

12%

0

1

1

0

1

113.00

13%

0

1

1

1

0

114.00

14%

OFF

0%

0

1

1

1

1

100.00

1

0

0

0

0

100.00

0%

1

0

0

0

1

101.00

1%

1

0

0

1

0

102.00

2%

1

0

0

1

1

103.00

3%

1

0

1

0

0

104.00

4%

1

0

1

0

1

105.00

5%

1

0

1

1

0

106.00

6%

1

1

0

1

1

1

107.00

7%

OFF

1

1

0

0

0

108.00

8%

1

1

0

0

1

109.00

9%

1

1

0

1

0

110.00

10%

1

1

0

1

1

111.00

11%

1

1

1

0

0

112.00

12%

1

1

1

0

1

113.00

13%

1

1

1

1

0

114.00

14%

OFF

1

1

1

1

1

100.00

0%

1

Note : After SRC SS_EN bit is enabled through SMBus Byte 6 bit 5,

there will be no spread for SRC's by default. To obtain spread spectrum

on SRC outputs, please program Byte23 & Byte24.

To pass USB3.0, please use below reference SMBus setting:

Byte Setting

Description

B4=E0h

Change SRC to FS0000 Frequency Setting

B6=2Fh

Enable SRC Spread Spectrum

B12=45h

SRC MN Enable

B21=8Ch

Set SRC M Div

B22=68h

Set SRC N Div

B23=1Ah

Set SRC Spread %

B24=3Eh

Set SRC Spread %

* Actual word used can deviate from above table pending usage

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

6

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

-0.50%

-0.50%

Table3: ATIG Frequency Selection Table

Byte 5

Spread

B12b4

Bit3 Bit2 Bit1 Bit0 ATIG(3:0)

%

(MHz)

OC

SB

SB

SB

SB

(B6b7=1)

Latch FS3 FS2 FS1 FS0

0

0

0

0

0

100.00

0

0

0

0

1

101.00

0

0

0

1

0

102.00

0

0

0

1

1

103.00

0

0

1

0

0

104.00

0

0

1

0

1

105.00

0

0

1

1

0

106.00

0

0

1

1

1

107.00

0

1

0

0

0

108.00

0

1

0

0

1

109.00

0

1

0

1

0

110.00

0

1

0

1

1

111.00

0

1

1

0

0

112.00

0

1

1

0

1

113.00

0

1

1

1

0

114.00

OFF

0

1

1

1

1

100.00

1

0

0

0

0

100.00

1

0

0

0

1

101.00

1

0

0

1

0

102.00

1

0

0

1

1

103.00

1

0

1

0

0

104.00

1

0

1

0

1

105.00

1

0

1

1

0

106.00

1

0

1

1

1

107.00

1

1

0

0

0

108.00

1

1

0

0

1

109.00

1

1

0

1

0

110.00

1

1

0

1

1

111.00

1

1

1

0

0

112.00

1

1

1

0

1

113.00

1

1

1

1

0

114.00

1

1

1

1

1

100.00

OFF

ATIG

OverClock %

ATIG

Output

Divider

VCO

(MHz)

0%

1%

2%

3%

4%

5%

6%

7%

8%

9%

10%

11%

12%

13%

14%

0%

0%

1%

2%

3%

4%

5%

6%

7%

8%

9%

10%

11%

12%

13%

14%

0%

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

1000.00

1010.00

1020.00

1030.00

1040.00

1050.00

1060.00

1070.00

1080.00

1090.00

1100.00

1110.00

1120.00

1130.00

1140.00

1000.00

800.00

808.00

816.00

824.00

832.00

840.00

848.00

856.00

864.00

872.00

880.00

888.00

896.00

904.00

912.00

800.00

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

7

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Table4: SB_SRC Frequency Selection Table

Byte 6

Bit4

Bit3

Bit2

Bit1

Bit0

SB_SRC

(1:0)

SRC

SRC

SRC

SRC

SRC

(MHz)

FS4

FS3

FS2

FS1

FS0

Table 5: IO_Vout select table

B12b2

B12b1

B12b0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Bold Entry is Power up Default

SB_SRC SB_SRC

OverClock Output

%

Divider

0

85.00

-15%

1

86.00

-14%

0

87.00

-13%

1

88.00

-12%

0

89.00

-11%

1

90.00

-10%

0

91.00

-9%

1

92.00

-8%

0

93.00

-7%

1

94.00

-6%

0

95.00

-5%

1

96.00

-4%

0

97.00

-3%

1

98.00

-2%

0

99.00

-1%

OFF

1

100.00

0%

0

100.00

0%

1

101.00

1%

0

102.00

2%

1

103.00

3%

0

104.00

4%

1

105.00

5%

0

106.00

6%

1

107.00

7%

0

108.00

8%

1

109.00

9%

0

110.00

10%

1

111.00

11%

0

112.00

12%

1

113.00

13%

0

114.00

14%

1

115.00

15%

the SB_SRC are at 0% Overclocking.

-0.50%

0

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

1

0

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

1

0

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

frequencies assume that

-0.50%

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

NOTE: All

Spread

%

(B6b6=1)

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

VCO

(MHz)

850.00

860.00

870.00

880.00

890.00

900.00

910.00

920.00

930.00

940.00

950.00

960.00

970.00

980.00

990.00

1000.00

1000.00

1010.00

1020.00

1030.00

1040.00

1050.00

1060.00

1070.00

1080.00

1090.00

1100.00

1110.00

1120.00

1130.00

1140.00

1150.00

IO_Vout

0.3V

0.4V

0.5V

0.6V

0.7V

0.8V

0.9V

1.0V

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

8

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

General SMBus Serial Interface Information for 9LPRS477D

How to Write

How to Read

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Controller (host) sends a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) sends the byte count = X

IDT clock will acknowledge

Controller (host) starts sending Byte N through Byte

N+X-1

IDT clock will acknowledge each byte one at a time

Controller (host) sends a Stop bit

Index Block Write Operation

Controller (Host)

T

Index Block Read Operation

IDT (Slave/Receiver)

Controller (Host)

starT bit

T

Slave Address

WR

•

•

•

Controller (host) will send a start bit

Controller (host) sends the write address

IDT clock will acknowledge

Controller (host) sends the beginning byte location = N

IDT clock will acknowledge

Controller (host) will send a separate start bit

Controller (host) sends the read address

IDT clock will acknowledge

IDT clock will send the data byte count = X

IDT clock sends Byte N+X-1

IDT clock sends Byte 0 through Byte X (if X(H) was

written to Byte 8)

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

IDT (Slave/Receiver)

starT bit

Slave Address

WRite

ACK

WR

WRite

ACK

Beginning Byte = N

ACK

Beginning Byte = N

ACK

Data Byte Count = X

ACK

RT

Slave Address

Beginning Byte N

ACK

O

O

RD

ReaD

ACK

X Byte

O

Repeat starT

O

Data Byte Count=X

O

O

ACK

ACK

ACK

Beginning Byte N

Byte N + X - 1

stoP bit

O

X Byte

P

O

O

O

O

O

Read Address

Write Address

D3(H)

D2(H)

Byte N + X - 1

N

Not acknowledge

P

stoP bit

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

9

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

B yte

0

Bit 7

Byte

1

100MHz Differential HTT clock

66 MHz 3.3V Single-ended HTT

clock

SRC6/SATA pair is SATA nonspread output

Enabled

Default

Latch

S EL_SATA readback

SATA Select

R

REF0_OE

Output Enable

RW

Bit 4

REF1_OE

Output Enable

RW

Hi-Z

Enabled

Bit 3

REF2_OE

Output Enable

RW

Hi-Z

Enabled

1

Bit 2

48MHz_1_OE

Output Enable

RW

Low

Enabled

1

Latch

1

1

Bit 1

48MHz_0_OE

Output Enable

RW

Low

Enabled

1

Bit 0

SEL_CPU1 readback

CPU1/S RC7 Select

R

CPU1 Di fferential output

SRC7 Differential output

Latch

1

2

3

4

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

R

Bit 5

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

Hypertransport Select

Bit 6

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

SEL_HTT66 readback

SRC6/SATA pair is SRC SS

capable output

Hi-Z

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

SMBus Table: Latched Input Readback Output Enable Control Register

Name

Description

Type

0

5

SMBus Table:Output Enable Control Register

Name

Control Function

SE L_DOC readback

SRC6/SA TA_OE Enable

SRC5_OE

SRC4_OE

SRC3_OE

SRC2_OE

SRC1_OE

SRC0_OE

DOC Select

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Type

0

1

Default

R

RW

RW

RW

RW

RW

RW

RW

SRC5 Di fferential output

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

DOC

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Latch

1

1

1

1

1

1

1

0

1

Default

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

Low/Low

1 Load

1 Load

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

2 Load

2 Load

1

1

1

1

1

1

1

1

SMBus Table: Output Enable and 48MHz Strength Control Register

Name

Control Function

Type

SB_SRC1_OE

SB_SRC0_OE

ATIG3_OE

ATIG2_OE

ATIG1_OE

ATIG0_OE

48MHz_1_Strength

48MHz_0_Strength

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

Output Enable

48MHz_1 Drive Strength Sel.

48MHz_0 Drive Strength Sel.

SMBus Table: CPU/H TT Frequency Control Register

Name

Control Function

CPU1_OE/SRC7_OE

CPU0_OE

CP U Spread Source

CPU_FS4

CPU_FS3

CPU_FS2

CPU_FS1

CPU_FS0

Output enable

Output enable

CP U Spread Source

CPU Frequency Select MS B

CPU Frequency Select

CPU Frequency Select

CPU Frequency Select

CP U Frequency Select LSB

SMBus Table: SRC Frequency C ontrol Register

Name

Control Function

REF0_Strength

REF1_Strength

REF2_Strength

REF0_Drive Strength Sel

REF1_Drive Strength Sel

REF2_Drive Strength Sel

SRC_FS3

SRC_FS2

SRC_FS1

SRC_FS0

SRC Frequency Select

SRC Frequency Select

SRC Frequency Select

SRC Frequency Select LSB

SMBus Table: ATIG Frequency Select Register

Name

Control Function

Bit 7

Bit 6

Bit 5

ATIG PLL TBEN

CP U PLL TBEN

SRC PLL TBEN

Bit 4

DISABLE _ORT

Bit 3

Bit 2

Bit 1

Bit 0

ATIG_FS3

ATIG_FS2

ATIG_FS1

ATIG_FS0

ATIG P LL Turbo Enable

CPU P LL Turbo Enable

SRC P LL Turbo Enable

Disabl e O vershoot R eduction

T echnology during CP U PLL M/N

Programming

ATIG Frequency Select

ATIG Freque ncy Select

ATIG Frequency Select

ATIG Frequency Select LSB

RW

RW

RW

RW

RW

RW

RW

RW

Type

0

1

Default

RW

RW

RW

RW

RW

RW

RW

RW

Low/Low

Low/Low

Fix PLL

Enable

Enable

SB_S RC PLL

1

1

1

0

1

1

1

1

See CPU Frequency Select Table

Default value corresponds to 200MHz.

Note that Selected HTT frequency tracks the CPU frequency.

Type

RW

RW

RW

Reserved

RW

RW

RW

RW

0

1

Default

1 Load

1 Load

1 Load

2 Load

2 Load

2 Load

1

1

1

0

1

1

1

1

See SRC Frequency Select Table

Type

0

1

Default

RW

RW

RW

Disable

Disable

Disable

Enable

Enable

Enable

0

0

0

RW

E NABLE ORT

DISABLE ORT

0

RW

RW

RW

RW

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

See ATIG Frequency Select Table

10

9LPRS477D

1

1

1

1

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

6

Byte

Default

Enable

Enable

Enable

0

0

0

SB _SRC_FS4

SB_SRC Frequen cy Select MSB

RW

Bit 3

Bit 2

Bit 1

Bit 0

SB _SRC_FS3

SB _SRC_FS2

SB _SRC_FS1

SB _SRC_FS0

SB_S RC Frequency Select

SB_SRC Frequency Select

SB_S RC Frequency Select

S B_SRC Frequency Select LSB

RW

RW

RW

RW

7

8

9

SMBus Table: Device ID register

Name

Control Function

Device ID7

Device ID6

Device ID5

Device ID4

Device ID3

Device ID2

Device ID1

Device ID0

Type

0

R

R

R

R

R

R

R

R

Devi ce ID

SMBus Table: Vendor & Revision ID Register

Name

Control Function

RID3

RID2

RID1

RID0

VID3

VID2

VID1

VID0

See S B_SRC Frequency Select Table

Note: SB_SRC and CPU Clo cks are synchronous. Changing this

frequency will alter the SB_SRC and CPU frequency by the same

percentage.

REVISION ID

VENDOR ID

SMBus Table: WatchDog Timer Control Register

Name

Control Function

1

75 hex for 9LPRS477

0

1

Default

R

R

R

R

R

R

R

R

-

-

0

1

0

0

0

0

0

1

Type

0

1

Default

Enable Timer

0

0

X

X

HWD_EN

Watchdog Hard Alarm Enable

RW

Bit 6

Bit 5

Bit 4

SWD_EN

WD Hard Statu s

WD Soft Status

Watch dog Soft Alarm Enable

WD Hard Alarm Status

WD Soft Alarm S tatus

RW

R

R

Disable

Normal

Normal

Enable

Alarm

Alarm

Bit 3

WDTCtrl

Watch Dog Alarm Time base Control

RW

290ms Base

1160ms Base

Bit 2

Bit 1

Bit 0

HWD2

HWD1

HWD0

WD Hard Alarm Timer Bit 2

WD Hard Alarm Timer Bit 1

WD Hard Alarm Timer Bit 0

RW

RW

RW

11

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

These bits represent the number of Watch Dog Time Base Units that

pass before the Wa tch Alarm expires. Default is 7 X 290ms = 2s.

SMBus Table: WD Timer Safe Frequency Control Register

Name

Control Function

Type

SWD2

SWD1

SWD0

WD SF4

WD SF3

WD SF2

WD SF1

WD SF0

WD Soft Alarm Timer Bit 2

WD Soft Alarm Timer Bit 1

WD Soft Alarm Timer Bit 0

Watch Dog Safe Freq Programming

bits

SMBus Table: Byte Count Register

Name

Control Function

BC5

BC4

BC3

BC2

BC1

BC0

Byte Count bit 5 (MSB)

Byte Count bit 4

Byte Count bit 3

Byte Count bit 2

Byte Count bit 1

Byte Count bit 0 (LSB)

Default

Type

Bit 7

10

0

1

1

1

1

x

x

x

x

x

x

x

x

Disable and Reload Hartd Alarm

Timer, Clear WD Hard status bit.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

1

Disable

Disable

Disable

Bit 4

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

0

RW

RW

RW

ATIG Spread Enable

SB_SRC/CPU Spread Enable

SRC Spread Enable

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

Type

ATIG SSEN

SB_SRC/CPU SSEN

SRC SSEN

Bit 7

Bit 6

Bit 5

Byte

SMBus Table: SB_SRC Frequency Select Register

Name

Control Function

RW

RW

RW

RW

RW

RW

RW

RW

0

1

These bits represent the number of Watch Dog Time Base Units that

pass before the Wa tch Alarm expires. Default is 7 X 290ms = 2s.

These bits configure the safe frequency that the device returns to if

the Watchdog Timer expires. The value show here corresponds to

the power up default of the device. See the various Frequency

Select Tables for the exact frequ encies.

Type

0

1

Reserved

Reserved

RW

RW

RW Determines the number of bytes that are read back from the device.

RW

Default is 0F hex.

RW

RW

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

11

9LPRS477D

0

1

1

1

Default

1

1

1

0

1

1

1

1

Default

0

0

0

0

1

1

1

1

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

12

SMBus Table: M/N Programming Enable and I/O Vout Control Register

Name

Control Function

Type

0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

CPU M/N En

SRC M/N En

ATIG M/N En

SB_SRC M/N En

S EL_OC_MODE readback

Bit 2

IO_VOUT2

Bit 1

IO_VOUT1

Bit 0

IO_VOUT0

CPU PLL M/N Prog. Enable

SRC M/N Prog.Enable

ATIG M/N Prog. Enable

SB_SRC M/N Prog. Enable

OC MODE Select

IO Output Voltage Select (Most

Significant B it)

IO Output Voltage Select

IO Output Voltage Select (Least

Significant B it)

RW

RW

RW

RW

R

M/N Prog. Disabled

M/N Prog. Disabled

M/N Prog. Disabled

M/N Prog. Disabled

PCIE Gen2 Mode

1

Default

M/N Prog. Enabled

M/N Prog. Enabled

M/N Prog. Enabled

M/N Prog. Enabled

PCIE Gen1 Mode

0

0

0

0

Latch

RW

1

See Table 5: V_IO Sele ction

(Default is 0.8V)

RW

0

RW

1

Bytes 13/14 are reserved

Byte

Byte

15

Type

0

1

Bit 7

Test_Sel

Sele cts Test Mode

RW

Normal mode

All ouputs are REF/N

0

Bit 6

SB_S RC Source

SB_S RC Source Sel ection

RW

SB_SRC PLL

SRC PLL

1

Bit 5

ATIG PLL

ATIG PLL DOC pin control

RW

DOC0

DOC1

0

Bit 4

CPU PLL

CPU PLL DOC pin control

RW

DOC0

DOC1

0

Bit 3

SRC PLL

SRC PLL DOC pin control

RW

DOC0

DOC1

0

Bit 2

ATIG PLL

ATIG PLL DOC0 2 pin control

RW

Disable

Enable

0

Bit 1

CPU PLL

CPU PLL DOC0 2 pin control

RW

Disable

Enable

0

Bit 0

SRC PLL

SRC PLL DOC0 2 pin control

RW

Disable

Enable

0

Type

0

1

Default

16

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

17

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

18

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

SMBus Table:Test Mode Register

Name

Control Function

19

SMBus Table: CPU PLL Frequency Control Register

Name

Control Function

N Div2

N Div1

M Div5

M Div4

M Div3

M Div2

M Div1

M Div0

N Divider Prog bit 2

N Divider Prog bit 1

M Divider Programming bits

SMBus Table: CPU PLL Frequency Control Register

Name

Control Function

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming b(10:3)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 16 and 17 will

configure the VCO frequency. Default at power up = Byte 3 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

The decimal representation of M and N Divider in Byte 16 and 17 will

configure the VCO frequency. Default at power up = Byte 3 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

SMBus Table: SB_SRC PLL Spread Spectrum Control Register

Name

Control Function

Type

SSP7

SSP6

SSP5

SSP4

SSP3

SSP2

SSP1

SSP0

Spread Spectrum P rogramming

b(7:0)

RW

RW

RW

RW

RW

RW

RW

RW

1

0

1

These bits set the SB_S RC spread pecentage.Please contact IDT

for the appropriate values.

SMBus Table: SB_SRC PLL Spread Spectrum Control Register

Name

Control Function

Type

0

1

Default

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

Bit 7

Bit 6

Bit 5

SSP15

SSP14

SSP13

Bit 4

SSP12

Bit 3

SSP11

Bit 2

SSP10

RW

X

Bit 1

SSP9

RW

X

Bit 0

SSP8

RW

X

RW

RW

RW

Spread Spectrum P rogramming

b(15:8)

RW

RW

X

X

X

These bits set the SB_S RC spread pecentage.Please contact IDT

for the appropriate values.

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

12

9LPRS477D

X

X

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

20

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

21

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

22

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

23

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

24

CPU NDiv0

CPUDiv3

CPUDiv2

CPUDiv1

CPUDiv0

RW

Reserved

Reserved

Reserved

RW

RW

CP U Divider Ratio Programming Bits

RW

RW

SMBUS Table: SRC Frequency Control Register

Name

Control Function

N Div2

N Div1

M Div5

M Div4

M Div3

M Div2

M Div1

M Div0

N Divider Prog bit 2

N Divider Prog bit 1

M Divider Programming

bit (5:0)

SMBUS Table: SRC Frequency Control Register

Name

Control Function

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

Type

LSB N Di vider Programming

N Divider Programming Byte16

bit(7:0) and Byte15 bit(7:6)

0

0000:/2 ; 0100:/4

0001:/3 ; 0101:/6

0010:/5 ; 0110:/10

0011:/9 ; 0111:/18

1000:/8 ; 1100:/16

1001:/12 ; 1101:/24

1010:/20 ; 1110:/40

1011:/36 ; 1111:/72

0

1

Default

The decimal representation of M and N Divider in Byte 21 and 22

configure the SRC VCO fre quency. See M/N Caculation Tables for

VCO frequency formulas.

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Spread Spectrum P rogramming

bit(7:0)

RW

RW

RW

RW

RW

RW

RW

RW

1

The decimal representation of M and N Divider in Byte 21 and 22

configure the SRC VCO fre quency. See M/N Caculation Tables for

VCO frequency formulas.

SMBUS Table: SRC Spread Spectrum Control Register

Name

Control Function

Type

SSP7

SSP6

SSP5

SSP4

SSP3

SSP2

SSP1

SSP0

Default

X

X

X

X

X

X

X

X

Type

RW

RW

RW

RW

RW

RW

RW

RW

1

Byte 28 has the N Divider LSB (bit 0) for CPU M/N programming.

0

1

These bits set the SRC spread pecentages.Please contact IDT for

the appropriate values.

SMBUS Table: SRC Spread Spectrum Control Register

Name

Control Function

Type

0

1

Default

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

Bit 5

Bit 4

SSP12

Bit 3

SSP11

Bit 2

Bit 1

SSP10

RW

X

SSP9

RW

X

Bit 0

SSP8

RW

X

25

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

RW

RW

RW

X

X

X

X

X

X

X

X

SSP15

SSP14

SSP13

Bit 7

Bit 6

Byte

SMBUS Table: CPU Output Divider Register

Name

Control Function

Spread Spectrum P rogramming

bi t(15:8)

SMBUS Table: SRC Output Divider Control R egister

Name

Control Function

SB_SRC NDiv0

SRCDiv3

SRCDiv2

SRCDiv1

SRCDiv0

LSB N Di vider Programming

RW

RW

X

X

X

These bits set the SRC spread pecentages.Please contact IDT for

the appropriate values.

Type

RW

Reserved

Reserved

Reserved

RW

RW

SRC Divider Ratio Programming Bits

RW

RW

0

1

N Divider LSB (bit 0) for SRC M/N programming.

0000:/2 ; 0100:/4

0001:/3 ; 0101:/6

0010:/5 ; 0110:/10

0011:/9 ; 0111:/18

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

1000:/8 ; 1100:/16

1001:/12 ; 1101:/24

1010:/20 ; 1110:/40

1011:/36 ; 1111:/72

13

9LPRS477D

X

X

Default

X

X

X

X

X

X

X

X

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

26

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

27

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

28

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

29

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

30

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

31

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBUS Table: ATIG Frequency Control Register

Name

Control Function

N Div2

N Div1

M Div5

M Div4

M Div3

M Div2

M Div1

M Div0

N Divider Prog bit 2

N Divider Prog bit 1

M Divider Programming

bit (5:0)

SMBUS Table: ATIG Frequency Control Register

Name

Control Function

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

The decimal representation of M and N Divider in Byte 26 and 27 will

configure the VCO frequency. Default at power up = Byte 5 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

ATIGDiv3

ATIGDiv2

ATIGDiv1

ATIGDiv0

LSB N Di vider Programming

RW

Reserved

Reserved

Reserved

RW

RW

ATIG Divider Ratio Programming Bits

RW

RW

SMBUS Table: SB_SRC Frequency Control Register

Name

Control Function

N Div2

N Div1

M Div5

M Div4

M Div3

M Div2

M Div1

M Div0

N Divider Prog bit 2

N Divider Prog bit 1

M Divider Programming

bit (5:0)

SMBUS Table: SB_SRC Frequency Control Register

Name

Control Function

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

0

SB_SRCDiv3

SB_SRCDiv2

SB_SRCDiv1

SB_SRCDiv0

LSB N Di vider Programming

RW

Reserved

Reserved

Reserved

RW

SB_SRC Divider Ratio Programming RW

B its

RW

RW

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

0000:/2 ; 0100:/4

0001:/3 ; 0101:/6

0010:/5 ; 0110:/10

0011:/9 ; 0111:/18

1000:/8 ; 1100:/16

1001:/12 ; 1101:/24

1010:/20 ; 1110:/40

1011:/36 ; 1111:/72

0

1

Default

The decimal representation of M and N Divider in Byte 29 and 30 will

configure the VCO frequency. Default at power up = Byte 6 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

0

1

The decimal representation of M and N Divider in Byte 29 and 30 will

configure the VCO frequency. Default at power up = Byte 6 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

SMBUS Table: SB_SRC Output Divider Control Register

Name

Control Function

Type

SB_SRC NDiv0

Default

X

X

X

X

X

X

X

X

Type

RW

RW

RW

RW

RW

RW

RW

RW

1

N Divider LSB (bit 0) for ATIG M/N programming.

Type

RW

RW

RW

RW

RW

RW

RW

RW

1

The decimal representation of M and N Divider in Byte 26 and 27 will

configure the VCO frequency. Default at power up = Byte 5 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

SMBUS Table: ATIG Output Divider Control Register

Name

Control Function

Type

ATIG NDiv0

1

0

1

N Divider LSB (bit 0) for SRC M/N programming.

0000:/2 ; 0100:/4

0001:/3 ; 0101:/6

0010:/5 ; 0110:/10

0011:/9 ; 0111:/18

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

1000:/8 ; 1100:/16

1001:/12 ; 1101:/24

1010:/20 ; 1110:/40

1011:/36 ; 1111:/72

14

9LPRS477D

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

32

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

33

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

34

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

35

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

36

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

37

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SMBUS Table: CPU PLL DOC 1 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 01)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 16 and 32 will

configure the VCO frequency. Default at power up = Byte 3 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: CPU PLL DOC 2 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 10)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 16 and 33 will

configure the VCO frequency. Default at power up = Byte 3 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: CPU PLL DOC 3 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 11)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 16 and 34 will

configure the VCO frequency. Default at power up = Byte 3 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: ATIG PLL DOC 1 N programming Register (1 pin control : D OC = 1; 2 pin control : DOC [0:1] = 01)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 26 and 35 will

configure the VCO frequency. Default at power up = Byte 5 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: ATIG PLL DOC 2 N programming Register (1 pin control : D OC = 1; 2 pin control : DOC [0:1] = 10)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 26 and 36 will

configure the VCO frequency. Default at power up = Byte 5 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: ATIG PLL DOC 3 N programming Register (1 pin control : D OC = 1; 2 pin control : DOC [0:1] = 11)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 26 and 37 will

configure the VCO frequency. Default at power up = Byte 5 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

15

9LPRS477D

X

X

X

X

X

X

X

X

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Byte

38

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

39

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

40

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

41

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Byte

42

SMBUS Table: SRC PLL DOC 1 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 01)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 21 and 38 will

configure the VCO frequency. Default at power up = Byte 4 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: SRC PLL DOC 2 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 10)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 21 and 39 will

configure the VCO frequency. Default at power up = Byte 4 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

X

X

X

X

X

X

X

X

SMBUS Table: SRC PLL DOC 3 N programming Register (1 pin control : DOC = 1; 2 pin control : DOC [0:1] = 11)

Name

Control Function

Type

0

1

Default

N Div10

N Div9

N Div8

N Div7

N Div6

N Div5

N Div4

N Div3

N Divider Programming Byte20

bit(7:0) and Byte19 bit(7:6)

RW

RW

RW

RW

RW

RW

RW

RW

The decimal representation of M and N Divider in Byte 21 and 37 will

configure the VCO frequency. Default at power up = Byte 4 Rom

table. See M/N Caculation Tables for VCO frequency formulas.

SMBus Table: ATIG PLL Spread Spectrum Control Register

Name

Control Function

Type

SSP7

SSP6

SSP5

SSP4

SSP3

SSP2

SSP1

SSP0

Spread Spectrum P rogramming

b(7:0)

RW

RW

RW

RW

RW

RW

RW

RW

0

1

These bi ts set the ATIG spread pecentage.Please contact IDT for

the appropriate values.

SMBus Table: ATIG PLL Spread Spectrum Control R egister

Name

Control Function

Type

0

1

X

X

X

X

X

X

X

X

Default

X

X

X

X

X

X

X

X

Default

Bit 7

Bit 6

Bit 5

SSP15

SSP14

SSP13

Bit 4

SSP12

Bit 3

SSP11

Bit 2

SSP10

RW

X

Bit 1

SSP9

RW

X

Bit 0

SSP8

RW

X

RW

RW

RW

Spread Spectrum P rogramming

b(15:8)

RW

RW

X

X

X

These bi ts set the ATIG spread pecentage.Please contact IDT for

the appropriate values.

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

16

9LPRS477D

X

X

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the 9LPRS477D. These ratings, which are

standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any

other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over

the recommended operating temperature range.

P ARAMETE R

SYMBOL

CONDITIONS

3 .3V Core Supply Voltage

VDDxxx

-

Storage Temperature

Ambient Operating Temp

Ts

Tambient

-

Case Temperature

Tcase

-

Input ESD protection HBM

ESD prot

-

MIN

TYP

MAX

UNITS

3.3

GND + 3.9V

V

-65

0

Notes

1

150

70

°

C

°C

1

1

115

°C

1

V

1

Notes

2000

1

Guaranteed by desig n and characterization, not 100% tested in production.

Electrical Characteristics–Input/Supply/Common Output Parameters

P ARAMETE R

SYMBOL

CONDITIONS*

MIN

TYP

MAX

UNITS

3 .3V Core Supply Voltage

VDDxxx

-

3.135

3.3

3.465

V

1

Input High Voltage

VIH

VDD = 3.3 V +/-5%

2

VDD + 0.3

V

1

Input Low Voltage

V IL

VDD = 3.3 V +/-5%

VSS - 0 .3

0.8

V

1

Input High Current

IIH

VIN = V DD

-5

5

uA

1

-5

uA

1

-200

uA

1

IIL1

Input L ow Current

IIL2

VIN = 0 V; Inputs with no pull-up

resistors

VIN = 0 V ; Inputs with pull-up

resistors

Low Thresh old InputHigh Voltage

Low Thresh old InputLow Voltage

Operating Current

ID D3.3 OP

Powerdown Current

I DD3 .3 PD

Input Frequency

Fi

VDD = 3.3 V +/-5%

Pin Inductance

L pin

V IH _FS

VDD = 3.3 V +/-5%

0.7

VDD + 0.3

V

1

VIL_ FS

VDD = 3.3 V +/-5%

VSS - 0 .3

0.35

V

1

all outputs driven

225

mA

1

all diff pairs low/low

12

mA

1

MHz

2

14.31818

7

nH

1

CIN

Logic Inputs

5

pF

1

COUT

Output pin capacitance

6

pF

1

CINX

Tfall_ PD

X1 & X 2 pins

From VDD Power-Up or deassertion of PD to 1st cl ock

Triangular Modulation

CPU output enable after

PD de-assertion

PD fall time of

Trise_PD

PD rise time of

Input Capacitance

Clk Stabiliza tion

T STAB

Modulation Frequency

Tdrive_PD

SMBus Voltage

VD DSMB

Low-level Output Voltage

V OL SMB

Current sinking at

I PUL LU PSMB

VOL = 0.4 V

SMB CLK/SMBDAT

TR SMB

Clock/Data Rise Time

SMB CLK/SMBDAT

T FSMB

Clock/Data Fall Time

*TA = 0 - 70°C; S upply Voltage VDD = 3.3 V +/-5%

30

2.7

@ I PUL LUP

4

5

pF

1

1.8

ms

1

33

kHz

1

300

us

1

5

ns

1

5

ns

1

5.5

V

1

0.4

V

1

mA

1

1000

ns

1

300

ns

1

6

(Max VIL - 0.15) to

(Min V IH + 0.15)

(Min VIH + 0.15) to

(Max VIL - 0.15)

1

Guaranteed by desig n and characterization, not 100% tested in production.

2

Input frequ ency should be measured at the REF pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

17

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

AC Electrical Characteristics–Low-Power DIF Outputs: CPUKG and HTT

P ARAMETE R

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Cro ssing Point Variation

∆VC ROSS

Single-ended Measurement

140

mV

Frequency

f

Spread Specturm On

198.8

200

MHz

1,3

Long Term Accuracy

ppm

Spread Specturm Off

-300

+300

ppm

1,1 1

1,2,5

Rising Edge Slew Rate

SRISE

Differential Measurement

0.5

10

V/ns

1,4

Falling Edge Slew Rate

SFALL

Differential Measurement

0.5

10

V/ns

1,4

Slew Rate Variation

CPU, DIF HTT

Jitter - Cycle to Cycle

Accumulated Jitter

tS LVAR

Single-ended Measurement

20

%

1

CPUJ C2 C

Differential Measurement

150

ps

1,6

tJ ACC

See Notes

1

ns

1,7

Peak to P eak Differential Voltage

VD(PK-PK)

Differential Measurement

400

2400

mV

1,8

Differential Voltage

VD

Differential Measurement

200

1200

mV

1,9

Duty Cycle

DCYC

Differential Measurement

45

55

%

1

Amplitude Variation

∆V D

Change in VD DC cycle to cycle

-75

75

mV

1,1 0

CPU[1:0] Skew

CPUSKEW1 0

Differential Measurement

100

ps

1

*TA = 0 - 70°C; S upply Voltage VDD = 3.3 V +/-5%, CL = 2pF with Rs = 0Ω (unless otherwise specified)

1

Guaranteed by desig n and characterization, not 100% tested in production.

2

S ingle-ended measurement at crossing point. Value is maximum – minimum over all time. DC value of common mo de is not important due to

the blocking cap.

3

Minimum Frequency is a result of 0.5% down spread spectrum

4

Differential measurement through the range of ±100 mV, differential signal must remain monotoni c and within slew rate spe c when crossing

through this region.

5

Defined as the total variation of all crossing voltages o f CLK rising and CLK# falli ng. Matchin g applies to rising edge rate of CLK and falling

edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

6

Max difference of t CYC LE between a ny two adjacent cycles.

7

Accumulated tjc.over a 10µs time period, measured with JIT2 TIE at 50ps interval.

8

VD(PK-PK) is the overall magnitud e of the differential signal .

VD(min) is the amplitude of the ring-back differential measurement, guaranteed by design, that ring-back will not cross 0V VD. VD(max) is the

largest amplitude allowed.

9

10

The difference in magnitude of two adjacent VD_DC measurements. VD_DC is the stable post overshoot and ring-back part of the signal.

11

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

IDT® PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

18

9LPRS477D

REV C 010715

�9LPRS477D

PROGRAMMABLE SYSTEM CLOCK CHIP FOR ATI RD790-K8TM BASED SYSTEMS

AC Electrical Characteristics–Low-Power DIF Outputs: SRC, SB_SRC, ATIG

P ARAMETE R

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Rising Edge Slew Rate

t SLR

Differential Measurement

0.6

4

V/ns

1,2

Falling Edge Slew Rate

t FL R

Differential Measurement

0.6

4

V/ns

1,2

Slew Rate Variation

tS LVAR

Single-ended Measurement

20

%

1

Maximum Output Voltage

V HIGH

Incl udes overshoot

1150