DATASHEET

HI-200, HI-201

FN3121

Rev 9.00

September 15, 2015

Dual/Quad SPST, CMOS Analog Switches

HI-200/HI-201 (dual/quad) are monolithic devices comprising

independently selectable SPST switches which feature fast

switching speeds (HI-200 240ns, and HI-201 185ns)

combined with low power dissipation (15mW at 25oC). Each

switch provides low “ON” resistance operation for input signal

voltage up to the supply rails and for signal current up to

80mA. Rugged DI construction eliminates latch-up and

substrate SCR failure modes.

Features

All devices provide break-before-make switching and are

TTL and CMOS compatible for maximum application

versatility. HI-200/HI-201 are ideal components for use in

high frequency analog switching. Typical applications

include signal path switching, sample and hold circuit, digital

filters, and operational amplifier gain switching networks.

• Low Power Dissipation . . . . . . . . . . . . . . . . . . . . . . .15mW

Ordering Information

• Sample and Hold Circuits

PART NUMBER

HI3-0200-5Z

(Note) (No

longer available

or supported)

HI1-0201-2

TEMP.

RANGE (°C)

0 to 75

PACKAGE

PKG.

DWG. #

14 Ld PDIP*

(Pb-free)

E14.3

16 Ld CERDIP

F16.3

16 Ld PDIP*

(Pb-free)

E16.3

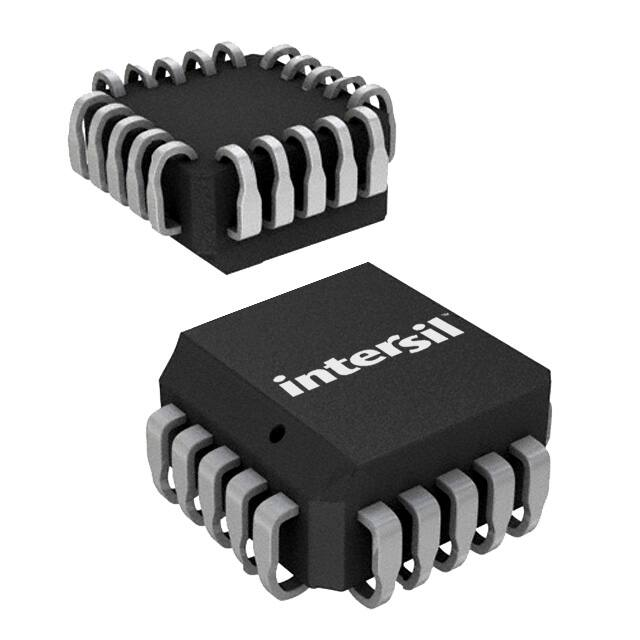

20 Ld PLCC

(Pb-free)

N20.35

• Pb-Free Available (RoHS Compliant)

• Analog Voltage Range . . . . . . . . . . . . . . . . . . . . . . . 15V

• Analog Current Range . . . . . . . . . . . . . . . . . . . . . . . 80mA

• Turn-On Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240ns

• Low rON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

• TTL/CMOS Compatible

Applications

• High Frequency Analog Switching

• Digital Filters

• Operational Amplifier Gain Switching Networks

Functional Diagram

V+

-55 to 125

HI3-0201-5Z

(Note)

0 to 75

HI4P0201-5Z

(Note) (No

longer available

or supported)

0 to 75

HI9P0201-5Z

(Note)

0 to 75

16 Ld SOIC

(Pb-free)

M16.15

HI9P0201-9Z

(Note)

-40 to 85

16 Ld SOIC

(Pb-free)

M16.15

VREF

INPUT

SOURCE

LOGIC

INPUT

GATE

REFERENCE,

LEVEL SHIFTER,

AND DRIVER

SWITCH

CELL

GATE

DRAIN

OUTPUT

*Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

processing applications.

NOTE: Intersil Pb-free products employ special Pb-free material sets;

molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both

SnPb and Pb-free soldering operations. Intersil Pb-free products are

MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020. Pb-free

PDIPs can be used for through hole wave solder processing only. They

are not intended for use in Reflow solder processing applications.

FN3121 Rev 9.00

September 15, 2015

V-

TRUTH TABLE

LOGIC

HI-200

HI-201

0

ON

ON

1

OFF

OFF

Page 1 of 11

�HI-200, HI-201

(Switches Shown For Logic “1” Input)

10 IN1

9 OUT1

8 VREF

IN1

3

14 IN2

V- 4

13 V+

GND

5

12 VREF

IN4

6

11 IN3

OUT4

7

10 OUT3

A4

8

9 A3

IN1

4

V-

5

NC

6

GND

7

IN4

OUT2

15 OUT2

A2

2

3

2

1

20

19

LE

AB

L

AI

AV

ER

G

8 ON

L

NO

9

10

R

O

ED

RT 18 IN2

O

PP

SU

17 V+

16 NC

15 VREF

14 IN3

11

12

13

OUT3

LA

OUT1

OUT4

G

OUT2 N6

LO

O

N V- 7

ER

AI

AV

16 A2

A3

NC 4

IN2 5

1

NC

GND 3

A1

NC

NC 2

14 A1

ED

RT

13 ONC

PP

SU

R 12 V+

O

E

11 NC

BL

HI-201 (PLCC)

TOP VIEW

A1

A2 1

HI-201 (CERDIP, PDIP, SOIC)

TOP VIEW

A4

HI-200 (PDIP)

TOP VIEW

OUT1

Pinouts

Schematic Diagrams

TTL/CMOS REFERENCE CIRCUIT VREF CELL

HI-200

TTL/CMOS REFERENCE CIRCUIT VREF CELL

HI-201

V+

V+

R6

300

R2

5K

QP2

QP1

QP3

QP4

MP13

QP5

QN2

GND

QN2

VLL

GND

MN15

MN16

MN17

V-

R7

100K

VREF

QN4

QP5

TO P2

R3

24.2K

D3

R5

7.9K

QP4

QN1

MN14

R4

5.4K

QP3

MP13

TO P2

R3

24.2K

QP2

QP1

VREF

QN4

QN1

D3

R6

600

R2

5K

MN14

R4

5.4K

MP14

QP6

MN15

V-

VLL

QN3

R5

7.9K

MN16

MN17

R7

100K

GND

GND

FN3121 Rev 9.00

September 15, 2015

Page 2 of 11

�HI-200, HI-201

Schematic Diagrams

(Continued)

SWITCH CELL

A’

QN11

V+

INPUT

QN12

QP11

OUTPUT

QN13

V-

QP12

A’

DIGITAL INPUT BUFFER AND LEVEL SHIFTER

V+

QP3

QP1

QP5

QP4

A’

V+

QN1

D1

QP6

QP7

QN6

QN7

QP8

QP10

QP9

TO VLL

TO VREF

200

QN8

D2

QN9

QN10

QP2

A

VA’

QN2

QN4

QN5

QN3

V-

FN3121 Rev 9.00

September 15, 2015

Page 3 of 11

�HI-200, HI-201

Absolute Maximum Ratings

Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . . . 44V (22)

VREF to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20V, -5V

Digital Input Voltage . . . . . . . . . . . . . . . . . . . . . . (V+) +4V to (V-) -4V

Analog Input Voltage (One Switch) . . . . . . . . . . (V+) +2V to (V-) -2V

Thermal Resistance (Typical, Note 1)

JA (oC/W)

JC (oC/W)

CERDIP Package . . . . . . . . . . . . . . . . .

75

20

PLCC Package. . . . . . . . . . . . . . . . . . .

80

N/A

PDIP Package* . . . . . . . . . . . . . . . . . .

95

N/A

SOIC Package . . . . . . . . . . . . . . . . . . .

110

N/A

Maximum Storage Temperature. . . . . . . . . . . . . . . . -65oC to 150oC

Maximum Junction Temperature (Hermetic Packages) . . . . . 175oC

Maximum Junction Temperature (Plastic Packages). . . . . . . 150oC

Maximum Lead Temperature (Soldering, 10s). . . . . . . . . . . . 300oC

(PLCC and SOIC - Lead Tips Only)

Operating Conditions

Temperature Ranges

HI-201-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

HI-201-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC

HI-200-5, HI-201-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 75oC

HI-201-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in reflow solder processing

applications.

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

Supplies = +15V, -15V; VREF = Open; VAH (Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.8V

-2

-4, -5, -9

TEMP

(oC)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

HI-200

25

-

240

500

-

240

-

ns

HI-201

25

-

185

500

-

185

-

ns

Full

-

1000

-

-

1000

-

ns

HI-200

25

-

330

500

-

500

-

ns

HI-201

25

-

220

500

-

220

-

ns

Full

-

1000

-

-

1000

-

ns

HI-200

25

-

70

-

-

70

-

dB

HI-201

25

-

80

-

-

80

-

dB

Input Switch Capacitance, CS(OFF)

25

-

5.5

-

-

5.5

-

pF

Output Switch Capacitance, CD(OFF)

25

-

5.5

-

-

5.5

-

pF

Output Switch Capacitance, CD(ON)

25

-

11

-

-

11

-

pF

Digital Input Capacitance, CA

25

-

5

-

-

5

-

pF

Drain-to-Source Capacitance, CDS(OFF)

25

-

0.5

-

-

0.5

-

pF

Input Low Threshold, VAL

Full

-

-

0.8

-

-

0.8

V

Input High Threshold, VAH

Full

2.4

-

-

2.4

-

-

V

Full

-

-

1.0

-

-

1.0

A

Full

-15

-

+15

-15

-

+15

V

25

-

55

70

-

55

80

Full

-

80

100

-

72

100

PARAMETER

TEST

CONDITIONS

DYNAMIC CHARACTERISTICS

Switch ON Time, tON

Switch OFF Time, tOFF

Off Isolation

(Note 4)

DIGITAL INPUT CHARACTERISTICS

Input Leakage Current (High or Low), IA

(Note 3)

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, VS

ON Resistance, rON

FN3121 Rev 9.00

September 15, 2015

(Note 2)

Page 4 of 11

�HI-200, HI-201

Electrical Specifications

Supplies = +15V, -15V; VREF = Open; VAH (Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.8V (Continued)

TEST

CONDITIONS

-2

-4, -5, -9

TEMP

(oC)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

-

500

-

-

250

nA

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

35

500

-

35

250

nA

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

-

500

-

-

250

nA

25

-

15

-

-

15

-

mW

Full

-

-

60

-

-

60

mW

25

-

0.5

-

-

0.5

-

mA

Full

-

-

2.0

-

-

2.0

mA

25

-

0.5

-

-

0.5

-

mA

Full

-

-

2.0

-

-

2.0

mA

PARAMETER

OFF Input Leakage Current, IS(OFF)

OFF Output Leakage Current, ID(OFF)

ON Leakage Current, ID(ON)

(Note 6)

(Note 6)

(Note 6)

POWER SUPPLY CHARACTERISTICS (Note 5)

Power Dissipation, PD

Current, I+

Current, I-

NOTES:

2. VOUT = 10V, IOUT = 1mA.

3. Digital Inputs are MOS gates: typical leakage is < 1nA.

4. VA = 5V, RL = 1k, CL = 10pF, VS = 3VRMS , f = 100kHz.

5. VA = +3V or VA = 0V for Both Switches.

6. Refer to Leakage Current Measurements (Figure 2).

Test Circuits and Waveforms

TA = 25oC, VSUPPLY = ±15V, VAH = 2.4V, VAL = 0.8V and VREF = Open

1mA

V

V2

2

r ON = ------------1mA

IN

OUT

VIN

FIGURE 1A. ON RESISTANCE TEST CIRCUIT

FN3121 Rev 9.00

September 15, 2015

Page 5 of 11

�HI-200, HI-201

Test Circuits and Waveforms

TA = 25oC, VSUPPLY = ±15V, VAH = 2.4V, VAL = 0.8V and VREF = Open (Continued)

80

100

V+ = +10V

V- = -10V

VIN = 0V

60

ON RESISTANCE ()

ON RESISTANCE ()

70

50

40

30

20

V+ = +12.5V

V- = -12.5V

50

V+ = +15V

V- = -15V

10

0

-50

-25

0

25

50

75

100

125

TEMPERATURE (oC)

FIGURE 1B. ON RESISTANCE vs TEMPERATURE

0

-15

-10

-5

0

5

ANALOG SIGNAL LEVEL (V)

10

15

FIGURE 1C. HI-200 ON RESISTANCE vs ANALOG SIGNAL

LEVEL

FIGURE 1. ON RESISTANCE

IS(OFF)

100

A

ID(OFF)

IN

OUT

A

14V

+ 14V

CURRENT (nA)

IS(OFF) / ID(OFF)

10

FIGURE 2B. OFF LEAKAGE CURRENT TEST CIRCUIT

ID(ON)

IN

1.0

OUT

A

0.1

25

50

75

100

TEMPERATURE (oC)

ID(ON)

14V

125

FIGURE 2A. LEAKAGE CURRENT vs TEMPERATURE

FIGURE 2C. ON LEAKAGE CURRENT TEST CIRCUIT

FIGURE 2. LEAKAGE CURRENTS

90

SWITCH CURRENT (mA)

80

70

60

50

40

30

20

IN

10

0

OUT

I

HI-201

0

1

2

3

4

5

6

7

VIN

VOLTAGE ACROSS SWITCH (V)

FIGURE 3A. SWITCH CURRENT vs VOLTAGE

FIGURE 3B. TEST CIRCUIT

FIGURE 3. SWITCH CURRENT

FN3121 Rev 9.00

September 15, 2015

Page 6 of 11

�HI-200, HI-201

Test Circuits and Waveforms

DIGITAL

INPUT

TA = 25oC, VSUPPLY = ±15V, VAH = 2.4V, VAL = 0.8V and VREF = Open (Continued)

VAH = 4V

50%

50%

VAL = 0V

tON

tOFF

80%

SWITCH

OUTPUT

80%

0V

FIGURE 4A. MEASUREMENT POINTS

VA

VA

OUTPUT

OUTPUT

VA = 0 to 15V

Vertical: 5V/Div.

Horizontal: 100ns/Div.

VA = 0 to 4V

Vertical: 2V/Div.

Horizontal: 100ns/Div.

FIGURE 4B. WAVEFORMS WITH TTL COMPATIBLE LOGIC

INPUT

FIGURE 4C. WAVEFORMS WITH CMOS COMPATIBLE LOGIC

INPUT

FIGURE 4. SWITCH tON AND tOFF

140

OFF ISOLATION (dB)

120

100

80

RL = 1k

60

40

20

0

100Hz

1kHz

10kHz

100kHz

1MHz

FREQUENCY (Hz)

FIGURE 5. HI-201 OFF ISOLATION vs FREQUENCY

For more information see Application Notes AN520, AN521, AN531, AN532 and AN557.

FN3121 Rev 9.00

September 15, 2015

Page 7 of 11

�HI-200, HI-201

Application Information

Single Supply Operation

The switch operation of the HI-200/201 is dependent upon

an internally generated switching threshold voltage

optimized for 15V power supplies. The HI-200/201 does not

provide the necessary internal switching threshold in a single

supply system. Therefore, if single supply operation is

required, the HI-300 series of switches is recommended.

The HI-300 series will remain operational to a minimum +5V

single supply.

Switch performance will degrade as power supply voltage is

reduced from optimum levels (15V). So it is recommended

that a single supply design be thoroughly evaluated to

ensure that the switch will meet the requirements of the

application.

For further information see Application Notes AN520,

AN557, AN1033 and AN1034.

FN3121 Rev 9.00

September 15, 2015

Page 8 of 11

�HI-200, HI-201

Die Characteristics

METALLIZATION:

PASSIVATION:

Type: CuAl

Thickness: 16kÅ 2kÅ

Type: Nitride over Silox

Nitride Thickness: 3.5kÅ 1kÅ

Silox Thickness: 12kÅ 2kÅ

WORST CASE CURRENT DENSITY:

2 x 105 A/cm2 at 25mA

Metallization Mask Layout

HI-200

GND

A2

2

IN 2

OUT 2

1

10

9

3

4

5

V-

FN3121 Rev 9.00

September 15, 2015

V+

A1

6

8

IN 1

7

OUT 1

VREF

Page 9 of 11

�HI-200, HI-201

Die Characteristics

METALLIZATION:

PASSIVATION:

Type: CuAl

Thickness: 16kÅ 2kÅ

Type: Nitride over Silox

Nitride Thickness: 3.5kÅ 1kÅ

Silox Thickness: 12kÅ 2kÅ

WORST CASE CURRENT DENSITY:

2 x 105 A/cm2 at 25mA

Metallization Mask Layout

HI-201

OUT 1

2

IN 1

3

V-

4

GND

5

IN 4

6

OUT 4

7

A1

A2

1

16

8

9

A4

A3

15

OUT 2

14

IN 2

13

V+

12

VREF

11

IN 3

10

OUT 3

© Copyright Intersil Americas LLC 1999-2015. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN3121 Rev 9.00

September 15, 2015

Page 10 of 11

�HI-200, HI-201

Revision History

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make

sure that you have the latest revision.

DATE

REVISION

September 15, 2015

FN3121.9

CHANGE

- Updated Ordering Information Table on page 1.

- Added Revision History.

- Added About Intersil Verbiage.

About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products

address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product

information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

FN3121 Rev 9.00

September 15, 2015

Page 11 of 11

�