ICS9250-10

Integrated

Circuit

Systems, Inc.

Frequency Timing Generator for Pentium II Systems

General Description

The ICS9250-10 is a single chip clock for Intel Pentium II.

It provides all necessary clock signals for such a system.

Spread spectrum may be enabled through I2C programming.

Spread spectrum typically reduces EMI by 8dB to 10 dB.

This simplifies EMI qualification without resorting to board

design iterations or costly shielding. The ICS9250-10

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Block Diagram

Features

Generates the following system clocks:

- 3 CPU (2.5V) 66.6/100 MHz (up to 133MHz through

I2C selection)

- 9 SDRAM (3.3V) up to 133MHz

- 8 PCI (3.3 V) @33.3MHz

- 2 IOAPIC (2.5V) @16.67 or 33.3MHz

- 2 Hublink clocks (3.3 V) @ 66.6 MHz

- 2 USB (3.3V) @ 48 MHz ( Non spread spectrum)

- 1 REF (3.3V) @ 14.318 MHz

Supports spread spectrum modulation ,

down spread 0 to -0.5%

I2C support for power management

Efficient power management scheme through PD#

Uses external 14.138 MHz crystal

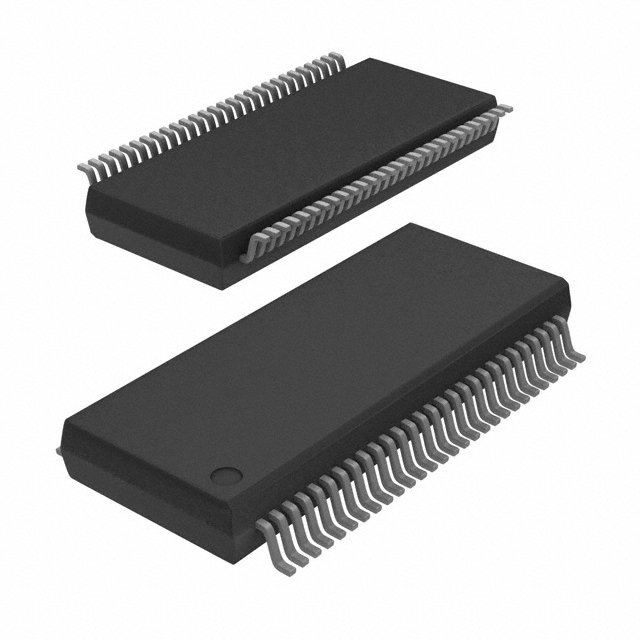

Pin Configuration

56-Pin 300 mil SSOP

*60K ohm pull-up to VDD on indicated inputs.

Power Groups

Pentium II is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

9250-10 Rev K 12/14/01

VDD0, GND0 = REF & Crystal

VDD1, GND1 = 3V66 [1:0]

VDD2, GND2 = PCICLK[7:0]

VDD3, GND3 = PLL core

VDD4, GND4 = 48MHz [1:0]

VDD5, GND5 = SDRAM_F, SDRAM [7:0]

VDDL0, GNDL0 = CPUCLK [2:0]

VDDL1, GNDL1 = IOAPIC [1:0]

�ICS9250-10

Pin Descriptions

PIN NUMBER

3

X1

IN

4

X2

OUT

DESCRIPTION

Latched input at Power On. this determines the IOAPIC frequency.

When a "0" is latched, IOAPIC Freq=16.67MHz

When "1" is latched, IOAPIC Freq=33.3MHz

This pin has a 60K internal pull-up.

3.3V, 14.318MHz reference clock output.

Crystal input, has internal load cap (33pF) and feedback

resistor from X2

Crystal output, nominally 14.318MHz. Has internal load

cap (33pF)

5, 6, 14, 17, 23,

24, 35, 41, 47

GND (0:5)

PWR

Ground pins for 3.3V supply

8, 7

3V66 [1:0]

OUT

3 . 3 V F i xe d 6 6 M H z c l o c k o u t p u t s f o r H U B

PWR

3.3V power supply

OUT

3.3V PCI clock outputs, with Synchronous CPUCLKS

OUT

3 . 3 V F i xe d 4 8 M H z c l o c k o u t p u t s f o r U S B

1

P I N NA M E

FREQ_APIC

REF0

2, 9, 10, 21,

VDD (0:5)

22, 27, 33, 38, 44

20,19,18,16,

PCICLK[7:0]

15,13,12,11

TYPE

IN

OUT

25, 26

48MHz (0:1)

28, 29

FS (0:1)

IN

Function Select pins. Determines CPU frequency, all output

functionality. Please refer to Functionality table on page 3.

30

SDATA

IN

Data input for I2C serial input.

31

SCLK

IN

Clock input of I2C input

32

PD#

IN

36, 37, 39, 40, 42,

SDRAM [7:0]

43, 45, 46

OUT

Asynchronous active low input pin used to power down the device

into a low power state. The internal clocks are disabled and the

VCO and the crystal are stopped. The latency of the power down

will not be greater than 3ms.

3.3V output running 100MHz. All SDRAM outputs can be turned

off through I2C

34

SDRAM_F

OUT

3.3V free running 100MHz SDRAM not affected by I2C

56,48

GNDL [1:0]

PWR

Ground for 2.5V power supply for CPU & APIC

CPUCLK [2:0]

OUT

2.5V Host bus clock output. 66MHz or 100MHz depending on FS

(0:1) pins Refer page 3.

51, 53

VDDL (0:1)

PWR

2.5V power suypply for CPU & IOAPIC

54, 55

IOAPIC [1:0]

OUT

2.5V clock outputs running at 16.67MHz or 33.3MHz.

49,50,52

2

�ICS9250-10

Functionality Table

FS1

FS0

CPU

SDRAM

3V66

PCICLK

48MHz

REF0

IOAPIC

0

0

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

0

1

TCLK/2

TCLK/4

TCLK/4

TCLK/8

TCLK/2

TCLK

TCLK/16

1

0

66 MHz

100 MHz

66 MHz

33 MHz

48 MHz

14.318MHz

16.67MHz

1

1

100 MHz

100 MHz

66 MHz

33MHz

48 MHz

14.318MHZ

16.67MHz

Clock Enable Configuration

PD#

CPUCLK

SDRAM

IOAPIC

66MHz

PCICLK

REF,

48MHz

Osc

VCOs

0

LOW

LOW

LOW

LOW

LOW

LOW

OFF

OFF

1

ON

ON

ON

ON

ON

ON

ON

ON

Select Functions

FS1

FS0

Notes

0

0

Tristate

0

1

Test Mode

1

0

Active CPU = 66MHz

1

1

Active CPU = 100MHz

3

Notes

Tristate

Test Mode

�ICS9250-10

Power Down Waveform

Note

1. After PD# is sampled active (Low) for 2 consective rising edges of CPUCLKs, all

the output clocks are driven Low on their next High to Low tranistiion.

2. Power-up latency