DATASHEET

ISL6536

FN9114

Rev 3.00

Jan 25, 2011

Four Channel Supervisory IC

The ISL6536 is a four channel supervisory IC designed to

monitor voltages >, = 0.7V. This IC bias range is from 2.7V

to 4V but can supervise any positive voltage using an

external resistor divider to translate to a lower voltage for

comparison to the internal 0.63V reference.

Once properly biased and enabled when all four voltage

monitor (VMON) inputs are satisfied the PGOOD output will

be immediately released to go high to signal that voltage is

valid on all four rails. Subsequently when the monitored

voltage on any rail drops below its user defined threshold

point, the PGOOD output is pulled low. Each rail’s VMON

point is independently adjustable with a resistor divider. The

PGOOD output is guaranteed to be valid with IC bias lower

than 1V. The VMON inputs will ignore 30µs transients on the

monitored supplies. The PGOOD output is an open-drain to

allow ORing of multiple signals and interfacing to a range of

logic levels. The ENABLE input provides for a reset of the

PGOOD output when it is pulled down below 0.5V. With an

internal 10uA pull-up to VDD it can be signalled with

common logic or pulled to ground with a push button switch.

• Adjustable undervoltage lockout for each supply

• Active high PGOOD Output

• Guaranteed PGOOD Valid to Falling VDD < 1V

• VMON Glitch Immunity

• Pb-Free (RoHS Compliant)

Applications

• Graphics Cards

• Multi voltage DSPs and Processors

• µP Voltage Monitoring

• Embedded Control Systems

• Intelligent Instruments

• Medical Equipment

• Network Routers

• Portable Battery-Powered Equipment

V1 in

V2 in

V3 in

Typical Application Schematic

V4 in

Features

• Set-Top Boxes

• Telecommunications Systems

ISL6536

*OPT

1

VDD

VMON1 8

2

PGD

VMON2 7

3

EN

VMON3 6

4

GND

VMON4 5

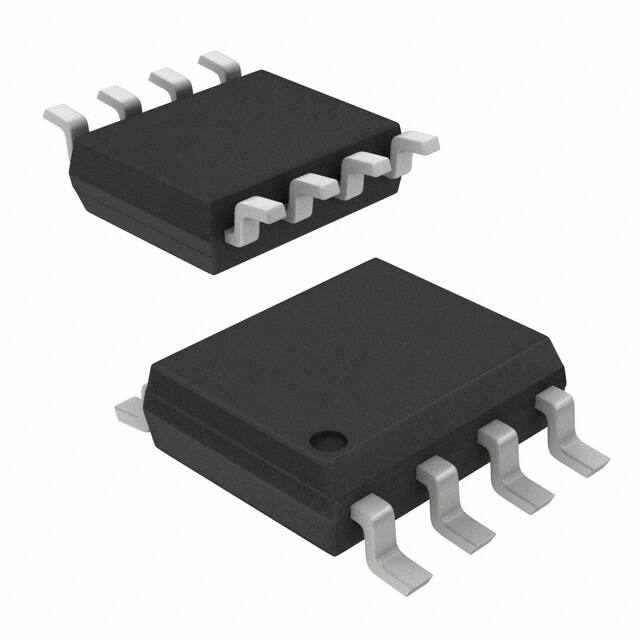

Ordering Information

PART NUMBER

(Note 2)

ISL6536IBZ

PART

MARKING

6536 IBZ

TEMP. RANGE

(°C)

-40 to +85

PACKAGE

(Pb-free)

8 Ld SOIC

PKG.

DWG. #

M8.15

NOTES:

1. Add “-T*” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin

plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

FN9114 Rev 3.00

Jan 25, 2011

Page 1 of 7

�ISL6536

Pin Descriptions

ISL6536

PIN NAME

FUNCTION DESCRIPTION

1

VDD

2

PGOOD

PGOOD is the boolean AND function of all the UV inputs being satisfied. This is an open drain output and

can be pulled high to the appropriate level with an external resistor. Additionally a 20k pull up to VDD is

provided internally.

3

ENABLE

Enabling input for supervisory function. Has a 10µA pull-up to VDD

4

GND

5-8

VMON1

VMON2

VMON3

VMON4

Bias IC from nominal 2.7V to 4V

IC ground

These inputs provide for a programmable monitored voltage threshold referenced to an internal 0.63V

reference. These inputs have a 30µs glitch filter to prevent transient upsets from being recognized by

PGOOD.

VDD

EN

10µA

VMON1

20k

VMON2

FALLING EDGE

GLITCH FILTER

PGOOD

VMON3

VMON4

+

ISL6536

633mV

-

FN9114 Rev 3.00

Jan 25, 2011

Page 2 of 7

�ISL6536

Absolute Maximum Ratings

Thermal Information

VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5.5V

VMON, PGOOD, ENABLE. . . . . . . . . . . . . . . . . -0.3V to VDD+0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4kV (HBM)

Thermal Resistance (Typical, Note 1)

JA (°C/W)

8 Ld SOIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

108

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . 150°C

Maximum Storage Temperature Range . . . . . . . . . . -65°C to 150°C

Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Operating Conditions

VDD Supply Voltage Range. . . . . . . . . . . . . . . . . . . . . +2.7V to +4V

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . . .-40°C to 85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

1. JA is measured in free air with the component mounted on a high effective thermal conductivity test board. See Tech Brief TB379 for details.

2. All voltages are relative to GND, unless otherwise specified.

Electrical Specifications

PARAMETER

Nominal VDD = 3.3V, TA = TJ = -40°C - 85°C, Unless Otherwise Specified.

TYP

MAX

(Note 3)

UNIT

VMON > VMON_L2H

165

1000

µA

SYMBOL

TEST CONDITIONS

MIN

(Note 3)

BIAS

IC Supply Current

IVDD

VDD Power On

VDD_L2H

VDD low to high

2.6

V

VDD Power On Reset

VDD_POR

VDD high to low

2.4

V

Pull-Down Current

PGpd

VPGOOD = 0.5V

2

mA

Pull-Up Resistance

PGpu

20

k

Output Low

VPGl

PGOOD

Delay from VMON Rising

tPGdelVMON

VDD = 1V

0.05

Last valid input = Vth to PG release

0.1

V

2

µs

Delay from EN Rising

tPGdelENR

EN high to PG release

0.05

µs

Delay from EN Falling

tPGdelENF

EN low to PG pulling low

0.015

µs

ENABLE

Rising Threshold

Threshold Hysteresis

Pull-up Current

VEN

ENABLE Low to High Threshold

0.4VDD

VEN_HYS

0.5VDD

0.6VDD

V

0.065

V

10

µA

IENpu

VEN = 0.5V

Falling Threshold

3.3VMON_H2L

TJ = +25°C

Falling Threshold Temp Coeff.

3.3VMON_TC

Hysteresis

VVMON_HYS

-

10

-

mV

Range

VMON_RNG

-

8

-

mV

-

30

-

µs

VMON Input

Glitch Filter Duration

TFIL

0.623

0.633

0.643

100

VMON glitch to PGOOD low Filter

V

uV/°C

NOTE:

3. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

FN9114 Rev 3.00

Jan 25, 2011

Page 3 of 7

�ISL6536

ISL6536 Description and Operation

The ISL6536 is a four channel supervisory IC designed to

monitor multiple voltages greater than 0.7V. This IC is

suitable for both microprocessors or industrial system

applications.

Upon VDD bias power up the PGOOD output is held low

with VDD as low as 0V. Once biased to 2.6V and enabled

the IC continuously monitors from one to four voltages

independently through external resistor dividers comparing

each VMON pin voltage to an internal 0.63V reference.

Once all VMON input voltages rise above 0.63V the PGOOD

(power good) output signal is released and is pulled high via

an external pull resistor to indicate that the power conditions

have been met. The PGOOD output is an open-drain to

allow ORing of the signals and interfacing to a wide range of

logic levels.

Once any VMON input falls below 0.63V the PGOOD output

is pulled low, the VMON inputs are designed to reject fast

transients (30µs).

If less than four voltages are being monitored, connect the

unused VMON pins to VDD.

The PGOOD pin has an internal 20k pull-up to VDD

making an external pull-up resistor unnecessary.

Figure 1 illustrates the operational timing diagram.

4/5 EN/VMON INPUTS HIGH

VTH

LAST EN/VMON INPUT

TFIL

很抱歉,暂时无法提供与“ISL6536IB”相匹配的价格&库存,您可以联系我们找货

免费人工找货