DATASHEET

X9119

FN8162

Rev 5.00

July 5, 2016

1024 Tap, Low Power, 2-Wire Interface, Digitally Controlled (XDCP™)

Potentiometer

The X9119 integrates a single digitally controlled

potentiometer (XDCP™) on a monolithic CMOS integrated

circuit.

Features

The digital controlled potentiometer is implemented using

1023 resistive elements in a series array. Between each

element are tap points connected to the wiper terminal

through switches. The position of the wiper on the array is

controlled by the user through the 2-wire bus interface. The

potentiometer has associated with it a volatile Wiper Counter

Register (WCR) and four nonvolatile data registers that can be

directly written to and read by the user. The contents of the

WCR controls the position of the wiper on the resistor array

through the switches. Power-up recalls the contents of the

default data register (DR0) to the WCR.

• 2-Wire serial interface for write, read, and

transfer operations of the potentiometer

• 1024 resistor taps – 10-bit resolution

The XDCP™ can be used as a 3-terminal potentiometer or as a

2-terminal variable resistor in a wide variety of applications

including control, parameter adjustments and signal

processing.

• Wiper resistance, 40Ω typical at VCC = 5V

• Four nonvolatile data registers

• Nonvolatile storage of multiple wiper positions

• Power-on recall, loads saved wiper position on power-up.

• Standby current > R2

VO = G VS

G = - R2/R1

FIGURE 21. INVERTING AMPLIFIER

FIGURE 22. EQUIVALENT L-R CIRCUIT

C

R2

–

+

R1

–

} RA

+

} RB

FREQUENCY µ R1, R2, C

AMPLITUDE µ RA, RB

FIGURE 23. FUNCTION GENERATOR

FN8162 Rev 5.00

July 5, 2016

Page 16 of 18

�X9119

Revision History

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted.

Please go to the web to make sure that you have the latest revision.

DATE

REVISION

July 5, 2016

FN8162.5

CHANGE

Updated entire datasheet applying Intersil’s new standards.

Updated title.

Updated Ordering Information table by removing obsolete parts, updating Note 1 and adding Note 3.

Removed Lead temperature (soldering, 10s) from the Thermal Information section on page 10.

Updated Absolute Linearity maximum specification from “±1” to “±1.5”.

Added Revision History and About Intersil sections.

Updated POD to the latest revision changes are as follows:

Updated drawing to remove table and added land pattern.

About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products

address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product

information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2005-2016. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN8162 Rev 5.00

July 5, 2016

Page 17 of 18

�X9119

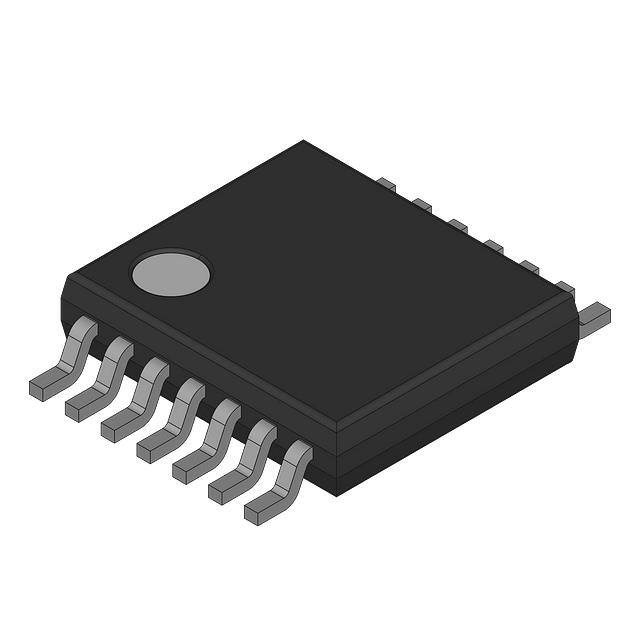

Package Outline Drawing

M14.173

14 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP)

Rev 3, 10/09

A

1

3

5.00 ±0.10

14

SEE

DETAIL "X"

8

6.40

PIN #1

I.D. MARK

4.40 ±0.10

2

3

1

0.20 C B A

7

B

0.65

0.09-0.20

TOP VIEW

END VIEW

1.00 REF

0.05

H

C

0.90 +0.15/-0.10

1.20 MAX

SEATING

PLANE

0.25 +0.05/-0.06

0.10 C

0.10

GAUGE

PLANE

0.25

5

0°-8°

0.05 MIN

0.15 MAX

CBA

SIDE VIEW

0.60 ±0.15

DETAIL "X"

(1.45)

NOTES:

1. Dimension does not include mold flash, protrusions or gate burrs.

(5.65)

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

2. Dimension does not include interlead flash or protrusion. Interlead

flash or protrusion shall not exceed 0.25 per side.

3. Dimensions are measured at datum plane H.

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

5. Dimension does not include dambar protrusion. Allowable protrusion

shall be 0.80mm total in excess of dimension at maximum material

condition. Minimum space between protrusion and adjacent lead is 0.07mm.

(0.65 TYP)

(0.35 TYP)

TYPICAL RECOMMENDED LAND PATTERN

FN8162 Rev 5.00

July 5, 2016

6. Dimension in ( ) are for reference only.

7. Conforms to JEDEC MO-153, variation AB-1.

Page 18 of 18

�

很抱歉,暂时无法提供与“X9119TV14”相匹配的价格&库存,您可以联系我们找货

免费人工找货