®

RT8463

High Voltage Multi-Topology LED Driver

General Description

Features

The RT8463 is a current mode PWM regulator for LED

driving applications. With a 2A power switch, wide input

voltage (4.5V to 50V) and output voltage (up to 50V)

ranges, the RT8463 can operate in any of the three

common topologies : Buck, Boost or Buck-Boost.

With 470kHz operating frequency, the size of the external

PWM inductor and input/output capacitors can be

minimized. High efficiency is achieved by a 100mV current

sensing control.

Brightness dimming can be controlled from either analog

or PWM signal. A unique built-in clamping comparator

and filtering resistor allow easy low noise analog dimming

conversion from PWM signal with only one external

capacitor.

High Voltage : VIN Up to 50V, VOUT Up to 50V

Buck, Boost or Buck-Boost Operation

Built-In 2A Power Switch

Current Mode PWM Control

470kHz Fixed Switching Frequency

Easy Dimming : Analog, PWM Digital or PWM

Converting to Analog with One External Capacitor

Adjustable Soft-Start to Avoid Inrush Current

Adjustable Over Voltage Protection to Limit Output

Voltage

Thermal Shutdown

Under Voltage Lockout

RoHS Compliant and Halogen Free

Applications

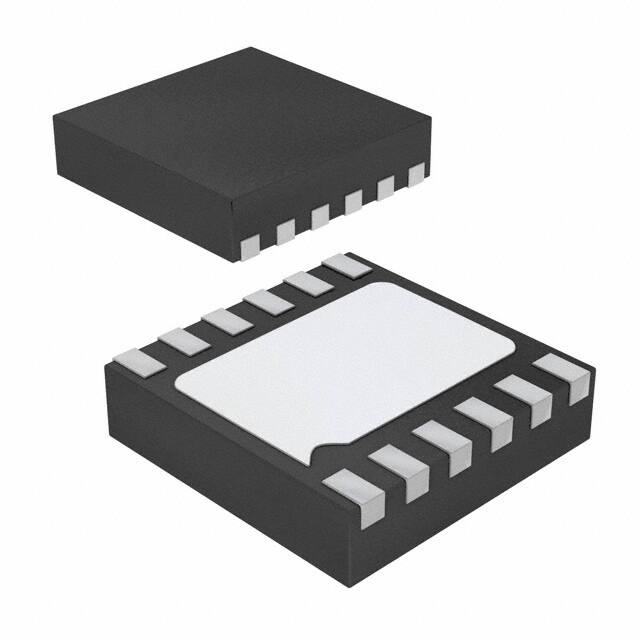

The RT8463 is available in the TSSOP-14 (Exposed pad)

and WDFN-12L 3x3 packages.

GPS, Portable DVD Backlight

Desk Lights and Room Lighting

Industrial Display Backlight

Ordering Information

Marking Information

RT8463

RT8463GCP

Package Type

CP : TSSOP-14 (Exposed Pad-Option 1)

QW : WDFN-12L 3x3 (W-Type)

(Exposed Pad-Option 1)

RT8463GCP : Product Number

RT8463

GCPYMDNN

Lead Plating System

G : Green (Halogen Free and Pb Free)

RT8463GQW

98 = : Product Code

Note :

YMDNN : Date Code

98=YM

DNN

Richtek products are :

YMDNN : Date Code

RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

Suitable for use in SnPb or Pb-free soldering processes.

Simplified Application Circuit

C1

5V

PWM

Dimming Control

R1

C2

C3

C6

RT8463

VCC

EN

DCTL

SW

ISP

ISN

VC

SS

ACTL

OVP

C4

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

D1

L

VIN

VOUT

R2

R3

CREG

C5

VOUT

R4

GND

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

1

�RT8463

Pin Configuration

(TOP VIEW)

ISP

ISN

VC

ACTL

DCTL

EN

GND

14

2

13

3

12

4

GND

5

11

10

6

15

7

9

8

VCC

CREG

SW

GND

SS

OVP

GND

ISP

ISN

VC

ACTL

DCTL

EN

TSSOP-14 (Exposed Pad)

1

2

3

4

5

6

GND

13

12

11

10

9

8

7

VCC

CREG

SW

GND

SS

OVP

WDFN-12L 3x3

Functional Pin Description

Pin No.

Pin Name

TSSOP-14

WDFN-12L 3x3

(Exposed Pad)

Pin Function

1

1

ISP

Positive current sense input.

2

2

ISN

Negative current sense input. Voltage threshold between ISP and

ISN is 100mV.

3

3

VC

Compensation node for PWM boost converter loop.

4

4

ACTL

Analog dimming control input. Effective programming range is

between 0.2V and 1.2V.

5

5

DCTL

Digital dimming control input. By adding a 0.47F filtering capacitor

on the ACTL pin, the PWM dimming signal on DCTL pin will be

averaged and converted into analog dimming signal on the ACTL

pin. VACTL = 1.2V x PWM dimming duty cycle.

6

6

EN

Enable control input (active high). When this pin is low, the chip is

in shutdown mode.

7, 8, 11, 15

9,

GND

(Exposed Pad) 13 (Exposed Pad)

Ground. The exposed pad must be soldered to a large PCB and

connected to GND for maximum power dissipation.

Over voltage protection sense input. The PWM Boost converter

turns off when VOVP goes higher than 1.2V.

Soft-start time setting. A minimum 10nF capacitor is required for

soft-start.

Switch node of PWM boost converter.

9

7

OVP

10

8

SS

12

10

SW

13

11

CREG

Regulator output for internal circuit. Placed a 1F capacitor to

stabilize the 5V output regulator.

14

12

VCC

Power supply voltage input. For good bypass, a low ESR capacitor

is required.

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

2

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

Functional Block Diagram

SW

VCC

4.5V

5V

LDO

OSC

-

S

+

CREG

R

OVP

+

1.2V

EN

R

+

+

Shutdown

-

-

1.4V

VC

ISN

ISP

GM

+

5µA

SS

1.2V

+

DCTL

+

-

-

GND

ACTL

VISP – VISN

(mV)

100

0

0.2

1.2

VACTL (V)

Figure 1

Operation

The RT8463 is specifically designed to be operated in

Buck, Boost and Buck-Boost converter applications. This

device uses a fixed frequency, current mode control

scheme to provide excellent line and load regulations. The

control loop has a current sense amplifier to sense the

voltage between the ISP and ISN pins and provides an

output voltage at the VC pin. A PWM comparator then

turns off the internal power switch when the sensed power

switch current exceeds the compensated VC pin voltage.

The power switch will not reset by the oscillator clock in

each cycle. If the comparator does not turn off the switch

in a cycle, the power switch is on for more than a full

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

switching period until the comparator is tripped. In this

manner, the programmed voltage across the sense

resistor is regulated by the control loop.

The current through the sense resistor is set by the

programmed voltage and the sense resistance. The voltage

across the sense resistor can be programmed by either

the analog or PWM signals at the ACTL pin, or the PWM

signal at the DCTL pin.

The RT8463 provides protection functions which include

over temperature, input voltage under voltage, output

voltage over voltage, and switch current limit.

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

3

�RT8463

Absolute Maximum Ratings

(Note 1)

Supply Input Voltage, VCC ------------------------------------------------------------------------------------ −0.3V to 60V

SW Pin Voltage at Switching Off, ISP, ISN ---------------------------------------------------------------- −0.3V to 60V

DCTL, ACTL, CREG, OVP Pin Voltage -------------------------------------------------------------------- −0.3V to 5.5V (Note 2)

EN Pin Voltage --------------------------------------------------------------------------------------------------- −0.3V to 20V

Power Dissipation, PD @ TA = 25°C

TSSOP-14 (Exposed Pad) ------------------------------------------------------------------------------------ 3.32W

WDFN-12L 3x3 --------------------------------------------------------------------------------------------------- 3.28W

Package Thermal Resistance (Note 3)

TSSOP-14 (Exposed Pad), θJA ------------------------------------------------------------------------------ 30.1°C/W

TSSOP-14 (Exposed Pad), θJC ------------------------------------------------------------------------------ 7.5°C/W

WDFN-12L 3x3, θJA --------------------------------------------------------------------------------------------- 30.5°C/W

WDFN-12L 3x3, θJC --------------------------------------------------------------------------------------------- 7.5°C/W

Junction Temperature ------------------------------------------------------------------------------------------- 150°C

Lead Temperature (Soldering, 10 sec.) --------------------------------------------------------------------- 260°C

Storage Temperature Range ---------------------------------------------------------------------------------- −65°C to 150°C

ESD Susceptibility (Note 4)

HBM (Human Body Model) ------------------------------------------------------------------------------------ 2kV

MM (Machine Model) ------------------------------------------------------------------------------------------- 200V

Recommended Operating Conditions

(Note 5)

Supply Input Voltage, VCC ------------------------------------------------------------------------------------ 4.5V to 50V

Junction Temperature Range ---------------------------------------------------------------------------------- −40°C to 125°C

Ambient Temperature Range ---------------------------------------------------------------------------------- −40°C to 85°C

Electrical Characteristics

(VCC = 12V, No Load on any Output, TA = 25°C, unless otherwise specified)

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

4.5

5

5.5

V

mA

Overall

Regulator Output Voltage

VCREG

ICREG = 20mA

Supply Current

IVCC

VC 0.2V (Not Switching )

--

--

5

VIN Under Voltage Lockout

Threshold

VUVLO

VIN Rising

--

4.2

--

VIN Falling

--

3.8

--

Shutdown Current

ISHDN

VEN < 0.5V

--

--

15

EN Input Voltage

Logic-High

VEN_H

2

--

--

Logic-Low

VEN_L

--

--

0.5

VEN > 2V

--

--

1

VACTL 1.25V

96

100

102

VACTL = 1.2V

95

98

101

EN Input Current

V

A

V

A

Current Sense Amplifier

Input Threshold (VISP VISN)

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

4

mV

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

Input Current

IISP

VISP = 24V

--

200

--

A

Input Current

IISN

VISN = 24V

--

20

--

A

Output Current

IVC

2V > VC > 0.2V

--

10

--

A

--

0.2

--

V

VC Threshold for PWM Switch Off

LED Dimming

Analog Dimming ACTL Pin Input

Current

IACTL

0 VACTL 3V, DCTL Floating

--

--

2

A

LED Current On Threshold at

ACTL

VACTL_ON

(VISP VISN) = 100mV

--

1.2

1.33

V

LED Current Off Threshold at

ACTL

VACTL_OFF

--

0.2

0.25

V

DCTL Input Current

IDCTL

--

0.5

2

A

DCTL Input

Voltage

0.3V VDCTL 5V

Logic-High

VDCTL_H

2

--

--

Logic-Low

VDCTL_L

--

--

0.1

420

470

520

kHz

--

--

100

%

--

150

250

ns

--

0.3

0.5

2

2.5

--

A

1.15

1.2

1.25

V

V

PWM Boost Converter

Switching Frequency

fSW

Maximum Duty Cycle

D MAX

Minimum On-Time

(Note 6)

SW RDS(ON)

SW Current Limit

ILIM_SW

OVP and Soft-Start

OVP Threshold

VOVP

OVP Input Current

IOVP

VOVP 1.5V

--

--

50

nA

Soft-Start SS Pin Current

ISS

VSS 2.5V

--

5

8

A

Temperature Protection

Thermal Shutdown Temperature

TSD

--

150

--

C

Thermal Shutdown Hysteresis

TSD

--

20

--

C

Note 1. Stresses beyond those listed “Absolute Maximum Ratings” may cause permanent damage to the device. These are

stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in

the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may

affect device reliability.

Note 2. If connected with a 20kΩ serial resistor, ACTL and DCTL can go up to 40V.

Note 3. θJA is measured under natural convection (still air) at TA = 25°C with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard. θJC is measured at the

exposed pad of the package.

Note 4. Devices are ESD sensitive. Handling precaution is recommended.

Note 5. The device is not guaranteed to function outside its operating conditions.

Note 6. Guaranteed by design, not subjected to production test.

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

5

�RT8463

Typical Application Circuit

D1

VIN

4.5V to 50V

C1

RT8463

ISP

VCC

EN

5V

R4

GND

VC

R1

10k

CREG

SS

ACTL

C3

10nF

C2

3.3nF

R3

ISN

OVP

DCTL

PWM

Dimming control

R2

100mV

C6

C5

1µF

L

22µH

SW

C4

0.47µF

Figure 2. PWM to Analog Dimming Buck Configuration

D1

VIN

4.5V to 50V

C1

RT8463

ISP

VCC

Analog

Dimming

ACTL

ISN

DCTL

OVP

CREG

VC

R1

10k

C2

3.3nF

R3

R4

GND

EN

5V

R2

100mV

SS

C6

C5

1µF

L

15µH

SW

C3

10nF

Figure 3. Analog Dimming Buck Configuration

D1

VIN

4.5V to 50V

C1

RT8463

VCC

ISP

PWM

Dimming control

ACTL

ISN

OVP

5V

EN

DCTL

VC

R1

10k

C2

3.3nF

R3

GND

CREG

SS

C3

10nF

R2

100mV

R4

C6

C5

1µF

L

15µH

SW

Figure 4. PWM Dimming Buck Configuration Through ACTL Pin

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

6

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

L

15µH

VIN

4.5V to 50V

D1

C1

C6

1µF

RT8463

SW

VCC

EN

5V

CREG

VC

R1

10k

SS

C2

3.3nF

ACTL

C3

10nF

R2

100mV

ISP

ISN

GND

DCTL

PWM

Dimming control

VOUT

50V (Max.)

C5

1µF

R3

OVP

VOUT

R4

C4

0.47µF

Figure 5. PWM to Analog Dimming Boost Configuration

C6

D1

L

VIN

4.5V to 50V

15µH

C1

VOUT

50V (Max.)

RT8463

5V

VCC

SW

EN

ISP

DCTL

PWM

Dimming control

VC

R1

10k

SS

C2

3.3nF

ISN

GND

CREG

ACTL

C3

10nF

R2

100mV

C5

1µF

OVP

C4

0.47µF

R3

VOUT

R4

Figure 6. PWM to Analog Dimming Buck-Boost Configuration

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

7

�RT8463

Typical Operating Characteristics

Supply Current vs. Temperature

2.2

2.0

2.0

Supply Current (mA)

Supply Current (mA)

Supply Current vs. VCC

2.5

1.5

1.0

0.5

1.8

1.6

1.4

VCC = 12V

1.2

0.0

0

5

10

15

20

25

30

35

40

45

-50

50

-25

0

25

50

75

100

125

Temperature (°C)

VCC (V)

Shutdown Current vs. VCC

ISP-ISN Threshold vs. Temperature

8.0

130

ISP-ISN Threshold (mV)

Shutdown Current (μA)1

7.5

7.0

6.5

6.0

5.5

5.0

4.5

118

106

94

82

VIN = 12V

4.0

70

0

10

20

30

40

50

-50

-25

0

VCC (V)

Efficiency vs. Input Voltage

100

50

75

100

125

Efficiency vs. Input Voltage

100

Boost

Buck

95

Efficiency (%)

95

Efficiency (%)

25

Temperature (°C)

90

85

80

90

85

80

VOUT = 30V, IOUT = 210mA

75

VOUT = 15V, IOUT = 210mA

75

5

10

15

20

25

Input Voltage (V)

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

8

30

15

18

21

24

27

30

Input Voltage (V)

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

IOUT vs. VACTL

Efficiency vs. Input Voltage

100

240

Buck-Boost

210

180

90

I OUT (mA)

Efficiency (%)

95

85

150

120

90

60

80

30

VOUT = 15V, IOUT = 210mA

VOUT = 30V, IOUT = 210mA

0

75

4

6

8

10

12

14

16

18

0

20

0.3

0.6

0.9

1.2

1.5

VACTL (V)

Input Voltage (V)

VOVP vs. Temperature

IOUT vs. VDCTL

1.4

240

210

1.3

180

1.2

VOVP (V)

I OUT (mA)

150

120

90

1.1

1.0

60

0.9

30

VOUT = 30V, IOUT = 210mA, f = 100Hz

VCC = 12V

0.8

0

0

10

20

30

40

50

60

70

80

90

-50

100

-25

0

Frequency vs. VCC

50

75

100

125

SS Current vs. Temperature

480

6.2

470

5.8

SS Current (µA)

Frequency (kHz)1

25

Temperature (°C)

PWM Duty (%)

460

450

440

5.4

5.0

4.6

430

VCC = 12V

420

4.2

0

5

10

15

20

25

30

35

40

45

VCC (V)

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

50

-50

-25

0

25

50

75

100

125

Temperature (°C)

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

9

�RT8463

Power Off from VIN

Power On from VIN

IOUT

(200mA/Div)

IOUT

(200mA/Div)

VOUT

(20V/Div)

VOUT

(20V/Div)

VIN

(10V/Div)

VIN

(10V/Div)

Time (25ms/Div)

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

10

Time (250ms/Div)

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

Application Information

Loop Compensation

Output Over Voltage Setting

The RT8463 has an external compensation pin (VC)

allowing the loop response optimized for specific

application. An external resistor in series with a capacitor

is connected from the VC pin to GND to provide a pole

and a zero for proper loop compensation. The

recommended compensation resistance and capacitance

for the RT8463 are 10kΩ and 3.3nF.

The RT8463 is equipped with Over Voltage Protection

(OVP) function. When the voltage at OVP pin exceeds a

threshold of approximately1.2V, the power switch is turned

off. The power switch can be turned on again once the

voltage at OVP pin drops below 1.2V.

Soft-Start

The soft-start can be achieved by connecting a capacitor

from the SS pin to GND. The built-in soft-start circuit

reduces the start-up current spike and output voltage

overshoot. The soft-start time is determined by the external

capacitor charged by an internal 5μA constant charging

current. The SS pin directly limits the slew rate of voltage

on the VC pin, which in turn limits the peak switch current.

The value of the soft-start capacitor is user defined to

satisfy the designer's requirements.

LED Current Setting

The LED current could be calculated by the following

equation :

For the Boost application, the output voltage could be

clamped at a certain voltage level. The OVP voltage can

be set by the following equation :

R3

)

R4

where R3 and R4 are the voltage divider from VOUT to GND

with the divider center node connected to the OVP pin.

VOUT_OVP = 1.2 (1 +

Current Limit Protection

The RT8463 can limit the peak switch current by the

internal over current protection feature. In normal operation,

the power switch is turned off when the switch current

reaches the loop-set value. The maximum peak-current

limit of the switch is 2.5A (typ.).

Over Temperature Protection

V (ISP ISN)

ILED(MAX) =

R2

where V (ISP − ISN) is the voltage between ISP and ISN

(100mV typ. if ACTL or DCTL dimming is not applied) and

the R2 is the resister between ISP and ISN.

The RT8463 provides Over Temperature Protection (OTP)

function to prevent the excessive power dissipation from

overheating. The OTP function will shut down switching

operation when the die junction temperature exceeds

150°C. The chip will automatically start to switch again

when the die junction temperature cools off.

Brightness / Dimming Control

Inductor Selection

The RT8463 features both analog and digital dimming

control. Analog dimming is linearly controlled by an

external voltage (0.2V < VACTL < 1.2V). With an on-chip

Choose an inductor that can handle the necessary peak

current without saturating, and ensure that the inductor

has a low DCR (copper wire resistance) to minimize I2R

power losses. Inductor manufacturers specify the

maximum current rating as the current where the

inductance falls to certain percentage of its nominal value

(65% typ.).

output clamping amplifier and a resistor, PWM dimming

signal fed at DCTL pin can be easily filtered to an analog

dimming signal with an external capacitor from the ACTL

pin to GND for noise-free PWM dimming. A very high

contrast ratio true digital PWM dimming can be achieved

by driving the ACTL pin with a PWM signal from 100Hz to

10kHz.

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

11

�RT8463

Table 1. Relevant Parameters for Buck, Boost, and Buck − Boost Topologies

Buck

Boost

Buck Boost

Duty Cycle : D

VOUT

VIN VF

VOUT VIN VF

VOUT VF

VOUT VF

VIN VOUT VF

Average Inductor

Current : IL

IOUT

IOUT

1 D

IOUT

1 D

I (A)

VOUT VF

(1 D)

L fSW

VOUT VF

D (1 D)

L fSW

VOUT VF

(1 D)

L fSW

VOUT VF

(1 D)

IOUT L fSW

VOUT VF

D (1 D)2

IOUT L fSW

VOUT VF

(1 D)2

IOUT L fSW

IOUT

(1 )

1 D

2

IOUT

(1 )

1 D

2

VOUT VF

D (1 D)2

IOUT fSW

VOUT VF

(1 D)2

IOUT fSW

I (A)

IL

IPK (A) = IL (1

2

)

L (H)

IOUT (1

2

)

VOUT VF

(1 D)

IOUT fSW

γ : Current ripple ratio, set γ = 1 for typical peak current

disign.

fSW : Switch Frequency

VF : Forward voltage drop of the output rectifier.

VIN : Nominal input voltage.

VOUT : Desired output voltage.

IOUT : Desired output current.

IPK : Peak current of Inductor.

L : Minimum Desired Inductor value.

Table1, shows the relevant parameters for Buck, Boost

and Buck − Boost topologies. The first column is for the

basic definition of the terms.

Schottky Diode Selection

The Schottky diode, with low forward voltage drop and

fast switching speed, is necessary for the RT8463

applications. In addition, power dissipation, reverse voltage

rating and pulsating peak current are the important

parameters of the Schottky diode that must be

considered. Choose a suitable Schottky diode whose

reverse voltage rating is greater than the maximum output

voltage. The diode's average current rating must exceed

the average output current. The diode conducts current

only when the power switch is turned off (typically less

than 50% duty cycle).

Capacitor Selection

The peak inductor current depends on the different

topologies. For a Buck converter the average value of the

inductor current equals the load current, irrespective of

the input voltage. When as the input increases, the peak

current increases.

The input capacitor reduces current spikes from the input

supply and minimizes noise injection to the converter. For

most RT8463 applications, a 4.7μF ceramic capacitor is

sufficient. A higher or lower value may be used depending

on the noise level from the input supply and the input

current to the converter.

The inductor must be selected with a saturation current

rating greater than the peak current limit.

In Boost application, the output capacitor is typically a

ceramic capacitor and is selected based on the output

voltage ripple requirements. The minimum value of the

output capacitor, COUT, is approximately given by the

following equation :

I

D T

COUT = LED

VRIPPLE

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

12

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

Maximum Power Dissipation (W)1

Thermal Considerations

The junction temperature should never exceed the

absolute maximum junction temperature TJ(MAX), listed

under Absolute Maximum Ratings, to avoid permanent

damage to the device. The maximum allowable power

dissipation depends on the thermal resistance of the IC

package, the PCB layout, the rate of surrounding airflow,

and the difference between the junction and ambient

temperatures. The maximum power dissipation can be

calculated using the following formula :

For continuous operation, the maximum operating junction

temperature indicated under Recommended Operating

Conditions is 125°C. The junction-to-ambient thermal

resistance, θJA, is highly package dependent. For a

TSSOP-14 (Exposed Pad) package, the thermal

resistance, θJA, is 30.1°C/W on a standard JEDEC 51-7

high effective-thermal-conductivity four-layer test board.

For a WDFN-12L 3x3 package, the thermal resistance,

θJA, is 30.5°C/W on a standard JEDEC 51-7 high effectivethermal-conductivity four-layer test board. The maximum

power dissipation at TA = 25°C can be calculated as below

:

PD(MAX) = (125°C − 25°C) / (30.1°C/W) = 3.32W for a

TSSOP-14 (Exposed Pad) package.

PD(MAX) = (125°C − 25°C) / (30.5°C/W) = 3.28W for a

WDFN-12L 3x3 package.

The maximum power dissipation depends on the operating

ambient temperature for the fixed TJ(MAX) and the thermal

resistance, θJA. The derating curves in Figure 7 allows

the designer to see the effect of rising ambient temperature

on the maximum power dissipation.

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

Four-Layer PCB

3.0

TSSOP-14 (Exposed Pad)

2.5

WDFN-12L 3x3

2.0

1.5

1.0

0.5

0.0

PD(MAX) = (TJ(MAX) − TA) / θJA

where TJ(MAX) is the maximum junction temperature, TA is

the ambient temperature, and θJA is the junction-to-ambient

thermal resistance.

3.5

0

25

50

75

100

125

Ambient Temperature (°C)

Figure 7. Derating Curve of Maximum Power Dissipation

Layout Consideration

PCB layout is very important to design power switching

converter circuits. The recommended layout guidelines

are listed as follows :

The power components L1, D1, CVIN, and COUT must be

placed as close to each other as possible to reduce the

ac current loop area. The PCB trace between power

components must be as short and wide as possible

due to large current flow through these traces during

operation.

Place L1 and D1 connected to SW pin as close as

possible. The trace should be as short and wide as

possible.

The input capacitors C1 must be placed as close to

VCC pin as possible.

Place the compensation components to the VC pin as

close as possible to avoid noise pick up.

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

13

�RT8463

Place these components as close as possible.

D1

COUT

L1

GND

C1

GND

RSENS

:

:

:

:

RVC

CVC

VIN

ISP

1

12

VCC

ISN

2

11

CREG

VC

3

10

SW

ACTL

4

9

GND

DCTL

5

8

SS

EN

6

7

OVP

GND

Grand Plane

CVIN

C5

GND

Locate input

capacitor to

VCC as close

as possible.

CSS

GND

Locate the compensation components to VC

pin as close as possible.

Figure 8. PCB Layout Guide for WDFN-12L 3x3

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

www.richtek.com

14

is a registered trademark of Richtek Technology Corporation.

DS8463-02 March 2018

�RT8463

Outline Dimension

Dimensions In Millimeters

Symbol

Dimensions In Inches

Min

Max

Min

Max

A

1.000

1.200

0.039

0.047

A1

0.000

0.150

0.000

0.006

A2

0.800

1.050

0.031

0.041

b

0.190

0.300

0.007

0.012

D

4.900

5.100

0.193

0.201

0.650

e

0.026

E

6.300

6.500

0.248

0.256

E1

4.300

4.500

0.169

0.177

L

0.450

0.750

0.018

0.030

Option1

1.900

2.900

0.075

0.114

Option2

2.350

2.850

0.093

0.112

Option3

2.640

3.100

0.104

0.122

Option1

1.600

2.600

0.063

0.102

Option2

2.250

2.750

0.089

0.108

Option3

2.550

3.000

0.100

0.118

U

V

14-Lead TSSOP (Exposed Pad) Plastic Package

Copyright © 2018 Richtek Technology Corporation. All rights reserved.

DS8463-02 March 2018

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

15

�RT8463

2

1

2

1

DETAIL A

Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional,

but must be located within the zone indicated.

Symbol

D2

Dimensions In Millimeters

Min.

Max.

Min.

Max.

A

0.700

0.800

0.028

0.031

A1

0.000

0.050

0.000

0.002

A3

0.175

0.250

0.007

0.010

b

0.150

0.250

0.006

0.010

D

2.950

3.050

0.116

0.120

Option1

2.300

2.650

0.091

0.104

Option2

1.970

2.070

0.078

0.081

2.950

3.050

0.116

0.120

Option1

1.400

1.750

0.055

0.069

Option2

1.160

1.260

0.046

0.050

E

E2

Dimensions In Inches

e

L

0.450

0.350

0.018

0.450

0.014

0.018

W-Type 12L DFN 3x3 Package

Richtek Technology Corporation

14F, No. 8, Tai Yuen 1st Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should

obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot

assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be

accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third

parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

www.richtek.com

16

DS8463-02 March 2018

�