No Input Electrolytic Capacitor Required, IEC61000-3-2 Class-C

Isolated LED Driver IC

LC5540LD Series

Data Sheet

Description

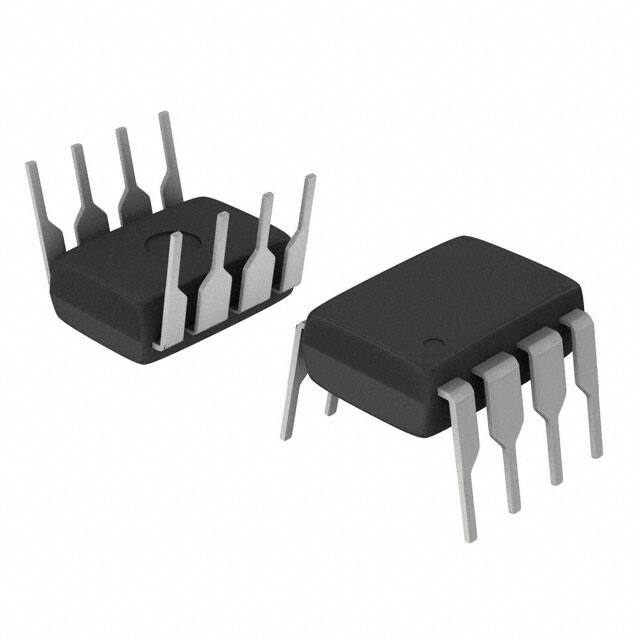

Package

The LC5540LD series are isolated LED drivers in

which a power MOSFET and a control IC are highly

integrated.

The IC provides the systems that can comply with the

harmonics standard (IEC61000-3-2 Class C) in all

conditions, including a light load condition. These

systems, moreover, can be achieved without an input

electrolytic capacitor.

The IC employs the average current and quasi-resonant

controls: the average current control realizes high power

factors, whereas the quasi-resonant control contributes to

high efficiency and low noise.

Having a rich set of protection features, the IC can

provide and more cost-effective power supply systems

with fewer external components.

DIP8

Not to scale

Selection Guide

● Electrical Characteristics

Part Number

VDSS (min.)

LC5545LD

fOSC (typ.)

tON(MAX)

(typ.)

72 kHz

9.3 µs

60 kHz

11.2 µs

650 V

Features

● Built-in On-time Control Circuit

(High Power Factor Achieved by Average Current

Control)

● Built-in Startup Circuit

(Reduced Numnber of External Components)

● Soft Start Function

(Startup Stress Reduction for Power MOSFET and

Secondary Rectifier Diode)

● Bias Assist Function

(Improved Startup Performance, VCC Voltage Drop

Suppresion in Operation, Reduced Capacitance of

VCC Pin Capacitor)

● Leading Edge Blanking Function

● Built-in Maximum On-time Limitation Function

● Protections Include:

Overcurrent Protection (OCP): Pulse-by-Pulse

Overvoltage Protection (OVP): Latched Shutdown

Overload Protection (OLP): Latched Shutdown

Thermal Shutdown (TSD): Latched Shutdown

LC5546LD

● Power MOSFET On-resistance and Output Power

POUT*

RDS(ON)

(max.)

230 VAC

85 VAC to

265 VAC

LC5545LD

3.95 Ω

13 W

10 W

LC5546LD

1.9 Ω

20 W

16 W

Part Number

* Based on the thermal ratings; the allowable maximum output

powers can be up to 120% to 140% of the rated values.

However, the maximum output powers may be limited in an

application with a low output voltage or according to a

maximum duty cycle for designing a transformer.

Applications

● LED Lighting Equipment

● LED Bulbs

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

1

�LC5540LD Series

Contents

Description ------------------------------------------------------------------------------------------------------ 1

Contents --------------------------------------------------------------------------------------------------------- 2

1. Absolute Maximum Ratings----------------------------------------------------------------------------- 3

2. Electrical Characteristics -------------------------------------------------------------------------------- 4

2.1. Electrical Characteristics of Control Parts----------------------------------------------------- 4

2.2. Electrical Characteristics of Power MOSFET------------------------------------------------- 5

3. Block Diagram --------------------------------------------------------------------------------------------- 6

4. Pin Configuration Definitions--------------------------------------------------------------------------- 6

5. Typical Application --------------------------------------------------------------------------------------- 7

6. Physical Dimensions -------------------------------------------------------------------------------------- 8

7. Marking Diagram ----------------------------------------------------------------------------------------- 8

8. Operational Description --------------------------------------------------------------------------------- 9

8.1. Startup Operation ----------------------------------------------------------------------------------- 9

8.1.1. Startup Time ----------------------------------------------------------------------------------- 9

8.1.2. Undervoltage Lockout (UVLO) ------------------------------------------------------------ 9

8.1.3. Bias Assist Function--------------------------------------------------------------------------- 9

8.1.4. Auxiliary Winding -------------------------------------------------------------------------- 10

8.1.5. Soft Start Function -------------------------------------------------------------------------- 11

8.1.6. Operation Mode at Startup---------------------------------------------------------------- 11

8.2. On-time Control Operation --------------------------------------------------------------------- 12

8.3. Quasi-resonant Operation and Bottom-on Timing ----------------------------------------- 13

8.3.1. Quasi-resonant Operation ----------------------------------------------------------------- 13

8.3.2. Bottom-on Timing Setup ------------------------------------------------------------------- 13

8.3.3. BD Blanking Time--------------------------------------------------------------------------- 16

8.4. Overvoltage Protection (OVP) ------------------------------------------------------------------ 16

8.4.1. VCC Pin Overvoltage Protection (VCC_OVP) ---------------------------------------- 16

8.4.2. OCP Pin Overvoltage Protection (OCP_OVP) ---------------------------------------- 17

8.4.3. OVP Pin Overvoltage Protection (OVP_OVP) ---------------------------------------- 17

8.5. Overload Protection (OLP)---------------------------------------------------------------------- 17

8.6. Overcurrent Protection (OCP) ----------------------------------------------------------------- 18

8.6.1. OCP Detection Method and Leading Edge Blanking Function -------------------- 18

8.6.2. Input Compensation Function ------------------------------------------------------------ 19

8.6.3. OCP Threshold Voltage with or without Compensation Circuit ------------------ 20

8.6.4. Determining OCP Input Compensation Circuit Component Values ------------- 21

8.6.5. Reference Design for OCP Input Compensation Circuit with Universal Input - 21

8.7. Thermal Shutdown (TSD) ----------------------------------------------------------------------- 22

8.8. Maximum On-time Limitation Function ----------------------------------------------------- 23

9. Design Notes ---------------------------------------------------------------------------------------------- 24

9.1. External Components ---------------------------------------------------------------------------- 24

9.2. Transformer Design ------------------------------------------------------------------------------ 24

9.3. Trace and Component Layout Design -------------------------------------------------------- 26

Important Notes ---------------------------------------------------------------------------------------------- 28

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

2

�LC5540LD Series

1.

Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out

of the IC (sourcing) is negative current (−).

Unless otherwise specified, TA = 25 °C.

Parameter

Pin

Symbol

Conditions

Rating

Unit

Remarks

Drain Current

Avalanche Energy

8–1

8–1

IDPEAK

EAS

Single pulse

Single pulse,

VDD = 99 V,

L = 20 mH,

ILPEAK = 2.0 A

Single pulse,

VDD = 99 V,

L = 20 mH,

ILPEAK = 2.7 A

2.5

4.0

A

47

LC5546LD

LC5545LD

mJ

86

LC5546LD

VCC Pin Voltage

2–1

VCC

35

V

OCP Pin Voltage

3–1

VOCP

−2.0 to 5.0

V

FB Pin Voltage

4–1

VFB

−0.3 to 7.0

V

OVP Pin Voltage

6–1

VOVP

−0.3 to 5.0

V

Power MOSFET Power

Dissipation

8–1

PD1

0.97

W

Operating Ambient

Temperature

Storage Temperature

―

TOP

−55 to 125

°C

―

Tstg

−55 to 125

°C

Channel Temperature

―

Tch

150

°C

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

LC5545LD

When mounted on

a board with a size

of 15 mm × 15 mm

3

�LC5540LD Series

2.

Electrical Characteristics

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out

of the IC (sourcing) is negative current (−).

2.1.

Electrical Characteristics of Control Parts

Unless specifically noted, TA = 25 °C, VCC = 20 V.

Parameter

Pin

Symbol

Min.

Typ.

Max.

Unit

Remarks

Power Supply Startup Operation

Operation Start Voltage

2–1

VCC(ON)

13.8

15.1

17.3

V

Operation Stop Voltage(1)

2–1

VCC(OFF)

8.4

9.4

10.7

V

Circuit Current in Operation

Startup Circuit Operation

Voltage

Startup Current

Startup Current Biasing

Threshold Voltage(1)

Normal Operation

2–1

ICC(ON)

―

―

4.7

mA

8–1

VSTARTUP

18

21

24

V

2–1

ICC(STARTUP)

−8.5

−4.0

−1.5

mA

2–1

VCC(BIAS)

9.5

11.0

12.5

V

PWM Operation Frequency

8–1

fOSC

60

72

84

50

60

70

Maximum On-time

8–1

tON(MAX)

8.0

9.3

11.2

9.0

11.2

13.4

4–1

VFB(MIN)

0.50

0.85

1.20

V

4–1

IFB(MAX)

−40

−25

−10

µA

3–1

tON(LEB)

―

600

―

ns

3–1

VBD(TH1)

0.14

0.24

0.34

V

3–1

VBD(TH2)

0.11

0.16

0.21

V

3–1

VOCP

−0.66

−0.60

−0.54

V

3–1

IOCP

−120

−40

−10

µA

3–1

VBD(OVP)

2.2

2.6

3.0

V

4–1

VFB(OLP)

4.1

4.5

4.9

V

6–1

VOVP(OVP)

1.6

2.0

2.4

V

2–1

VCC(OVP)

28.5

31.5

34.0

V

―

TJ(TSD)

135

―

―

°C

FB Pin Control Minimum

Voltage

Maximum Feedback Current

Leading Edge Blanking Time

Quasi-resonant Operation

Threshold Voltage 1

Quasi-resonant Operation

Threshold Voltage 2

Protection Function

Overcurrent Detection

Threshold Voltage

OCP Pin Source Current

OCP Pin OVP Threshold

Voltage

OLP Threshold Voltage

OVP Pin OVP Threshold

Voltage

VCC Pin OVP Threshold

Voltage

Thermal Shutdown Operating

Temperature

(1)

kHz

µs

VCC = 13 V

LC5545LD

LC5546LD

LC5545LD

LC5546LD

Always in the condition of VCC(BIAS) > VCC(OFF).

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

4

�LC5540LD Series

2.2.

Electrical Characteristics of Power MOSFET

Unless otherwise specified, TA = 25 °C.

Parameter

Pin

Drain-to-Source Breakdown

8–1

Voltage

Drain Leakage Current

8–1

Symbol

Min.

Typ.

Max.

Unit

VDSS

650

―

―

V

IDSS

―

―

300

µA

―

―

3.95

―

―

1.9

―

―

250

―

―

400

―

―

42

―

―

35.5

On-resistance

8–1

RDS(ON)

Switching Time

8–1

tf

―

θch-c

Thermal Resistance(1)

(1)

Ω

ns

°C/W

Remarks

LC5545LD

LC5546LD

LC5545LD

LC5546LD

LC5545LD

LC5546LD

LC5545LD

LC5546LD

Refers to the thermal resistance between the channel of the power MOSFET and the case. The case temperature, TC,

is measured at the center of the branding side on the case.

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

5

�LC5540LD Series

3.

Block Diagram

VCC

②

⑧ D/ST

STARTUP

TSD

UVLO

Reg

DRV

Bias

OVP ⑥

OVP

① S/GND

S

R Q

OCP ③

Bottom

Detection

NF ⑤

OCP

OLP

OSC

LEB

Feedback

Control

④ FB

Reg

4.

(1)

Pin Configuration Definitions

S/GND

1

8

VCC

2

7

OCP

3

6

OVP

FB

4

5

NF

D/ST

Pin

Number

1

Pin

Name

S/GND

2

VCC

3

OCP

4

FB

5

NF

6

OVP

7

―

8

D/ST

Description

Power MOSFET source and control ground

Power supply voltage input for control part and

OCP pin overvoltage protection signal input

Overcurrent protection signal input, quasiresonant signal input, and overvoltage protection

signal input

Feedback signal input and overload protection

signal input

(No function assigned)(1)

OVP pin overvoltage protection signal input

(Pin removed)

Power MOSFET drain and startup current input

Should be connected to the S/GND pin (pin 1) with a minimum-length trace for stable operations.

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

6

�C1

ROCP

1

8

S/GND

D/ST

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

VCC

R3

C5

2

LC554xLD

U1

L1

OVP

5

3

C6

OCP

FB

R7

L2

PC1

S/GND

D4

D2

NF

D7

4

Control

Block

6

D3

D1

C4

C7

R21 C18 DZ3

R6

PC2

C2

D5

C8

R4

D6

D9

R1

R5

C17

T1

C9

D8

C11

C10

PC2

DZ2

R9

R8

DZ1

R10

C12

R12

PC1

Q1

U2

C14

+

-

C13 R17

R11

R13

R16

R15

R14

C15

R19 R20 C16

R18

LED

5.

C3

VAC

F1

LC5540LD Series

Typical Application

Figure 5-1. Typical Application

7

�LC5540LD Series

6.

Physical Dimensions

● DIP8

9.4±0.3

8

6.5 ±0.2

5

1.0

+0.3

-0.05

4

+0.3

1.52 -0.05

1

3.3 ±0.2

4.2 ±0.3

3.4 ±0.1

7.5 ±0.5

(7.6 typ.)

0.2 +0.

5

1

-0.

05

2.54 typ.

0 to 15°

0 to 15°

0.89 typ.

0.5±0.1

NOTES:

- Dimensions in millimeters

- Pb-free (RoHS compliant)

7.

Marking Diagram

8

LC5 54x

Part Number

S KY MD L

Lot Number:

Y is the last digit of the year of manufacture (0 to 9)

1

M is the month of the year (1 to 9, O, N, or D)

D is the period of days represented by:

1: the first 10 days of the month (1st to 10th)

2: the second 10 days of the month (11th to 20th)

3: the last 1 –11 days of the month (21st to 31st)

Control Number

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

8

�LC5540LD Series

Current polarities are defined as follows: current going

into the IC (sinking) is positive current (+); current coming

out of the IC (sourcing) is negative current (−). All the

characteristic values given in this section are typical

values, unless they are specified as minimum or maximum.

8.1.

Startup Operation

8.1.1. Startup Time

Figure 8-1 shows the VCC pin peripheral circuit. The

IC has the startup circuit connected to the D/ST pin. When

the D/ST pin voltage reaches the Startup Circuit Operation

Voltage, VSTARTUP = 21 V, the startup circuit starts to

operate. During the startup process, the constant current,

ICC(STARTUP) = −4.0 mA, charges C4 connected to the VCC

pin. When the VCC pin voltage increases to VCC(ON) = 15.1

V, the IC starts to operate. After that, the startup circuit is

automatically cut off to eliminate power dissipation by the

startup circuit.

The startup time is determined by the capacitor C4. Use

a ceramic or film capacitor for C4, and set its value to 0.22

μF to 22 μF when a general power supply specification is

to be applied. The approximate value of the startup time

can be calculated by the following equation:

t START ≒ C4 ×

VCC(ON) − VCC(INT)

|ICC(STARTUP) |

.

voltage and the circuit current, ICC. When the VCC pin

voltage reaches the Operation Start Voltage,

VCC(ON) = 15.1 V, the control circuit starts to operate, then

the circuit current increases. When the VCC pin voltage

decreases to VCC(OFF) = 9.4 V, the control circuit operation

is stopped by the undervoltage lockout (UVLO) circuit,

and is put back to the state before startup. After the IC

starts switching operation, the rectified auxiliary winding

voltage is supplied to the VCC pin. The auxiliary winding

voltage, VD, is presented in Figure 8-1. In the variation

range of the input and output specifications, the winding

turns of the auxiliary winding, D, should be adjusted so

that the VCC pin voltage falls within the range defined by

Equation (2). The reference voltage across an auxiliary

winding is about 20 V.

VCC(BIAS)MAX < VCC < VCC(OVP)MIN ,

that is, 12.5 V < VCC < 28.5 V .

(2)

Circuit Current, ICC

ICC(ON) = 4.7 mA

(max.)

Start

Operational Description

Stop

8.

(1)

9.4 V

VCC(OFF)

Where:

tSTART is the startup time (s), and

VCC(INT) is the initial VCC pin voltage (V).

VCC Pin

15.1 V Voltage

VCC(ON)

Figure 8-2. VCC Pin Voltage vs. Circuit Current, ICC

L2

T1

VAC

C2

8

D/ST

VCC

S/GND

2

1

P

D5

R1

C4

VD

D

LC554xLD

Figure 8-1. VCC Pin Peripheral Circuit

8.1.2. Undervoltage Lockout (UVLO)

Figure 8-2 shows the relationship of the VCC pin

8.1.3. Bias Assist Function

Figure 8-3 shows a VCC pin voltage behavior during

the startup period. When the VCC pin voltage decreases

to the Startup Current Biasing Threshold Voltage,

VCC(BIAS) = 11.0 V, the bias assist function is activated.

While the bias assist function is operating, the VCC pin

voltage is kept almost constant because a decrease in the

VCC pin voltage is regulated by a startup current from the

startup circuit. While the output voltage rises, the VCC pin

voltage increases to the target voltage with the slope

determined by the voltage drop caused by increasing IC

current and the voltage rise across the auxiliary winding,

VD, which is proportional to the output voltage.

The bias assist function reduces C4 capacitance. In

addition, the response time of the OVP function can be

shortened because the VCC pin voltage rise along with the

output voltage rise also becomes faster. To avoid a startup

failure, be sure to check the startup operation based on

operations in an actual application, and to adjust a circuit

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

9

�LC5540LD Series

constant including C4.

VCC Pin Voltage

IC startup

Startup succeeded

Target voltage

VCC(ON)

VCC(BIAS)

Output voltage rising

Bias assist period

VCC(OFF)

Startup failure

Time

Figure 8-3. VCC Pin Voltage at Startup

8.1.4. Auxiliary Winding

In actual operation of power supply circuits, the

transient surge voltage that occurs at power MOSFET

turn-off induces a voltage across the auxiliary winding, D.

C4 is charged at the peak of the induced voltage. The surge

voltage increases as the output current, IOUT increases.

Thus, the VCC pin voltage increases as IOUT increases, as

shown in Figure 8-4. When the VCC pin voltage increases

to VCC(OVP) = 31.5 V or more, the VCC pin overvoltage

protection (VCC_OVP) is activated. To prevent the C4

peak charging, add R1 with a value ranging from several

ohms to several ten ohms, in series with D5 (see Figure

8-5). The optimal value of R1 should be determined with

a transformer set for an actual application, because the

variation of the VCC pin voltage depends on the

transformer’s structural design.

VCC Pin Voltage

In the following cases, the VCC pin voltage is more

susceptible to the effect of IOUT. Care must be taken in the

placement of the auxiliary winding, D, when designing

your transformer.

● When poor coupling between the primary and

secondary windings causes high surge voltage in the

conditions such as low output voltage and high output

current.

● When poor coupling between the auxiliary winding, D,

and the secondary winding causes the auxiliary

winding voltage to be susceptible to the effect of surge

voltage variation.

Figure 8-6 shows two transformer design examples for

minimizing the impact of VCC surge voltage, with

consideration given to the placement of the auxiliary

winding, D (in which triple insulation wires are used for

the primary or secondary winding, but no margin tapes

used).

● Winding Structural Example (a):

Separate the auxiliary winding, D, from the primary

windings, P1 and P2 (P1 and P2 are two separated primary

windings).

● Winding Structural Example (b):

Improve the coupling between the secondary winding,

S1, and the auxiliary winding, D.

P1 S1 P2 S1

D

Without R1

Winding Structural Example (a)

With R1

Output Current, IOUT

Figure 8-4. IOUT vs. VCC with or without R1

P1 S1

D5

2

VCC

S1 P2

With R1

C4

LC554xLD

D

R1

D

S/GND

1

Figure 8-5. VCC Pin Peripheral Circuit to Reduce

Effect of Output Current

Winding Structural Example (b)

Where:

P1 and P2 are the primary windings,

S1 is the secondary winding, and

D is the auxiliary winding.

Figure 8-6. Winding Structural Examples

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

10

�LC5540LD Series

8.1.5. Soft Start Function

8.1.6. Operation Mode at Startup

Figure 8-7 shows the operation waveforms during the

startup. The soft start function reduces the voltage and

current stress of the power MOSFET and the secondary

rectifier diode during the startup period. When the FB pin

voltage reaches VFB(MIN) = 0.85 V, the IC shifts into the

soft start operation. The soft start operation continues until

the output current becomes constant, as shown in Figure

8-7. During the soft start operation, the output power

gradually increases. To avoid a startup failure, be sure to

check waveforms during the soft start operation and to

adjust the power supply circuit so that the IC starts with

the following conditions.

Figure 8-7 shows the operation mode during the startup.

After the startup, when the FB pin voltage reaches

VFB(MIN) = 0.85 V, the IC starts a PWM switching

operation. The LC5540LD series requires different PWM

operation frequencies, fOSC, as follows: 72 kHz for the

LC5545LD, and 60 kHz for the LC5546LD.

● The VCC pin voltage maintains over the Operation

Stop Voltage, VCC (OFF).

● The output current reaches the target value before the

overload protection (OLP) is activated (i.e., the FB pin

voltage is less than VFB(OLP) = 4.5 V).

When the auxiliary winding voltage rises along with the

output voltage, the positive voltage on the OCP pin also

rises. When the OCP pin voltage reaches VBD(TH1) = 0.24 V

or more, the IC shifts into the quasi-resonant operation.

Figure 8-8 shows the OCP pin voltage waveforms on an

expanded time scale when the IC shifts into quasi-resonant

operation mode from PWM operation (point A in Figure

8-7).

Soft start period

FB Pin Voltage

IC startup

VFB(MIN)

S/GND

VCC Pin Voltage

VCC(BIAS)

S/GND

Constant output current control

Output Current, IOUT

(Output Load

Current)

Target value

GND(I OUT)

PWM operation

Quasi-resonant (QR) operation

Drain Current, ID

S/GND

Time

A

Figure 8-7. Soft Start Operation Waveforms at Startup

Quasi-resonant Signal,

VBD

VBD(TH1)

PWM operation

Quasi-resonant (QR) operation

S/GND

Drain Current, I D

GND(ID)

Time

Figure 8-8. OCP Pin Voltage Waveforms on Expanded Time Scale (Point A)

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

11

�LC5540LD Series

8.2.

On-time Control Operation

Figure 8-9 shows the peripheral circuit of the FB pin,

whereas Figure 8-10 shows the on-time control. The IC

controls an output current with the voltage mode, which

controls an on-time depending on an output load, and the

average current control. In the average current control

shown in Figure 8-10, the IC compares the voltage drop

of the secondary-side constant current detection resistor

with the reference voltage by the secondary operational

amplifier. Then, the output of the secondary operational

amplifier is run through the optocoupler PC1 to the FB

pin, and its output is averaged at the FB pin. The IC

compares the averaged voltage at the FB pin with the

internal oscillator (OSC) output by the internal FB

comparator to control the on-time. The OSC indicates the

oscillator circuit to control operations such as the PWM

operation frequency, the quasi-resonant oscillation, and

the maximum on-time limit.

The recommended value of capacitor, C6, connected to

the FB pin is approximately 2.2 μF.

The IC controls the constant output current according

to loads as follows:

● When the output current becomes less than the

target value

When the output current decreases to less than the

target value, the power supply circuit operates as follows:

The voltage drop across the resistor that is for constant

current detection in the secondary side becomes low.

Therefore, the current through the optocoupler decreases.

This leads to a decrease in the primary-side feedback

current. Thus, the averaged FB pin voltage and on-time

increase, and the output current increases.

● When the output current becomes greater than the

target value

When the output current increases to greater than the

target value, the power supply circuit operates opposite to

the above as follows: The voltage drop across the resistor

that is for constant current detection in the secondary side

becomes high. Therefore, the current through the

optocoupler increases. This leads to an increase in the

primary-side feedback current. Thus, the averaged FB pin

voltage and on-time decrease, and the output current

decreases.

LC554xLD

FB pin voltage

-

OSC

+

4

FB

S/GND

C6

PC1

LED

1

+

Constant current

detection resistor

OSC

-

FB

+

FB pin

voltage

Gate on-time

Drain current

Figure 8-10. On-time Control

Figure 8-11 shows the average input current waveform.

The averaged FB pin voltage becomes constant. Since

duty cycle is controlled according to the VIN voltage (C2

voltage in Figure 5-1), an averaged input current becomes

a sine waveform. This yields a high power factor.

FB Pin Voltage

VIN

S/GND

Drain current

Averaged input

current

LC554xLD

Figure 8-11. Averaged Input Current Waveform

S/GND

FB

OCP

4

3

1

D7

R7

R3

ROCP

PC1

C6

Figure 8-9. FB Pin Peripheral Circuit

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

12

�LC5540LD Series

8.3.

Quasi-resonant Operation and Bottomon Timing

Half cycle of the free oscillation tONDLY

t ONDLY ≒ L P C V

8.3.1. Quasi-resonant Operation

VFLY

Figure 8-12 shows the circuit of a flyback converter.

The flyback converter is a system which transfers the

energy stored in the transformer to the secondary side

when the primary-side power MOSFET is turned off. The

MOSFET stays in the off state even after the energy is

completely transferred to the secondary side. During the

off state, the voltage between the drain and source, VDS,

begins free oscillation based on the primary inductance,

LP, and the capacitance between the drain and source, CV.

The quasi-resonant operation provides VDS bottom-on

operation that the power MOSFET turns on at the lowest

voltage point of VDS free oscillation. Figure 8-13 shows

an ideal VDS waveform during the bottom-on operation.

The bottom-on operation reduces switching loss and

switching noise. This results in a power supply with high

efficiency and low noise.

VIN

VDS 0

Bottom point

IOFF 0

ID 0

tON

Figure 8-13. Ideal Bottom-on Operation Waveforms

(Power MOSFET Turns On at the Lowest Voltage of

VDS Waveform)

VF

NP T1

VFLY

ID

VIN

NS

D8

LP

P

S

IOFF

VOUT

C9

C2

CV

Figure 8-12. Basic Flyback Converter Circuit

The symbols in Figure 8-12 represent as follows:

VIN is the input voltage,

VFLY is the flyback voltage calculated by

VFLY =

NP

× (VOUT + VF ) ,

NS

NP is the number of turns in the primary winding,

NS is the number of turns in the secondary winding,

VOUT is the output voltage,

VF is the forward voltage drop of the secondary

rectifier diode,

ID is the drain current of the power MOSFET,

IOFF is the current running through the secondary

rectifier diode during the power MOSFET offperiod,

CV is the voltage resonant capacitor, and

LP is the primary inductance.

8.3.2. Bottom-on Timing Setup

Figure 8-14 shows an OCP pin peripheral circuit,

Figure 8-15 shows the waveform of an auxiliary winding

voltage. The OCP pin detects the auxiliary winding

voltage, which is synchronized with the VDS waveform,

through a delay circuit (D6, R4, C7, and D7 in Figure

8-14). The bottom-on operation is controlled by the

delayed signal. The delay time, tONDLY, is the period from

when VDS free oscillation starts to when the power

MOSFET turns on. The delay time is then adjusted by the

delay circuit. During the power MOSFET turn-off, the

positive voltage is supplied through the delay circuit to

the OCP pin from auxiliary winding. This input signal to

the OCP pin is defined as a quasi-resonant signal, VBD.

When the VBD increases to the Quasi-resonant

Operation Threshold Voltage 1 (VBD(TH1) = 0.24 V) or

more after the power MOSFET turns off, the IC maintains

the power MOSFET in an off state. After that, when the

VBD decreases to the Quasi-resonant Operation Threshold

Voltage 2 (VBD(TH2) = 0.16 V) or less, the IC turns on the

power MOSFET and automatically raise the threshold

voltage to VBD(TH1) to prevent malfunctions caused by the

noise added to the OCP pin.

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

13

�LC5540LD Series

T1

VIN

P

VBD(PK) = 1.5 V to 2.0 V, and tQR ≥ 1.2 μs. These

conditions must be fulfilled within the power supply input

and output ranges (see Figure 8-16).

C2

R1

D5

Vrev1

C4

C3

8

D/ST

Quasi-resonant

Signal

VBD

VIN VFLY

Clamping

snubber circuit

D

Vfw1

VBD(TH2)

tQR 1.2 µs

R4

Forward

voltage

Flyback voltage

D7

Figure 8-16. The Effective Pulse Width of QuasiResonant Signal

3

LC554xLD

S/GND

1

VBD(TH1)

D6

2

VCC

OCP

Recommended V BD(PK) value

= 1.5 V to 2.0 V ( 2.6 V)

C5

C7

R3

R3, R4, C5, and C7 should be set as follows:

VBD

ROCP

Figure 8-14. OCP Pin Peripheral Circuit

● R3

100 Ω to 330 Ω (reference value)

● R4

R4 should be adjusted so that VBD(PK) meets the

following conditions:

- VBD(PK) ≥ VBD(TH1) under the lowest VCC pin voltage

condition in the ranges of the input and output

specifications.

- VBD(PK) < 2.6 V under the highest VCC pin voltage

condition in normal operation. 2.6 V is the OCP Pin

OVP Threshold Voltage, VBD(OVP).

Auxiliary Winding Voltage

VD

Vrev1

Because ROCP is much less than R3, R4 is calculated as

follows:

0

Vfw1

R4 =

Quasi-resonant Signal

VBD

tON

VBD(TH1)

VBD(TH2)

(VCC − VBD(PK) − 2 × VF ) × R3

.

VBD(PK)

(3)

For example, if the VCC = 16 V, R3 = 22 Ω,

VBD(PK) = 1.5 V, and the forward voltage drop (VF) of D6

and D7 = 0.8 V, R4 is approximately 1.89 kΩ. Hence, R4

is 1.8 kΩ in the E12 series.

If tQR < 1.2 µs, tQR should be set to 1.2 µs or more

through the following adjustments:

0

Figure 8-15. Auxiliary Winding Voltage

The delay time, tONDLY is determined by the constant

values of the delay circuit. The values should be adjusted

so that the power MOSFET turns on at the bottom of the

VDS waveform. The peak voltage of the quasi-resonant

signal, VBD(PK), and the effective pulse width of the quasiresonant signal, tQR, should be adjusted as follows with

the variations of R3 and R4 taken into account:

- To raise VBD(PK), increase the R3value.

- To raise VBD(PK), reduce the R4 value.

- To increase the free oscillation period, increase the

capacitance of the voltage resonant capacitor, C3.

(The greater the C3 value, the higher the switching

loss; therefore, be sure to check that the IC

temperature ranges within the absolute maximum

rating when increasing the C3 value.)

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

14

�LC5540LD Series

● C5

100 pF to 470 pF (reference value)

- When the power MOSFET turn-on is earlier than the

VDS bottom point at the VDS(PEAK) as Figure 8-17 (A):

Confirm the VDS bottom point at the initial constant,

and then increase the value of C7 gradually until the

power MOSFET turn-on point matches the VDS

bottom point.

- When the power MOSFET turn-on is later than the

VDS bottom point at the VDS(PEAK) as Figure 8-17 (B):

Confirm the VDS bottom point at the initial constant,

and then increase the value of C7 gradually until the

power MOSFET turn-on point matches the VDS

bottom point.

● C7

The delay time, tONDLY, is adjusted by the value of C7.

To set the ideal bottom-on of VDS (see Figure 8-13), adjust

C7 value with measuring actual waveforms under the

maximum AC input voltage and the maximum output

power. Measurement waveforms are the power MOSFET

drain voltage, VDS, the quasi-resonant signal, VBD, and the

drain current, ID. A measurement point is the maximum

amplitude of VDS waveform, VDS(PEAK). An initial constant

for C7 is about 1000 pF.

Commercial frequency (50Hz/60Hz)

2 × Commercial frequency

VDS(PEAK)

VIN

(B) When the power MOSFET turn-on is later than

the VDS bottom point

Free oscillation

frequency, fR

(A) When the power MOSFET turn-on is earlier

than the VDS bottom point

Free oscillation frequency, fR

Advanced turn-on point

fR ≒

Delayed turn-on point

1

Bottom

point

IOFF 0

Auxiliary

Winding Voltage

VD

2 L P CV

VDS 0

Bottom

point

VBD(TH1)

OCP Pin 0

Voltage

1

2 L P CV

VDS 0

ID 0

fR ≒

IOFF 0

ID 0

tON

VBD(TH2)

VBD(TH1)

OCP Pin 0

Voltage

tON

VBD(TH2)

Auxiliary

Winding Voltage

VD

Figure 8-17. VDS Waveforms at the VDS(PEAK)

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

15

�LC5540LD Series

8.4.

8.3.3. BD Blanking Time

Figure 8-18 shows the normal and inappropriate

waveforms of the OCP pin voltage. An inappropriate

operation is caused by poor coupling between the primary

winding and the secondary winding of the transformer. A

transformer with NP >> NS (e.g., low output power

design) has poor coupling and large leakage inductance.

NP and NS indicate the number of turns of the primary

winding and secondary winding, respectively. The poor

coupling causes high surge voltage ringing at the OCP pin

through the auxiliary winding when the power MOSFET

turns off. The OCP pin has a blanking period of 250 ns

(max.). In this period, the IC does not detect the OCP pin

input signal (i.e., quasi-resonant signal). If the period

when a surge voltage is being added to the OCP pin

becomes longer than the blanking period, the power

MOSFET can start switching at a high frequency because

the IC responds to the surge. As a result, power

dissipation in the internal power MOSFET increases.

When the junction temperature reaches its absolute

maximum rating, the power MOSFET can be damaged.

When such high frequency operation occurs, the

following adjustments are required:

● Add C5 of Figure 8-14 near the IC with minimizing a

trace length between the OCP and S/GND pins.

● Redesign the PCB so that the trace of the OCP pin to

the S/GND pin is separated from large current traces.

● Redesign the transform so that the coupling of the

primary winding and the auxiliary winding is poor.

● Adjust the value of a clamping snubber circuit.

To measure any surge voltage waveform on the OCP

pin correctly, connect a test probe as short as possible to

the OCP pin and the S/GND pin.

Normal waveform

(well coupled)

Overvoltage Protection (OVP)

The IC has the overvoltage protection (OVP) for the

VCC, OCP, and OVP pins. When these OVPs are

activated, the IC stops switching operation in a latched

state and the VCC pin voltage decreases. When it

decreases to VCC(BIAS) = 11.0 V, the bias assist function is

activated, and the startup current is supplied to the VCC

pin. The VCC pin voltage then maintains at

VCC(OFF) = 9.4 V or more, thus allowing the latched state

to maintain.

To release the latched state, turn off the input voltage

and decrease the VCC pin voltage below VCC(OFF).

8.4.1. VCC Pin Overvoltage Protection

(VCC_OVP)

Figure 8-19 shows operational waveforms of the VCC

pin overvoltage protection (VCC_OVP). When the

voltage across the VCC and S/GND pins reaches

VCC(OVP) = 31.5 V or more, the VCC_OVP is activated,

and then the IC stops switching operation in a latched

state. Because the VCC pin voltage is proportional to the

output voltage, it can be used to detect an output

overvoltage event such as an open load condition. The

approximate secondary output voltage at VCC_OVP

activation, VOUT(OVP), can be calculated by Equation (4)

below:

VOUT(OVP) =

VOUT

× 31.5 .

VCC

(4)

Where VOUT is the secondary output voltage in normal

operation, and VCC is the VCC pin voltage in normal

operation.

VCC Pin Voltage

Latched shutdown

VCC(OVP)

Input voltage off

Latch

release

VBD(TH1)

VBD(TH2)

0

VCC(BIAS)

VCC(OFF)

FB Pin Voltage

Inappropriate waveform

(poorly coupled)

VFB(MIN)

VBD(TH1)

VBD(TH2)

0

Drain Current

ID

BD blanking time 250 ns(max.)

Figure 8-18. OCP Pin Voltage Waveforms Differed by

Coupling Conditions of Transformer

Figure 8-19. VCC_OVP Operational Waveforms

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

16

�LC5540LD Series

8.4.2. OCP Pin Overvoltage Protection

(OCP_OVP)

Figure 8-20 shows operational waveforms of the OCP

pin overvoltage protection (OCP_OVP). When the

voltage across the OCP and S/GND pins reaches

VBD(OVP) = 2.6 V or more, the OCP_OVP is activated.

Then, the IC stops switching operation in a latched state.

The OCP pin input voltage must be less than its rated

maximum voltage of 5 V. The OCP pin overvoltage will

occur due to improper settings, such as an improper

setting of a quasi-resonant signal (VBD), or a poor

coupling of the transformer between the primary and

secondary winding.

VCC Pin Voltage

VCC(BIAS)

Input voltage off

Latch

release

VCC(OFF)

0

OCP Pin Voltage

Latched shutdown

Input voltage off

Latch

release

VCC Pin Voltage

t

VCC(BIAS)

OVP Pin Voltage

VCC(OFF)

Latched shutdown

VOVP(OVP)

Drain Current

ID

Figure 8-21. OVP_OVP Operational Waveforms

8.5.

Overload Protection (OLP)

In the overload protection (OLP), the peak drain

current is limited by the OCP operation. Figure 8-22

shows the FB pin peripheral circuit, whereas Figure 8-23

shows the OLP operational waveforms.

VBD(OVP)

0

Drain Current

ID

0

t

LC554xLD

7 V Reg.

R7

FB 4

t

Figure 8-20. OCP_OVP Operational Waveforms

8.4.3. OVP Pin Overvoltage Protection

(OVP_OVP)

Figure 8-21 shows operational waveforms of the OVP

pin overvoltage protection (OVP_OVP). When the

voltage across the OVP and S/GND pins reaches

VOVP(OVP) = 2.0 V or more, the OVP_OVP is activated.

Then, the IC stops switching operation in a latched state.

The OVP pin input voltage must be less than its rated

maximum voltage of 5 V. The OVP_OVP operates as the

protection against abnormal conditions, such as a shortcircuit load of serially connected LEDs. The IC detects

the secondary output voltage through an optocoupler

(PC2, as in Figure 5-1) and activates the OVP_OVP.

S/GND

1

C6

PC1

Figure 8-22. FB Pin Peripheral Circuit

VCC Pin

Voltage

VCC(BIAS)

FB Pin Voltage

Input voltage off

Latch

release

VCC(OFF)

Latched

shutdown

VFB(OLP)

Drain Current

ID

Figure 8-23. OLP Operational Waveforms

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

17

�LC5540LD Series

In the overload condition, the VCC pin voltage drops

along with the output voltage drop. When the VCC pin

voltage reaches the Startup Current Biasing Threshold

Voltage, VCC(BIAS) = 11.0 V, the bias assist function is

activated to suppress a reduction in the VCC pin voltage.

Simultaneously, the output of the secondary-side error

amplifier turns off as the output voltage decreases, then

the optocoupler, PC1, is cut off. Since C6 connected to

the FB pin is charged with the feedback current after the

PC1 cutoff, the FB pin voltage increases. When the FB

pin voltage reaches the OLP Threshold Voltage,

VFB(OLP) = 4.5 V, the IC stops switching operation in a

latched state (see Section 8.4).

To release the latched state, turn off the input voltage

and decrease the VCC pin voltage below VCC(OFF).

The reference capacitance of C6 is about 1 μF to 4.7 μF.

If the capacitance is too small, the OLP function may be

activated when the IC restarts. C6 should be adjusted

based on actual operations in your application.

P

D/ST 8

LC554xLD

LOGIC

C3

DRIVE

1

S/GND

OCP Comp.

+

−0.6 V

3

OCP

Reg

C5

VROCP

R3

ROCP

Filter

Figure 8-24. OCP Circuit for Negative Side Detect

To prevent malfunctions, connect a filter to the OCP

pin. Set the constants of the filter (R3, C5) as follows:

8.6.

Overcurrent Protection (OCP)

The overcurrent protection (OCP) detects the peak

drain current of the power MOSFET on a pulse-by-pulse

basis, and limits the output power.

8.6.1. OCP Detection Method and Leading

Edge Blanking Function

The drain current of the power MOSFET is detected by

the current detection resistor, ROCP, placed between the

OCP and S/GND pins, as shown in Figure 8-24. The

detection signals, VROCP, are fed through R3 to the OCP

pin.

The power MOSFET turns off when VROCP reaches the

value obtained by Equation (5), below:

VROCP = −(|VOCP | + R3 × |IOCP |) .

(5)

Where VOCP is the overcurrent detection threshold

voltage of −0.6 V, R3 is the value of R3, and IOCP is the

OCP pin source current of −40 μA.

● R3

To minimize the effects of a variation in the internal

resistor, set R3 value to about 100 Ω to 33 Ω.

● C5

C5 value is about 100 pF to 470 pF. C5 must be a

capacitor with good temperature characteristics. If the C5

value is too large, a response time of the OCP function

may become slow. This causes the peak of drain current

to be increased in transient conditions such as a startup.

The OCP function employs a peak current detection

method. If the OCP pin detects a surge voltage at the

power MOSFET turn-on edge, the power MOSFET may

turn off. As a prevention against such operation, the IC

has the Leading Edge Blanking Time (tON(LEB) = 600 ns),

which starts immediately after the power MOSFET turnon.

When the power MOSFET turns on, the surge voltage

width of the OCP pin voltage should be less than tON(LEB),

as shown in Figure 8-25. If the surge voltage width

becomes tON (LEB) or more, be sure to regulate the surge

voltage value and surge voltage width by implementing

the following settings:

- Adjust the timing of power MOSFET turn-on to the

bottom point of VDS waveform.

- Reduce the capacitance of the voltage resonant

capacitor, CV (i.e., C3).

- Reduce the capacitance of the secondary rectifier

snubber capacitor.

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

18

�LC5540LD Series

The Overcurrent Detection Threshold Voltage, VROCP'

applied with OCP input compensation is calculated by the

following equation:

OCP detection period

S/GND

′

VROCP

= −(|VOCP | + |R3 × IOCP | − R3 × I) .

VROCP

Surge voltage pulse width at

turning on

Figure 8-25. OCP Pin Voltage (Converted from Power

MOSFET Drain Current by ROCP)

8.6.2. Input Compensation Function

The IC has the input compensation function that

compensates the Overcurrent Detection Threshold

Voltage, VOCP, according to AC input voltages. In an

application using a quasi-resonant converter with

universal input (85 VAC to 265 VAC), the peak drain

current of the power MOSFET decreases due to a higher

operation frequency caused by an increased input voltage

under a condition of constant output power.

Figure 8-26 shows the relationship between AC input

voltage and the output current at OCP activation, IOUT(OCP),

with the OCP input compensation function being

activated or deactivated. When the IC without the input

compensation, IOUT(OCP) increases as the AC input voltage

increases (see “IOUT without input compensation” in

Figure 8-26). To regulate IOUT(OCP) at the maximum AC

input voltage, add the OCP input compensation circuit

(DX1, DZX1, RX1) as shown in Figure 8-27. The values of

these components should be adjusted so that IOUT(OCP) at

the maximum AC input voltage exceeds the target output

current, IOUT (see “IOUT with appropriate input

compensation” in Figure 8-26).

Figure 8-27 shows the OCP input compensation circuit,

and Figure 8-28 shows the Vfw1 and Vfw2 voltages

according to the AC input voltage. The compensation

amount of VOCP depends on values of the input

compensation current, I, RX1, R3, and ROCP. The input

compensation current, I, is calculated by the following

equation:

I=

Vfw1 − VZX1 − VFX1

.

R X1 + R3 + R OCP

(7)

Where:

I is the input compensation current,

R3 is the value of R3,

VOCP is the overcurrent detection threshold voltage

(−0.6 V), and

IOCP is is OCP pin source current (−40 μA).

As the input voltage, VIN, increases, the voltage drop

across R3 by the input compensation current, I (i.e., R3 ×

I) increases. Then, the input compensation amount also

increases, and the absolute value of VROCP' decreases.

The compensation start voltage of the OCP input

voltage is determined by the Zener voltage (VZX1) of the

Zener diode (DZX1). Set VZX1 to the same voltage as Vfw1

at the OCP input compensation starting point. The OCP

pin voltage, including surge voltage, must be regulated

within the rated voltages (−2. V to 5. V) under a

condition of the maximum AC input voltage.

Output Current at OCP, IOUT(OCP) (A)

tON(LEB)

IOUT with appropriate input compensation

IOUT without input compensation

IOUT

IOUT (target output current)

IOUT with excessive input

compensation

IOUT cannot be acquired

85 V

265 V

AC Input Voltage (V)

Figure 8-26. AC Input Voltage vs. Output Current at

OCP (with or without OCP Input Compensation

Function)

(6)

Where:

I is the input compensation current,

Vfw1 is the forward voltage of the auxiliary winding, D

proportional to input voltage,

VFX1 is the forward voltage of the rectifier diode DX1,

and

VZX1 is the Zener voltage of the Zener diode DZX1.

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

19

�LC5540LD Series

Forward voltage, Vfw1

Flyback voltage, Vrev1

T1

P

VIN

C2

R1

D

D5

Where:

VROCP is the overcurrent detection threshold voltage

without an OCP input compensation circuit,

IDP(OCP) is the peak drain current during OCP operation,

VOCP is the overcurrent detection threshold voltage

(−0.6 V), and

IOCP is the OCP pin source current (−40 μA).

C4

Input compensation

current, I

C3

8

D/ST

2

VCC

D6

DX1

R4

DZX1

C7

S/GND

1

VROCP ′ = −|R OCP × IDP(OCP) ′|

RX1

D7

LC554xLD I

OCP

(9)

OCP 3

= −(|VOCP | + |R3 × IOCP | − R3 × I) .

R3

IDP(OCP) C5

ROCP

OCP input voltage, Vfw2

Figure 8-27. OCP Input Compensation Circuit

100 V

0

The overcurrent detection threshold voltage with an

OCP input compensation circuit, VROCP', is calculated by

Equation (9).

When VROCP' with reference to the S/GND pin becomes

equal to the sum of VOCP, the voltage across R3 (i.e., R3

× IOCP), and R3 × I, OCP is activated (see Figure 8-30).

230 V

VZX1

Where:

VROCP' is the overcurrent detection threshold voltage

with an OCP input compensation circuit,

IDP(OCP)' is the peak drain current during OCP operation

with OCP input compensation circuit,

VOCP is the overcurrent detection threshold voltage

(−0.6 V),

IOCP is the OCP pin source current (−40 μA), and

I is the input compensation current.

Thus, the overcurrent detection threshold voltage will

be changed by adding the OCP input compensation circuit

for limiting the output power.

AC

Vfw1

0

Vfw2

OCP 3

AC

VOCP

S/GND

1

ROCP

IDP

R3

OCP input compensation starting point

Vfw1 ≒ VZX1

Figure 8-28. Vfw1 and Vfw2 vs. AC Input Voltages

VOCP

ROCP

ROCP × IDP

R3

R3 × IOCP

IOCP

R3 × IOCP

8.6.3. OCP Threshold Voltage with or

without Compensation Circuit

ROCP × IDP

The overcurrent detection threshold voltage without an

OCP input compensation circuit, VROCP, is calculated by

Equation (8). When VROCP with reference to the S/GND

pin becomes equal to the sum of VOCP and the voltage

across R3 (i.e., R3 × IOCP), OCP is activated (see Figure

8-29).

VOCP

IDP

Drain current

Increased

Figure 8-29. Without OCP Input Compensation

Function

VROCP = −|R OCP × IDP(OCP) |

(8)

= −(|VOCP | + R3 × |IOCP |) .

LC5540LD-DSE Rev.2.0

SANKEN ELECTRIC CO., LTD.

Mar. 05, 2020

https://www.sanken-ele.co.jp/en/

© SANKEN ELECTRIC CO., LTD. 2011

20

�LC5540LD Series

R OCP × |IDP(OCP) ′| = |VOCP |

+ R3 × |IOCP |– R3 × I

OCP 3

VOCP

VOCP

S/GND

IDP'

1

ROCP

ROCP × IDP'

RX1

R3

ROCP

(11)

R3 × IOCP

R3

R3 × I

IDP(OCP)' in the maximum AC input voltage should be

set to the peak drain current where the output current is

equal to “IOUT with appropriate input compensation” in

Figure 8-26.

The input compensation current, I, can be expressed by

the following equation obtained from Equations (10) and

(11):

IOCP

I

R3 × IOCP

R3 × I

ROCP × IDP'

|VOCP | + R3 × (|IOCP | − I)

∴ |IDP(OCP) ′| =

.

R OCP

VOCP

I = (|IDP(OCP) | − |IDP(OCP) ′|) ×

Drain current

IDP'

Decreased

(12)

The forward voltage, Vfw1, at C2 peak voltage

VIN(PK)MAX in the maximum AC input voltage is expressed

as follows:

Figure 8-30. With OCP Input Compensation Function

Vfw1 =

8.6.4. Determining OCP Input

Compensation Circuit Component

Values

The component symbols used in this section are

represented as follows:

IDP is the peak drain current of the power MOSFET,

VFX1 is the forward voltage of the rectifier diode DX1,

VZX1 is the Zener voltage of the Zener diode DZX1,

VOCP is the overcurrent detection threshold voltage

(−0.6 V),

IOCP is the OCP pin source current (−40 µA), and

I is the input compensation current.

For other component numbers, such as resistors, see

Figure 8-27.

The peak drain current during OCP operation without

OCP input compensation circuit, IDP(OCP), is expressed by

Equation (10) obtained from Figure 8-29. IDP(OCP) is equal

to the drain current limited by overcurrent detection

threshold voltage without OCP input compensation in the

minimum AC input voltage condition.

R OCP × |IDP(OCP) | = |VOCP | + R3 × |IOCP |

|VOCP | + R3 × |IOCP |

∴ |IDP(OCP) | =

.

R OCP

R OCP

.

R3

(10)

The peak drain current during OCP operation with

OCP input compensation circuit, IDP(OCP)', is expressed by

Equation (11) obtained from Figure 8-30:

ND × VIN(PK)MAX

.

Np

(13)

To supply input compensation current, I, in the

maximum AC input voltage, calculate RX1 value as the

following steps:

The input compensation current, I, can be expressed by

the following equation:

I=

Vfw1 − VZX1 − VFX1

.

R X1 + R3 + R OCP

(14)

Assuming R3