Application Information

SLA7070MPRT Series Unipolar 2-Phase

Stepper Motor Driver ICs

General Description

This document describes the SLA7070MPRT series,

which are unipolar 2-phase stepping motor driver ICs. The

SLA7070MPRT series employs a clock input method as

a control signal input method, enabling full control of the

device operation using only a few signal lines, instead of

the conventional phase input method that requires about 10

signal lines. This allows simplification of the circuit design

and a reduced workload on the control microprocessor.

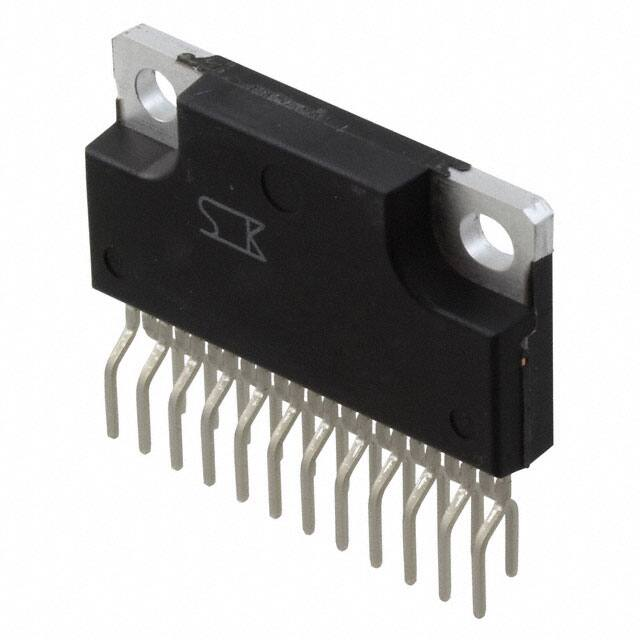

Figure 1. SLA7070MPRT packages are fully molded ZIPs with an

exposed pad for heatsink mounting.

In addition, the SLA7070MPRT series is improved in its

reliability by preventing the IC from damage due to abnormal conditions. For example, it has a flag output terminal

to signal that a protection circuit has operated. The series

also has a built-in protection circuitry against motor coil

opens/shorts and thermal shutdown protection as well.

• Built-in sense resistor, RSInt

• All variants are pin-compatible for enhanced

design flexibility

• ZIP type 23-pin molded package (SLA package)

• Self-excitation PWM current control with fixed off-time

(microstepping options off-time adjusted automatically by

step reference current ratio; 3 levels)

• Built-in synchronous rectifying circuit reduces losses at

PWM-off

• Synchronous PWM chopping function prevents motor

noise in Hold mode

• Sleep mode for reducing the IC input current in

stand-by state

• Built-in protection circuitry against motor coil

opens/shorts and thermal shutdown protection options

All the SLA7070MPRT series ICs are compatible in their

pin layouts and interface specifications, allowing customers the flexibility of choosing the IC that is optimal for the

target equipment characteristics.

Features and Benefits

• Power supply voltages, VBB : 46 V (max.), 10 to 44 V

normal operating range

• Logic supply voltages, VDD : 3.0 to 5.5 V

• Maximum output currents: 1 A, 1.5 A, 2 A, 3 A

• Built-in sequencer

• Full-, half-, and microstepping available (microstepping

options are capable of full-, half-, quarter-, eighth-, and

sixteenth-stepping

Applications

• LBPs, PPCs, ATMs, industrial robots, and so forth

The SLA7070MPRT series product variants and optional features

Part Number

Output Current

(IOUT)

(A)

SLA7070MPRT

1

SLA7071MPRT

1.5

SLA7072MPRT

Full and

half step

2

SLA7073MPRT

3

SLA7075MPRT

1

SLA7076MPRT

SLA7077MPRT

SLA7078MPRT

SLA7070MPRT-AN, Rev. 2.1

January 10, 2013

Stepping

Rate

Microstep

1.5

2

Input Clock

Edge Detection

Blanking Time

(µs)

Standard

Standard

Rising (positive)

edge

3.2

Rising (positive)

edge

1.7

3

SANKEN ELECTRIC CO., LTD.

http://www.sanken-ele.co.jp/en/

�Table of Contents

Specifications

Functional Block Diagrams

Pin Descriptions

Package Outline Drawing

Electrical Characteristics

Allowable Power Dissipation

Typical Application

3

3

3

5

6

10

11

Device Logic

12

Functional Description

23

Application Information

29

Pin Logic and Timing

Common Input Pins

Monitor Output Pin

Logic Input Pins

Clock Edge Timing

Reset Release and Clock Input Timing

Logic Level Change

Stepping Sequence Diagrams

Motor Excitation Sequencing

Individual Circuit Descriptions

Monolithic IC (MIC)

Output MOSFET Chip

Sense Resistor

PWM Current Control

Blanking Time

PWM Off-Time

Protection Functions

12

12

12

13

13

13

13

14

21

22

22

22

22

23

23

26

27

Motor Current Ratio Setting (R1, R2, RS)

29

Lower Limit of Control Current

29

Avalanche Energy

29

On-Off Sequence of Power Supply (VBB

and VDD)

30

Motor Supply Voltage (VM) and Main Power

Supply Voltage (VBB)

31

Internal Logic Circuits

31

Reset

31

Clock Input

31

Chopping Synchronous Circuit

31

Output Disable (Sleep1 and Sleep2) Circuits 31

Ref/Sleep1 Pin

32

Logic Input Pins

32

Thermal Design Information

32

Characteristic Data

34

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

2

�Functional Block Diagrams

SLA7070MPRT to SLA7073MPRT: Full and Half step

MIC

PreDriver

Sequencer

and

Sleep Circuit

Protect

Protect

DAC

+

-

Comp

5

20 21 22 23

Reg.

PreDriver

SenseA

OutB

11

OutB

9 16 10 15

OutB

8

OutB

7

VBB

Clock

Reset

M3

6

CW/CCW

18

M1

13

M2

14

Flag

OutA

4

N.C.

OutA

3

Ref/Sleep1

OutA

2

VDD

OutA

1

DAC

Synchro

Control

PWM

Control

OSC

Rs

TSD

SLA707xMPRT

17

+

-

Comp

PWM

Control

OSC

19

SenseB

Rs

12

Sync

Gnd

Pad Side

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

23

Pin Number.

Symbol

1, 2

OutA

Output of phase A

Function

3, 4

¯O¯ ¯u¯¯

¯t ¯A¯

¯

Output of phase A

5

SenseA

6

N.C.

7

M1

8

M2

9

M3

10

Clock

Step clock input

11

VBB

Main power supply (for motor)

12

Gnd

Ground

13

Ref/Sleep1

14

VDD

Power supply to logic

15

Reset

Reset for internal logic

16

CW/CCW

17

Sync

Synchronous PWM control switch input

18

Flag

Output from protection circuits monitor

Phase A current sensing

No connection

Commutation and Sleep2 setting

Input for control current and Sleep1 setting

Forward/reverse switch input

19

SenseB

20, 21

¯O¯ ¯u¯¯

¯t ¯B¯

¯

Output of phase B

22, 23

OutB

Output of phase B

SLA7070MPRT-AN, Rev. 2.1

Phase B current sensing

SANKEN ELECTRIC CO., LTD.

3

�SLA7075MPRT to SLA7078MPRT: Microstep

11

MIC

PreDriver

Sequencer

and

Sleep Circuit

Protect

Protect

DAC

+

-

Comp

5

20 21 22 23

Reg.

PreDriver

SenseA

OutB

9 16 10 15

OutB

8

OutB

7

OutB

6

VBB

Clock

Reset

M3

CW/CCW

18

M2

13

M1

14

MO

OutA

4

Flag

OutA

3

Ref/Sleep1

OutA

2

VDD

OutA

1

Rs

TSD

Synchro

Control

PWM

Control

OSC

DAC

SLA707xMPRT

17

+

-

19

Comp

PWM

Control

SenseB

Rs

OSC

12

Sync

Gnd

Pad Side

2

1

4

3

6

5

8

7

10

9

12

11

14

13

Pin Number.

Symbol

1, 2

OutA

Output of phase A

3, 4

¯O¯ ¯u¯¯

¯t ¯A¯

¯

Output of phase A

5

SenseA

15

18

17

20

19

22

21

23

Function

Phase A current sensing

6

MO

7

M1

8

M2

9

M3

10

Clock

Step clock input

11

VBB

Main power supply (for motor)

Ground

2-phase commutation status monitor output

Commutation and Sleep2 setting

12

Gnd

13

Ref/Sleep1

14

VDD

Input for control current and Sleep1 setting

Power supply to logic

15

Reset

16

CW/CCW

Reset for internal logic

17

Sync

Synchronous PWM control switch input

18

Flag

Output from protection circuits monitor

Forward/reverse switch input

19

SenseB

20, 21

¯O¯ ¯u¯¯

¯t ¯B¯

¯

Output of phase A

22, 23

OutB

Output of phase B

SLA7070MPRT-AN, Rev. 2.1

16

Phase B current sensing

SANKEN ELECTRIC CO., LTD.

4

�Package Outline Drawing, SLA 23-Pin

31 ±0.2

24.4 ±0.2

4.8 ±0.2

φ3.2 ±0.15 x 3.8

16.4 ±0.2

1.7 ±0.1

b

16 ±0.2

5 ±0.5

c

9.9 ±0.2

Japan

a

(Heatsink Pad)

φ3.2 ±0.15

12.9 ±0.2

Gate Flash

2.45 ±0.2

(Measured at

Base of Pins)

+1

9.5 -0.5

4-(R1)

R-end

22 × P1.27±0.5 = 27.94±1

+0.2

0.55 -0.1

(4.3)

+0.2

0.65 -0.1

4.5 ±0.7

(Measured at

Pin Tips)

(Measured at Pin Tips)

31.3 ±0.2

(Includes Mold Flash)

1

2

3

4

5

6

7

9 11 13 15 17 19 21 23

8 10 12 14 16 18 20 22

Unit: mm

Pin material: Cu

Pin Plating: Solder plating (Pb free)

a: Item name 1: SLA707xMRT (x is 0 to 3, or 5 to 8; last digit

of part number, corresponding to current rating and stepping rate)

b: Item name 2: P

c: Lot number:

1st letter is last digit of year

2nd letter is month

January to September: 1 to 9

October: O

November: N

December: D

3rd and 4th are date of manufacture (01 to 31)

Leadframe plating Pb-free. Device composition

includes high-temperature solder (Pb >85%),

which is exempted from the RoHS directive.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

5

�Electrical Characteristics

• This section provides separate sets of electrical characteristic data for each product.

• The polarity value for current specifies a sink as "+ ," and a source as “−,” referencing the IC.

• Please refer to the datasheet of each product for additional details.

Absolute Maximum Ratings Unless specifically noted, TA is 25°C

Characteristic

Symbol

Notes

Rating

Unit

Load (Motor Supply) Voltage

VM

46

V

Main Power Supply Voltage

VBB

46

V

6

V

≤1 μs (5% duty)

7

V

SLA7070MPRT

SLA7075MPRT

1.0

A

1.5

A

2.0

A

3.0

A

Logic Supply Voltage

VDD

Output Current

IO

SLA7071MPRT

SLA7076MPRT

SLA7072MPRT

SLA7077MPRT

Control current value

SLA7073MPRT

SLA7078MPRT

Logic Input Voltage

VIN

−0.3 to VDD+0.3

V

REF Input Voltage

VREF

−0.3 to VDD+0.3

V

Sense Voltage

VRS

Power Dissipation

PD

Junction Temperature

TJ

Without heatsink

±2

V

4.7

W

150

°C

Recommended Operating Conditions Unless specifically noted, TA is 25°C

Min.

Typ.

Max.

Load (Motor Supply) Voltage

Characteristic

VM

–

–

44

V

Main Power Supply Voltage

VBB

10

–

44

V

Logic Supply Voltage

VDD

3.0

–

5.5

V

–

–

90

°C

Case Temperature

SLA7070MPRT-AN, Rev. 2.1

Symbol

Tc

Test Conditions

Surge voltage at VDD pin should

be less than ±0.5 V to avoid

malfunctioning in operation

Measured at pin 12, without

heatsink

SANKEN ELECTRIC CO., LTD.

Unit

6

�Electrical Characteristics Common to All Variants Unless specifically noted, TA is 25°C

Characteristic

Main Power Supply Current

Logic Power Current

Min.

Typ.

Max.

Unit

IBB

Normal mode

Test Conditions

–

–

15

mA

IBBS

Sleep1 and Sleep2 mode

–

–

100

μA

–

–

5

mA

IDD

MOSFET Breakdown Voltage

Maximum Response Frequency

Logic Supply Voltage

Logic Supply Current

VDSS

fclk

VBB = 44 V, ID = 1 mA

100

–

–

V

Clock duty = 50%

250

–

–

KHz

V

VIL

–

–

0.25 × VDD

VIH

0.75 × VDD

–

–

V

IIL

–

±1

–

μA

–

±1

–

μA

–

–

–

V

2.0

–

VDD

V

–

±10

–

μA

VREF –

0.03

–

VREF –

0.03

V

IIH

REF Input Voltage1

REF Input Current

VREF

See figure 1

VREFS

Output off, Sleep1 mode

IREF

SENSE Voltage

VSENSE

Sleep to Enable Recovery Time

Switching Time

Overcurrent Detection

Symbol

Voltage2

VREF = 0 to 1.5 V

Step reference current ratio: 100%

tSE

Sleep1 and Sleep2

100

–

–

μs

tcon

Clock edge to output on

–

2.0

–

μs

tcoff

Clock edge to output off

–

1.5

–

μs

VOCP

At motor coil short-circuit

0.65

0.7

0.75

V

SLA7070MPRT, SLA7075MPRT,

SLA7071MPRT, SLA7076MPRT

–

2.3

–

A

SLA7072MPRT, SLA7077MPRT

–

3.5

–

A

Overcurrent Detection Current

( VOCP / RS )

IOCP

SLA7073MPRT, SLA7078MPRT

–

4.6

–

A

Load Disconnection Undetected Time

topp

From PWM off

–

2

–

µs

Overheat Protection Temperature

Ttsd

Measured at back of device case (after heat

has saturated)

–

140

–

°C

VFlagL

IFlagL = 1.25 mA

–

–

1.25

V

VFlagH

IFlagH = –1.25 mA

VDD –

1.25

–

–

V

Flag Output Voltage

Flag Output Current

1In

2In

IFlagL

–

–

1.25

mA

IFlagH

–1.25

–

–

mA

a state of: Sleep1, IBBS, output off, and Sequencer enabled.

a condition of VSENSE ≥ VOCP , the protection circuit will activate.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

7

�Electrical Characteristics Varying with Stepping Sequence Unless specifically noted, TA is 25°C, VBB = 24 V, VDD = 5 V

SLA7070MPRT, SLA7071MPRT, SLA7072MPRT, and SLA7073MPRT (Full- and Half-Stepping)

Characteristic

Step Reference Current Ratio

PWM Minimum On-Time

PWM Off-Time

Symbol

Mode F

Mode 8

Test Conditions

VREF ≈ VSENSE = 100 V,

VREF = 0 to 1.0 V

Min.

Typ.

Max.

Unit

–

100

–

%

–

70

–

%

ton(min)

–

3.2

–

µs

toff

–

12

–

µs

SLA7075MPRT, SLA7076MPRT, SLA7077MPRT, and SLA7078MPRT (Microstepping)

Mode F

–

100

–

%

Mode E

–

98.1

–

%

Mode D

–

95.7

–

%

Mode C

–

92.4

–

%

Mode B

–

88.2

–

%

Mode A

–

83.1

–

%

–

77.3

–

%

–

70.7

–

%

Mode 9

Step Reference Current Ratio

Mode 8

Mode 7

MO (Load) Output Voltage

MO (Load) Output Current

PWM Minimum On-Time

PWM Off-Time

SLA7070MPRT-AN, Rev. 2.1

VREF ≈ VSENSE = 100 V,

VREF = 0 to 1.0 V

–

63.4

–

%

Mode 6

–

55.5

–

%

Mode 5

–

47.1

–

%

Mode 4

–

38.2

–

%

Mode 3

–

29

–

%

Mode 2

–

19.5

–

%

Mode 1

–

9.8

–

%

–

–

1.25

V

VDD – 1.25

–

–

V

VMOL

IMOL = 1.25 mA

VMOH

IMOH = –1.25 mA

IMOL

–

–

1.25

mA

IMOH

–1.25

–

–

mA

ton(min)

–

1.7

–

µs

toff1

Mode 8, 9, A, B, C, D, E, and F

–

12

–

µs

toff2

Mode 4, 5, 6, and 7

–

9

–

µs

toff3

Mode 1, 2, and 3

–

7

–

µs

SANKEN ELECTRIC CO., LTD.

8

�Electrical Characteristics Varying with Output Current Range Unless specifically noted, TA is 25°C, VBB = 24 V, VDD = 5 V

SLA7070MPRT and SLA7075MPRT (IO = 1.0 A)

Characteristic

Output On-Resistance

Symbol

Test Conditions

Min.

Typ.

Max.

Unit

–

0.7

0.85

Ω

RDS(on)

ID = 1 A

Body Diode Forward Voltage

Vf

If = 1 A

–

0.85

1.1

V

Sense Resistor*

RS

±3% tolerance

0.296

0.305

0.314

Ω

Within specified current limit, IO = 1.0 A

0.04

–

0.3

V

REF Input Voltage

VREF

SLA7071MPRT and SLA7076MPRT (IO = 1.5 A)

Output On-Resistance

Body Diode Forward Voltage

Sense Resistor*

REF Input Voltage

RDS(on)

ID = 1.5 A

–

0.45

0.6

Ω

Vf

If = 1.5 A

–

1.0

1.25

V

RS

±3% tolerance

0.296

0.305

0.314

Ω

Within specified current limit, IO = 1.5 A

0.04

–

0.45

V

Ω

VREF

SLA7072MPRT and SLA7077MPRT (IO = 2.0 A) Electrical Characteristics

RDS(on)

ID = 2 A

–

0.25

0.4

Body Diode Forward Voltage

Output On-Resistance

Vf

If = 2 A

–

0.95

1.2

V

Sense Resistor*

RS

±3% tolerance

0.199

0.205

0.211

Ω

Within specified current limit, IO = 2.0 A

0.04

–

0.4

V

–

0.18

0.24

Ω

REF Input Voltage

VREF

SLA7073MPRT and SLA7078MPRT (IO = 3.0 A) Electrical Characteristics

Output On-Resistance

RDS(on)

ID = 3 A

Body Diode Forward Voltage

Vf

If = 3 A

–

0.95

2.1

V

Sense Resistor*

RS

±3% tolerance

0.150

0.155

0.160

Ω

Within specified current limit, IO = 3.0 A

0.04

–

0.45

V

REF Input Voltage

VREF

*Includes the inherent bulk resistance (approximately 5 mΩ) of the resistor itself.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

9

�VDD

Sleep 1 Set Range

2.0V

Prohibition Zone

VOCP = 0.7 V

0.45V

0.4V

0.3V

1.0 A

Devices

0V

2.0 A

Devices

1.5 A and

3.0 A

Devices

Motor Current Set Range*

*Motor Current Set Range is determined

by the value of the resistor built into the device.

Figure 1. Reference Voltage Setting (VREF, REF/SLEEP1 Pin). Please pay extra

attention to the change-over between the motor current specification range, IMO , and

the Sleep1 Set Range. VOCP falls on the "prohibition zone" threshold. If the changeover time is too slow, OCP operation will start when VSInt > VOCP.

Allowable Power Dissipation, PD [W]

5

4

Rθj-a=26.6℃/W

3

2

1

0

0

10

20

30

40

50

60

70

Ambient Temperature, T A [℃]

80

90

Figure 2. Allowable Power Dissipation

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

10

�Typical Application

(Microstepper Variants)

Vs =10 to 44 V

VCC =3.0 to 5.5V

Sleep

R1

Q1

C1

OutA

VDD

OutA

Reset/Sleep1

Clock

CW/CCW

M1

M2

M3

Sync

Mo

Flag

Ref/Sleep

Sense A

CB

Microcontroller

R2

R3

VBB

OutB

OutB

CA

SLA7075MPRT

SLA7076MPRT

SLA7077MPRT

SLA7078MPRT

Gnd

Sense B

C2

Pin12

Gnd

Logic Gnd

Power Gnd

Figure 3. Typical Application Circuit

External Component Typical Values

(for reference use only):

Component

Value

Component

Value

R1

10 kΩ

CA

100 μF / 50 V

R2

1 kΩ (varistor)

CB

10 μF / 10 V

R3

10 kΩ

C1

0.1 μF

SLA7070MPRT-AN, Rev. 2.1

• Take precautions to avoid noise on the VDD line; noise

levels greater than 0.5 V on the VDD line may cause device

malfunction. Noise can be reduced by separating the logic

ground and the power ground on a PCB from the GND pin

(pin 12).

• Unused logic input pins (CW / CCW, M1, M2, M3, Reset,

and SYNC) must be pulled up or down to VDD or ground. If

those unused pins are left open, the device malfunctions.

• Unused logic output pins (Mo, Flag) must be kept open.

SANKEN ELECTRIC CO., LTD.

11

�Truth Tables

Common Input Pins

Table 1 shows the truth table for input pins common to both

half/full step and microstep variants of the SLA7070MPRT

series.

• The Reset function is asynchronous. If the input on the Reset

pin is high, the internal logic circuit is reset. At this point, if the

Ref pin stays low, then the DMOS outputs turn on at the starting

point of excitation. Note that the Disable control functions are not

available with the Reset pin signal set high.

• Voltage at the Ref / Sleep1 pin controls the PWM current and

the Sleep1 function. For normal operation, VREF should be below

1.5 V (low level). Applying a voltage greater than 2.0 V (high

level) to the Ref / Sleep1 pin disables the outputs and puts the

motor in a free state (coast). This function is used to minimize

power consumption when the device is not in use. Although

it disables much of the internal circuitry, including the output MOSFETs and regulator, the sequencer / translator circuit

remains active.

• The Sync function is active only for 2-phase excitation timing.

If this function is used during other than 2-phase excitation timing, the overall stepping sequence might collapse because PWM

off-time and set current are different in each phase A and phase

B control scenario. (2-phase excitation timing is when the step

reference current ratio of both phase A and phase B is Mode 8.)

Commutation/Sleep2 Function

Table 2 shows the logic of the pins (M1, M2, and M3) which set

commutation. In the Sleep2 function, the outputs are disabled and

the driver supply current (IBB) is reduced. However, unlike the

Sleep1 function, the logic circuitry is put into a standby state and

therefore the sequencer / translator circuit is not active.

Note: When awakening from Sleep2 mode, a delay of 100 μs or

longer before sending a Clock pulse is recommended.

Monitor Output Pin

The SLA7070MPRT series provides two device status monitor

outputs:

• Flag pin – Protection feature operation

• Mo pin (microstep variants only) – Stepping sequence

Table 3 shows the logic for the monitor pins. The outputs turn off

when the protection circuit starts operating. To release the protection state, cycle (set low, and then high) the logic supply voltage

(VDD).

Table 2. Commutation-Sleep2 Truth Table for

Common Input Pins (Half/Full and Microstep)

Pin Name

M1

M2

M3

Full / Half Step

Microstep

L

L

L

Full step (Mode 8 fixed)

Full step (Mode 8 fixed)

H

L

L

Full step (Mode F fixed)

Full step (Mode F fixed)

L

H

L

Half step

Half step

H

H

L

Half step (Mode F fixed)

Half step (Mode F fixed)

L

L

H

H

L

H

L

H

H

H

H

H

Quarter step

Eighth step

Sleep2 function

Sixteenth step

Sleep2 function

Table 3. Monitor Output Pins Logic

Pin Name

Low Level

High Level

Flag

Normal operation

Protection circuit operation

Mo

Other than 2-phase

excitation timing

2-phase excitation timing

Table 1. Truth Table for Common Input Pins (Half/Full and Microstep)

Pin Name

Low Level

High Level

Reset

Normal operation

Logic reset

CW/CCW

Forward (CW)

Reverse (CCW)

M1, M2, M3

SLA7070MPRT-AN, Rev. 2.1

Clock

Commutation (Sleep2 is not included)

Ref / Sleep1

Normal operation

Sleep1 function

Sync

Non-sync PWM control

Sync PWM control

SANKEN ELECTRIC CO., LTD.

(Positive Edge)

12

�Logic Input Pins

The low pass filter incorporated with the logic input pins (Reset,

Clock, CW/CCW, M1, M2, M3, and Sync) improves noise rejection. The logic inputs are CMOS input compatible, and therefore

they are in a high impedance state. Use the IC at a fixed input

level, either low or high.

edges and as setup and hold times. The sequencer logic circuitry

might malfunction if the logic polarity is changed during these

setup and hold times. (Refer to figure 4).

Input Logic Timing

When the timing of a Reset release (falling edge) and a Clock

edge is simultaneous, the internal logic might cause an unexpected operation. Therefore, a greater than 5 μs delay is required

between the falling edge of the Reset input and the next rising

edge of the Clock input. (Refer to figure 4).

Clock Signal

A low-to-high then high-to-low transition on the Clock input

advances the sequencer / translator. The Clock pulse width should

be set at 2 μs in both positive and negative polarities. Therefore,

clock response frequency should be 250 kHz. Only the positive

edge is used for timing, however, it is necessary to control the

logic levels of the Clock signal both before and after each Clock

signal edge sent to the sequencer logic circuit, in order to maintain proper stepping operation.

Clock Edge Timing

With regard to the input logic of the CW/CCW, M1, M2, and M3

pins, a 1 μs delay should occur both before and after the pulse

Reset

Clock

CW/CCW

M1, M2, M3

2 µs(min)

Reset Release and Clock Input Timing

The Reset pulse width is equivalent to the high pulse level hold

time. It should be greater than the 2 μs Clock input pulse width.

Logic Level Change

Logic level inputs on CW/CCW, M1, M2, and M3 set the translator step direction (CW/CCW) and step mode (M1, M2, and M3;

refer to the Commutation Truth Table). Changes to these inputs

do not take effect until the rising edge of the Clock input. However, depending on the type and state of a motor, there may be

errors in motor operation. A thorough evaluation on the changes

of sequence should be carried out.

5 µs(min)

4 µs(min)

2 µs(min)

2 µs(min)

1 µs(min) 1 µs(min)

2 µs(min)

1 µs(min) 1 µs(min)

2 µs(min)

Figure 4. Input Signal Timing. When awakening from Sleep1 or Sleep2 mode, a delay of 100 μs or

longer before sending a Clock pulse is recommended.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

13

�Stepping Sequence Diagrams

RESET

CLOCK

0

2

1

B

CW

A

A

0

70.7

0

70.7

CCW

B

Figure 5. Full step; for microstep and full/half step products

Sequence Selection

Mode

Full Step

8

Pin Logic

M1

M2

M3

Low

Low

Low

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

14

�R ES ET

C LO C K

0

1

2

B

CW

A

A

0

CCW

0

0

10

B

Figure 6. Full step; for microstep and full/half step products

Sequence Selection

Mode

Full Step

F

Pin Logic

M1

M2

M3

High

Low

Low

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

15

�RESET

CLOCK

0

1

2

3

4

B

CW

A

A

0

70.7

0

10

0

70.7

CCW

B

Figure 7. Half step; for microstep and full/half step products

Sequence Selection

Mode

Half Step

8, F

Pin Logic

M1

M2

M3

Low

High

Low

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

16

�RESET

CLOCK

0

1

2

3

4

B

CW

A

A

0

10

0

0

CCW

B

Figure 8. Half step; for microstep and full/half step products

Sequence Selection

Mode

Half Step

F

Pin Logic

M1

M2

M3

High

High

Low

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

17

�RESET

…

CLOCK

0

1

2

3

4

5

6

7

8

B

CW

A

A

0

38.2

70.7

CCW

0

38.2

70.7

92.4

10

0

92.4

B

Figure 9. Quarter step; for microstep products

Sequence Selection

Mode

Quarter

Step

SLA7070MPRT-AN, Rev. 2.1

Pin Logic

M1

M2

M3

Low

Low

High

SANKEN ELECTRIC CO., LTD.

18

�RESET

…

CLOCK

0

1

2

3

4

5

6

7

8

1

0

9

1

1

1

2

1

3

1

4

1

5

1

6

B

CW

A

A

0

19.5

38.2

55.5

70.7

83.1

0

19.5

38.2

55.5

70.7

83.1

92.4

CCW

10

0

98.1

92.4

98.1

B

Figure 10. Eighth step; for microstep products

Sequence Selection

Mode

Eighth

Step

Pin Logic

M1

M2

M3

High

Low

High

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

19

�RESET

CLOCK

0

1

2

3

4

5

6

7

8

9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

3

2

…

B

CW

A

A

0

9.8

19.5

29.0

38.2

47.1

55.5

63.4

70.7

77.3

CCW

0

9.8

19.5

29.0

38.2

55.5

63.4

70.7

77.3

47.1

B

92.4

98.1

88.2

83.1

95.7

10

0

98.1

83.1

88.2

95.7

92.4

Figure 11. Sixteenth step; for microstep products

Sequence Selection

Mode

Sixteenth

Step

Pin Logic

M1

M2

M3

Low

High

High

Shows the state to which the stepping sequence progresses at the rising

(positive) edge of the Clock input.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

20

�Excitation Change Sequence

The change of excitation modes is determined by the settings of

the excitation pins (M1, M2, and M3) before and after the step

signal.Table 4 shows each excitation mode state setting.

Table 4. Excitation Mode States

Direction

Internal Sequence State

Phase A

Phase B

PWM

Mode

PWM

Mode

Full Step

Mode 8

Mode F

Step Sequencing

Half Step

1/4 Step

Mode 8, F

Mode F

1/8 Step

A

8

B

8

X

X*

X

X*

X

A

7

B

9

A

6

B

A

A

5

B

B

A

4

B

C

X

Counter

A

3

B

D

Clockwise

A

2

B

E

A

1

B

F

–

–

B

F

X

X

X

1

B

F

A

¯

2

B

E

A

¯

3

B

D

A

¯

4

B

C

X

A

¯

5

B

B

A

¯

6

B

A

A

¯

7

B

9

A

¯

8

B

8

X

X*

X

X*

X

A

¯

9

B

7

A

¯

A

B

6

A

¯

B

B

5

A

¯

C

B

4

X

A

¯

D

B

3

A

¯

E

B

2

A

¯

F

B

1

A

¯

F

–

–

X

X

X

A

¯

F

1

A

¯

B

¯

E

2

A

¯

B

¯

D

3

A

¯

B

¯

C

4

X

A

¯

B

¯

B

5

A

¯

B

¯

A

6

A

¯

B

¯

9

7

A

¯

B

¯

8

8

X

X*

X

X*

X

A

¯

B

¯

7

9

A

¯

B

¯

6

A

A

¯

B

¯

5

B

A

¯

B

¯

4

C

X

A

¯

B

¯

3

D

A

¯

B

¯

2

E

A

¯

B

¯

1

F

A

¯

B

¯

–

–

F

X

X

X

B

¯

A

1

F

B

¯

A

2

E

B

¯

A

3

D

B

¯

A

4

C

X

B

¯

A

5

B

B

¯

A

6

A

B

¯

A

7

9

B

¯

A

8

8

X

X*

X

X*

X

B

¯

A

9

7

B

¯

A

A

6

B

¯

A

B

5

B

¯

A

C

4

X

B

¯

A

D

3

B

¯

A

E

2

B

¯

A

F

1

B

¯

A

F

–

–

X

X

X

A

F

B

1

A

E

B

2

A

D

B

3

Clockwise

A

C

B

4

X

A

B

B

5

A

A

B

6

A

9

B

7

∗ Sequence state is Mode 8, but step reference current ratio is Mode F. Mode F has step reference current ratio of 100%, and PWM off-time of 12 μs.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1/16 Step

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

21

�Individual Circuit Descriptions

Monolithic IC (MIC)

• Sequencer Logic The single Clock input is used for step timing. Direction is controlled by the CW/CCW input. Commutation

mode is controlled by the combination of the M1, M2, and M3

inputs logic levels. For details, refer to the Commutation Truth

Table.

• PWM Control Each pair of outputs is controlled by a fixed offtime PWM current-control circuit. The internal oscillator (OSC)

sets the off-time. Its operation mechanism is identical to that of

the SLA7070M family. Refer to the PWM Current Control section for further details.

• Synchronous Control This function prevents occasional

motor noise during Hold mode, which normally results from

asynchronous PWM operation of both motor phases. A logic

high at the Sync input sets synchronous operation. A logic low

sets asynchronous operation. The use of synchronous operation

during normal stepping is not recommended because it produces

less motor torque and can cause motor vibration due to staircase

current. The use of synchronous operation when the motor is not

in operation is allowed only in full/half step sequence timing, due

to the difference in the current controlled and PWM off-time at

other step sequence timings.

• DAC (D-to-A Converter) In microstep sequencing, the current at each step is set by the value of a sense resistor (RSInt), a

reference voltage (VREF), and the output voltage of the DACs,

controlled by the output of the sequencer / translator). Please refer

the electric characteristic, Step Reference Current Ratio, page 8.

• Regulator Circuit The integrated regulator circuit is used in

driving the output MOSFET gates and powering other internal

linear circuits.

SLA7070MPRT-AN, Rev. 2.1

• Protect Circuit A built-in protection circuit against motor coil

opens or shorts is provided. Protection is activated by sensing

voltage on the internal RSInt resistors; therefore, an overcurrent

condition cannot be detected which results from the the Outx pins

or Sensex pins, or both, shorting to Gnd. Protection against motor

coil opens is available only during PWM operation; therefore,

it does not work at constant voltage driving, when the motor is

rotating at high speed. Operation of the protection circuit disables

all of the DMOS outputs. To come out of protection mode, cycle

the logic supply, VDD .

• TSD circuit This circuit protects a driver by shifting the output

to Disable mode when the temperature of a product control IC

(MIC) rises and becomes higher than threshold value. In order to

reset, cycle the logic supply, VDD .

Output MOSFET Chip

The value of the built-in output DMOS chip varies according

to which of the four different output current ratings has been

selected.

Sense Resistor

The resistance varies according to which of the four different

output current ratings has been selected, as follows:

Output Current

(A)

RSInt Resistance

(Ω typ)

1

0.305

1.5

0.305

2

0.205

3

0.155

Each resistance shown above includes the inherent resistance

(approximately 5 mΩ) in the resistor itself.

SANKEN ELECTRIC CO., LTD.

22

�Functional Description

PWM Current Control

Blanking Time

The actual operating waveforms on the Sensex pins when driving

a motor are shown in figure 12. The actual operating waveforms

on the Sensex pins when driving a motor are shown in figure 13.

Immediately after PWM turns OFF, ringing (or spike) noise on

the Sensex pins isobserved for a few μs. Ringing noise can be

generated by various causes, such as capacitance between motor

coils and inappropriate motor wiring.

Each pair of outputs is controlled by a fixed off-time (7 to 12 μs,

depending on stepping mode) PWM current-control circuit that

limits the load current to a target value, ITRIP . Initially, an output

is enabled and current flows through the motor winding and the

current-sense resistors. When the voltage across the current sense

resistor equals the DAC output voltage, VTRIP , the current sense

comparator resets the PWM latch. This turns off the driver for the

fixed off-time, during which the load inductance causes the current to recirculate for the off-time period. Therefore, if the ringing

noise on the sense resistor equals and surpasses VTRIP , PWM

turns off.

To prevent this phenomenon, the blanking time is set to override

signals from the current-sense comparator for a certain period

immediately after PWM turns on.

5 µs/div

PWM Pulse Width

A

tOFF

(Fixed)

tON

ITRIP

0

A

Blanking Time

Figure 13. Sensex pin waveform during PWM control

500 ns/div

ITRIP

ITRIP

Figure 12. Operating waveforms on the Sensex pins during PWM chopping (circled area of left

panel is shown in expanded scale in right panel)

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

23

�• Blanking time and seeking phenomenon Although current

control can be improved by shortening blanking time, the degree

of margin to a ringing noise decreases simultaneously. For this

reason, when a motor is driven by the device, a seeking phenomenon may occur. Figure 14 shows an example of the waveform

when the phenomenon occurs.

• Blanking time difference The difference in blanking time is

shown in table 5. This comparison is based on the case where

drive conditions, such as a motor, motor power supply voltage,

and Ref input voltage, and a circuit constant were kept the same

while only the indicated parameter was changed.

▫ Minimum PWM On-time ton(min) . The product blanking time is

fixed by the PWM control. Thus, when the on-time is shortened

in order to reduce the current, it would not go below the blanking

time. Minimum PWM On-time refers to the time the output is

on during this blanking period, that is, when the output MOSFET

actually is turned on. In other words, the blanking time determines the minimum time (small in table 5).

▫ Minimum coil current. This refers to the coil current when

PWM control is performed during PWM minimum on-time. In

other words, when the coil current is reduced when the power is

reduced, where blanking time is shorter can reduce current.

• Coil current waveform distortion during a high velocity

revolution While a microstep drive is active, the ITrip value

changes with the Clock input, to the predetermined value. The

Itrip value (internal reference voltage splitting ratio) is set up to be

a sine wave. Because PWM control of the motor coil current is

set according to the Itrip value, the coil current will be controlled

to be sine wave-like. In fact, according the inductance characteristic of the coil, the device requires some time to bring the coil

current completely to the targeted value.

Roughly, the relationship between the convergence time (tconv)

between the Itrip value of the coil current and the duty cycle (tclk)

of the input Clock pulse in any mode is:

tconv < tclk

(1)

where the coil current waveform amplitude serves as the limit

for Itrip .

When the current attempts to increase, the full limits of tconv are

determined by the damping time constant of power supply voltage and the coil used. When the current attempts to decrease, the

limits are determined by the power supply voltage, the damping

time constant, and the minimum on-time.

When the frequency of the input clock is raised, because tclk

becomes small, it is normal that the case will occur in which the

coil current cannot be raised to the Itrip value within a single clock

period. In this situation, the waveform amplitude of the coil current degenerates from the sine wave, referred to as waveform distortion.

20 µs/div

Table 5. Characteristic Comparison by the

Difference in Blanking Time

Parameter

Better Performance

Internal Blanking Time Setting

Short

PWM minimum on-time

Short

Maximize ringing noise suppression

Minimum coil current

Coil current waveform distortion at a

high rotation (mainly microstep)

Long

←

→

Small

Large

←

→

Large

Figure 14. Example of a Sensex terminal waveform during hunching

phenomenon

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

24

�Figure 15 shows the compared result of the waveform distortion by observing the waveform of various devices for which the

operating condition of power supply voltage, the current preset

value, the motor, and so forth are kept the same. As shown in the

places circled (blanking time) in the figure, while the amplitude

envelope of the Sensex pin waveform, which is the same as the

current waveform, in the 1.7 μs case has become sine wave-like,

the blanking time in the 3.2 μs case has degenerated from an ideal

sine wave.

The term Large in table 5 means that the wave distortion will be

less where the blanking time is longer, assuming the same drive

conditions, while the wave distortion will be larger where the

blanking time is shorter, if the Clock frequency is the same. In

addition, when such waveform distortion is confirmed, there is

uncertainty if the motor characteristic will be affected. Therefore,

please make a final judgment after evaluating very thoroughly.

Blanking Time: 1.51.5

µs (typ)typ(

Clock

SenseA

SenseB

500 µs/div

Figure 15. Comparison of a Sense terminal waveform during high speed revolution

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

25

�PWM Off-Time

The PWM off-time for the SLA7070MPRT series is controlled

at a fixed time by an internal oscillator. It also is switched in

three levels by current proportion (see the Electrical Characteristics table). In addition, the SLA7070MPRT series provides a

function that decreases losses occurring when the PWM turns

off. This function dissipates back EMF stored in the motor coil

at MOSFET turn-on, as well as at PWM turn-on (synchronous

rectification operation).

Figure 16 shows the difference in back EMF generation

between the SLA7060M series and SLA7070MPRT series. The

SLA7060M series performs on–off operations using only the

MOSFET on the PWM-on side, but the SLA7070MPRT series

also performs on–off operations using only the MOSFET on

the PWM-off side. To prevent simultaneous switching of the

MOSFETs at synchronous rectification operation, the IC has a

dead time of approximately 0.5 μs. During dead time, the back

EMF flows through the body diode of the MOSFET.

SLA7060M Series

SLA7070MPRT Series

VBB

VBB

Ion

Ioff

Ion

Ioff

Stepper Motor

Stepper Motor

Vg

Vg

Vg

Vg

Back EMF at Dead Time

VS

+V

PWM On

RSExt

PWM Off

VS

+V

PWM On

Vg

Vg

FET Gate 0

Signal

t

PWM On

Dead

Time

FET Gate 0

Signal

Vg

RSInt

PWM Off

PWM On

Dead

Time

t

Vg

VREF

VREF

VS

VS

0

t

0

t

Figure 16. Synchronous rectification operation

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

26

�Protection Functions

The SLA7070MPRT series includes a motor coil short-circuit

protection circuit, a motor coil open protection circuit, and an

overheating protection circuit. An explanation of each protection

circuit is provided below.

• Motor Coil Short-Circuit Protection (Load Short) Circuit.

This protection circuit, embedded in the SLA7070MPRT series,

begins to operate when the device detects an increase in the sense

resistor voltage level, VRS. The voltage at which motor coil shortcircuit protection starts its operation, VOCP , is set at approximately 0.7 V. The output is disabled at the time the protection

circuit starts, where VRS exceeds VOCP . (See figure 17.)

• Motor Coil Open Protection (Patent acquired) Driver destruction can occur when one output pin (motor coil) is disconnected

in a unipolar drive during operation. This is because a MOSFET

connected after disconnection will be in the avalanche breakdown state, where very high energy is added with back EMF

when PWM is off. With an avalanche state, an output cancels

the energy stored in the motor coil where the resisting pressure

between the drain and source of the MOSFET is reached (the

condition which caused the breakdown).

Although MOSFETs with a certain amount of avalanche energy

tolerance rating are used in the SLA7070MPRT series, avalanche

energy tolerance falls as temperature increases.

Because high energy is added repeatedly whenever PWM operation disconnects the MOSFET, the temperature of the MOSFET

rises, and when the applied energy exceeds the tolerance, the

driver will be destroyed. Therefore, a circuit which detects

this avalanche state and protects the driver was added in the

SLA7070MPRT series. The operation is shown in figure 18.

As explained above, when the motor coil is disconnected, the

accumulated voltage in the MOSFET causes a reverse current to

flow during the PWM off-time. For this reason, VRS that is negative during the PWM off-time in a normal operation becomes

positive when the motor coil is disconnected. Thus, a disconnected motor is detectable by sensing that VRS in the PWM offtime is positive.

In the SLA7070MPRT series, in order to avoid detection malfunctions, when a state of motor disconnection is detected 3 times

continuously, the protection functions are enabled (figure 19).

Note: When the breakdown of an output is confirmed by the

occurrence of surge noise after PWM turn-off, when a breakdown

condition continues after an overload disconnection undetected

time (topp) has elapsed, even if the load is not actually disconnected, a protection feature may operate. Please review the placement of the motor, wiring, and so forth to improve and to settle

the breakdown time within the load disconnection undetected

time (topp) (application variations also must be taken into consideration). When the breakdown is not confirmed, there will be no

issue in operation. Moreover, the device may be made to operate

normally by inserting a capacitor for surge noise suppression

between the Out and Gnd pins as one possible corrective strategy.

VM

Coil Short Circuit

+V

Coil Short Circuit

Stepper Motor

VS

RSInt

Output Disable

VOCP

VREF

Vg

Normal Operation

VS

0

t

Figure 17. Motor coil short circuit protection circuit operation. Overcurrent that flows without passing the sense resistor is undetectable.

To recover the circuit after protection operates, VDD must be cycled and started up again.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

27

�Surge does not

reach VDSS level

When the product temperature rises and exceeds Ttsdk , the protection circuit starts operating and all the outputs are set to Disable

mode.

Breakdown period

shorter than tOPP

tOPP

Breakdown period

longer than tOPP

tOPP

tOPP

VDSS

Note: This product has multichip composition (one IC for control,

four MOSFETs, and two chip resistors). Although the location which actually detects temperature is the control IC (MIC),

because the main heat sources are the MOSFET chips and the

chip resistors, which are separated by a distance from the control

IC, some delay will occur while the heat propagates to the control

IC. For this reason, because a rapid temperature change cannot

be detected, please perform worst-case thermal evaluations in the

application design phase.

VOUT

tCONFIRM

tCONFIRM

No problem

tCONFIRM

No problem

Improvement

required

Figure 19. Coil Open Protection (Patent acquired)

PWM Operation

at Normal Device Operation

VM

PWM Operation

at Motor Disconnection

VM

Stepper Motor

Stepper Motor

Ion

Ioff

Disconnection

Vg

Vg

VOUT

VOUT

VRS

RS

VRS

RS

Motor

Disconnection

FET

Gate Signal

Vg

0

FET

Gate Signal

Vg

0

VDSS

Vout

2 VM

VM

Vout

0

VREF

VREF

VRS

VRS

0

Breakdown (Avalanche state)

0

0

Motor

Disconnection

Sense

Figure 18. Motor coil short circuit protection circuit operation. Overcurrent that flows without passing the sense resistor is undetectable.

To recover the circuit after protection operates, VDD must be cycled and started up again.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

28

�Application Information

Motor Current Ratio Setting (R1, R2, RS)

The setting calculation of motor current, IOUT , for the

SLA7070MPRT series is determined by the ratios of the external

components R1, R2, and current sense resistor, RS. The following

is a formula for calculating IOUT:

R2

IOUT =

VDD / RS

(2)

R1 + R2

when VREF is within specification. If VREF is set less than 0.1 V,

variation or impedance of the wiring pattern may influence the IC

and the possibility of less accurate current sensing becomes high.

The standard voltage for current ITrip that the SLA7070MPRT

series controls is partially divided by the internal DAC:

ITrip =

VREF

Mode Proportion

RS

(3)

Lower Limit of Control Current

The SLA7070MPRT series uses a self-oscillating PWM current

control topology in which the off- time is fixed. As energy stored

in motor coil is eliminated within the fixed PWM off-time, coil

current flows intermittently, as shown in figure 20. Thus, average

current decreases and motor torque also decreases.

The point at which current starts flowing to the coil is considered

as the lower limit of the control current, IOUT(min) , where IOUT is

the target current level. The lower limit of control current differs

by conditions of the motor or other factors, but it is calculated

from the following formula:

IO(min) =

VM

R

1

–t

exp OFF

tc

–1

(4)

RDS(on) is the MOSFET on-resistance,

IO is the target current level,

Rm is the motor winding resistance,

Lm is the motor winding reactance,

tOFF is the PWM off-time, and

tC is calculated as:

where

(5)

tc = Lm / R ,

R

= Rm + RDS(on) + RS

(6)

Even if the control current value is set at less than the lower limit

of the control current, there is no setting at which the IC fails to

operate. However, control current will worsen against setting

current.

Avalanche Energy

In the unipolar topology of the SLA7070MPRT series, a surge

voltage (ringing noise) that exceeds the MOSFET capacity to

withstand might be applied to the IC. To prevent damage, the

SLA7070MPRT series is designed with a built-in MOSFET having sufficient avalanche resistance to withstand this surge voltage. Therefore, even if surge voltages occur, users will be able

to use the IC without any problems. However, in cases in which

the motor harness is long or the IC is used above its rated current

or voltage, there is a possibility that an avalanche energy could

be applied that exceeds Sanken design expectations. Thus, users

must test the avalanche energy applied to the IC under actual

application conditions.

The following procedure can be used to check the avalanche

energy in an application.

where

VM is the motor supply voltage,

A

ITRIP(Big)

ITRIP(Small)

0

A

Figure 20. Control current lower limit model waveform

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

29

�Given:

VM

From the waveform test result (reference figure 22)

VDS(AV) = 140 V,

ID

ID = 1 A, and

Stepper Motor

t = 0.5 μs.

VD S(A V )

The avalanche energy, EAV can be calculated using the following:

EAV = VDS(AV)

1/2

= 140 (V)

1/

2

ID

t

(7)

RSInt

1 (A) 0.5 10-6 (µs)

= 0.035 (mJ)

By comparing the EAV calculated with the graph shown in figure 23, the application can be evaluated if it is safe for the IC,

by being within the avalanche energy-tolerated does range of the

MOSFET.

Figure 21. Test points

V D S(A V )

On-Off Sequence of Power Supply (VBB and VDD)

There is no restriction of the on-off sequence between the main

power supply, VBB, and the logic supply, VDD.

ID

t

Figure 22. Waveform at avalanche breakdown

20

SLA7073M and

SLA7078M

EAV [mJ ]

16

12

SLA7072M

and SLA7077M

8

SLA7071M and

SLA7076M

4

SLA7070M and

SLA7075M

0

0

25

50

75

100

125

150

Product Temperature, Tc [°C]

Figure 23. SLA7070MPRT iterated avalanche energy tolerated level, EAV(max)

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

30

�Motor Supply Voltage (VM) and Main Power Supply

Voltage (VBB)

Because the SLA7070MPRT series has a structure that separates the control IC (MIC) and the power MOSFETs as shown

in the Functional Block diagrams, the motor supply and main

power supply are separated. Therefore, it is possible to drive

the IC using different power supplies and different voltages for

motor supply and main power supply. However, extra caution is

required because the supply voltage ranges differ among power

supplies.

Internal Logic Circuits

Reset

The sequencer/translator circuit of this product is initialized after

logic supply (VDD) is applied, and the power-on reset function

operates. To initialize the sequencer/translator, the output immediately after power-on indicates the status that the power circuits

are in the home state. In a case where the sequencer/translator

must be reset after the motor has been operating, a reset signal

must be input on the Reset pin. In a case in which external reset

control is not necessary, and the Reset pin is not used, the Reset

pin must be pulled to logic low on the application circuit board.

Clock Input

When the Clock input signal stops, excitation changes to the

motor Hold state. At this time, there is no difference to the IC if

the Clock input signal is at the low level or the high level. The

SLA7070MPRT series is designed to move one sequence increment at a time, according to the current stepping mode, when a

positive Clock pulse edge is detected.

Chopping Synchronous Circuit

The SLA7070MPRT series has a chopping synchronous function to protect from abnormal noises that may occasionally occur

during the motor Hold state. This function can be operated by

setting the Sync pin at high level. However, if this function is

used during motor rotation, control current does not stabilize, and

therefore this may cause reduction of motor torque or increased

vibration. So, Sanken does not recommend using this function

while the motor is rotating. In addition, the synchronous circuit

should be disabled in order to control motor current properly in

case it is used other than in dual excitation state (Modes 8 and F)

or single excitation Hold state.

In normal operation, generally the input signal for switching can

be sent from an external microcomputer. However, in applications where the input signal cannot be transmitted adequately due

to limitations of the port, the following method can be taken to

use the functions.

SLA7070MPRT-AN, Rev. 2.1

The schematic diagram in figure 24 shows how the IC is designed

so that the Sync signal can be determined by the Clock input

signal. When a logic high signal is received on the Clock pin,

the internal capacitor, C, is charged, and the Sync signal is set to

logic low level. However, if the Clock signal cannot rise above

logic low level (such as when the circuit between the microcomputer and the IC is not adequate), the capacitor is discharged by

the internal resistor, R, and the Sync signal is set to logic high,

causing the IC to shift to synchronous mode.

The RC time constant in the circuit should be determined by the

minimum clock frequency used. In the case of a sequence that

keeps the Clock input signal at logic high, an inverter circuit must

be added. In a case where the Clock signal is set at an undetermined level, an edge detection circuit (figure 25) can be used to

prepare the signal for the Clock input, allowing correct processing by the circuit shown in figure 24.

Output Disable (Sleep1 and Sleep2) Circuits

There are two methods to set this IC at motor free-state (coast,

with outputs disabled). One is to set the Ref/Sleep1 pin to more

than 2 V (Sleep1), and the other (Sleep2) is to set the excitation

signals (pins M1, M2, and M3). In either way, the IC will change

to Sleep mode, stopping the main power supply at the same time,

and decreasing circuit current. The difference between the two

methods is that, in the first way, the internal sequencer remains

in an enabled state, and in the latter method, the IC enters the

VCC

Clock

74HC14

74HC14

R

Sync

C

Figure 24. Clock signal shutoff detection circuit

Step

Clock

Clock

Figure 25. Clock signal edge detection circuit

SANKEN ELECTRIC CO., LTD.

31

�Hold state. Moreover, in the method using the excitation signals

(Sleep2), excitation timing remains in a standby state, even if a

signal is input on the Clock pin during Sleep mode.

When awaking to normal operating mode (motor rotation) from

Disable (Sleep1 or Sleep2) mode, set an appropriate delay time

from cancellation of the Disable mode to the initial Clock input

edge. In doing so, consider not only the rise time for the IC,

but also the rise time for the motor excitation current, which is

important (see figure 26).

Ref/Sleep1 Pin

The Ref/Sleep1 pin provides access to the following functions:

• Standard voltage setting for output current level setting

• Output Enable-Disable control input

These functions are further described in the Truth Table section,

and in the discussion of output disabling, above.

where

P is the power dissipation in the IC,

IOUT is the operating output current,

RDS(on) is the resistance of the output MOSFET, and

RS is the current sense resistance.

Based on the PD calculated using the above formula, the

expected increase in operating junction temperature, ΔTJ , of the

IC can be estimated using figure 28. This result must be added

to the worst case ambient temperature when operating, TA(max).

Based on the calculation, there is no problem unless TA(max) plus

ΔTJ exceeds 150°C.

Ref/Sleep1 or

M1, M2, and M3

100 µs

(minimum)

Range A. In this range, control current value also varies in

accordance with VREF. Therefore, losses in the IC and the sense

resistors must be given extra consideration.

Clock

t

Range B. In this range, the voltage that switches output enable

Logic Input Pins

If a logic input pin (Clock, Reset, CW/CCW, M1, M2, M3, or

Sync) is not used (fixed logic level), the pin must be tied to VDD

or Gnd. Please do not leave them floating, because there is possibility of undefined effects on IC performance when they are

left open.

Output Pins (MO and Flag). The MO and Flag output pins are

designed as monitor outputs, and inside of the IC is an output

inverter (see figure 27). Therefore, let these pins float if they are

not used.

Thermal Design Information

It is not practical to calculate the power dissipation of the

SLA7070MPRT series accurately, because that would require

factors that are variable during operation, such as time periods

and excitation modes during motor rotation, input frequencies

and sequences, and so forth. Given this situation, it is preferable

to perform an approximate calculation at worst conditions. The

following is a simplified formula for calculation of power dissipation:

I2

PD = OUT

(RDS(on)+ RS) 2

(8)

Figure 26. Timing delay between Disable mode cancellation and the next

Clock input

VDD

Static electricity

protection circuit

Mo or FLAG

Figure 27. MO pin and Flag pin general internal circuit layout

150

Increase in Junction Temperature

∆TJ (°C)

and disable (Sleep mode) exists. At enable, the same cautions

apply as in range A. In addition, for some cases, there are possibilities that the output status will become unstable as a result of

iteration between enable and disable.

125

100

∆TJ-A = 26.6 x PD

75

∆TC-A = 21.3 x PD

50

25

0

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

Maximum Allowable Power Dissipation, PD(max) (W)

Figure 28. Temperature increase

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

32

�CAUTION

When the IC is used with a heatsink attached, device package

thermal resistance, RθJA , is a variable used in calculating ΔTj-a.

The value of RθFIN is calculated from the following formula:

RθJA≈RθJC+RθFin=RθJA–RθCA+RθFin

(9)

where Rθj-a is the thermal resistance of the heatsink. ΔTj-a can be

calculated with using the value of RθJA.

The following procedure should be used to measure product temperature and to estimate junction temperature in actual operation:

First, measure the temperature rise at pin 12 of the device (ΔTc-a).

Second, estimate the loss (P) and junction temperature (Tj) from

the temperature rise with reference to figure 28, temperature

increase graph. At this point, the device temperature rise )(ΔTc-a)

and the junction temperature rise (Tj) are almost equivalent under

the following formula:

∆TJ ˜ ∆Tc-a+PD

Rθj-c

(10)

The SLA7070MPRT series is designed as a multichip, with

separate power elements (MOSFET), control IC (MIC), and

sense resistance. Consequently, because the control IC cannot

accurately detect the temperature of the power elements (which

are the primary sources of heat), the ICs do not provide a protection function against overheating. For thermal protection, users

must conduct sufficient thermal evaluations to be able to ensure

that the junction temperature does not exceed the warranty level

(150°C).

This thermal design information is provided for preliminary

design estimations only. The thermal performance of the IC will

be significantly determined by the conditions of the application,

in particular the state of the mounting PCB, heatsink, and the

ambient air. Before operating the IC in an application, the user

must experimentally determine the actual thermal performance.

The maximum recommended case temperatures (at the center, pin

12) for the IC are:

• With no external heatsink connection: 90°C

• With external heatsink connection: 80°

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

33

�Characteristic Data

Output MOSFET On-Voltage, VDS(on)

SLA7070MPRT/SLA7075MPRT

SLA7071MPRT/SLA7076MPRT

1.4

1.4

Io=1.5A

Io=1A

1.2

1.2

1.0

0.8

Io=0.5A

0.6

V DS(on) (V)

V DS(on) (V)

1.0

0.8

0.4

0.4

0.2

0.2

0.0

-25

0

25

50

75

Io=1A

0.6

0.0

100 125

-25

Product Temperature, TC (°C)

0

25

50

75

100 125

Product Temperature, TC (°C)

SLA7073MPRT/SLA7078MPRT

SLA7072MPRT/SLA7077MPRT

1.4

1.2

Io=2A

Io=3A

1.2

1.0

1.0

0.6

Io=1A

0.4

V DS(on) (V)

V DS(on) (V)

0.8

Io=2A

0.8

0.6

Io=1A

0.4

0.2

0.2

0.0

0.0

-25

0

25

50

75

100 125

Product Temperature, TC (°C)

SLA7070MPRT-AN, Rev. 2.1

-25

0

25

50

75

100 125

Product

Temperature,

(°C)

(°C)

Product

Temperature,

TCTC

SANKEN ELECTRIC CO., LTD.

34

�Output MOSFET Body Diode Forward Voltage, Vf

SLA7071MPRT/SLA7076MPRT

1.1

1.1

1.0

1.0

0.9

0.9

V f (V)

V f (V)

SLA7070MPRT/SLA7075MPRT

0.8

Io=1A

0.8

0.7

Io=0.5A

0.7

Io=1.5A

Io=1A

0.6

-25

0

25

50

0.6

75 100 125

-25

Product Temperature, TC (°C)

1.0

1.0

0.9

0.9

Io=1A

0.6

-25

0

25

50

75 100 125

Product Temperature, TC (°C)

SLA7070MPRT-AN, Rev. 2.1

V f (V)

V f (V)

1.1

0.7

50

75 100 125

SLA7073MPRT/SLA7078MP RT

1.1

0.8

25

Product Temperature, TC (°C)

SLA7072MPRT/SLA7077MP RT

Io=2A

0

Io=3A

Io=2A

0.8

Io=1A

0.7

0.6

-25

0

25

50

75

100 125

Product Temperature, TC (°C)

SANKEN ELECTRIC CO., LTD.

35

�• The contents in this document are subject to changes, for improvement and other purposes, without notice. Make sure that this is the

latest revision of the document before use.

• Application and operation examples described in this document are quoted for the sole purpose of reference for the use of the products herein and Sanken can assume no responsibility for any infringement of industrial property rights, intellectual property rights or

any other rights of Sanken or any third party which may result from its use.

• Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures

including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device

failure or malfunction.

• Sanken products listed in this document are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.).

When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and

its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), and whenever

long life expectancy is required even in general purpose electronic equipment or apparatus, please contact your nearest Sanken sales

representative to discuss, prior to the use of the products herein.

The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required

(aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

• In the case that you use Sanken products or design your products by using Sanken products, the reliability largely depends on the

degree of derating to be made to the rated values. Derating may be interpreted as a case that an operation range is set by derating the

load from each rated value or surge voltage or noise is considered for derating in order to assure or improve the reliability. In general,

derating factors include electric stresses such as electric voltage, electric current, electric power etc., environmental stresses such

as ambient temperature, humidity etc. and thermal stress caused due to self-heating of semiconductor products. For these stresses,

instantaneous values, maximum values and minimum values must be taken into consideration.

In addition, it should be noted that since power devices or IC's including power devices have large self-heating value, the degree of

derating of junction temperature affects the reliability significantly.

• When using the products specified herein by either (i) combining other products or materials therewith or (ii) physically, chemically

or otherwise processing or treating the products, please duly consider all possible risks that may result from all such uses in advance

and proceed therewith at your own responsibility.

• Anti radioactive ray design is not considered for the products listed herein.

• Sanken assumes no responsibility for any troubles, such as dropping products caused during transportation out of Sanken's distribution network.

• The contents in this document must not be transcribed or copied without Sanken's written consent.

SLA7070MPRT-AN, Rev. 2.1

SANKEN ELECTRIC CO., LTD.

36

�