Si 5 54

REVISION D

Q UAD F R E Q U E N C Y V O LTAG E - C O N T R O L L E D

C RY STA L O S C I L L ATO R ( V C X O ) 1 0 M H Z TO 1 . 4 G H Z

Features

Available with any-rate output

frequencies from 10–945 MHz and

selected frequencies to 1.4 GHz

Four selectable output frequencies

3rd generation DSPLL® with superior

jitter performance

3x better frequency stability than

SAW-based oscillators

Internal fixed crystal frequency

ensures high reliability and low

aging

Available CMOS, LVPECL,

LVDS, and CML outputs

3.3, 2.5, and 1.8 V supply options

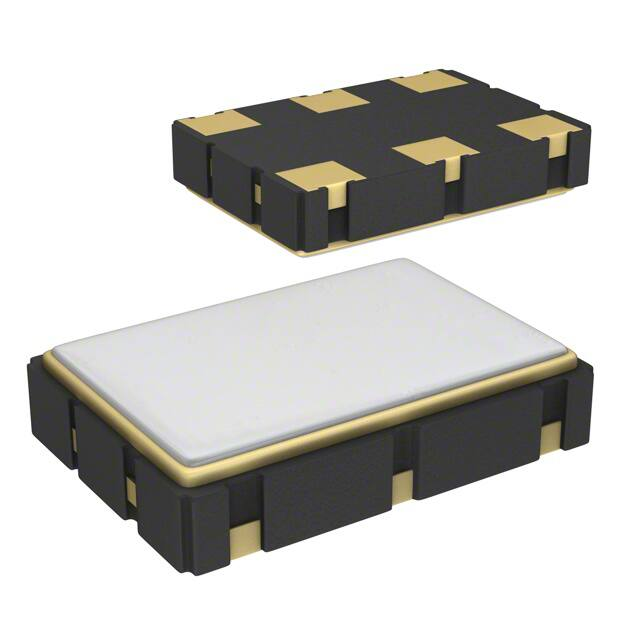

Industry-standard 5 x 7 mm

package and pinout

Pb-free/RoHS-compliant

Applications

Si5602

Ordering Information:

SONET/SDH

xDSL

10 GbE LAN / WAN

Low jitter clock generation

Optical modules

Clock and data recovery

See page 10.

Description

The Si554 quad-frequency VCXO utilizes Skyworks Solutions’ advanced

DSPLL® circuitry to provide a very low jitter clock for all output frequencies.

The Si554 is available with any-rate output frequency from 10 to 945 MHz

and selected frequencies to 1400 MHz. Unlike traditional VCXOs, where a

different crystal is required for each output frequency, the Si554 uses one

fixed crystal frequency to provide a wide range of output frequencies. This

IC-based approach allows the crystal resonator to provide exceptional

frequency stability and reliability. In addition, DSPLL clock synthesis

provides superior supply noise rejection, simplifying the task of generating

low jitter clocks in noisy environments typically found in communication

systems. The Si554 IC-based VCXO is factory-configurable for a wide

variety of user specifications including frequency, supply voltage, output

format, tuning slope, and temperature stability. Specific configurations are

factory-programmed at time of shipment, thereby eliminating the long lead

times associated with custom oscillators.

Pin Assignments:

See page 9.

(Top View)

FS[1]

7

VC

1

6

VDD

OE

2

5

CLK–

GND

3

4

CLK+

8

FS[0]

Functional Block Diagram

VDD

FS1

CLK- CLK+

Fixed

Frequency XO

Any-rate

10–1400 MHz

DSPLL®

Clock Synthesis

FS0

ADC

Vc

OE

GND

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

Rev. 1.2 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 27, 2021

�Si5 54

1. Electrical Specifications

Table 1. Recommended Operating Conditions

Parameter

Symbol

Supply Voltage1

VDD

Supply Current

IDD

Output Enable (OE)

and Frequency Select FS[1:0]2

Operating Temperature Range

Test Condition

Min

Typ

Max

Units

3.3 V option

2.97

3.3

3.63

V

2.5 V option

2.25

2.5

2.75

V

1.8 V option

1.71

1.8

1.89

V

Output enabled

LVPECL

CML

LVDS

CMOS

—

—

—

—

120

108

99

90

130

117

108

98

Tristate mode

—

60

75

mA

VIH

0.75 x VDD

—

—

V

VIL

—

—

0.5

V

–40

—

85

ºC

TA

mA

Notes:

1. Selectable parameter specified by part number. See Section 3. "Ordering Information" on page 10 for further details.

2. OE and FS[1:0] pins include a 17 k resistor to VDD.

Table 2. VC Control Voltage Input

Parameter

Symbol

1,2,3

Control Voltage Tuning Slope

Test Condition

Min

Typ

Max

Units

10 to 90% of VDD

—

33

45

90

135

180

356

—

ppm/V

BSL

–5

±1

+5

%

Incremental

–10

±5

+10

%

KV

Control Voltage Linearity4

LVC

Modulation Bandwidth

BW

9.3

10.0

10.7

kHz

VC Input Impedance

ZVC

500

—

—

k

—

VDD/2

—

V

VDD

V

Nominal Control Voltage

Control Voltage Tuning Range

VCNOM

VC

@ fO

0

Notes:

1. Positive slope; selectable option by part number. See Section 3. "Ordering Information" on page 10.

2. For best jitter and phase noise performance, always choose the smallest KV that meets the application’s minimum APR

requirements. See “AN266: VCXO Tuning Slope (KV), Stability, and Absolute Pull Range (APR)” for more information.

3. KV variation is ±10% of typical values.

4. BSL determined from deviation from best straight line fit with VC ranging from 10 to 90% of VDD. Incremental slope

determined with VC ranging from 10 to 90% of VDD.

2

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

Rev. 1.2 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 27, 2021

�Si554

Table 3. CLK± Output Frequency Characteristics

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

fO

LVDS/CML/LVPECL

10

—

945

MHz

CMOS

10

—

160

MHz

TA = –40 to +85 °C

–20

–50

–100

—

—

—

+20

+50

+100

ppm

±12

—

±375

ppm

Frequency drift over first year.

—

—

±3

Frequency drift over 15 year life.

—

—

±10

—

—

10

ms

—

—

20

ms

Nominal Frequency1,2,3

1,4

Temperature Stability

Absolute Pull Range1,4

APR

Aging

Power up Time5

tOSC

Settling Time After FS[1:0]

Change

tFRQ

Both FS[1] and FS[0] changing

simultaneously

ppm

Notes:

1. See Section 3. "Ordering Information" on page 10 for further details.

2. Specified at time of order by part number. Also available in frequencies from 970 to 1134 MHz and 1213 to 1417 MHz.

3. Nominal output frequency set by VCNOM = VDD/2.

4. Selectable parameter specified by part number.

5. Time from power up or tristate mode to fO (to within ±1 ppm of fO).

Table 4. CLK± Output Levels and Symmetry

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

VO

mid-level

VDD – 1.42

—

VDD – 1.25

V

VOD

swing (diff)

1.1

—

1.9

VPP

VSE

swing (single-ended)

0.55

—

0.95

VPP

VO

mid-level

1.125

1.20

1.275

V

VOD

swing (diff)

0.5

0.7

0.9

VPP

2.5/3.3 V option mid-level

—

VDD – 1.30

—

V

1.8 V option mid-level

—

VDD – 0.36

—

V

2.5/3.3 V option swing (diff)

1.10

1.50

1.90

VPP

1.8 V option swing (diff)

0.35

0.425

0.50

VPP

VOH

IOH = 32 mA

0.8 x VDD

—

VDD

VOL

IOL = 32 mA

—

—

0.4

Rise/Fall time (20/80%)

tR, tF

LVPECL/LVDS/CML

—

—

350

ps

CMOS with CL = 15 pF

—

1

—

ns

Symmetry (duty cycle)

SYM

45

—

55

%

LVPECL Output Option

LVDS Output Option

1

2

CML Output Option2

VO

VOD

CMOS Output

Option3

LVPECL:

(diff)

LVDS:

CMOS:

V

VDD – 1.3 V

1.25 V (diff)

VDD/2

Notes:

1. 50 to VDD – 2.0 V.

2. Rterm = 100 (differential).

3. CL = 15 pF

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

3

Rev. 1.2 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 27, 2021

�Si5 54

Table 5. CLK± Output Phase Jitter

Parameter

1,2,3

Phase Jitter (RMS)

for FOUT > 500 MHz

Symbol

Test Condition

Min

Typ

Max

Units

J

Kv = 33 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.26

0.26

—

—

ps

Kv = 45 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.27

0.26

—

—

ps

Kv = 90 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.32

0.26

—

—

ps

Kv = 135 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.40

0.27

—

—

ps

Kv = 180 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.49

0.28

—

—

ps

Kv = 356 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

—

0.87

0.33

—

—

ps

Notes:

1. Refer to AN255, AN256, and AN266 for further information.

2. For best jitter and phase noise performance, always choose the smallest KV that meets the application’s minimum APR

requirements. See “AN266: VCXO Tuning Slope (KV), Stability, and Absolute Pull Range (APR)” for more information.

3. See “AN255: Replacing 622 MHz VCSO devices with the Si550 VCXO” for comparison highlighting power supply

rejection (PSR) advantage of Si55x versus SAW-based solutions.

4. Max jitter for LVPECL output with VC=1.65V, VDD=3.3V, 155.52 MHz.

5. Max offset frequencies: 80 MHz for FOUT > 250 MHz, 20 MHz for 50 MHz < FOUT

很抱歉,暂时无法提供与“510CBA000186AAGR”相匹配的价格&库存,您可以联系我们找货

免费人工找货