Si4063/60-C

H I G H - P ERFORMANCE , L O W -C U R R E N T T RANSMITTER

Features

Smart metering

Remote control

Home security and alarm

Telemetry

Garage and gate openers

Remote keyless entry

Home automation

Industrial control

Sensor networks

Health monitors

Electronic shelf labels

1

20

19

18

17

16

NC 2

15 nSEL

NC 3

14 SDI

GND

PAD

TX 4

13 SDO

NC 5

Description

Silicon Laboratories' Si406x devices are high-performance, low-current

transmitters covering the sub-GHz frequency bands from 142 to

1050 MHz. The radios are part of the EZRadioPRO® family, which

includes a complete line of transmitters, receivers, and transceivers

covering a wide range of applications. All parts offer extremely low active

and standby current consumption. The Si406x includes optimal phase

noise performance for narrow band applications, such as FCC Part90 and

169 MHz wireless Mbus. The Si4063 offers exceptional output power of

up to +20 dBm with outstanding TX efficiency. The high output power

allows extended ranges and highly robust communication links. The

Si4060 active mode TX current consumption of 18 mA at +10 dBm

coupled with extremely low standby current and fast wake times ensure

extended battery life in the most demanding applications. The Si4063 can

achieve up to +27 dBm output power with built-in ramping control of a

low-cost external FET. The devices can meet worldwide regulatory

standards: FCC, ETSI, wireless MBus, and ARIB. All devices are

designed to be compliant with 802.15.4g and WMbus smart metering

standards. The devices are highly flexible and can be configured via the

Wireless Development Suite (WDS) available at Silicon Labs web site.

Rev 1.0 10/14

SDN

XOUT

XIN

GND

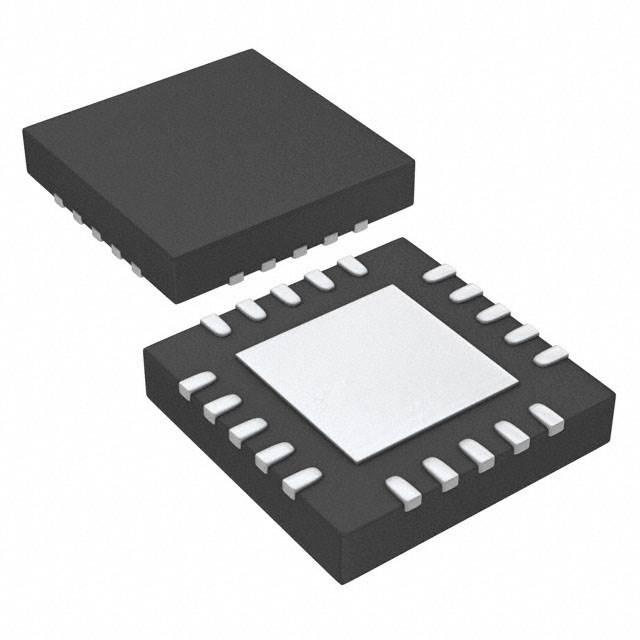

Pin Assignments

Applications

Copyright © 2014 by Silicon Laboratories

12 SCLK

6

7

8

9

10

GPIO1

GPIO0

GPIO2

VDD

Power supply = 1.8 to 3.8 V

Highly configurable packet handler

TX 129 byte FIFO

Low BOM

Low battery detector

Temperature sensor

20-Pin QFN package

IEEE 802.15.4g compliant

Suitable for FCC Part 90 Mask D, FCC

part 15.247, 15,231, 15,249, ARIB T-108,

T-96, T-67, China regulatory ETSI EN

300 220

GPIO3

Frequency range = 142–1050 MHz

Modulation

(G)FSK, 4(G)FSK, (G)MSK

OOK

Max output power

+20 dBm (Si4063)

+13 dBm (Si4060)

PA support for +27 or +30 dBm

Ultra low current powerdown modes

30 nA shutdown, 40 nA standby

Data rate = 100 bps to 1 Mbps

Fast wake times

TXRamp

VDD

11 nIRQ

Patents pending

Si4063/60-C

�Si4063/60-C

Functional Block Diagram

GPIO3 GPIO2

XIN XOUT

Loop

Filter

PFD / CP

VCO

FBDIV

TX DIV

30 MHz XO

Frac-N Div

LO

Gen

Bootup

OSC

SDN

PA

PowerRamp

Cntl

SPI Interface

Controller

TX

ADC

Temp

sensor

MODEM

FIFO

Packet

Handler

LDOs

PA

LDO

LBD

32K LP

OSC

TXRAMP

2

Digital

Logic

POR

VDD

GPIO0 GPIO1

Product

Freq. Range

Max Output

Power

TX Current

Narrowband

Operation

Si4063

Major bands

142–1050 MHz

+20 dBm

169 MHz:

68.5 mA

Si4060

Major bands

142–1050 MHz

+13 dBm

+10 dBm: 18 mA

+13 dBm: 24 mA

Rev 1.0

nSEL

SDI

SDO

SCLK

nIRQ

�Si4063/60-C

TABLE O F C ONTENTS

Section

Page

1. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3. Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1. Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2. Fast Response Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

3.3. Operating Modes and Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.4. Application Programming Interface (API) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.5. Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6. GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4. Modulation and Hardware Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1. Modulation Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2. Hardware Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5. Internal Functional Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.1. Synthesizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

5.2. Transmitter (TX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

5.3. Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

6. Data Handling and Packet Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

6.1. TX FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.2. Packet Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7. Auxiliary Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.1. Wake-up Timer and 32 kHz Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.2. Low Duty Cycle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.3. Temperature, Battery Voltage, and Auxiliary ADC . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.4. Low Battery Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

8. Pin Descriptions: Si4063/60 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

9. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

10. Package Outline: Si4063/60 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

11. PCB Land Pattern: Si4063/60 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

12. Top Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

12.1. Si4063/60 Top Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

12.2. Top Marking Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Rev 1.0

3

�Si4063/60-C

1. Electrical Specifications

Table 1. DC Characteristics1

Parameter

Min

Typ

Max

Unit

1.8

3.3

3.8

V

RC Oscillator, Main Digital Regulator,

and Low Power Digital Regulator OFF

—

30

—

nA

IStandby

Register values maintained and RC

oscillator/WUT OFF

—

40

—

nA

ISleepRC

RC Oscillator/WUT ON and all register values maintained, and all other blocks OFF

—

740

—

nA

ISleepXO

Sleep current using an external 32 kHz crystal.

—

1.7

—

µA

ISensor

Low battery detector ON, register values maintained,

and all other blocks OFF

—

1

—

µA

IReady

Crystal Oscillator and Main Digital Regulator ON,

all other blocks OFF

—

1.8

—

mA

TUNE Mode Current

ITune_TX

TX Tune, High Performance Mode

—

7.8

—

mA

TX Mode Current

(Si4063)

ITX_+20

+20 dBm output power, class-E match, 915 MHz,

3.3 V

—

88

—

mA

+20 dBm output power, square-wave match,

169 MHz, 3.3 V

—

68.5

—

mA

ITX_+10

+10 dBm output power, Class-E match, 169 MHz,

3.3 V2

—

18

—

mA

ITX_+13

+13 dBm output power, Class-E match,

915/868 MHz, 3.3 V2

—

24

—

mA

Supply Voltage

Range

Symbol

VDD

Power Saving Modes IShutdown

-LBD

TX Mode Current

(Si4060)

Test Condition

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and

from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. Measured on direct tie RF evaluation board.

4

Rev 1.0

�Si4063/60-C

Table 2. Synthesizer AC Electrical Characteristics1

Parameter

Synthesizer Frequency

Range (Si4063/60)

Synthesizer Frequency

Resolution2

Symbol

Test Condition

FSYN

FRES-960

850–1050 MHz

FRES-525

420–525 MHz

FRES-420

350–420 MHz

FRES-350

284–350 MHz

FRES-175

142–175 MHz

Min

Typ

Max

Unit

850

—

1050

MHz

350

—

525

MHz

284

—

350

MHz

142

—

175

MHz

—

28.6

—

Hz

—

14.3

—

Hz

—

11.4

—

Hz

—

9.5

—

Hz

—

4.7

—

Hz

Synthesizer Settling Time

tLOCK

Measured from exiting Ready mode with

XOSC running to any frequency.

Including VCO Calibration.

—

50

—

µs

Phase Noise

L(fM)

F = 10 kHz, 169 MHz, High Perf Mode

—

–117

—

dBc/Hz

F = 100 kHz, 169 MHz, High Perf Mode

—

–120

—

dBc/Hz

F = 1 MHz, 169 MHz, High Perf Mode

—

–138

—

dBc/Hz

F = 10 MHz, 169 MHz, High Perf Mode

—

–148

—

dBc/Hz

F = 10 kHz, 915 MHz, High Perf Mode

—

–102

—

dBc/Hz

F = 100 kHz, 915 MHz, High Perf Mode

—

–105

—

dBc/Hz

F = 1 MHz, 915 MHz, High Perf Mode

—

–125

—

dBc/Hz

F = 10 MHz, 915 MHz, High Perf Mode

—

–138

—

dBc/Hz

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage

and from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise

stated.

2. Default API setting for modulation deviation resolution is double the typical value specified.

Rev 1.0

5

�Si4063/60-C

Table 3. Transmitter AC Electrical Characteristics1

Parameter

Symbol

Test Condition

TX Frequency Range

Min

Typ

Max

Unit

850

—

1050

MHz

350

—

525

MHz

284

—

350

MHz

142

—

175

MHz

FTX

(G)FSK Data Rate2

DRFSK

0.1

—

500

kbps

4(G)FSK Data Rate2

DR4FSK

0.2

—

1000

kbps

OOK Data Rate2

DROOK

0.1

—

120

kbps

Modulation Deviation

Range

Modulation Deviation

Resolution3

Output Power Range

(Si4063)4

f960

850–1050 MHz

—

1.5

—

MHz

f525

420–525 MHz

—

750

—

kHz

f420

350–420 MHz

—

600

—

kHz

f350

284–350 MHz

—

500

—

kHz

f175

142–175 MHz

—

250

—

kHz

FRES-960

850–1050 MHz

—

28.6

—

Hz

FRES-525

420–525 MHz

—

14.3

—

Hz

FRES-420

350–420 MHz

—

11.4

—

Hz

FRES-350

284–350 MHz

—

9.5

—

Hz

FRES-175

142–175 MHz

—

4.7

—

Hz

PTX63

Typical range at 3.3 V with Class E

match optimized for best PA efficiency

–20

—

+20

dBm

PTX60

Typical range at 3.3 V with Class E

match optimized for best PA efficiency.

Efficiency can be traded off for higher

Tx output power up to +13 dBm.

–20

—

+12.5

dBm

PRF_OUT

Using switched current match within

6 dB of max power

—

0.25

—

dB

At 20 dBm PA power setting, 915 MHz,

Class E match, 3.3 V, 25 °C

19

20

21

dBm

Output Power Range

(Si4060)4

TX RF Output Steps

Output Power Variation

(Si4063)

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and

from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. The maximum data rate is dependent on the XTAL frequency and is calculated as per the formula:

Maximum Symbol Rate = Fxtal/60, where Fxtal is the XTAL frequency (typically 30 MHz).

3. Default API setting for modulation deviation resolution is double the typical value specified.

4. Output power is dependent on matching components and board layout.

6

Rev 1.0

�Si4063/60-C

Table 3. Transmitter AC Electrical Characteristics1 (Continued)

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

Output Power Variation

(Si4060)

At 10 dBm PA power setting, 915 MHz,

Class E match, 3.3 V, 25 °C

9.5

10

10.5

dBm

Output Power Variation

(Si4063)

At 20 dBm PA power setting, 169 MHz,

Square Wave match, 3.3 V, 25 °C

18.5

20

21

dBm

Output Power Variation

(Si4060)

At 10 dBm PA power setting, 169 MHz,

Square Wave match, 3.3 V, 25 °C

—

10

—

dBm

TX RF Output Level

Variation vs. Temperature

PRF_TEMP

–40 to +85 C

—

2.3

—

dB

TX RF Output Level

Variation vs. Frequency

PRF_FREQ

Measured across 902–928 MHz

—

0.6

—

dB

B*T

Gaussian Filtering Bandwith Time

Product

—

0.5

—

Transmit Modulation

Filtering

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and

from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. The maximum data rate is dependent on the XTAL frequency and is calculated as per the formula:

Maximum Symbol Rate = Fxtal/60, where Fxtal is the XTAL frequency (typically 30 MHz).

3. Default API setting for modulation deviation resolution is double the typical value specified.

4. Output power is dependent on matching components and board layout.

Rev 1.0

7

�Si4063/60-C

Table 4. Auxiliary Block Specifications1

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

Temperature Sensor

Sensitivity

TSS

—

4.5

—

ADC

Codes/

°C

Low Battery Detector

Resolution

LBDRES

—

50

—

mV

Microcontroller Clock

Output Frequency Range2

Temperature Sensor

Conversion

XTAL Range3

30 MHz XTAL Start-Up Time

30 MHz XTAL Cap

Resolution

32 kHz XTAL Start-Up Time

32 kHz Accuracy using

Internal RC Oscillator

POR Reset Time

FMC

Configurable to Fxtal or Fxtal

divided by 2, 3, 7.5, 10, 15, or

30 where Fxtal is the reference

XTAL frequency. In addition,

32.768 kHz is also supported.

32.768K

—

Fxtal

Hz

TEMPCT

Programmable setting

—

3

—

ms

25

—

32

MHz

—

300

—

µs

30MRES

—

70

—

fF

t32k

—

2

—

sec

32KRCRES

—

2500

—

ppm

tPOR

—

—

6

ms

XTALRange

t30M

Using XTAL and board layout in

reference design. Start-up time

will vary with XTAL type and

board layout.

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage

and from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise

stated.

2. Microcontroller clock frequency tested in production at 1 MHz, 30 MHz, 32 MHz, and 32.768 kHz. Other frequencies

tested in bench characterization.

3. XTAL Range tested in production using an external clock source (similar to using a TCXO).

8

Rev 1.0

�Si4063/60-C

Table 5. Digital IO Specifications (GPIO_x, SCLK, SDO, SDI, nSEL, nIRQ, SDN)1

Parameter

Rise Time

2,3

Fall Time3,4

Symbol

Test Condition

Min

Typ

Max

Unit

TRISE

0.1 x VDD to 0.9 x VDD,

CL = 10 pF,

DRV = LL

—

2.3

—

ns

TFALL

0.9 x VDD to 0.1 x VDD,

CL = 10 pF,

DRV = LL

—

2

—

ns

Input Capacitance

CIN

—

2

—

pF

Logic High Level Input Voltage

VIH

VDD x 0.7

—

—

V

Logic Low Level Input Voltage

VIL

—

—

VDD x 0.3

V

Input Current

IIN

0 3.3 V. When Vdd < 3.3 V, the Vhi will be closely following the Vdd, and ramping time will be

smaller also.

Vlo = 0 V when NO current needed to be sunk into TXRAMP pin. If 10 µA need to be sunk into the chip, Vlo will be

10 µA x 10k = 100 mV.

22

Rev 1.0

�Si4063/60-C

Number

Command

Summary

0x2200

PA_MODE

0x2201

PA_PWR_LVL

0x2202

PA_BIAS_CLKDUTY

Adjust TX power in coarse steps and optimizes for different match configurations.

0x2203

PA_TC

Changes the ramp up/down time of the PA.

Sets PA type.

Adjust TX power in fine steps.

5.2.1. Si4063: +20 dBm PA

The +20 dBm configuration utilizes a class-E matching configuration. Typical performance for the 900 MHz band

for output power steps, voltage, and temperature are shown in Figures 8–10. The output power is changed in 128

steps through PA_PWR_LVL API. For detailed matching values, BOM, and performance at other frequencies, refer

to the PA Matching application note.

TX�Power�vs.�PA_PWR_LVL

25

20

15

10

5

Ͳ5

Ͳ10

Ͳ15

Ͳ20

Ͳ25

Ͳ30

Ͳ35

Ͳ40

0

20

40

60

80

100

120

PA_PWR_LVL

Figure 8. +20 dBm TX Power vs. PA_PWR_LVL

TX Power vs. VDD

22

TX Power (dBm)

TX�Power(dBm)

0

20

18

16

14

12

10

1.8

2

2.2

2.4

2.6

2.8

3

3.2

3.4

3.6

Supply Voltage (VDD)

Figure 9. +20 dBm TX Power vs. VDD

Rev 1.0

23

�Si4063/60-C

TX Power vs Temp

TX Power (dBm)

20.5

20

19.5

19

18.5

18

-40 -30 -20 -10

0

10

20

30

40

50

60

Temperature (C)

Figure 10. +20 dBm TX Power vs. Temp

24

Rev 1.0

70

80

�Si4063/60-C

5.3. Crystal Oscillator

The Si406x includes an integrated crystal oscillator with a fast start-up time of less than 250 µs. The design is

differential with the required crystal load capacitance integrated on-chip to minimize the number of external

components. By default, all that is required off-chip is the crystal. The default crystal is 30 MHz, but the circuit is

designed to handle any XTAL from 25 to 32 MHz. If a crystal different than 30 MHz is used, the POWER_UP API

boot command must be modified. The WDS calculator crystal frequency field must also be changed to reflect the

frequency being used. The crystal load capacitance can be digitally programmed to accommodate crystals with

various load capacitance requirements and to adjust the frequency of the crystal oscillator. The tuning of the crystal

load capacitance is programmed through the GLOBAL_XO_TUNE API property. The total internal capacitance is

11 pF and is adjustable in 127 steps (70 fF/step). The crystal frequency adjustment can be used to compensate for

crystal production tolerances. The frequency offset characteristics of the capacitor bank are demonstrated in

Figure 11.

Figure 11. Capacitor Bank Frequency Offset Characteristics

Utilizing the on-chip temperature sensor and suitable control software, the temperature dependency of the crystal

can be canceled.

A TCXO or external signal source can easily be used in place of a conventional XTAL and should be connected to

the XIN pin. The incoming clock signal is recommended to be peak-to-peak swing in the range of 600 mV to 1.4 V

and ac-coupled to the XIN pin. If the peak-to-peak swing of the TCXO exceeds 1.4 V peak-to-peak, then dc

coupling to the XIN pin should be used. The maximum allowed swing on XIN is 1.8 V peak-to-peak.

The XO capacitor bank should be set to 0 whenever an external drive is used on the XIN pin. In addition, the

POWER_UP command should be invoked with the TCXO option whenever external drive is used.

Rev 1.0

25

�Si4063/60-C

6. Data Handling and Packet Handler

6.1. TX FIFOs

By default, a 64 byte FIFO is available in the device. This can be increased to support a 129 byte FIFO via API

configuration. Writing to command Register 66h loads data into the TX FIFO. The TX FIFO has a threshold for

when the FIFO is almost empty, which is set by the “TX_FIFO_EMPTY” property. An interrupt event occurs when

the data in the TX FIFO reaches the almost empty threshold. If more data is not loaded into the FIFO, the chip

automatically exits the TX state after the PACKET_SENT interrupt occurs. The TX FIFO may be cleared or reset

with the “FIFO_RESET” command.

TX FIFO

TX FIFO Almost

Empty Threshold

Figure 12. TX FIFO

6.2. Packet Handler

Config

0, 2, o r 4

Bytes

Con fig

0, 2, o r 4

Bytes

Con fig

0, 2, o r 4

B ytes

C RC Field 5 (op t)

Field 5 (opt)

Data

C RC Field 4 (op t)

Field 4 (opt)

Data

C RC Field 3 (op t)

Field 3 (opt)

Data

Con fig

C RC Field 2 (op t)

1-4 Bytes

F ield 2 (o pt)

Pkt Len gth or Data

Field 1

Header or Data

1-255 Bytes

C RC Field 1 (op t)

Preamble

Sync Word

When using the FIFOs, automatic packet handling may be enabled. The usual fields for network communication,

such as preamble, synchronization word, headers, packet length, and CRC, can be configured to be automatically

added to the data payload. The fields needed for packet generation normally change infrequently and can

therefore be stored in registers. Automatically adding these fields to the data payload in TX mode greatly reduces

the amount of communication between the microcontroller and Si406x. It also greatly reduces the required

computational power of the microcontroller. The general packet structure is shown in Figure 13. Any or all of the

fields can be enabled and checked by the internal packet handler.

Con fig

0, 2, or 4

Bytes

0, 2, or 4

Bytes

Figure 13. Packet Handler Structure

The fields are highly programmable and can be used to check any kind of pattern in a packet structure. The

general functions of the packet handler include the following:

Construction

of Preamble field in TX mode

Construction of Sync field in TX mode

Construction of Data Field from FIFO memory in TX mode

Construction of CRC field (if enabled) in TX mode

Data whitening and/or Manchester encoding (if enabled) in TX mode

26

Rev 1.0

�Si4063/60-C

7. Auxiliary Blocks

7.1. Wake-up Timer and 32 kHz Clock Source

The chip contains an integrated wake-up timer that can be used to periodically wake the chip from sleep mode. The

wake-up timer runs from either the internal 32 kHz RC Oscillator, or from an external 32 kHz XTAL.

The wake-up timer can be configured to run when in sleep mode. If WUT_EN = 1 in the GLOBAL_WUT_CONFIG

property, prior to entering sleep mode, the wake-up timer will count for a time specified defined by the

GLOBAL_WUT_R and GLOBAL_WUT_M properties. At the expiration of this period, an interrupt will be generated

on the nIRQ pin if this interrupt is enabled in the INT_CTL_CHIP_ENABLE property. The microcontroller will then

need to verify the interrupt by reading the chip interrupt status either via GET_INT_STATUS or a fast response

register. The formula for calculating the Wake-Up Period is as follows:

WUT_R

42

WUT = WUT_M ----------------------------- ms

32.768

The RC oscillator frequency will change with temperature; so, a periodic recalibration is required. The RC oscillator

is automatically calibrated during the POWER_UP command and exits from the Shutdown state. To enable the

recalibration feature, CAL_EN must be set in the GLOBAL_WUT_CONFIG property, and the desired calibration

period should be selected via WUT_CAL_PERIOD[2:0] in the same API property. During the calibration, the

32 kHz RC oscillator frequency is compared to the 30 MHz XTAL and then adjusted accordingly. The calibration

needs to start the 30 MHz XTAL, which increases the average current consumption; so, a longer CAL_PERIOD

results in a lower average current consumption. The 32 kHz XTAL accuracy is comprised of both the XTAL

parameters and the internal circuit. The XTAL accuracy can be defined as the XTAL initial error + XTAL aging +

XTAL temperature drift + detuning from the internal oscillator circuit. The error caused by the internal circuit is

typically less than 10 ppm.

7.2. Low Duty Cycle Mode

The low duty cycle (LDC) mode is implemented to automatically wake-up the transmitter to send a packet. It allows

low average current polling operation by the Si406x for which the wake-up timer (WUT) is used. TX LDC operation

must be set via the GLOBAL_WUT_CONFIG property when setting up the WUT. The LDC wake-up period is

determined by the following formula:

WUT_R

42

LDC = WUT_LDC ----------------------------- ms

32.768

where the WUT_LDC parameter can be set by the GLOBAL_WUT_LDC property. The WUT period must be set in

conjunction with the LDC mode duration; for the relevant API properties, see the wake-up timer (WUT) section.

Figure 14. TX LDC Sequences

In TX LDC mode, the transmitter periodically wakes itself up to transmit a packet that is in the data buffer. If a

packet has been transmitted, nIRQ goes low if the option is set in the INT_CTL_ENABLE property. After

transmitting, the transmitter immediately returns to the WUT state and stays there until the next wake-up time

expires.

Rev 1.0

27

�Si4063/60-C

7.3. Temperature, Battery Voltage, and Auxiliary ADC

The Si406x family contains an integrated auxiliary ADC for measuring internal battery voltage, an internal

temperature sensor, or an external component over a GPIO. The ADC utilizes a SAR architecture and achieves

11-bit resolution. The Effective Number of Bits (ENOB) is 9 bits. When measuring external components, the input

voltage range is 1 V, and the conversion rate is between 300 Hz to 2.44 kHz. The ADC value is read by first

sending the GET_ADC_READING command and enabling the inputs that are desired to be read: GPIO, battery, or

temp. The temperature sensor accuracy at 25 °C is typically ±2 °C.

7.4. Low Battery Detector

The low battery detector (LBD) is enabled and utilized as part of the wake-up-timer (WUT). The LBD function is not

available unless the WUT is enabled, but the host MCU can manually check the battery voltage anytime with the

auxiliary ADC. The LBD function is enabled in the GLOBAL_WUT_CONFIG API property. The battery voltage will

be compared against the threshold each time the WUT expires. The threshold for the LBD function is set in

GLOBAL_LOW_BATT_THRESH. The threshold steps are in increments of 50 mV, ranging from a minimum of

1.5 V up to 3.05 V. The accuracy of the LBD is ±3%. The LBD notification can be configured as an interrupt on the

nIRQ pin or enabled as a direct function on one of the GPIOs.

28

Rev 1.0

�Si4063/60-C

SDN

1

XOUT

XIN

GND

GPIO2

GPIO3

8. Pin Descriptions: Si4063/60

20 19 18 17 16

NC 2

15 nSEL

NC 3

14 SDI

GND

PAD

TX 4

13 SDO

Pin

Pin Name

7

8

9

VDD

GPIO0

10 11 nIRQ

GPIO1

6

TXRamp

12 SCLK

VDD

NC 5

I/0

Description

I

Shutdown Input Pin.

0–VDD V digital input. SDN should be = 0 in all modes except Shutdown mode.

When SDN = 1, the chip will be completely shut down, and the contents of the

registers will be lost. Can be used to reset the chip

1

SDN

2

NC

Leave pin floating.

3

NC

Leave pin floating.

Transmit Output Pin.

4

TX

O

5

NC

6

VDD

VDD

7

TXRAMP

O

8

VDD

VDD

9

GPIO0

I/O

General Purpose Digital I/O.

10

GPIO1

I/O

May be configured through the registers to perform various functions including:

Microcontroller Clock Output, FIFO status, POR, Wake-Up timer, Low Battery

Detect, etc.

The PA output is an open-drain connection, so the L-C match must supply

VDD (+3.3 VDC nominal) to this pin.

It is recommended to connect this pin to GND per the reference design schematic. Not connected internally to any circuitry.

+1.8 to +3.8 V Supply Voltage Input to Internal Regulators.

The recommended VDD supply voltage is +3.3 V.

Programmable Bias Output with Ramp Capability for External FET PA.

See "5.2. Transmitter (TX)" on page 22.

+1.8 to +3.8 V Supply Voltage Input to Internal Regulators.

The recommended VDD supply voltage is +3.3 V.

General Microcontroller Interrupt Status Output.

11

nIRQ

O

When the Si406x exhibits any one of the interrupt events, the nIRQ pin will be

set low = 0. The Microcontroller can then determine the state of the interrupt

by reading the interrupt status. No external resistor pull-up is required, but it

may be desirable if multiple interrupt lines are connected.

Rev 1.0

29

�Si4063/60-C

Pin

Pin Name

I/0

Description

Serial Clock Input.

12

SCLK

I

13

SDO

O

0–VDD V digital input. This pin provides the serial data clock function for the

4-line serial data bus. Data is clocked into the Si406x on positive edge transitions.

0–VDD V Digital Output.

Provides a serial readback function of the internal control registers.

Serial Data Input.

14

SDI

I

0–VDD V digital input. This pin provides the serial data stream for the 4-line

serial data bus.

Serial Interface Select Input.

15

nSEL

I

0–VDD V digital input. This pin provides the Select/Enable function for the

4-line serial data bus.

Crystal Oscillator Output.

16

XOUT

O

17

XIN

I

Crystal Oscillator Input.

Connect to an external 25 to 32 MHz crystal, or connect to an external source.

When using an XTAL, leave floating per the reference design schematic. When

using a TCXO, connect to TCXO GND, which should be separate from the

board’s reference ground plane.

18

GND

GND

19

GPIO2

I/O

General Purpose Digital I/O.

20

GPIO3

I/O

May be configured through the registers to perform various functions, including

Microcontroller Clock Output, FIFO status, POR, Wake-Up timer, Low Battery

Detect.

GND

The exposed metal paddle on the bottom of the Si406x supplies the RF and circuit ground(s) for the entire chip. It is very important that a good solder connection is made between this exposed metal paddle and the ground plane of the

PCB underlying the Si406x.

PKG

30

Connect to an external 25 to 32 MHz crystal, or leave floating when driving

with an external source on XIN.

PADDLE_GND

Rev 1.0

�Si4063/60-C

9. Ordering Information

Part Number*

Description

Package Type

Operating

Temperature

Si4063-C2A-GM

ISM EZRadioPRO Transmitter

QFN-20

Pb-free

–40 to 85 °C

Si4060-C2A-GM

ISM EZRadioPRO Transmitter

QFN-20

Pb-free

–40 to 85 °C

*Note: Add an “(R)” at the end of the device part number to denote tape and reel option.

Rev 1.0

31

�Si4063/60-C

10. Package Outline: Si4063/60

Figure 15 illustrates the package details for the Si406x. Table 14 lists the values for the dimensions shown in the

illustration.

2X

bbb C

B

A

D

D2

Pin 1 (Laser)

e

20

20x L

1

E

E2

2X

aaa C

A1

20x b

ccc C

ddd

eee C

A

A3

SEATING PLANE

C

Figure 15. 20-Pin Quad Flat No-Lead (QFN)

32

Rev 1.0

C A B

�Si4063/60-C

Table 14. Package Dimensions

Dimension

Min

Nom

Max

A

0.80

0.85

0.90

A1

0.00

0.02

0.05

A3

b

0.20 REF

0.18

0.25

D

D2

0.30

4.00 BSC

2.45

2.60

e

0.50 BSC

E

4.00 BSC

2.75

E2

2.45

2.60

2.75

L

0.30

0.40

0.50

aaa

0.15

bbb

0.15

ccc

0.10

ddd

0.10

eee

0.08

Notes:

1. All dimensions are shown in millimeters (mm) unless otherwise noted.

2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MO-220,

Variation VGGD-8.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C

specification for Small Body Components.

Rev 1.0

33

�Si4063/60-C

11. PCB Land Pattern: Si4063/60

Figure 16 illustrates the PCB land pattern details for the Si406x. Table 15 lists the values for the dimensions shown

in the illustration.

Figure 16. PCB Land Pattern

34

Rev 1.0

�Si4063/60-C

Table 15. PCB Land Pattern Dimensions

Symbol

Millimeters

Min

Max

C1

3.90

4.00

C2

3.90

4.00

E

0.50 REF

X1

0.20

0.30

X2

2.55

2.65

Y1

0.65

0.75

Y2

2.55

2.65

Notes:

General

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This land pattern design is based on IPC-7351 guidelines.

Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance

between the solder mask and the metal pad is to be 60 µm minimum, all

the way around the pad.

Stencil Design

4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal

walls should be used to assure good solder paste release.

5. The stencil thickness should be 0.125 mm (5 mils).

6. The ratio of stencil aperture to land pad size should be 1:1 for the

perimeter pads.

7. A 2x2 array of 1.10 x 1.10 mm openings on 1.30 mm pitch should be

used for the center ground pad.

Card Assembly

8. A No-Clean, Type-3 solder paste is recommended.

9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020

specification for small body components.

Rev 1.0

35

�Si4063/60-C

12. Top Marking

12.1. Si4063/60 Top Marking

12.2. Top Marking Explanation

Mark Method

YAG Laser

Line 1 Marking

Part Number

40632A = Si4063 Rev 2A1

40602A = Si4060 Rev 2A1

Line 2 Marking

TTTTT = Internal Code

Internal tracking code.2

Line 3 Marking

YY = Year

WW = Workweek

Assigned by the Assembly House. Corresponds to the last

significant digit of the year and workweek of the mold date.

Notes:

1. The first letter after the part number is part of the ROM revision. The last letter indicates the firmware

revision.

2. The first letter of this line is part of the ROM revision.

36

Rev 1.0

�Simplicity Studio

One-click access to MCU tools,

documentation, software, source

code libraries & more. Available

for Windows, Mac and Linux!

www.silabs.com/simplicity

MCU Portfolio

www.silabs.com/mcu

SW/HW

www.silabs.com/simplicity

Quality

www.silabs.com/quality

Support and Community

community.silabs.com

Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers

using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific

device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories

reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy

or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply

or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific

written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected

to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no

circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations

thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®,

USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of

ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc.

400 West Cesar Chavez

Austin, TX 78701

USA

http://www.silabs.com

�