Si84xxISO-EVB UG

Si84 XX ISO E VALUATION B OAR D U SER ’ S G UIDE

1. Introduction

The Si84xxISO evaluation board allows designers to evaluate Silicon Lab's family of CMOS ultra-low-power

isolators. These isolators are CMOS devices employing RF coupler technology to transmit digital information

across an isolation barrier. Very high speed operation at low power levels is achieved. These products are based

on Silicon Laboratories’ proprietary RF isolation technology and offer shorter propagation delays, lower power

consumption, improved noise immunity, smaller installed size, and more stable operation with temperature and age

versus opto couplers. The Si841x/2x/3x/4x/5x/6x include up to six unidirectional isolated channels, permitting data

transmission up to 150 Mbps. The Si840x isolator series consists of single-package galvanic isolation solutions for

I2C, SMBus, and PMBus serial port applications. For more information, refer to the respective family data sheets.

A summary of the benefits provided by the Silicon Laboratories Si84xx CMOS Digital Isolator family includes:

Robust Noise Tolerance:

5.0

kV, 2.5 kV, and 1.0 kV Isolation Ratings

to 50 V/m Electric-field immunity

> 1000 A/m Magnetic-field immunity

25 kV/µs CMTI

FCC Class B Compliant

Up

Class-leading ESD Performance:

4

kV HBM, 2 kV CDM, 400 V MM

Ultra Low Power Operation:

<

1.4 mA/Channel @ 1 Mbps

µA standby mode

200

High Speed Operation:

DC–150

<

Mbps from –40 to 125 °C

250 ps (peak) Jitter

Precise Timing:

1.5

ns pulse width distortion

ns channel-channel matching

2 ns pulse width skew

0.5

I2C Compatible Isolators:

Bidirectional

isolated Serial Data (SDA) and Serial Clock

Rates up to 1.7 Mbps

35 mA open drain I/O

Data

Flexible Packaging Options:

NB

SOIC-8, WB SOIC-16, NB SOIC-16

compliant

RoHS

Rev. 0.3 8/10

Copyright © 2010 by Silicon Laboratories

Si84xxISO-EVB UG

�Si84xxISO-EVB UG

2. Kit Contents

The Si84xxISO Evaluation Kit contains the following items:

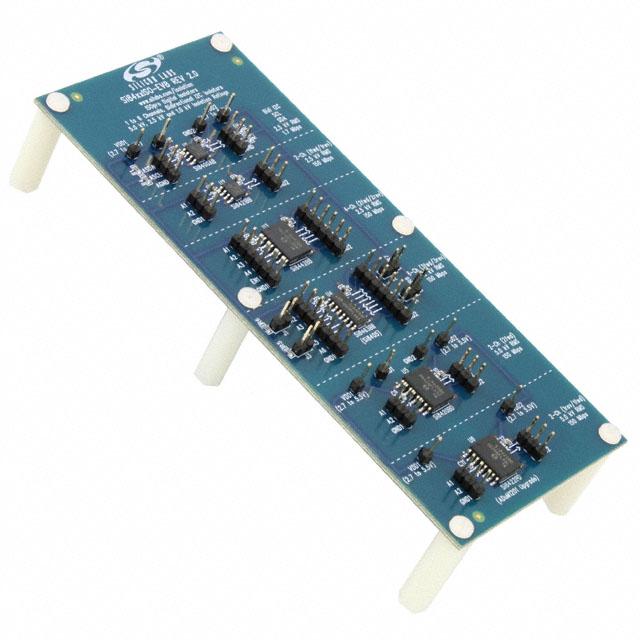

Si84xxISO based evaluation board (Si84xxISO-EVB or Si84xx5kVISO-EVB) shown in Figures 1 and 2.

Si8400, Si8421, Si8442, Si8463, Si8420 (5 kV), and Si8422 (5 kV) CMOS digital isolators installed on the

evaluation board

Figure 1. Si84xxISO Evaluation Board Overview

2

Rev. 0.3

�Si84xxISO-EVB UG

Figure 2. Si84xx5kVISO Evaluation Board Overview

Rev. 0.3

3

�Si84xxISO-EVB UG

3. Hardware Overview and Setup

The Si84xxISO evaluation board comes populated with an Si8400 (isolated I2C), Si8421 (2-channel digital isolator,

one forward, one reverse), Si8442 (4-channel digital isolator, two forward, two reverse), and Si8463 (6-channel

digital isolator, three forward, three reverse) installed. The Si84xx5kVISO-EVB adds the Si8420 and Si8422 5 kV

family members. The board is designed to be powered from two separate 5 V supplies (500 mA) that power all the

isolators on the board. Power is applied to the board before evaluating any isolated channel. Power is applied to

the Si84xxISO-EVB by connecting 5 V supplies to the topmost supply terminals (VDD1 and GND1, VDD2 and

GND2). Power is applied to the Si84xx5kVISO-EVB by applying 5 V supplies to the topmost and middle power

terminals (VDD1 and GND1, VDD2 and GND2). The top power terminals power the 2.5 kV isolators. The middle

power terminals power the 5 kV isolators. Supplies as low as 2.7 V can be used. If a user wants to evaluate an

isolator other than the ones populated, this can be accomplished by removing the footprint-compatible device

installed on the evaluation board and replacing it with the desired isolator device. Figures 3 and 5 provide

silkscreen overviews of the boards.

Figure 3. Si84xxISO Evaluation Board Silkscreen

4

Rev. 0.3

�Si84xxISO-EVB UG

Figure 4. Si84xx5kVISO Evaluation Board Silkscreen

Rev. 0.3

5

�Si84xxISO-EVB UG

3.1. Digital Isolator Considerations

The Si84xxISO evaluation board (see Figure 1 on page 2) provides a means to evaluate the Si841x,2x,3x,4x,5x,6x

digital isolator families as well as the Si8400 isolated I2C family. After power has been supplied to the board,

connect a digital input signal (5 Vpeak max, with desired clock frequency up to 150 Mbps) to the desired input

channel. To view the isolated channel’s data transmission, connect a scope probe to the output channel of interest.

There are various inputs and outputs on either side of the board depending on the device one chooses to evaluate,

as indicated by the silk screen. The board can be used to measure propagation delay, pulse-width distortion,

channel-channel matching, pulse-width skew, and various other parameters.

The nominal output impedance of an isolator driver channel is approximately 50 , ±40%, which is a combination

of the values of the on-chip series termination resistor and the channel resistance of the output driver FET. When

driving loads where transmission line effects will be a factor, output pins should be terminated with 50 controlled

impedance PCB traces.

Figure 5 illustrates the Si8421 transmitting a 500 kHz (5 Vpeak) signal through the Si8421. VDD1 and VDD2 were

powered from 5 V. Channel 1 illustrates the input, and Channel 2 illustrates the output.

Figure 5. 500 kHz (5 V Peak) Signal

6

Rev. 0.3

�Si84xxISO-EVB UG

3.2. I2C Isolator Considerations

After power has been supplied to the board, connect a digital square wave input (5 Vpeak max, with desired clock

frequency up to 1.7 MHz) to the desired input channel. The Si8400 I2C isolator has 1 k pull-up resistors already

installed. If these resistors are redundant with another board that is being used to evaluate the Si8400, the user

should remove the redundant pull-up resistors to accommodate adequate drive current for the test being

performed. Moreover, note that the Si8463 can be replaced with an Si8405 (Bidirectional I2C Isolator with two

unidirectional digital channels). Pull-up resistors of 1 k are already installed to accommodate the Si8405’s

evaluation. Pull-up jumpers J1, J2, J3, and J4 need to be installed to evaluate the Si8405. They will need to be

removed or not installed (default from factory) to evaluate the Si8463.

Figure 6 illustrates Side B Pulling Up, with Side A following for the Si8400. The Si8400 was powered from 5 V on

both sides with a 100 kHz input test signal.

Figure 6. Side B Pulling Up, Side A Following

Note: The test points in front of each device have 1 mm spacing. If desired, the test points can be replaced with a 1 mm

spacing terminal block to assist in evaluation.

Rev. 0.3

7

�R4

1K

R1

1K

TP17

TP39

TP33

TP27

Si8400

ASCL

ASDA

3

2

Si8421

A2

A1

U2

C7

1uF

VDD1(5V)

Si8400 Populated

3

2

U1

Si8421 Populated

TP18

TP15

TP7

1

AVDD

AGND

4

C3

1uF

1

VDD1

8

BVDD

BGND

VDD1(5V)

GND1

4

8

VDD2

B2

B1

6

7

BSCL

BSDA

C8

1uF

6

7

C4

1uF

VDD2(5V)

VDD2(5V)

5

GND2

5

TP40

TP34

TP28

TP19

TP16

TP10

R3

1K

J3

JUMPER

R5

1K

J1

JUMPER

R6

1K

2

TP37

TP35

TP31

TP29

TP25

TP23

7

6

5

4

3

Si8442

EN1

A4

A3

A2

A1

U3

Si8463

A6

A5

A4

A3

A2

A1

Si8463 Populated

7

6

5

4

3

2

U4

C5

1uF

VDD1(5V)

Si8442 Populated

TP41

TP21

TP13

TP11

TP8

TP5

TP3

Figure 7. Si84xxISO Evaluation Board Schematic

TP20

R2

1K

TP2

2

1

1

VDD1

GND1

1

1

GND1

GND1

8

2

VDD1

16

VDD2

8

TP1

ISOLATION

GND2

GND2

C1

1uF

ISOLATION

9

15

10

11

12

13

14

B6

B5

B4

B3

B2

B1

10

11

12

13

14

TP14

TP12

TP9

TP6

TP4

TP42

TP22

C6

1uF

15

C2

1uF

VDD2(5V)

EN2

B4

B3

B2

B1

VDD2(5V)

VDD2

16

GND2

9

Rev. 0.3

TP38

TP36

TP32

TP30

TP26

TP24

2

1

8

J2

JUMPER

R7

1K

2

1

VDD1(5V)

J4

JUMPER

R8

1K

Si84xxISO-EVB UG

4. Si84xxISO Evaluation Board Schematic

ISOLATION

ISOLATION

�R4

1K

R1

1K

3

2

ASCL

ASDA

3

2

A2

A1

Si8421

TP39

WHITE Si8421 Populated

TP33

WHITE

U2

C7

1uF

VDD1(5V)

TP18

Si8400

WHITE

Si8400 Populated

TP27

WHITE

TP17

WHITE

TP15

WHITE

TP7

WHITE

U1

1

AVDD

AGND

4

C3

1uF

1

VDD1

8

BVDD

BGND

VDD1(5V)

GND1

4

8

VDD2

B2

B1

C8

1uF

6

7

TP40

WHITE

TP34

WHITE

TP28

TP19

WHITE

TP16

WHITE

TP10

WHITE

TP20

WHITE

R2

1K

R3

1K

TP2

WHITE

J3

JUMPER

R5

1K

J1

JUMPER

R6

1K

2

7

6

5

4

3

Si8442

EN1

A4

A3

A2

A1

U3

TP37

WHITE

TP35

WHITE

TP31

WHITE

TP29

WHITE

TP25

WHITE

TP23

WHITE

Si8463

A6

A5

A4

A3

A2

A1

TP41

WHITE Si8463 Populated

7

6

5

4

3

2

U4

C5

1uF

VDD1(5V)

TP21

WHITE Si8442 Populated

TP13

WHITE

TP11

WHITE

TP8

WHITE

TP5

WHITE

TP3

WHITE

10

11

12

13

14

B6

B5

B4

B3

B2

B1

10

11

12

13

14

TP14

WHITE

TP12

WHITE

TP9

WHITE

TP6

WHITE

TP4

WHITE

TP42

WHITE

TP22

WHITE

C6

1uF

15

C2

1uF

VDD2(5V)

EN2

B4

B3

B2

B1

VDD2(5V)

Figure 8. Si84xx5kVISO Evaluation Board Schematic (1 of 2)

6

7

BSCL

BSDA

C4

1uF

VDD2(5V)

VDD2(5V)

5

GND2

5

2

1

1

VDD1

GND1

1

1

GND1

GND1

8

2

VDD1

16

VDD2

TP1

WHITE

ISOLATION

GND2

GND2

9

15

8

16

VDD2

C1

1uF

ISOLATION

GND2

9

TP38

WHITE

TP36

WHITE

TP32

WHITE

TP30

WHITE

TP26

WHITE

TP24

WHITE

2

1

Rev. 0.3

J2

JUMPER

R7

1K

2

1

ISOLATION

ISOLATION

VDD1(5V)

J4

JUMPER

R8

1K

Si84xxISO-EVB UG

5. Si84xx5kVISO Evaluation Board Schematics

9

�10

C9

1uF

VDD1(5V)_5kV

Rev. 0.3

C11

1uF

VDD1(5V)_5kV

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

1

Si8422

NC

GND1

NC

A2

A1

VDD1

NC

GND1

U6

Si8420

NC

GND1

NC

A2

A1

VDD1

NC

GND1

U5

GND2

NC

NC

B2

B1

VDD2

NC

GND2

GND2

NC

NC

B2

B1

VDD2

NC

GND2

16

9

10

11

12

13

14

15

16

9

10

11

12

13

14

15

TP44

WHITE

TP54

WHITE

TP59

WHITE

TP58

WHITE

TP56

WHITE

C12

1uF

VDD2(5V)_5kV

TP49

WHITE

TP48

WHITE

TP46

WHITE

C10

1uF

VDD2(5V)_5kV

TP51

WHITE

Figure 9. Si84xx5kVISO Evaluation Board Schematic (2 of 2)

TP60

WHITE Si8422 Populated

TP57

WHITE

TP55

WHITE

TP53

WHITE

TP50

TP52

WHITE Si8420 Populated

WHITE

TP47

WHITE

TP45

WHITE

TP43

WHITE

Si84xxISO-EVB UG

�Si84xxISO-EVB UG

6. Bill of Materials

Table 1. Si84xxISO Evaluation Board Bill of Materials

Item

Qty

Reference

Value

Mfr Part Number

Mfr

1

8

C1,C2,C3,C4,

C5,C6,C7,C8

1 µF

C0603X5R250-105K

Venkel

2

4

J1,J2,J3,J4

Jumper

TSW-102-07-T-S

Samtec

3

8

R1,R2,R3,R4,

R5,R6,R7,R8

1 k

CR0603-10W-1001F

Venkel

4

42

TP1,TP2,TP3,TP4,

TP5,TP6,TP7,TP8,

TP9,TP10,TP11,

TP12,TP13,TP14,

TP15,TP16,TP17,

TP18,TP19,TP20,

TP21,TP22,TP23,

TP24,TP25,TP26,

TP27,TP28,TP29,

TP30,TP31,TP32,

TP33,TP34,TP35,

TP36,TP37,TP38,

TP39,TP40,TP41,

TP42

White

151-201-RC

Kobiconn

5

1

U1

Si8400

Si8400AB-A-IS

Silicon Labs

6

1

U2

Si8421

Si8421AB-C-IS1

Silicon Labs

7

1

U3

Si8442

Si8442BB-C-IS

Silicon Labs

8

1

U4

Si8463

Si8463BB-A-IS1

Silicon Labs

Rev. 0.3

11

�Si84xxISO-EVB UG

Table 2. Si84xx5kVISO Evaluation Board Bill of Materials

12

Item

Qty

Reference

Value

Mfr Part Number

Mfr

1

12

C1,C2,C3,C4,C5,C6,C7,

C8,C9,C10,C11,C12

1uF

C0603X5R250-105K

Venkel

2

4

J1,J2,J3,J4

JUMPER

TSW-102-07-T-S

Samtec

3

8

R1,R2,R3,R4,R5,R6,R7,R8

1 k

CR0603-10W-1001F

Venkel

4

60

TP1,TP2,TP3,TP4,TP5,

TP6,TP7,TP8,TP9,TP10,

TP11,TP12,TP13,TP14,

TP15,TP16,TP17,TP18,

TP19,TP20,TP21,TP22,

TP23,TP24,TP25,TP26,

TP27,TP28,TP29,TP30,

TP31,TP32,TP33,TP34,

TP35,TP36,TP37,TP38,

TP39,TP40,TP41,TP42,

TP43,TP44,TP45,TP46,

TP47,TP48,TP49,TP50,

TP51,TP52,TP53,TP54,

TP55,TP56,TP57,TP58,

TP59,TP60

WHITE

151-201-RC

Kobiconn

5

1

U1

Si8400

Si8400AB-A-IS

Silicon Labs

6

1

U2

Si8421

Si8421AB-C-IS1

Silicon Labs

7

1

U3

Si8442

Si8442BB-C-IS

Silicon Labs

8

1

U4

Si8463

Si8463BB-A-IS1

Silicon Labs

9

1

U5

Si8420

Si8420BD-A-IS

Silicon Labs

10

1

U6

Si8422

Si8422BD-B-IS

Silicon Labs

11

6

Standoff

12

6

Standoff

screw

Rev. 0.3

�Si84xxISO-EVB UG

7. Ordering Guide

Table 3. Si84xxISO Evaluation Board Ordering Guide

Ordering Part Number (OPN)

Description

Si84XXISO-KIT

Si84xx CMOS digital isolator evaluation board kit (2.5 kV, 5 kV)

Rev. 0.3

13

�Si84xxISO-EVB UG

DOCUMENT CHANGE LIST

Revision 0.1 to Revision 0.2

Added Si84xx5kVISO-EVB descriptive details

throughout.

Added

Figure 2 on page 3.

Figure 4 on page 5.

Added Figure 8 on page 9.

Added Figure 9 on page 10.

Added Table 2.

Added

Revision 0.2 to Revision 0.3

Replaced “ISOpro” with “CMOS” in text.

Added "7. Ordering Guide" on page 13.

14

Rev. 0.3

�Si84xxISO-EVB UG

NOTES:

Rev. 0.3

15

�Si84xxISO-EVB UG

CONTACT INFORMATION

Silicon Laboratories Inc.

400 West Cesar Chavez

Austin, TX 78701

Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669

Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page:

https://www.silabs.com/support/pages/contacttechnicalsupport.aspx

and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice.

Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from

the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features

or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to

support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

16

Rev. 0.3

�