LNBS21

LNB SUPPLY AND CONTROL IC WITH

STEP-UP CONVERTER AND I2C INTERFACE

■

■

COMPLETE INTERFACE BETWEEN LNB

AND I2CTM BUS

BUILT-IN DC/DC CONTROLLER FOR

SINGLE 12V SUPPLY OPERATION

ACCURATE BUILT-IN 22KHz TONE

OSCILLATOR

SUITS WIDELY ACCEPTED STANDARDS

FAST OSCILLATOR START-UP FACILITATES

DiSEqCTM ENCODING

BUILT-IN 22KHz TONE DETECTOR

SUPPORTS BI-DIRECTIONAL DiSEqCTM

LOOP-THROUGH FUNCTION FOR SLAVE

OPERATION

LNB SHORT CIRCUIT PROTECTION AND

DIAGNOSTIC

CABLE LENGTH DIGITAL COMPENSATION

INTERNAL OVER TEMPERATURE

PROTECTION

)

s

(

t

c

u

d

o s)

r

(

P

t

c

e u

t

e

l od

o

s Pr

b

O ete

l

)

o

s

(

s

t

b

c

u -O

d

o s)

r

P

(

t

e uc

t

e

l od

o

s Pr

b

O te

e

l

o

s

b

■

■

■

■

■

■

■

■

DESCRIPTION

Intended for analog and digital satellite STB

receivers/SatTV, sets/PC cards, the LNBS21 is a

monolithic voltage regulator and interface IC,

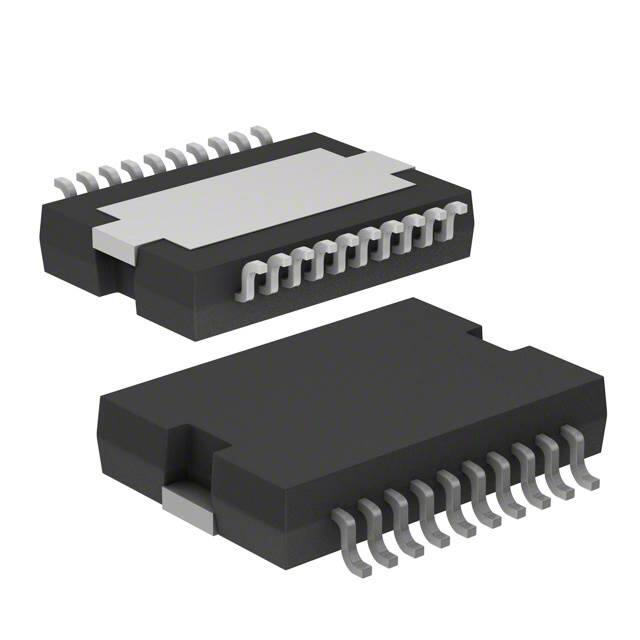

PowerSO-20

assembled in PowerSO-20, specifically designed

to provide the power and the 13/18V, 22KHz tone

signalling to the LNB downconverter in the

antenna or to the multiswitch box. In this

application field, it offers a complete solution with

extremely low component count, low power

dissipation together with simple design and I2CTM

standard interfacing.

This IC has a built in DC/DC step-up controller

that, from a single supply source ranging from 8 to

15V, generates the voltages that let the linear

Figure 1: Schematic Diagram

LNBS21

Gate

LT1

Sense

Step-up

Controller

Feedback

LT2

Vup

Vcc

OUT

Preregul.+

U.V.lockout

O

Byp

+P.ON res.

Enable

I Select

V Select

Linear Post-reg

+Modulator

+Protections

SDA

SCL

ADDR

DSQIN

October 2004

EXTM

Diagnostics

I²C

interf.

DETIN

22KHz

Oscill.

Tone

Detector

DSQOUT

Rev. 3

1/21

�LNBS21

post-regulator to work at a minimum dissipated

power. An UnderVoltage Lockout circuit will

disable the whole circuit when the supplied VCC

drops below a fixed threshold (6.7V typically). The

internal 22KHz tone generator is factory trimmed

in accordance to the standards, and can be

controlled either by the I2CTM interface or by a

dedicated pin (DSQIN) that allows immediate

DiSEqCTM data encoding (*). All the functions of

this IC are controlled via I2CTM bus by writing 6

bits on the System Register (SR, 8 bits). The

same register can be read back, and two bits will

report the diagnostic status. When the IC is put in

Stand-by (EN bit LOW), the power blocks are

disabled and the loop-through switch between

LT1 and LT2 pins is closed, thus leaving all LNB

powering and control functions to the Master

Receiver (**). When the regulator blocks are

active (EN bit HIGH), the output can be logic

controlled to be 13 or 18 V (typ.) by mean of the

VSEL bit (Voltage SELect) for remote controlling

of non-DiSEqC LNBs. Additionally, it is possible to

increment by 1V (typ.) the selected voltage value

to compensate for the excess voltage drop along

the coaxial cable (LLC bit HIGH). In order to

minimize the power dissipation, the output voltage

of the internal step-up converter is adjusted to

allow the linear regulator to work at minimum

dropout. Another bit of the SR is addressed to the

remote control of non-DiSEqC LNBs: the TEN

(Tone ENable) bit. When it is set to HIGH, a

continuous 22KHz tone is generated regardless of

the DSQIN pin logic status. The TEN bit must be

set LOW when the DSQIN pin is used for

DiSEqCTM encoding. The fully bi-directional

DiSEqCTM interfacing is completed by the built-in

22KHz tone detector. Its input pin (DETIN) must

be AC coupled to the DiSEqCTM bus, and the

extracted PWK data are available on the

DSQOUT pin (*).

The current limitation block has two thresholds

that can be selected by the ISEL bit of the SR; the

lower threshold is between 650 and 900mA

(ISEL=HIGH), while the higher threshold is

between 750 and 1000mA (ISEL=LOW).

In order to improve design flexibility and to allow

implementation of newcoming LNB remote control

standards, an analogic modulation input pin is

available (EXTM). An appropriate DC blocking

capacitor must be used to couple the modulating

signal source to the EXTM pin. When external

modulation is not used, the relevant pin can be left

open.

This IC is also protected against overheating:

when the junction temperature exceeds 150°C

(typ.), the step-up converter and the linear

regulator are shut off, the loop-trough switch is

opened, and the OTF bit of the SR is set to HIGH.

Normal operation is resumed and the OTF bit is

reset to LOW when the junction is cooled down to

140°C (typ.).

The current protection block is SOA type. This

limits the short circuit current (ISC) typically at

300mA with ISEL=HIGH and at 400mA with

ISEL=LOW when the output port is connected to

ground.

It is possible to set the Short Circuit Current

protection either statically (simple current clamp)

or dynamically by the PCL bit of the SR; when the

PCL (Pulsed Current Limiting) bit is set to LOW,

the

overcurrent

protection

circuit

works

dynamically: as soon as an overload is detected,

the output is shut-down for a time toff, typically

900ms. Simultaneously the OLF bit of the System

Register is set to HIGH. After this time has

elapsed, the output is resumed for a time ton=1/

10toff (typ.). At the end of ton, if the overload is still

detected, the protection circuit will cycle again

through Toff and Ton. At the end of a full Ton in

which no overload is detected, normal operation is

resumed and the OLF bit is reset to LOW. Typical

Ton+Toff time is 990ms and it is determined by an

internal timer. This dynamic operation can greatly

reduce the power dissipation in short circuit

condition, still ensuring excellent power-on start

up in most conditions (**).

)

s

(

t

c

u

d

o s)

r

(

P

t

c

e u

t

e

l od

o

s Pr

b

O ete

l

)

o

s

(

s

t

b

c

u -O

d

o s)

r

P

(

t

e uc

t

e

l od

o

s Pr

b

O te

e

l

o

s

b

O

However, there could be some cases in which an

highly capacitive load on the output may cause a

difficult start-up when the dynamic protection is

chosen. This can be solved by initiating any power

start-up in static mode (PCL=HIGH) and then

switching to the dynamic mode (PCL=LOW) after

a chosen amount of time. When in static mode,

the OLF bit goes HIGH when the current clamp

limit is reached and returns LOW when the

overload condition is cleared.

(*): External components are needed to comply to bi-directional DiSEqCTM bus hardware requirements. Full compliance of the whole application to DiSEqCTM specifications is not implied by the use of this IC.

(**): The current limitation circuit has no effect on the loop-through switch. When EN bit is LOW, the current flowing from LT1 to LT2 must be

externally limited.

2/21

�LNBS21

Table 1: Ordering Codes

TYPE

PowerSO-20

(Tube)

PowerSO-20

(Tape & Reel)

LNBS21

LNBS21PD

LNBS21PD-TR

Table 2: Absolute Maximum Ratings

Symbol

Parameter

Value

Unit

VCC

DC Input Voltage

16

V

VUP

DC Input Voltage

25

V

VLT1, VLT2 DC Input Voltage

20

V

Internally Limited

mA

DC Output Pin Voltage

-0.3 to 22

V

Logic Input Voltage (SDA, SCL, DSQIN)

-0.3 to 7

V

2

VPP

)

s

(

t

c

u

d

o s)

r

(

P

t

c

e u

t

e

l od

o

s Pr

b

O ete

l

)

o

s

(

s

t

b

c

u -O

d

o s)

r

P

(

t

e uc

t

e

l od

o

s Pr

b

O te

e

l

o

s

b

IO

Output Current

VO

VI

VDETIN

VOH

Detector Input Signal Amplitude

Logic High Output Voltage (DSQOUT)

7

V

900

mA

ILT

Bypass Switch ON Current

VLT

Bypass Switch OFF Voltage

±20

V

Gate Current

±400

mA

-0.3 to 1

V

-0.3 to 7

V

IGATE

VSENSE

Current Sense Voltage

VADDRESS Address Pin Voltage

Tstg

Storage Temperature Range

-40 to +150

°C

Top

Operating Junction Temperature Range

-40 to +125

°C

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is

not implied.

Table 3: Thermal Data

Symbol

Rthj-case

Parameter

Thermal Resistance Junction-case

PowerSO-20

Unit

2

°C/W

Figure 2: Pin Connection (top view)

O

PowerSO-20

3/21

�LNBS21

Table 4: Pin Description

SYMBOL

VCC

NAME

Supply Input

GATE

External Switch Gate

SENSE

Current Sense Input

Vup

Step-up Voltage

FUNCTION

8V to 15V supply. A 220µF bypass capacitor to

GND with a 470nF (ceramic) in parallel is

recommended

External MOS switch Gate connection of the

step-up converter

Current Sense comparator input. Connected to

current sensing resistor

Input of the linear post-regulator. The voltage on this

pin is monitored by internal step-ut controller to

keep a minimum dropout across the linear pass

transistor

Output of the linear post regulator modulator to the

LNB. See truth table for voltage selections.

PIN NUMBER

vs. PACKAGE

18

17

16

19

)

s

(

t

c

u

d

o s)

r

(

P

t

c

e u

t

e

l od

o

s Pr

b

O ete

l

)

o

s

(

s

t

b

c

u -O

d

o s)

r

P

(

t

e uc

t

e

l od

o

s Pr

b

O te

e

l

o

s

b

OUT

Output Port

SDA

Serial Data

Bidirectional data from/to I2C bus.

12

SCL

Serial Clock

Clock from I2C bus.

When the TEN bit of the System Register is LOW,

this pin will accept the DiSEqC code from the main

µcontroller. The LNBS21 will use this code to

modulate the internally generated 22kHz carrier. Set

to GND the pin if not used.

22kHz Tone Detector Input. Must be AC coupled to

the DiSEqC bus.

Open collector output of the tone Detector to the

main µcontroller for DiSEqC data decoding. It is

LOW when tone is detected.

External Modulation Input. Need DC decoupling to

the AC source. If not used, can be left open.

Pins to be connected to ground.

Needed for internal preregulator filtering

In standby mode the power switch between LT1 and

LT2 is closed. Max allowed current is 900mA. this

pin can be left open if loop through function is not

needed.

Same as above

13

DSQIN

DiSEqC Input

DETIN

Detector In

DSQOUT DiSEqC Output

EXTM

External Modulator

GND

BYP

LT1

Ground

Bypass Capacitor

Loop Through Switch

LT2

ADDR

Loop Through Switch

Address Setting

O

4/21

I2C

bus addresses available by setting the

Four

Address Pin level voltage

2

14

9

15

5

1, 6, 10, 11, 20

8

4

3

7

�LNBS21

Figure 3: Typical Application Circuit

D1 1N4001

IC1

Master STB

LT1

Vup

C2

220µF

C3

470nF

C7

10nF

Ceramic

IC2

(Note 3)

LT2

STS4DNFS30L

270µH

to LNB

Gate

Vo

C8

10nF

D2

BAT43

)

s

(

t

c

u

d

o s)

r

(

P

t

c

e u

t

e

l od

o

s Pr

b

O ete

l

)

o

s

(

s

t

b

c

u -O

d

o s)

r

P

(

t

e uc

t

e

l od

o

s Pr

b

O te

e

l

o

s

b

LNBS21

Sense

L1=22µH

Rsc

0.1Ω

Ω

15 ohm

see Note 2

DETIN

(Note 1)

(Note 4)

C6

10nF

Byp

C5

470nF

Vcc

Vin

12V

C1

220µF

C4

470nF

Ceramic

EXTM

DSQIN(Note 1)

ADDRESS

SCL

SDA

GND

0

很抱歉,暂时无法提供与“LNBS21PD-TR”相匹配的价格&库存,您可以联系我们找货

免费人工找货