TSX9291, TSX9292

16 MHz rail-to-rail CMOS 16 V operational amplifiers

Datasheet - production data

Applications

• Communications

• Process control

• Active filtering

627������76;�����

')1���[���76;�����

• Test equipment

Description

0LQL62���76;�����

62���76;�����

Features

• Rail-to-rail input and output

• Wide supply voltage: 4 V - 16 V

The TSX9291 and TSX9292 operational

amplifiers (op amps) offer excellent AC

characteristics such as 16 MHz gain bandwidth,

27 V/µs slew rate, and 0.0003 % THD+N. They

are decompensated amplifiers which are stable

when used with a gain higher than 2 or lower than

-1. The rail-to-rail input and output capability of

these devices operates on a wide supply voltage

range of 4 V to 16 V. These last two features

make the TSX929x series particularly welladapted for a wide range of applications such as

communications, I/V amplifiers for ADCs, and

active filtering applications.

Table 1. Device summary

• Gain bandwidth product: 16 MHz typ at 16 V

• Low power consumption: 2.8 mA typ at 16 V

• Slew rate: 27 V/µs

Op amp version

Single

Dual

TSX9291

TSX9292

• Stable when used in gain configuration

• Low input bias current: 10 pA typ

• High tolerance to ESD: 4 kV HBM

• Extended temperature range:

-40° C to +125° C

• Automotive qualification

Related products

• See the TSX5 series for low power features

• See the TSX6 series for micro power features

• See the TSX92 series for unity gain stability

• See the TSV9 series for lower voltage

August 2022

This is information on a product in full production.

DocID024568 Rev 5

1/32

www.st.com

�Contents

TSX9291, TSX9292

Contents

1

Package pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2

Absolute maximum ratings and operating conditions . . . . . . . . . . . . . 4

3

Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4

Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5

4.1

Operating voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.2

Rail-to-rail input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.3

Input pin voltage range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.4

Stability for gain = -1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.5

Input offset voltage drift over temperature . . . . . . . . . . . . . . . . . . . . . . . . 19

4.6

Long-term input offset voltage drift . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.7

Capacitive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.8

High side current sensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.9

High speed photodiode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.1

SOT23-5 package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.2

DFN8 2x2 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3

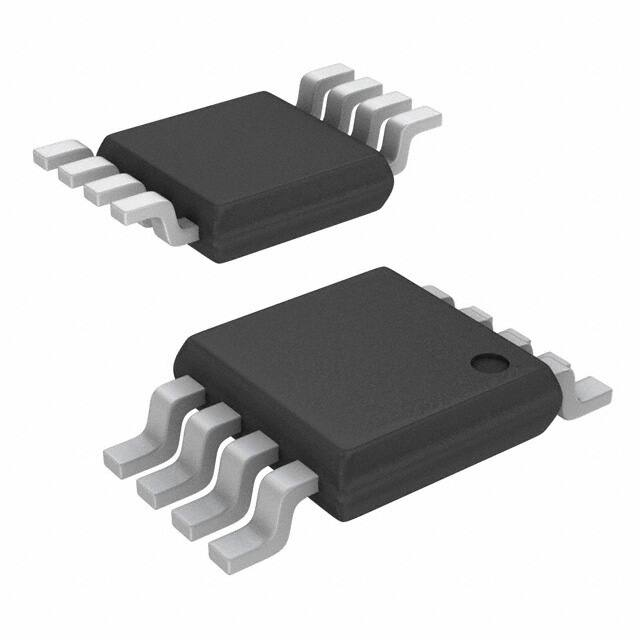

MiniSO8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.4

SO8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

6

Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2/32

DocID024568 Rev 5

�TSX9291, TSX9292

1

Package pin connections

Package pin connections

Figure 1. Pin connections (top view)

287

9&&�

�

�

9&&�

�

,1�

,1�

�

�

SOT23-5 (TSX9291)

287�

�

�

9&&�

287�

9&&�

,1��

�

�

287�

,1��

287�

,1��

�

�

,1��

,1��

,1��

9&&�

�

�

,1��

9&&�

,1��

DFN8 2x2 (TSX9292)

DocID024568 Rev 5

MiniSO8/SO8 (TSX9292)

3/32

32

�Absolute maximum ratings and operating conditions

2

TSX9291, TSX9292

Absolute maximum ratings and operating conditions

Table 2. Absolute maximum ratings (AMR)

Symbol

VCC

Parameter

Supply voltage

(1)

Vid

Differential input voltage

Vin

Input voltage

Iin

Tstg

Rthja

Tj

Input current

(3)

Storage temperature

Thermal resistance junction to ambient

SOT23-5

DFN8 2x2

MiniSO8

SO8

MM: machine

18

V

±VCC

mV

VCC- - 0.2 to VCC++ 0.2

V

10

mA

-65 to +150

°C

250

57

190

125

150

model(6)

°C/W

°C

4000

model(7)

CDM: charged device

Unit

(4)(5)

Maximum junction temperature

HBM: human body

ESD

(2)

Value

100

model(8)

V

1500

Latch-up immunity

200

mA

1. All voltage values, except the differential voltage are with respect to network ground terminal.

2. The differential voltage is the non-inverting input terminal with respect to the inverting input terminal.

3. Input current must be limited by a resistor in series with the inputs.

4. Short-circuits can cause excessive heating and destructive dissipation.

5. Rth are typical values.

6. According to JEDEC standard JESD22-A114F

7. According to JEDEC standard JESD22-A115A

8. According to ANSI/ESD STM5.3.1

Table 3. Operating conditions

Symbol

4/32

Parameter

VCC

Supply voltage

Vicm

Common mode input voltage range

Toper

Operating free air temperature range

Value

4 to 16

DocID024568 Rev 5

VCC- - 0.1 to VCC+ + 0.1

-40 to +125

Unit

V

°C

�TSX9291, TSX9292

3

Electrical characteristics

Electrical characteristics

Table 4. Electrical characteristics at VCC+ = +4.5 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL = 10 kΩ connected to VCC/2 (unless otherwise specified)

Symbol

Vio

∆Vio/∆T

∆Vio

Iib

Iio

Parameter

Input offset voltage

Conditions

Min.

Typ.

Vicm = 2 V

Tmin < Top < Tmax

Input offset voltage drift

2

Max.

Unit

4

5

mV

10

µV/°C

nV

month

Long-term input offset

voltage drift(1)(2)

TSX9291

TSX9292

6

9

Input bias current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

Input offset current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

---------------------------

pA

RIN

Input resistance

1

TΩ

CIN

Input capacitance

8

pF

CMR

Avd

VOH

VOL

Common mode rejection

ratio 20 log (∆Vic/∆Vio)

GBP

FU

61

59

82

Vicm = -0.1 V to 4.6 V, VOUT = VCC/2

Tmin < Top < Tmax

59

57

72

RL= 2 kΩ, Vout = 0.3 V to 4.2 V

Tmin < Top < Tmax

100

90

108

RL= 10 kΩ, Vout = 0.2 V to 4.3 V

Tmin < Top < Tmax

100

90

112

dB

Large signal voltage gain

RL= 2 kΩ to VCC/2

Tmin < Top < Tmax

50

80

100

RL= 10 kΩ to VCC/2

Tmin < Top < Tmax

10

16

20

RL= 2 kΩ to VCC/2

Tmin < Top < Tmax

42

80

100

RL= 10 kΩ to VCC/2

Tmin < Top < Tmax

9

16

20

High level output voltage

Low level output voltage

mV

from

VCC+

mV

Isink

Vout = 4.5 V

Tmin < Top < Tmax

16

13

21

Isource

Vout = 0 V

Tmin < Top < Tmax

16

13

21

Supply current

(per amplifier)

No load, Vout = VCC/2

Tmin < Top < Tmax

2.9

Gain bandwidth product

RL = 10 kΩ, CL = 20 pF, G = 20 dB

15.6

Unity gain frequency

RL = 10 kΩ, CL = 20 pF

14.2

Iout

ICC

Vicm = -0.1 V to 2 V, VOUT = VCC/2

Tmin < Top < Tmax

DocID024568 Rev 5

mA

3.4

3.5

MHz

5/32

32

�Electrical characteristics

TSX9291, TSX9292

Table 4. Electrical characteristics at VCC+ = +4.5 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL = 10 kΩ connected to VCC/2 (unless otherwise specified) (continued)

Symbol

Parameter

Conditions

Phase margin = 60 °, Rg = Rf = 1 kΩ

Min.

Typ.

Max.

Unit

-1

+2

Gain

Minimum gain for stability

SR+

Positive slew rate

Av = +1, Vout = 0.5 to 4.0 V

Measured between 10 % to 90 %

27

SR-

Negative slew rate

Av = +1, Vout = 4.0 to 0.5 V

Measured between 90 % to 10 %

22

en

Equivalent input noise

voltage

f = 10 kHz

f = 100 kHz

17.9

12.9

nV

-----------Hz

e n

Low-frequency peak-topeak input noise

Bandwidth: f = 0.1 to 10 Hz

8.1

µVpp

Total harmonic distortion +

noise

f = 1 kHz, Av = +1,

RL = 10 kΩ, Vout = 2 Vrms

0.002

%

THD+N

RL = 10 kΩ, CL = 20 pF

V/µs

1. Typical value is based on the Vio drift observed after 1000h at 125°C extrapolated to 25°C using the Arrhenius law and

assuming an activation energy of 0.7 eV. The operational amplifier is aged in follower mode configuration. See Section 4.6:

Long-term input offset voltage drift.

2. When used in comparator mode, with high differential input voltage, during a long period of time with VCC close to 16V and

Vicm>VCC/2, Vio can experience a permanent drift of few mV drift. The phenomenon is particularly worsen at low

temperatures.

6/32

DocID024568 Rev 5

�TSX9291, TSX9292

Electrical characteristics

Table 5. Electrical characteristics at VCC+ = +10 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL= 10 kΩ connected to VCC/2 (unless otherwise specified)

Symbol

Vio

∆Vio/∆T

Parameter

Input offset voltage

Conditions

Min.

Typ.

Tmin < Top < Tmax

Input offset voltage drift

2

Max.

Unit

4

5

mV

10

µV/°C

nV

month

Long-term input offset

voltage drift(1) (2)

TSX9291

TSX9292

92

128

Iib

Input bias current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

Iio

Input offset current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

∆Vio

---------------------------

pA

RIN

Input resistance

1

TΩ

CIN

Input capacitance

8

pF

CMR

Avd

VOH

VOL

Common mode rejection

ratio 20 log (∆Vic/∆Vio)

GBP

FU

Gain

72

70

85

Vicm = -0.1 V to 10.1 V, VOUT = VCC/2

Tmin < Top < Tmax

64

62

75

RL = 2 kΩ, Vout = 0.3 V to 9.7 V

Tmin < Top < Tmax

100

90

107

RL = 10 kΩ, Vout = 0.2 V to 9.8 V

Tmin < Top < Tmax

100

90

117

dB

Large signal voltage gain

RL = 2 kΩ to VCC/2

Tmin < Top < Tmax

94

110

130

RL = 10 kΩ to VCC/2

Tmin < Top < Tmax

31

40

50

RL = 2 kΩ to VCC/2

Tmin < Top < Tmax

80

110

130

RL = 10 kΩ to VCC/2

Tmin < Top < Tmax

14

40

50

High level output voltage

Low level output voltage

mV

from

VCC+

mV

Isink

Vout = 10 V

Tmin < Top < Tmax

50

42

55

Isource

Vout = 0 V

Tmin < Top < Tmax

75

70

82

Supply current

(per amplifier)

No load, Vout = VCC/2

Tmin < Top < Tmax

3.1

Gain bandwidth product

RL = 10 kΩ, CL = 20 pF, G = 20 dB

16

Unity gain frequency

RL = 10 kΩ, CL = 20 pF

Minimum gain for stability

Phase margin = 60 °, Rg = Rf = 1 kΩ

Iout

ICC

Vicm = -0.1 V to 7 V, VOUT = VCC/2

Tmin < Top < Tmax

RL = 10 kΩ, CL = 20 pF

DocID024568 Rev 5

15.4

mA

3.6

3.6

MHz

-1

+2

7/32

32

�Electrical characteristics

TSX9291, TSX9292

Table 5. Electrical characteristics at VCC+ = +10 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL= 10 kΩ connected to VCC/2 (unless otherwise specified) (continued)

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

Positive slew rate

Av = +1, Vout = 0.5 to 9.5 V

Measured between 10 % to 90 %

29

Negative slew rate

Av = +1, Vout = 9.5 to 0.5 V

Measured between 90 % to 10 %

30

en

Equivalent input noise

voltage

f = 10 kHz

f = 100 kHz

16.8

12

nV

-----------Hz

en

Low-frequency peak-topeak input noise

Bandwidth: f = 0.1 to 10 Hz

8.64

µVpp

THD+N

Total harmonic distortion

+ noise

f = 1 kHz, Av = +1,

RL = 10 kΩ, Vout = 2 Vrms

0.0006

%

SR+

SR-

V/µs

1. Typical value is based on the Vio drift observed after 1000h at 125°C extrapolated to 25°C using the Arrhenius law and

assuming an activation energy of 0.7 eV. The operational amplifier is aged in follower mode configuration. See Section 4.6:

Long-term input offset voltage drift.

2. When used in comparator mode, with high differential input voltage, during a long period of time with VCC close to 16V and

Vicm>VCC/2, Vio can experience a permanent drift of few mV drift. The phenomenon is particularly worsen at low

temperatures.

8/32

DocID024568 Rev 5

�TSX9291, TSX9292

Electrical characteristics

Table 6. Electrical characteristics at VCC+ = +16 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL= 10 kΩ connected to VCC/2 (unless otherwise specified)

Symbol

Vio

∆Vio/∆T

Parameter

Input offset voltage

Conditions

Min.

Typ.

Tmin < Top < Tmax

Input offset voltage drift

2

Max.

Unit

4

5

mV

10

µV/°C

µV

month

Long-term input offset

voltage drift(1) (2)

TSX9291

TSX9292

Iib

Input bias current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

Iio

Input offset current

Vout = VCC/2

Tmin < Top < Tmax

10

100

200

∆Vio

1.73

2.26

---------------------------

pA

RIN

Input resistance

1

TΩ

CIN

Input capacitance

8

pF

CMR

SVR

Avd

VOH

VOL

Common mode rejection

ratio 20 log (∆Vic/∆Vio)

Supply voltage rejection

ratio

GBP

FU

73

71

85

Vicm = -0.1 V to 16.1 V, VOUT = VCC/2

Tmin < Top < Tmax

67

65

76

Vcc = 4.5 V to 16 V

Tmin < Top < Tmax

73

71

85

RL= 2 kΩ, Vout = 0.3 V to 15.7 V

Tmin < Top < Tmax

100

90

105

RL= 10 kΩ, Vout = 0.2 V to 15.8 V

Tmin < Top < Tmax

100

90

113

dB

Large signal voltage gain

RL= 2 kΩ to VCC/2

Tmin < Top < Tmax

150

200

230

RL= 10 kΩ to VCC/2

Tmin < Top < Tmax

43

50

70

RL= 2 kΩ to VCC/2

Tmin < Top < Tmax

140

200

230

RL= 10 kΩ to VCC/2

Tmin < Top < Tmax

30

50

70

High level output voltage

Low level output voltage

mV

from

VCC+

mV

Isink

Vout = 16 V

Tmin < Top < Tmax

45

40

50

Isource

Vout = 0 V

Tmin < Top < Tmax

65

60

74

Supply current

(per amplifier)

No load, Vout = VCC/2

Tmin < Top < Tmax

2.8

Gain bandwidth product

RL = 10 kΩ, CL = 20 pF, G = 20 dB

16

Unity gain frequency

RL = 10 kΩ, CL = 20 pF

Iout

ICC

Vicm = -0.1 V to 13 V, VOUT = VCC/2

Tmin < Top < Tmax

DocID024568 Rev 5

15.7

mA

3.4

3.4

MHz

9/32

32

�Electrical characteristics

TSX9291, TSX9292

Table 6. Electrical characteristics at VCC+ = +16 V with VCC- = 0 V, Vicm = VCC/2, Tamb = 25 ° C, and

RL= 10 kΩ connected to VCC/2 (unless otherwise specified) (continued)

Symbol

Parameter

Conditions

Gain

Minimum gain for stability

Phase margin = 60 °, Rg = Rf = 1 kΩ

SR+

Positive slew rate

Av = +1, Vout = 0.5 to 15.5 V

Measured between 10 % to 90 %

26

SR-

Negative slew rate

Av = +1, Vout = 15.5 to 0.5 V

Measured between 90 % to 10 %

27

en

Equivalent input noise

voltage

f = 10 kHz

f = 100 kHz

16.5

11.8

nV

-----------Hz

e n

Low-frequency peak-topeak input noise

Bandwidth: f = 0.1 to 10 Hz

8.58

µVpp

THD+N

Total harmonic distortion

+ Noise

f = 1 kHz, Av = +1,

RL= 10 kΩ, Vout = 4Vrms

0.0003

%

Settling time

Gain = +1, 100 mV input voltage

0.1 % of final value

1 % of final value

245

178

ns

tS

RL = 10 kΩ, CL = 20 pF

Min.

Typ.

Max.

Unit

-1

+2

V/µs

1. Typical value is based on the Vio drift observed after 1000h at 125°C extrapolated to 25°C using the Arrhenius law and

assuming an activation energy of 0.7 eV. The operational amplifier is aged in follower mode configuration. See Section 4.6:

Long-term input offset voltage drift.

2. When used in comparator mode, with high differential input voltage, during a long period of time with VCC close to 16V and

Vicm>VCC/2, Vio can experience a permanent drift of few mV drift. The phenomenon is particularly worsen at low

temperatures.

10/32

DocID024568 Rev 5

�TSX9291, TSX9292

Electrical characteristics

Figure 2. Supply current vs. supply voltage

Figure 3. Distribution of input offset voltage at

VCC = 4.5 V

0

3

T=25°C

V

5

2

.

2

=

m

c

i

V

,

V

5

.

4

=

c

c

V

T=125°C

5

2

VICM=VCC/2

o

i

V

f

o

n

o

i

t

u

b

i

r

t

s

i

D

3.6

0

2

2.4

T=-40°C

1.2

5

0.6

0

3

2

1

16.0

0

14.0

)

V

m

(

e

g

a

t

l

o

V

t

e

s

f

f

O

t

u

p

n

I

6.0

8.0 10.0 12.0

Supply voltage (V)

1

-

4.0

2

-

2.0

3

-

0.0

0.0

0

1

%

n

o

i

t

a

l

u

p

o

P

1.8

5

1

Supply Current (mA)

3.0

Figure 4. Distribution of input offset voltage at Figure 5. Input offset voltage vs. temperature at

VCC = 16 V

VCC = 16 V

0

3

5

o

i

V

f

o

n

o

i

t

u

b

i

r

t

s

i

D

0

2

Input offset voltage (mV)

V

8

=

m

c

i

V

,

V

6

1

=

c

c

V

5

2

5

1

0

1

%

n

o

i

t

a

l

u

p

o

P

Vcc=16V, Vicm=8V

3

0

-3

5

0

3

2

1

0

1

-

2

-

3

-

-5

-40

-20

0

)

V

m

(

e

g

a

t

l

o

v

t

e

s

f

f

o

t

u

p

n

I

20

40

60

Temperature (°C)

Figure 6. Distribution of input offset voltage

drift over temperature

100

120

Figure 7. Input offset voltage vs. common mode

voltage at VCC = 4 V

5

2

1.0

0.8

T

/

o

iV

∆

∆

Vcc=4V

0.5

V

8

=

m

c

i

V

,

V

6

1

=

c

c

V

5

1

Input offset voltage (mV)

0

2

0

1

%

n

o

i

t

a

l

u

p

o

P

80

0.3

0.0

-0.3

-0.5

T=-40°C

-0.8

T=25°C

-1.0

5

-1.3

-1.5

T=125°C

-1.8

0

0

1

-

2

-

3

-

4

-

5

-

6

-

7

-

-2.0

0.0 0.3 0.5 0.8 1.0 1.3 1.5 1.8 2.0 2.3 2.5 2.8 3.0 3.3 3.5 3.8 4.0

)

C

°

/

V

µ

(

T

/

o

iV

∆

Common mode voltage(V)

∆

DocID024568 Rev 5

11/32

32

�Electrical characteristics

TSX9291, TSX9292

Figure 9. Output current vs. output voltage at

VCC = 4 V

1.8

30

1.2

20

0.6

T=25°C

0.0

-0.6

T=-40°C

-1.2

-1.8

Output Current (mA)

Input offset voltage (mV)

Figure 8. Input offset voltage vs. common mode

voltage at VCC = 16 V

Vcc=16V

-3.0

0.0

1.5

3.0

4.5

6.0

7.5

9.0

10.5

12.0

13.5

Figure 10. Output current vs. output voltage at

VCC = 10 V

Sink

Vid=-1V

Vcc=4V

-10

50

T=125°C

T=25°C

Source

Vid=1V

0

Vcc=10V

-25

0.5

1.0

1.5

2.0

2.5

Output Voltage (V)

3.0

3.5

-50

Sink

Vid=-1V

T=-40°C

25

T=125°C

T=25°C

0

Vcc=16V

-25

-50

Source

Vid=1V

-75

0.0

1.0

2.0

3.0 4.0 5.0 6.0 7.0

Output Voltage (V)

8.0

9.0 10.0

Figure 12. Output rail linearity

Source

Vid=1V

-75

0.0

2.5

5.0

7.5

10.0

Output Voltage (V)

12.5

140

15.6

120

15.4

100

14.8

1.0

0.4

Vcc=16V

G=2

T=25°C

Rl=10kΩ

0.2

40

-20

-40

8.0

7.9

7.8

7.7

7.6

7.5

7.4

0.5

0.4

0.3

0.2

0.1

Phase

0

0.0

0.0

60

20

Rl=2kΩ

Phase (°)

80

15.0

0.6

360

320

280

240

200

160

120

80

40

0

-40

-80

-120

-160

-200

-240

-280

-320

-360

Gain

15.2

Gain (dB)

Output voltage (V)

15.8

0.8

15.0

Figure 13. Open loop gain vs. frequency

16.0

0.01

Input voltage (V)

12/32

4.0

Figure 11. Output current vs. output voltage at

VCC = 16 V

Output Current (mA)

Output Current (mA)

T=125°C

0

T=-40°C

25

T=25°C

10

-30

0.0

15.0

Common mode voltage(V)

50

T=-40°C

-20

T=125°C

-2.4

Sink

Vid=-1V

DocID024568 Rev 5

Vcc=16V, Vicm=8V,

Rl=10kΩ , Cl=20pF, VRl=Vcc/2

0.1

1

10

100

Frequency (kHz)

1000

10000

�TSX9291, TSX9292

Electrical characteristics

Figure 14. Bode diagram vs. temperature for

VCC = 4 V

Figure 15. Bode diagram vs. temperature for

VCC = 10 V

250

250

Gain

200

200

Gain

150

150

T=25°C

T=125°C

0

-50

T=-40°C

50

T=125°C

0

0

-50

T=-40°C

-20

-100

Phase

100

-100

Phase

-150

-150

Vcc=4V, Vicm=2V, G=100

Rl=10kΩ , Cl=20pF, VRl=Vcc/2

-40

-200

-200

-250

-250

1

10

100

1000

1

10000

10

100

1000

10000

Frequency (kHz)

Frequency (kHz)

Figure 16. Bode diagram vs. temperature for

VCC = 16 V

Figure 17. Bode diagram at VCC = 16 V with low

common mode voltage

250

40

250

200

Gain

40

200

Gain

T=25°C

150

T=25°C

100

T=125°C

0

0

-50

T=-40°C

-20

-100

Phase

150

T=-40°C

100

50

Gain (dB)

Gain (dB)

50

T=125°C

20

Phase (°)

20

0

0

-50

-20

-100

Phase

-150

Vcc=16V, Vicm=8V, G=100

Rl=10kΩ , Cl=20pF, Vrl=Vcc/2

-40

-150

-200

Vcc=16V, Vicm=0.5V, G=100

Rl=10kΩ , Cl=20pF, VRl=Vcc/2

-40

-250

1

10

100

1000

-200

-250

10000

1

10

Frequency (kHz)

100

1000

10000

Frequency (kHz)

Figure 18. Bode diagram at VCC = 16 V with high

common mode voltage

Figure 19. Bode diagram at VCC = 16 V and

RL = 10 kΩ, CL = 47 pF

250

250

40

40

200

150

150

T=25°C

50

0

-50

-100

Phase

Gain (dB)

T=-40°C

0

-20

T=25°C

100

20

100

Phase (°)

Gain (dB)

T=125°C

200

Gain

Gain

20

50

0

0

T=125°C

T=-40°C

-20

-200

-150

Vcc=16V, Vicm=8V, G=100

Rl=10kΩ , Cl=47pF, VRl=Vcc/2

-40

-200

-250

-250

1

10

100

1000

10000

-50

-100

Phase

-150

Vcc=16V, Vicm=15.5V, G=100

Rl=10kΩ , Cl=20pF, VRl=Vcc/2

-40

Phase (°)

-40

Vcc=10V, Vicm=5V, G=100

Rl=10kΩ, Cl=20pF, VRl=Vcc/2

Phase (°)

-20

Phase (°)

Gain (dB)

50

0

T=25°C

20

100

Gain (dB)

20

Phase (°)

40

40

1

10

100

1000

10000

Frequency (kHz)

Frequency (kHz)

DocID024568 Rev 5

13/32

32

�Electrical characteristics

TSX9291, TSX9292

Figure 20. Bode diagram at VCC = 16 V and

RL = 2 kΩ, CL = 20 pF

Figure 21. Slew rate vs. supply voltage and

temperature

250

40

30

200

Gain

Gain (dB)

50

0

T=-40°C

-50

-20

Slew Rate (V/µs)

100

T=125°C

0

T=25°C

Phase (°)

20

-100

Phase

-40

-200

T=125°C

T=-40°C

10

0

Vicm=VRl=Vcc/2

Rl=10kΩ, Cl=20pF

Vin from 0.5V to Vcc-0.5V

-10

-20

-150

Vcc=16V, Vicm=8V, G=100

Rl=2.2kΩ , Cl=20pF, VRl=Vcc/2

SR positive

20

150

T=25°C

SR negative

-30

-250

1

10

100

1000

4.0 5.0 6.0 7.0 8.0 9.0 10.011.0

10.0

12.013.0

12.0

14.015.016.0

14.0

16.0

Vcc (V)

10000

Frequency (kHz)

Figure 22. Small signal overshoot vs capacitive

load without feedback capacitor Cf

Figure 23. Small step response with G = +2

0.15

80

Overshoot (%)

60

50

0.10

Vcc=16V,

100mVpp,

G=-1; Rf=Rg=1kΩ

Rl=10kΩ

Output Voltage (V)

70

40

30

20

0.05

0.00

-0.05

Vcc = 16V

Rl=10kΩ;Cl=20pF

G=2; Rf=Rg=1kΩ

T=25°C

-0.10

10

0

10

-0.15

-400.0n

100

0.0

Load capacitance (pF)

Figure 24. Small step response with feedback

capacitor

Cf=0pF

2.00

Cf=5pF

Cf=8pF

Output Voltage (V)

Output Voltage (V)

1.2µ

3.00

0.05

Cf=12pF

0.00

-0.05

Vcc = 16V

Rl=10kΩ;Cl=20pF

G=-1; Rf=Rg=1kΩ

T=25°C

-0.10

-0.15

-400.0n

14/32

800.0n

Figure 25. Large step response

0.15

0.10

400.0n

Time (s)

0.0

400.0n

Time (s)

800.0n

1.00

0.00

-1.00

Vcc = 16V

Rl=10kΩ;Cl=20pF

G=-1; Rf=Rg=1kΩ

T=25°C

-2.00

1.2µ

-3.00

-400.0n

DocID024568 Rev 5

0.0

400.0n

Time (s)

800.0n

1.2µ

�TSX9291, TSX9292

Electrical characteristics

Figure 26. Desaturation time

Figure 27. Peaking close loop with different Rl

20

15

1.5

Input Signal

1.0

10

0.5

5

0.0

0

10

-0.5

-5

Gain (dB)

Output signal (V)

Input signal (V)

Rl=10kΩ

Rl=2kΩ

-10

Vcc=4.5V to 16V

Vicm=Vcc/2

Rf=Rg=1kΩ

Gain=-1

Cl=20pF

-20

-10

-1.0

0

Vcc=16V, Vicm=8V, G=11

Rl=10kΩ, Cl=20pF

-1.5

0

2µ

4µ

6µ

8µ

10µ

12µ

14µ

16µ

18µ

-30

-15

20µ

1k

10k

100k

Figure 28. Output impedance vs frequency in

close loop configuration

Output Impedance (Ω )

10

Vcc=16V

Vicm=8V

Osc level=30mVRMS

G=1

Ta=25°C

1

0.1

0.01

100

1k

10k

100k

Frequency (Hz)

1M

600

Vicm=15.5V

400

Vicm=0.5V

300

Vicm=8V

200

100

0

10

100

1k

Frequency (Hz)

10

Vcc=16V

4 Vicm=8V

T=25°C

THD + N (%)

2

0

-2

-1

10

-2

10

-3

Vcc=16V

Vicm=Vcc/2

Vin=2Vrms

Gain=2

BW=80kHz

Rl=600Ω

Rl=2kΩ

-4

10

2

4

6

8

10k

Figure 31. THD+N vs. frequency at VCC = 16 V

6

Input voltage noise (µV)

Vcc=16V

T=25°C

500

10M

Figure 30. 0.1 to 10 Hz noise with 16 V

supply voltage

-6

0

10M

Figure 29. Noise vs. frequency with 16 V

supply voltage

Equivalent Input Voltage Noise (nV/VHz)

1000

100

1M

Frequency (Hz)

Time (s)

Rl=10kΩ

-4

10

Time (s)

DocID024568 Rev 5

100

1k

10k

100k

Frequency (Hz)

15/32

32

�Electrical characteristics

TSX9291, TSX9292

Figure 32. THD+N vs. output voltage at

VCC = 16 V

THD + N (%)

10

0

-120

Vcc=16V

Vicm=Vcc/2

f=1kHz

Gain=2

BW=22kHz

-1

10

-2

10

-3

+PSRR

-100

PSRR (dB)

10

Figure 33. Power supply rejection ratio (PSRR)

vs. frequency

Rl=600Ω

-80

-PSRR

-60

-40

-20

Rl=10kΩ

10

Vcc=16V, Vicm=8V, G=1

Rl=10kΩ, Cl=20pF, Vripple=100mVpp

Rl=2kΩ

-4

0.1

1

0

100

10

1k

10k

100k

Frequency (Hz)

Output Voltage (Vrms)

Figure 34. Crosstalk vs. frequency between operators on TSX9292 at VCC = 16 V

0

-20

Vcc=16V

Vicm=Vcc/2

Rl=10kΩ

Cl=20pF

Vout=3.5Vrms

Crosstalk (dB)

-40

-60

-80

-100

Ch1 to Ch2

-120

-140

Ch2 to Ch1

-160

-180

1k

10k

100k

Frequency (Hz)

16/32

DocID024568 Rev 5

1M

10M

1M

�TSX9291, TSX9292

Application information

4

Application information

4.1

Operating voltages

The TSX929x series of operation amplifiers can operate from 4 V to 16 V. Parameters are

fully specified at 4.5 V, 10 V, and 16 V power supplies. However, parameters are very stable

in the full VCC range. Additionally, the main specifications are guaranteed in the extended

temperature range of -40 to +125 °C.

4.2

Rail-to-rail input

The TSX9291 and TSX9292 are designed with two complementary PMOS and NMOS input

differential pairs. The devices have a rail-to-rail input and the input common mode range is

extended from (VCC-) - 0.1 V to (VCC+) + 0.1 V. However, the performance of these devices

is clearly optimized for the PMOS differential pairs (which means from (VCC-) - 0.1 V to

(VCC+) - 2 V).

Beyond (VCC+) - 2 V, the operational amplifiers are still functional but with downgraded

performances (see Figure 19). Performances are still suitable for a large number of

applications requiring the rail-to-rail input feature.

TSX9291 and TSX9292 are designed to prevent phase reversal.

4.3

Input pin voltage range

The TSX929x series has internal ESD diode protection on the inputs. These diodes are

connected between the input and each supply rail to protect MOSFETs inputs from

electrostatic discharges.

Thus, if the input pin voltage exceeds the power supply by 0.5 V, the ESD diodes become

conductive and excessive current could flow through them. To prevent any permanent

damage, this current must be limited to 10 mA. This can be done by adding a resistor, Rs, in

series with the input pin (Figure 35). The Rs resistor value has to be calculated for a 10 mA

current limitation on the input pins.

Figure 35. Limiting input current with a series resistor

5J

5I

���9

5V

9LQ

�

�

�

�

76;����

9RXW

*$06����������&%

DocID024568 Rev 5

17/32

32

�Application information

4.4

TSX9291, TSX9292

Stability for gain = -1

TSX9291 and TSX9292 can be used in gain = -1 configuration (see Figure 36). However

some precautions must be taken regarding the setting of the Rg and Rf resistors. Effectively,

the input capacitance of the TSX929x series creates a pole with Rf and Rg. In high

frequency, this pole decreases the phase margin and also causes gain peaking. This effect

has a direct impact on the stability.

Figure 37 shows the peaking, depending on the values of the gain and feedback

resistances.

Figure 36. Configuration for gain = -1

Cf

Rf

+Vcc

Rg

Vin

-

Vout

+

CL=20pF

-Vcc

Figure 37. Close loop gain vs. frequency

20

Rf=Rg=20kΩ

10

Gain (dB)

Rf=Rg=1kΩ

0

Rf=Rg=10kΩ

-10

-20

-30

1k

Vcc=16V

Vicm=Vcc/2

Gain=-1

Rl=10kΩ

Cl=20pF

10k

100k

1M

Frequency (Hz)

18/32

DocID024568 Rev 5

10M

RL=10kO

�TSX9291, TSX9292

Application information

Whenever possible, it is best to choose smaller feedback resistors. It is recommended to

use 1 kΩ gain and feedback resistance (Rf and Rg) when gain = -1 is necessary. In the

application, if a large value of Rf and Rg has to be used, a feedback capacitance can be

added in parallel with Rf, to reduce or eliminate the gain peaking. Additionally, Cf helps to

compensate the input capacitance and to increase stability.

Figure 38 shows how Cf reduces the gain peaking.

Figure 38. Close loop gain vs. frequency with capacitive compensation

20

Cf=0pF

10

Gain (dB)

Cf=1pF

0

Cf=1.5pF

-10

-20

Vcc=16V

Vicm=Vcc/2

Gain=-1

Rf=Rg=10kΩ

Rl=10kΩ

Cl=20pF

-30

1k

10k

100k

1M

10M

Frequency (Hz)

4.5

Input offset voltage drift over temperature

The maximum input voltage drift over the temperature variation is defined as the offset

variation related to offset value measured at 25 °C. The operational amplifier is one of the

main circuits of the signal conditioning chain, and the amplifier input offset is a major

contributor to the chain accuracy. The signal chain accuracy at 25 °C can be compensated

during production at application level. The maximum input voltage drift over temperature

enables the system designer to anticipate the effect of temperature variations.

The maximum input voltage drift over temperature is computed using Equation 1.

Equation 1

∆Vio

V io ( T ) – Vio ( 25°C )

------------ = max ------------------------------------------------∆T

T – 25°C

with T = -40 °C and 125 °C.

The datasheet maximum value is guaranteed by a measurement on a representative

sample size ensuring a Cpk (process capability index) greater than 2.

DocID024568 Rev 5

19/32

32

�Application information

4.6

TSX9291, TSX9292

Long-term input offset voltage drift

To evaluate product reliability, two types of stress acceleration are used:

•

Voltage acceleration, by changing the applied voltage

•

Temperature acceleration, by changing the die temperature (below the maximum

junction temperature allowed by the technology) with the ambient temperature.

The voltage acceleration has been defined based on JEDEC results, and is defined using

Equation 2.

Equation 2

A FV = e

β ⋅ ( VS – VU )

Where:

AFV is the voltage acceleration factor

β is the voltage acceleration constant in 1/V, constant technology parameter (β = 1)

VS is the stress voltage used for the accelerated test

VU is the voltage used for the application

The temperature acceleration is driven by the Arrhenius model, and is defined in Equation 3.

Equation 3

AF T = e

Ea 1

1

------ ⋅ ------ – ------

k T U T S

Where:

AFT is the temperature acceleration factor

Ea is the activation energy of the technology based on the failure rate

k is the Boltzmann constant (8.6173 x 10-5 eV.K-1)

TU is the temperature of the die when VU is used (K)

TS is the temperature of the die under temperature stress (K)

The final acceleration factor, AF, is the multiplication of the voltage acceleration factor and

the temperature acceleration factor (Equation 4).

Equation 4

AF = A F T × A FV

AF is calculated using the temperature and voltage defined in the mission profile of the

product. The AF value can then be used in Equation 5 to calculate the number of months of

use equivalent to 1000 hours of reliable stress duration.

20/32

DocID024568 Rev 5

�TSX9291, TSX9292

Application information

Equation 5

Months = A F × 1000 h × 12 months ⁄ ( 24 h × 365.25 days )

To evaluate the op amp reliability, a follower stress condition is used where VCC is defined

as a function of the maximum operating voltage and the absolute maximum rating (as

recommended by JEDEC rules).

The Vio drift (in µV) of the product after 1000 h of stress is tracked with parameters at

different measurement conditions (see Equation 6).

Equation 6

V CC = maxV op with V icm = VCC ⁄ 2

The long-term drift parameter (∆Vio), estimating the reliability performance of the product, is

obtained using the ratio of the Vio (input offset voltage value) drift over the square root of the

calculated number of months (Equation 7).

Equation 7

V io drift

∆V io = -----------------------------( months )

where Vio drift is the measured drift value in the specified test conditions after 1000 h stress

duration.

4.7

Capacitive load

Driving a large capacitive load can cause stability issues. Increasing the load capacitance

produces gain peaking in the frequency response, with overshooting and ringing in the step

response. It is usually considered that with a gain peaking higher than 2.3 dB the op amp

might become unstable. Generally, the unity gain configuration is the worst configuration for

stability and the ability to drive large capacitive loads. Figure 39 shows the serial resistor

(Riso) that must be added to the output, to make the system stable. Figure 40 shows the

test configuration for Riso.

DocID024568 Rev 5

21/32

32

�Application information

TSX9291, TSX9292

Figure 39. Stability criteria with a serial resistor

Vcc=16V, Vicm=8V, T=25°C, Rl=10 kΩ

G=-1, Rf=Rg=1kΩ

100

Serial Resistor (Ohm)

Stable

Unstable

10

0.01

0.1

1

10

Capacitive Load (nF)

Figure 40. Test configuration for Riso

5I

9,1

5J

���9

5LVR

�

�

���9

&ORDG

���N

*$06����������&%

22/32

DocID024568 Rev 5

100

�TSX9291, TSX9292

4.8

Application information

High side current sensing

TSX9291 and TSX9292 rail to rail input devices can be used to measure a small differential

voltage on a high side shunt resistor and translate it into a ground referenced output voltage.

The gain is fixed by external resistance.

Figure 41. High side current sensing configuration

&�

ORDG

5J�

,

5I�

,Q

5VKXQW

5J�

���9

,S

���9

� �

� �

9287

76;����

5I�

*$06����������&%

VOUT can be expressed as shown in Equation 8.

Equation 8

R g2

R f1

Rg2 R f2

R f1

R f1

V out = R shunt × I 1 – ------------------------- 1 + ---------- + Ip ------------------------- × 1 + ---------- – I n xR f1 – Vio 1 + ----------

R g2 + R f2

R g1

R g2 + R f2

R g1

Rg1

Assuming that Rf2 = Rf1 = Rf and Rg2 = Rg1 = Rg, Equation 8 can be simplified as

Equation 9.

Equation 9

Rf

Rf

Vout = R shunt × I ------- – V io 1 + ------- + R f × I io

Rg

R g

With the TSX929x series, the high side current measurement must be made by respecting

the common mode voltage of the amplifier: (VCC-) - 0.1V to (VCC+) + 0.1V. If the application

requires a higher common voltage, please refer to the TSC high side current sensing family.

DocID024568 Rev 5

23/32

32

�Application information

4.9

TSX9291, TSX9292

High speed photodiode

The TSX929x series is an excellent choice for current to voltage (I-V) conversions. Due to

the CMOS technology, the input bias currents are extremely low. Moreover, the low noise

and high unity-gain bandwidth of TSX9291 TSX9292 make them particularly suitable for

high-speed photodiode preamplifier applications.

The photodiode is considered as a capacitive current source. The input capacitance, CIN,

includes the parasitic input common mode capacitance, CCM (3pF), and the input differential

mode capacitance, CDIFF (8pF). CIN acts in parallel with the intrinsic capacitance of the

photodiode, CD. At higher frequencies, the capacitors affect the circuit response. The output

capacitance of a current sensor has a strong effect on the stability of the op amp feedback

loop.

CF stabilizes the gain and limits the transimpedance bandwidth. To ensure good stability

and to obtain good noise performance, CF can be set as shown in Equation 10.

Equation 10

C IN + C D

C F > ------------------------------------------ – C SMR

2 ⋅ π ⋅ R F ⋅ F GBP

where,

• CIN = CCM + CDIFF = 11 pF

• CDIFF is the differential input capacitance: 8 pF typical

• CCM is the Common mode input capacitance: 3 pF typical

• CD is the intrinsic capacitance of the photodiode

• CSMR is the parasitic capacitance of the surface mount RF resistor: 0.2 pF typical

• FGBP is the gain bandwidth product: 10 MHz at 16 V

RF fixes the gain as shown in Equation 11.

Equation 11

V OUT = R F × I D

Figure 42. High speed photodiode

&)

5)

�9&&

1IPUPEJPEF

*%

&'

�

&LQ

9287

�

�9&&

*$06����������&%

24/32

DocID024568 Rev 5

�TSX9291, TSX9292

5

Package information

Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK packages, depending on their level of environmental compliance. ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK is an ST trademark.

DocID024568 Rev 5

25/32

32

�Package information

5.1

TSX9291, TSX9292

SOT23-5 package mechanical data

Figure 43. SOT23-5 package mechanical drawing

Table 7. SOT23-5 package mechanical data

Dimensions

Ref.

A

Millimeters

Min.

Typ.

Max.

Min.

Typ.

Max.

0.90

1.20

1.45

0.035

0.047

0.057

A1

26/32

Inches

0.15

0.006

A2

0.90

1.05

1.30

0.035

0.041

0.051

B

0.35

0.40

0.50

0.013

0.015

0.019

C

0.09

0.15

0.20

0.003

0.006

0.008

D

2.80

2.90

3.00

0.110

0.114

0.118

D1

1.90

0.075

e

0.95

0.037

E

2.60

2.80

3.00

0.102

0.110

0.118

F

1.50

1.60

1.75

0.059

0.063

0.069

L

0.10

0.35

0.60

0.004

0.013

0.023

K

0°

10 °

0°

DocID024568 Rev 5

10 °

�TSX9291, TSX9292

DFN8 2x2 package information

Figure 44. DFN8 2x2 package mechanical drawing

'

$

%

���� & �[

(

3,1���,1'(;�$5($

���� & �[

723�9,(:

$�

���� &

$

&

6($7,1*

3/$1(

6,'(�9,(:

���� &

H

E����SOFV�

3,1���,1'(;�$5($

�

����

�

& $ %

3LQ���,'

/

5.2

Package information

�

�

%27720�9,(:

*$06����������&%

Table 8. DFN8 2x2 package mechanical data

Dimensions

Ref.

Millimeters

Inches

Min.

Typ.

Max.

Min.

Typ.

Max.

A

0.70

0.75

0.80

0.028

0.030

0.031

A1

0.00

0.02

0.05

0.000

0.001

0.002

b

0.15

0.20

0.25

0.006

0.008

0.010

D

2.00

0.079

E

2.00

0.079

e

0.50

0.020

L

0.045

0.55

0.65

N

0.018

0.022

0.026

8

DocID024568 Rev 5

27/32

32

�Package information

5.3

TSX9291, TSX9292

MiniSO8 package information

Figure 45. MiniSO8 package mechanical drawing

Table 9.

MiniSO8 package mechanical data

Dimensions

Ref.

Millimeters

Min.

Typ.

A

Max.

Min.

Typ.

1.1

A1

0

A2

0.75

b

Max.

0.043

0.15

0

0.95

0.030

0.22

0.40

0.009

0.016

c

0.08

0.23

0.003

0.009

D

2.80

3.00

3.20

0.11

0.118

0.126

E

4.65

4.90

5.15

0.183

0.193

0.203

E1

2.80

3.00

3.10

0.11

0.118

0.122

e

L

0.85

0.65

0.40

0.60

0.006

0.033

0.80

0.016

0.024

0.95

0.037

L2

0.25

0.010

ccc

0°

0.037

0.026

L1

k

28/32

Inches

8°

0.10

DocID024568 Rev 5

0°

0.031

8°

0.004

�TSX9291, TSX9292

5.4

Package information

SO8 package information

Figure 46. SO8 package mechanical drawing

Table 10.

SO8 package mechanical data

Dimensions

Ref.

Millimeters

Min.

Typ.

A

Inches

Max.

Min.

Typ.

1.75

0.069

A1

0.10

A2

1.25

b

0.28

0.48

0.011

0.019

c

0.17

0.23

0.007

0.010

D

4.80

4.90

5.00

0.189

0.193

0.197

E

5.80

6.00

6.20

0.228

0.236

0.244

E1

3.80

3.90

4.00

0.150

0.154

0.157

e

0.25

Max.

0.004

0.010

0.049

1.27

0.050

h

0.25

0.50

0.010

0.020

L

0.40

1.27

0.016

0.050

L1

k

ccc

1.04

0°

0.040

8°

0.10

DocID024568 Rev 5

1°

8°

0.004

29/32

32

�Ordering information

6

TSX9291, TSX9292

Ordering information

Table 11. Order codes

Order code

Temperature

range

TSX9291ILT

TSX9292IST

TSX9292IDT

TSX9292IYDT (1)

Packing

Marking

K28

SOT23-5

TSX9291IYLT (1)

TSX9292IQ2T

Package

-40° C to +125° C

DFN8 2x2

MiniSO8

SO8

K308

Tape and reel

K28

TSX9292I

SX9292IY

1. Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening

according to AEC Q001 & Q 002 or equivalent.

30/32

DocID024568 Rev 5

�TSX9291, TSX9292

7

Revision history

Revision history

Table 12. Document revision history

Date

Revision

24-Apr-2013

1

Initial release

2

Added the dual version op amp (TSX9292) and updated

the datasheet accordingly.

Added the silhouettes, pin connections, and package

information for DFN8 2x2, MiniSO8, and SO8; updated

Table 2.

Added Figure 34.

3

Added long-term input offset voltage drift parameter in

Table 4, Table 5, and Table 6.

Added Section 4.5: Input offset voltage drift over

temperature in Section 4: Application information.

Added Section 4.6: Long-term input offset voltage drift in

Section 4: Application information.

Corrected Figure 15: Bode diagram vs. temperature for

VCC = 10 V.

28-Apr-2014

4

Table 4, Table 5, and Table 6: updated phase margin

condition for the gain parameter.

Section 4.3: Input pin voltage range: added information

concerning an Rs resistor; updated Figure 35.

Table 11: updated marking of order codes TSX9291IYLT

and TSX9291IQ2T.

04-Aug-2022

5

Updated marking column in Table 11.

01-Jul-2013

10-Dec-2013

Changes

DocID024568 Rev 5

31/32

32

�TSX9291, TSX9292

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and

improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on

ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order

acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or

the design of Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other

product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

32/32

DocID024568 Rev 5

�