8 Bit Microcontroller

870C Series

TMP86FS49FG

�TMP86FS49FG

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third

parties which may result from its use. No license is granted by implication or otherwise under any

patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless,

semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and

vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards

of safety in making a safe design for the entire system, and to avoid situations in which a malfunction

or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to

property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating

ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for

Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc..

The Toshiba products listed in this document are intended for usage in general electronics applications

( computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic

appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires

extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of

human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control

instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments,

combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended

Usage of Toshiba products listed in this document shall be made at the customer’s own risk.

The products described in this document may include products subject to the foreign exchange and

foreign trade laws.

TOSHIBA products should not be embedded to the downstream products which are prohibited to be

produced and sold, under any law and regulations.

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3

of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

© 2004 TOSHIBA CORPORATION

All Rights Reserved

Page 2

�TMP86FS49FG

TENTATIVE

CMOS 8-Bit Microcontroller

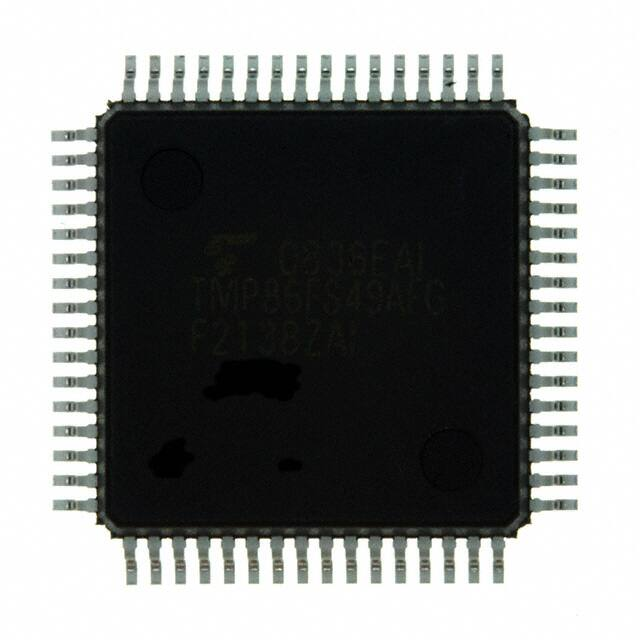

TMP86FS49FG

Product No.

FLASH

RAM

PACKAGE

Mask MCU

TMP86FS49FG

60K bytes

2K bytes

P-QFP64-1414-0.80A

TMP86CH49/CM49

1.1 Features

1. 8-bit single chip microcomputer TLCS-870/C series

- Instruction execution time :

0.25 µs (at 16 MHz)

122 µs (at 32.768 kHz)

- 132 types & 731 basic instructions

2. 24interrupt sources (External : 5 Internal : 19)

3. Input / Output ports (56pins)

4. Time Base Timer

5. Watchdog Timer

6. 16-bit timer counter: 1 ch

- Timer, External trigger, Window, Pulse width measurement, Event counter, PPG(Programmable Pulse

Generator) output modes

7. 16-bit timer counter : 1ch

- Timer, Event counter, Window modes

8. 8-bit timer counter : 4ch

Timer, Event counter, PWM(Pulse width modulation) output, PDO(Programmable Divider Output) output and PPG(Programmable Pulse Generator) modes

9. 8-bit UART: 2ch

10. High-Speed SIO: 2ch

11. Serial Bus Interface(I2C Bus): 1ch

This product uses the Super Flash technology under the licence of Sillicon Storage Technology,Inc. Super Flash is registered

trademark of Sillicon Storage Technology,Inc.

Purchase of TOSHIBA I2C components conveys a license under the Philips I2C Patent Rights to use these components in an

I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

030619EBP1

• The information contained herein is subject to change without notice.

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by

TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can

malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when

utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations

in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most

recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for

Semiconductor Devices,”or “TOSHIBA Semiconductor Reliability Handbook”etc..

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither

intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of

which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical

instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the

customer’s own risk.

• The products described in this document are subject to the foreign exchange and foreign trade laws.

• TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law

and regulations.

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and

Reliability Assurance/Handling Precautions.

Page 1

�1.1 Features

TENTATIVE

TMP86FS49FG

12. 10-bit successive approximation type AD converter

Analog inputs: 16ch

13. Key On Wake Up : 4ch

14. Clock operation

Single clock mode

Dual clock mode

15. Low power consumption operation

STOP mode: Oscillation stops. (Battery/Capacitor back-up.)

SLOW1 mode: Low power consumption operation using low-frequency clock.(High-frequency clock

stop.)

SLOW2 mode: Low power consumption operation using low-frequency clock.(High-frequency clock

oscillate.)

IDLE0 mode: CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using high frequency clock. Release by falling edge of the source clock which is set by TBTCR.

IDLE1 mode: CPU stops and peripherals operate using high frequency clock. Release by interruputs(CPU restarts).

IDLE2 mode: CPU stops and peripherals operate using high and low frequency clock. Release by interruputs. (CPU restarts).

SLEEP0 mode: CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using low frequency clock.Release by falling edge of the source clock which is set by TBTCR.

SLEEP1 mode: CPU stops, and peripherals operate using low frequency clock. Release by interruput.(CPU restarts).

SLEEP2 mode: CPU stops and peripherals operate using high and low frequency clock.

interruput.

16. Wide operation voltage:

4.5 V~5.5 V at 16.0MHz /32.768 kHz

3.0 V~3.6 V at 8 MHz /32.768 kHz

Page 2

Release by

�TMP86FS49FG

TENTATIVE

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

RESET

(STOP/INT5) P20

(INT0) P00

(BOOT/RxD1) P01

(TxD1) P02

(INT1) P03

(SI1) P04

(SO1) P05

(SCK1) P06

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

VSS

XIN

XOUT

TEST

VDD

(XTIN) P21

(XTOUT) P22

(INT3/TC2) P15

(PDO5/PWM5/TC5) P16

(PDO6/PWM6/PPG6/TC6) P17

(SCL) P50

(SDA) P51

P52

P53

P54

P30

P31

P32

P33

P34

P35

P36

P37

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P14 (TC4/PDO4/PWM4/PPG4)

P13 (TC3/PDO3/PWM3)

P12 (PPG)

P11 (DVO)

P10 (TC1)

P47

P46 (SCK2)

P45 (SO2)

P44 (SI2)

P43

P42 (TxD2)

P41 (RxD2)

P40

P77 (AIN17)

P76 (AIN16)

P75 (AIN15)

1.2 Pin Assignment

Figure 1-1 Pin Assignment

Page 3

P74(AIN14)

P73(AIN13)

P72(AIN12)

P71(AIN11)

P70(AIN10)

P67(AIN07/STOP3)

P66(AIN06/STOP2)

P65(AIN05/STOP1)

P64(AIN04/STOP0)

P63(AIN03)

P62(AIN02)

P61(AIN01)

P60(AIN00)

AVDD

VAREF

P07(INT2)

�1.3 Block Diagram

TENTATIVE

1.3 Block Diagram

Figure 1-2 Block Diagram

Page 4

TMP86FS49FG

�TMP86FS49FG

TENTATIVE

1.4 Pin Names and Functions

Table 1-1 Pin Names and Functions(1/3)

Pin Name

P07

INT2

Pin Number

Input/Output

Functions

17

IO

I

PORT07

External interrupt 2 input

16

IO

IO

PORT06

Serial clock input/output 1

P05

SO1

15

IO

O

PORT05

Serial data output 1

P04

SI1

14

IO

I

PORT04

Serial data input 1

P03

INT1

13

IO

I

PORT03

External interrupt 1 input

P02

TxD1

12

IO

O

PORT02

UART data output 1

P01

RxD1

BOOT

11

IO

I

I

PORT01

UART data input 1

Serial PROM mode control input

10

IO

I

PORT00

External interrupt 0 input

51

IO

I

O

PORT17

Timer counter 6 input

PDO6/PWM6/PPG6 output

50

IO

I

O

PORT16

Timer counter 5 input

PDO5/PWM5 output

49

IO

I

I

PORT15

Timer counter 2 input

External interrupt 3 input

48

IO

I

O

PORT14

Timer counter 4 input

PDO4/PWM4/PPG4 output

47

IO

I

O

PORT13

Timer counter 3 input

PDO3/PWM3 output

46

IO

I

PORT12

PPG Output

45

IO

O

PORT11

Divider output

P10

TC1

44

IO

I

PORT10

Timer counter 1 input

P22

XTOUT

7

IO

O

PORT22

Resonator connecting pins(32.768kHz) for inputting external

clock

P21

XTIN

6

IO

I

PORT21

Resonator connecting pins(32.768kHz) for inputting external

clock

9

IO

I

I

PORT20

External interrupt 5 input

STOP mode release signal input

P06

SCK1

P00

INT0

P17

TC6

PDO6/PWM6/PPG6

P16

TC5

PDO5/PWM5

P15

TC2

INT3

P14

TC4

PDO4/PWM4/PPG4

P13

TC3

PDO3/PWM3

P12

PPG

P11

DVO

P20

INT5

STOP

Page 5

�1.4 Pin Names and Functions

TMP86FS49FG

TENTATIVE

Table 1-1 Pin Names and Functions(2/3)

Pin Name

Pin Number

Input/Output

Functions

P37

64

IO

PORT37

P36

63

IO

PORT36

P35

62

IO

PORT35

P34

61

IO

PORT34

P33

60

IO

PORT33

P32

59

IO

PORT32

P31

58

IO

PORT31

P30

57

IO

PORT30

P47

43

IO

PORT47

42

IO

IO

PORT46

Serial clock input/output 2

P45

SO2

41

IO

O

PORT45

Serial data output 2

P44

SI2

40

IO

I

PORT44

Serial data input 2

P43

39

IO

PORT43

P42

TxD2

38

IO

O

PORT42

UART data output 2

P41

RxD2

37

IO

I

PORT41

UART data input 2

P40

36

IO

PORT40

P54

56

IO

PORT54

P53

55

IO

PORT53

P52

54

IO

PORT52

P51

SDA

53

IO

IO

PORT51

I2C bus serial data input/output

P50

SCL

52

IO

IO

PORT50

I2C bus serial clock input/output

P67

AIN07

STOP3

27

IO

I

I

PORT67

AD converter analog input 7

STOP3 input

P66

AIN06

STOP2

26

IO

I

I

PORT66

AD converter analog input 6

STOP2 input

P65

AIN05

STOP1

25

IO

I

I

PORT65

AD converter analog input 5

STOP1 input

P64

AIN04

STOP0

24

IO

I

I

PORT64

AD converter analog input 4

STOP0 input

P63

AIN03

23

IO

I

PORT63

AD converter analog input 3

P62

AIN02

22

IO

I

PORT62

AD converter analog input 2

P46

SCK2

Page 6

�TMP86FS49FG

TENTATIVE

Table 1-1 Pin Names and Functions(3/3)

Pin Name

Pin Number

Input/Output

Functions

P61

AIN01

21

IO

I

PORT61

AD converter analog input 1

P60

AIN00

20

IO

I

PORT60

AD converter analog input 0

P77

AIN17

35

IO

I

PORT77

AD converter analog input 17

P76

AIN16

34

IO

I

PORT76

AD converter analog input 16

P75

AIN15

33

IO

I

PORT75

AD converter analog input 15

P74

AIN14

32

IO

I

PORT74

AD converter analog input 14

P73

AIN13

31

IO

I

PORT73

AD converter analog input 13

P72

AIN12

30

IO

I

PORT72

AD converter analog input 12

P71

AIN11

29

IO

I

PORT71

AD converter analog input 11

P70

AIN10

28

IO

I

PORT70

AD converter analog input 10

XIN

2

I

Resonator connecting pins for high-frequency clock

XOUT

3

O

Resonator connecting pins for high-frequency clock

RESET

8

I

Reset signal input

TEST

4

I

Test pin for out-going test and the Serial PROM mode control

pin. Usually fix to low level. Fix to high level when the Serial

PROM mode starts.

VAREF

18

I

Analog reference voltage input (High)

AVDD

19

I

AD circuit power supply

VDD

5

I

+5V

VSS

1

I

0(GND)

Page 7

�1.4 Pin Names and Functions

TENTATIVE

Page 8

TMP86FS49FG

�TENTATIVE

TMP86FS49FG

2. Operational Description

2.1 CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, and the reset circuit.

2.1.1

Memory Address Map

The TMP86FS49FG memory consists of 4 blocks: FLASH, RAM, DBR (Data buffer register) and SFR

(Special function register). They are all mapped in 64-Kbyte address space. Figure 2-1 shows the

TMP86FS49FG memory address map. The general-purpose registers are not assigned to the RAM address

space.

0000H

SFR

64 byte

003FH

0040H

2Kbyte

RAM

FLASH: includes;

083FH

RAM:

0F80H

SFR:

128byte

DBR

0FFFH

DBR:

Program memory

Vector table

Random access memory includes:

Data memory

Stack

Special function register includes:

I/O ports

Peripheral control registers

Peripheral status registers

System control registers

Program status word

Databuffer register includes:

Peripheral status registers

1000H

60Kbyte

FLASH

FFA0H

FFFFH

Figure 2-1 Memory Address Map

Page 9

�2. Operational Description

2.2 System Clock Controller

2.1.2

TMP86FS49FG

TENTATIVE

Program Memory (FLASH)

The TMP86FS49FG has a 60K × 8 bits (Address 1000H to FFFFH) of program memory (FLASH ). A program code placed on the internal RAM can be excutable when a certain procedure is executed ( See "2.3.2

Address trap reset ").

2.1.3

Data Memory (RAM)

Data memory consists of internal data memory (Internal FLASH or RAM). The TMP86FS49FG has 2Kbyte

(Address 0040H to 083FH) of internal RAM. The first 192 bytes (0040H to 00FFH) of the internal RAM are

located in the direct area; instructions with shorten operations are available against such an area.

The data memory contents become unstable when the power supply is turned on; therefore, the data memory

should be initialized by an initialization routine.

Example :Clears RAM to “00H”. (TMP86FS49FG)

SRAMCLR:

LD

HL, 0040H

; Start address setup

LD

A, H

; Initial value (00H) setup

;

LD

BC, 07FFH

LD

(HL), A

INC

HL

DEC

BC

JRS

F, SRAMCLR

2.2 System Clock Controller

The system clock controller consists of a clock generator, a timing generator, and a standby controller.

Timing generator control register

TBTCR

0036H

Clock

generator

XIN

fc

High-frequency

clock oscillator

Timing

generator

XOUT

Standby controller

0038H

XTIN

Low-frequency

clock oscillator

SYSCR1

fs

System clocks

XTOUT

Clock generator control

Figure 2-2 System Colck Control

Page 10

0039H

SYSCR2

System control registers

�TMP86FS49FG

TENTATIVE

2.2.1

Clock Generator

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core

and peripheral hardware. It contains two oscillation circuits: One for the high-frequency clock and one for the

low-frequency clock. Power consumption can be reduced by switching of the standby controller to low-power

operation based on the low-frequency clock.

The high-frequency (fc) clocks and low-frequency (fs) clock can easily be obtained by connecting a resonator between the XIN/XOUT and XTIN/XTOUT pins respectively. Clock input from an external oscillator is

also possible. In this case, external clock is applied to XIN/XTIN pin with XOUT/XTOUT pin not connected.

Low-frequency clock

High-frequency clock

XIN

XOUT

XIN

XOUT

XTIN

XTOUT

(Open)

(a) Crystal/Ceramic

resonator

XTIN

XTOUT

(Open)

(c) Crystal

(b) External oscillator

(d) External oscillator

Figure 2-3 Examples of Resonator Connection

Note:The function to monitor the basic clock directly at external is not provided for hardware, however, with disabling all interrupts and watchdog timers, the oscillation frequency can be adjusted by monitoring the pulse

which the fixed frequency is outputted to the port by the program.

The system to require the adjustment of the oscillation frequency should create the program for the adjustment in advance.

2.2.2

Timing Generator

The timing generator generates the various system clocks supplied to the CPU core and peripheral hardware

from the basic clock (fc or fs). The timing generator provides the following functions.

1. Generation of main system clock

2. Generation of divider output (DVO) pulses

3. Generation of source clocks for time base timer

4. Generation of source clocks for watchdog timer

5. Generation of internal source clocks for timer/counters

6. Generation of warm-up clocks for releasing STOP mode

2.2.2.1

Configuration of timing generator

The timing generator consists of a 2-stage prescaler, a 21-stage divider, a main system clock generator,

and machine cycle counters.

An input clock to the 7th stage of the divider depends on the operating mode, DV7CK (Bit4 in

TBTCR), that is shown in Figure 1-5. As reset and STOP mode started/canceled, the prescaler and the

divider are cleared to “0”.

Page 11

�2. Operational Description

2.2 System Clock Controller

TMP86FS49FG

TENTATIVE

fc or fs

Main system clock generator

Machine cycle counters

SYSCK

DV7CK

High-frequency

clock fc

1 2

fc/4

S

A

Divider

Y

1 2 3 4 5 6

7 8 9 10 11 12 13 14 15 16 17 18 19 20 21

B

Multiplexer

Low-frequency

clock fs

S

B0

Multiplexer

B1

A0 Y0

A1 Y1

Warm-up

controller

Watchdog

timer

Timer/

counters

Time base

timer

Serial

interface

Divider

output circuit

Figure 2-4 Configuration of Timing Generator

Timing Generator Control Register

TBTCR

(0036H)

7

6

(DVOEN)

DV7CK

5

(DVOCK)

4

3

DV7CK

(TBTEN)

Selection of input to the 7th stage

of the divider

2

1

0

(TBTCK)

(Initial value: 0000 0000)

0: fc/28 [Hz]

1: fs

R/W

Note 1: In single clock mode, do not set DV7CK to “1”.

Note 2: Do not set “1” on DV7CK while the low-frequency clock is not operated stably.

Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], *: Don’t care

Note 4: In SLOW1/2 and SLEEP1/2 modes, the DV7CK setting is ineffective, and fs is input to the 7th stage of the divider.

Note 5: When STOP mode is entered from NORMAL1/2 mode, the DV7CK setting is ineffective during the warm-up period after

release of STOP mode, and the 6th stage of the divider is input to the 7th stage during this period.

2.2.2.2

Machine cycle

Instruction execution and peripheral hardware operation are synchronized with the main system clock.

The minimum instruction execution unit is called an “machine cycle”. There are a total of 10 different

types of instructions for the TLCS-870/C Series: Ranging from 1-cycle instructions which require one

machine cycle for execution to 10-cycle instructions which require 10 machine cycles for execution. A

machine cycle consists of 4 states (S0 to S3), and each state consists of one main system clock.

Page 12

�TMP86FS49FG

TENTATIVE

1/fc or 1/fs [s]

Main system clock

(fm)

State

S0

S1

S2

S3

S0

S1

S2

S3

Machine cycle

Figure 2-5 Machine Cycle

2.2.3

Operation Mode Control Circuit

The operation mode control circuit starts and stops the oscillation circuits for the high-frequency and lowfrequency clocks, and switches the main system clock. There are two operating modes: Single clock and dual

clock. These modes are controlled by the system control registers (SYSCR1 and SYSCR2).

Figure 2-6 shows the operating mode transition diagram.

2.2.3.1

Single-clock mode

Only the oscillation circuit for the high-frequency clock is used, and P21 (XTIN) and P22 (XTOUT)

pins are used as input/output ports. The main-system clock is obtained from the high-frequency clock. In

the single-clock mode, the machine cycle time is 4/fc [s].

(1)

NORMAL1 mode

In this mode, both the CPU core and on-chip peripherals operate using the high-frequency clock.

The TMP86FS49FG is placed in this mode after reset.

(2)

IDLE1 mode

In this mode, the internal oscillation circuit remains active. The CPU and the watchdog timer are

halted; however on-chip peripherals remain active (Operate using the high-frequency clock).

IDLE1 mode is started by SYSCR2, and IDLE1 mode is released to NORMAL1 mode by

an interrupt request from the on-chip peripherals or external interrupt inputs. When the IMF (Interrupt master enable flag) is “1” (Interrupt enable), the execution will resume with the acceptance of

the interrupt, and the operation will return to normal after the interrupt service is completed. When

the IMF is “0” (Interrupt disable), the execution will resume with the instruction which follows the

IDLE1 mode start instruction.

(3)

IDLE0 mode

In this mode, all the circuit, except oscillator and the timer-base-timer, stops operation.

This mode is enabled by setting “1” on bit TGHALT on the system control register 2 (SYSCR2).

When IDLE0 mode starts, the CPU stops and the timing generator stops feeding the clock to the

peripheral circuits other than TBT. Then, upon detecting the falling edge of the source clock selected

with TBTCR, the timing generator starts feeding the clock to all peripheral circuits.

Page 13

�2. Operational Description

2.2 System Clock Controller

TENTATIVE

TMP86FS49FG

When returned from IDLE0 mode, the CPU restarts operating, entering NORMAL1 mode back

again. IDLE0 mode is entered and returned regardless of how TBTCR is set. When IMF =

“1”, EF6 (TBT interrupt individual enable flag) = “1”, and TBTCR = “1”, interrupt processing is performed. When IDLE0 mode is entered while TBTCR = “1”, the INTTBT

interrupt latch is set after returning to NORMAL1 mode.

2.2.3.2

Dual-clock mode

Both the high-frequency and low-frequency oscillation circuits are used in this mode. P21 (XTIN) and

P22 (XTOUT) pins cannot be used as input/output ports. The main system clock is obtained from the

high-frequency clock in NORMAL2 and IDLE2 modes, and is obtained from the low-frequency clock in

SLOW and SLEEP modes. The machine cycle time is 4/fc [s] in the NORMAL2 and IDLE2 modes, and

4/fs [s] (122 ms at fs = 32.768 kHz) in the SLOW and SLEEP modes.

The TLCS-870/C is placed in the signal-clock mode during reset. To use the dual-clock mode, the lowfrequency oscillator should be turned on at the start of a program.

(1)

NORMAL2 mode

In this mode, the CPU core operates with the high-frequency clock. On-chip peripherals operate

using the high-frequency clock and/or low-frequency clock.

(2)

SLOW2 mode

In this mode, the CPU core operates with the low-frequency clock, while both the high-frequency

clock and the low-frequency clock are operated. On-chip peripherals are triggered by the low-frequency clock. As the SYSCK on SYSCR2 becomes “0”, the hardware changes into NORMAL2

mode. As the XEN on SYSCR2 becomes “0”, the hardware changes into SLOW1 mode. Do not clear

XTEN to “0” during SLOW2 mode.

(3)

SLOW1 mode

This mode can be used to reduce power-consumption by turning off oscillation of the high-frequency clock. The CPU core and on-chip peripherals operate using the low-frequency clock.

Switching back and forth between SLOW1 and SLOW2 modes are performed by XEN bit on the

system control register 2 (SYSCR2). In SLOW1 and SLEEP modes, the input clock to the 1st stage

of the divider is stopped; output from the 1st to 6th stages is also stopped.

(4)

IDLE2 mode

In this mode, the internal oscillation circuit remain active. The CPU and the watchdog timer are

halted; however, on-chip peripherals remain active (Operate using the high-frequency clock and/or

the low-frequency clock). Starting and releasing of IDLE2 mode are the same as for IDLE1 mode,

except that operation returns to NORMAL2 mode.

(5)

SLEEP1 mode

In this mode, the internal oscillation circuit of the low-frequency clock remains active. The CPU,

the watchdog timer, and the internal oscillation circuit of the high-frequency clock are halted; however, on-chip peripherals remain active (Operate using the low-frequency clock). Starting and releasing of SLEEP mode are the same as for IDLE1 mode, except that operation returns to SLOW mode.

In SLOW and SLEEP modes, the input clock to the 1st stage of the divider is stopped; output from

the 1st to 6th stages is also stopped.

Page 14

�TMP86FS49FG

TENTATIVE

(6)

SLEEP2 mode

The SLEEP2 mode is the idle mode corresponding to the SLOW2 mode. The status under the

SLEEP2 mode is same as that under the SLEEP1 mode, except for the oscillation circuit of the highfrequency clock.

(7)

SLEEP0 mode

In this mode, all the circuit, except oscillator and the timer-base-timer, stops operation. This mode

is enabled by setting “1” on bit TGHALT on the system control register 2 (SYSCR2).

When SLEEP0 mode starts, the CPU stops and the timing generator stops feeding the clock to the

peripheral circuits other than TBT. Then, upon detecting the falling edge of the source clock selected

with TBTCR, the timing generator starts feeding the clock to all peripheral circuits.

When returned from SLEEP0 mode, the CPU restarts operating, entering SLOW1 mode back

again. SLEEP0 mode is entered and returned regardless of how TBTCR is set. When IMF

= “1”, EF6 (TBT interrupt individual enable flag) = “1”, and TBTCR = “1”, interrupt processing is performed. When SLEEP0 mode is entered while TBTCR = “1”, the INTTBT

interrupt latch is set after returning to SLOW1 mode.

2.2.3.3

STOP mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted. The

internal status immediately prior to the halt is held with a lowest power consumption during STOP mode.

STOP mode is started by the system control register 1 (SYSCR1), and STOP mode is released by a

inputting (Either level-sensitive or edge-sensitive can be programmably selected) to the STOP pin. After

the warm-up period is completed, the execution resumes with the instruction which follows the STOP

mode start instruction.

IDLE0

mode

IDLE1

mode

(a) Single-clock mode

Reset release

Note 2

SYSCR2 = "1"

SYSCR1 = "1"

SYSCR2 = "1"

NORMAL1

mode

Interrupt

STOP pin input

SYSCR2 = "0"

SYSCR2 = "1"

SYSCR2 = "1"

IDLE2

mode

RESET

SYSCR1 = "1"

NORMAL2

mode

Interrupt

STOP pin input

SYSCR2 = "0"

SYSCR2 = "1"

STOP

SYSCR2 = "1"

SLEEP2

mode

SLOW2

mode

Interrupt

SYSCR2 = "0"

SYSCR2 = "1"

SYSCR2 = "1"

SLEEP1

mode

(b) Dual-clock mode

SYSCR1 = "1"

SLOW1

mode

Interrupt

STOP pin input

SYSCR2 = "1"

Note 2

SLEEP0

mode

Note 1: NORMAL1 and NORMAL2 modes are generically called NORMAL; SLOW1 and SLOW2 are called SLOW; IDLE0, IDLE1

and IDLE2 are called IDLE; SLEEP0, SLEEP1 and SLEEP2 are called SLEEP.

Page 15

�2. Operational Description

2.2 System Clock Controller

TMP86FS49FG

TENTATIVE

Note 2: The mode is released by falling edge of TBTCR setting.

Figure 2-6 Operating Mode Transition Diagram

Oscillator

Operating Mode

High

Frequency

Low

Frequency

CPU Core

TBT

Other

Peripherals

Reset

Reset

Reset

RESET

NORMAL1

Single clock

IDLE1

Operate

Oscillation

Stop

Operate

IDLE0

Halt

STOP

Stop

–

Operate with

high frequency

4/fc [s]

Halt

Oscillation

Operate with

low frequency

SLOW2

Dual clock

4/fc [s]

Operate

Halt

Halt

NORMAL2

IDLE2

Machine Cycle

Time

Oscillation

SLEEP2

Operate

Halt

Operate

4/fs [s]

Operate with

low frequency

SLOW1

SLEEP1

Stop

SLEEP0

Halt

STOP

Stop

Halt

Halt

–

System Control Register 1

SYSCR1

(0038H)

7

6

5

4

STOP

RELM

RETM

OUTEN

3

2

1

0

WUT

(Initial value: 0000 00**)

STOP

STOP mode start

0: CPU core and peripherals remain active

1: CPU core and peripherals are halted (Start STOP mode)

RELM

Release method for STOP

mode

0: Edge-sensitive release

1: Level-sensitive release

RETM

Operating mode after STOP

mode

0: Return to NORMAL1/2 mode

1: Return to SLOW1 mode

Port output during STOP mode

0: High impedance

1: Output kept

OUTEN

R/W

Return to NORMAL mode

00

WUT

Warm-up time at releasing

STOP mode

3×

Return to SLOW mode

216/fc

3 × 213/fs

01

216/fc

213/fs

10

3 × 214/fc

3 × 26/fs

11

214/fc

26/fs

Note 1: Always set RETM to “0” when transiting from NORMAL mode to STOP mode. Always set RETM to “1” when transiting

from SLOW mode to STOP mode.

Note 2: When STOP mode is released with RESET pin input, a return is made to NORMAL1 regardless of the RETM contents.

Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], *; Don’t care

Note 4: Bits 1 and 0 in SYSCR1 are read as undefined data when a read instruction is executed.

Note 5: As the hardware becomes STOP mode under OUTEN = “0”, input value is fixed to “0”; therefore it may cause interrupt

request on account of falling edge.

Note 6: When the key-on wakeup is used, the edge realease can not function according to some conditions. It is recommended to

set the level realease (RELM = “1”).

Note 7: Port P20 is used as STOP pin. Therefore, when stop mode is started, OUTEN does not affect to P20, and P20 becomes

High-Z mode.

Note 8: The warmig-up time should be set correctly for using oscillator.

Page 16

�TMP86FS49FG

TENTATIVE

System Control Register 2

SYSCR2

(0039H)

7

6

5

4

XEN

XTEN

SYSCK

IDLE

3

2

1

TGHALT

0

(Initial value: 1000 *0**)

XEN

High-frequency oscillator control

0: Turn off oscillation

1: Turn on oscillation

XTEN

Low-frequency oscillator control

0: Turn off oscillation

1: Turn on oscillation

SYSCK

Main system clock select

(Write)/main system clock monitor (Read)

0: High-frequency clock

1: Low-frequency clock

IDLE

CPU and watchdog timer control

(IDLE1/2 and SLEEP1/2 modes)

0: CPU and watchdog timer remain active

1: CPU and watchdog timer are stopped (Start IDLE1/2 and SLEEP1/2 modes)

TGHALT

TG control (IDLE0 and SLEEP0

modes)

0: Feeding clock to all peripherals from TG

1: Stop feeding clock to peripherals except TBT from TG.

(Start IDLE0 and SLEEP0 modes)

R/W

Note 1: A reset is applied if both XEN and XTEN are cleared to “0”, XEN is cleared to “0” when SYSCK = “0”, or XTEN is cleared

to “0” when SYSCK = “1”.

Note 2: *: Don’t care, TG: Timing generator

Note 3: Bits 3, 1 and 0 in SYSCR2 are always read as undefined value.

Note 4: Do not set IDLE and TGHALT to “1” simultaneously.

Note 5: Because returning from IDLE0/SLEEP0 to NORMAL1/SLOW1 is executed by the asynchronous internal clock, the period

of IDLE0/SLEEP0 mode might be shorter than the period setting by TBTCR.

Note 6: When IDLE1/2 or SLEEP1/2 mode is released, IDLE is automatically cleared to “0”.

Note 7: When IDLE0 or SLEEP0 mode is released, TGHALT is automatically cleared to “0”.

Note 8: Before setting TGHALT to “1”, be sure to stop peripherals. If peripherals are not stopped, the interrupt latch of peripherals

may be set after IDLE0 or SLEEP0 mode is released.

2.2.4

Operating Mode Control

2.2.4.1

STOP mode

STOP mode is controlled by the system control register 1, the STOP pin input .

The STOP pin is also used both as a port P20 and an INT5 (external interrupt input 5) pin.

STOP mode is started by setting STOP (Bit7 in SYSCR1) to “1”. During STOP mode, the following

status is maintained.

1. Oscillations are turned off, and all internal operations are halted.

2. The data memory, registers, the program status word and port output latches are all held in the

status in effect before STOP mode was entered.

3. The prescaler and the divider of the timing generator are cleared to “0”.

4. The program counter holds the address 2 ahead of the instruction (e.g., [SET (SYSCR1).7])

which started STOP mode.

STOP mode includes a level-sensitive mode and an edge-sensitive mode, either of which can be

selected with the RELM (Bit6 in SYSCR1).

Note 1: During STOP period (from start of STOP mode to end of warm up), due to changes in the external

interrupt pin signal, interrupt latches may be set to “1” and interrupts may be accepted immediately

after STOP mode is released. Before starting STOP mode, therefore, disable interrupts. Also, before

enabling interrupts after STOP mode is released, clear unnecessary interrupt latches.

(1)

Level-sensitive release mode (RELM = “1”)

In this mode, STOP mode is released by setting the STOP pin high. This mode is used for capacitor

backup when the main power supply is cut off and long term battery backup.

Page 17

�2. Operational Description

2.2 System Clock Controller

TMP86FS49FG

TENTATIVE

When the STOP pin input is high, executing an instruction which starts STOP mode will not place

in STOP mode but instead will immediately start the release sequence (Warm up). Thus, to start

STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that

the STOP pin input is low. The following two methods can be used for confirmation.

1. Testing a port P20.

2. Using an external interrupt input INT5 (INT5 is a falling edge-sensitive input).

Example 1 :Starting STOP mode from NORMAL mode by testing a port P20.

SSTOPH:

LD

(SYSCR1), 01010000B

; Sets up the level-sensitive release mode

TEST

(P2PRD). 0

; Wait until the STOP pin input goes low level

JRS

F, SSTOPH

; IMF ← 0

DI

SET

(SYSCR1). 7

; Starts STOP mode

Example 2 :Starting STOP mode from NORMAL mode with an INT5 interrupt.

PINT5:

TEST

(P2PRD). 0

JRS

F, SINT5

; To reject noise, STOP mode does not start if

LD

(SYSCR1), 01010000B

port P20 is at high

; IMF ← 0

DI

SET

SINT5:

; Sets up the level-sensitive release mode.

(SYSCR1). 7

; Starts STOP mode

RETI

VIH

STOP pin

XOUT pin

NORMAL

operation

STOP

operation

Warm up

Confirm by program that the

STOP pin input is low and start

STOP mode.

NORMAL

operation

STOP mode is released by the hardware.

Always released if the STOP

pin input is high.

Figure 2-7 Level-sensitive Release Mode

Note 1: In this case of changing to the level-sensitive mode from the edge-sensitive mode, the release

mode is not switched until a rising edge of the STOP pin input is detected.

(2)

Edge-sensitive release mode (RELM = “0”)

In this mode, STOP mode is released by a rising edge of the STOP pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic

signal (for example, a clock from a low-power consumption oscillator) is input to the STOP pin. In

the edge-sensitive release mode, STOP mode is started even when the STOP pin input is high level.

Example :Starting STOP mode from NORMAL mode

; IMF ← 0

DI

LD

(SYSCR1), 10010000B

Page 18

; Starts after specified to the edge-sensitive release mode

�TMP86FS49FG

TENTATIVE

VIH

STOP pin

XOUT pin

NORMAL

operation

STOP

operation

Warm up

NORMAL

operation

STOP mode started

by the program.

STOP

operation

STOP mode is released by the hardware at the rising

edge of STOP pin input.

Figure 2-8 Edge-sensitive Release Mode

STOP mode is released by the following sequence.

1. In the dual-clock mode, when returning to NORMAL2, both the high-frequency and lowfrequency clock oscillators are turned on; when returning to SLOW1 mode, only the lowfrequency clock oscillator is turned on. In the single-clock mode, only the high-frequency

clock oscillator is turned on.

2. A warm-up period is inserted to allow oscillation time to stabilize. During warm up, all

internal operations remain halted. Four different warm-up times can be selected with the

WUT (Bits 2 and 3 in SYSCR1) in accordance with the resonator characteristics.

3. When the warm-up time has elapsed, normal operation resumes with the instruction following the STOP mode start instruction. The start is made after the prescaler and the divider of

the timing generator are cleared to “0”.

Table 2-1 Warm-up Time Example (at fc = 16.0 MHz, fs = 32.768 kHz)

Warm-up Time [ms]

WUT

Return to NORMAL Mode

Return to SLOW Mode

00

12.288

750

01

4.096

250

10

3.072

5.85

11

1.024

1.95

Note: The warm-up time is obtained by dividing the basic clock by the divider. Therefore, the warm-up

time may include a certain amount of error if there is any fluctuation of the oscillation frequency

when STOP mode is released. Thus, the warm-up time must be considered as an approximate

value.

STOP mode can also be released by inputting low level on the RESET pin, which immediately performs the normal reset operation.

Note: When STOP mode is released with a low hold voltage, the following cautions must be observed.

The power supply voltage must be at the operating voltage level before releasing STOP mode.

The RESET pin input must also be “H” level, rising together with the power supply voltage. In this

case, if an external time constant circuit has been connected, the RESET pin input voltage will

increase at a slower pace than the power supply voltage. At this time, there is a danger that a

reset may occur if input voltage level of the RESET pin drops below the non-inverting high-level

input voltage (Hysteresis input).

Page 19

�Page 20

Figure 2-9 STOP Mode Start/Release

Divider

Instruction

execution

Program

counter

Main

system

clock

Oscillator

circuit

STOP pin

input

Divider

Instruction

execution

Program

counter

Main

system

clock

Oscillator

circuit

0

Halt

Turn off

Turn on

Turn on

n

Count up

a+3

Warm up

a+2

n+2

n+3

n+4

0

(b) STOP mode release

1

Instruction address a + 2

a+4

2

Instruction address a + 3

a+5

(a) STOP mode start (Example: Start with SET (SYSCR1). 7 instruction located at address a)

n+1

SET (SYSCR1). 7

a+3

3

Instruction address a + 4

a+6

0

Halt

Turn off

2.2 System Clock Controller

2. Operational Description

TENTATIVE

TMP86FS49FG

�TMP86FS49FG

TENTATIVE

2.2.4.2

IDLE1/2 mode and SLEEP1/2 mode

IDLE1/2 and SLEEP1/2 modes are controlled by the system control register 2 (SYSCR2) and maskable

interrupts. The following status is maintained during these modes.

1. Operation of the CPU and watchdog timer (WDT) is halted. On-chip peripherals continue to

operate.

2. The data memory, CPU registers, program status word and port output latches are all held in the

status in effect before these modes were entered.

3. The program counter holds the address 2 ahead of the instruction which starts these modes.

Starting IDLE1/2

and SLEEP1/2 modes

by instruction

CPU and WDT are halted

Yes

Reset input

Reset

No

No

Interrupt request

Normal

release mode

No

Yes

IMF = 1

Yes (Interrupt release mode)

Interrupt processing

Execution of the

instruction which follows

the IDLE1/2 and SLEEP1/2

modes start instruction

Figure 2-10 IDLE1/2 and SLEEP1/2 Modes

(1)

Start the IDLE1/2 and SLEEP1/2 modes

When IDLE1/2 and SLEEP1/2 modes start, set SYSCR2 to “1”. After IMF is set to "0",

set the individual interrupt enable flag (EF) which releases IDLE1/2 and SLEEP1/2.

(2)

Release the IDLE1/2 and SLEEP1/2 modes

IDLE1/2 and SLEEP1/2 modes include a normal release mode and an interrupt release mode.

These modes are selected by interrupt master enable flag (IMF). After releasing IDLE1/2 and

SLEEP1/2 modes, the SYSCR2 is automatically cleared to “0” and the operation mode is

returned to the mode preceding IDLE1/2 and SLEEP1/2 modes.

IDLE1/2 and SLEEP1/2 modes can also be released by inputting low level on the RESET pin. After

releasing reset, the operation mode is started from NORMAL1 mode.

Page 21

�2. Operational Description

2.2 System Clock Controller

TENTATIVE

(3)

TMP86FS49FG

Normal release mode (IMF = “0”)

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled by the individual

interrupt enable flag (EF). After the interrupt is generated, the program operation is resumed from the

instruction following the IDLE1/2 and SLEEP1/2 modes start instruction. Normally, the interrupt

latches (IL) of the interrupt source used for releasing must be cleared to “0” by load instructions.

(4)

Interrupt release mode (IMF = “1”)

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled with the individual

interrupt enable flag (EF) and the interrupt processing is started. After the interrupt is processed, the

program operation is resumed from the instruction following the instruction, which starts IDLE1/2

and SLEEP1/2 modes.

Note: When a watchdog timer interrupts is generated immediately before IDLE1/2 and SLEEP1/2 mode

are started, the watchdog timer interrupt will be processed but IDLE1/2 and SLEEP1/2 mode will

not be started.

Page 22

�Page 23

Figure 2-11 IDLE1/2 and SLEEP1/2 Modes Start/Release

Watchdog

timer

Instruction

execution

Program

counter

Interrupt

request

Main

system

clock

Watchdog

timer

Instruction

execution

Program

counter

Interrupt

request

Main

system

clock

Watchdog

timer

Instruction

execution

Program

counter

Interrupt

request

Main

system

clock

Halt

Halt

Halt

Halt

Operate

Operate

Operate

a+4

Acceptance of interrupt

Instruction address a + 2

(b) IDLE1/2 and SLEEP1/2 modes release

Interrupt release mode

a+3

Normal release mode

a+3

(a) IDLE1/2 and SLEEP1/2 modes start (Example: Starting with the SET instruction located at address a)

Operate

SET (SYSCR2). 4

a+2

Halt

a+3

TENTATIVE

TMP86FS49FG

�2. Operational Description

2.2 System Clock Controller

2.2.4.3

TMP86FS49FG

TENTATIVE

IDLE0 and SLEEP0 modes (IDLE0, SLEEP0)

IDLE0 and SLEEP0 modes are controlled by the system control register 2 (SYSCR2) and the time base

timer control register (TBTCR). The following status is maintained during IDLE0 and SLEEP0 modes.

1. Timing generator stops feeding clock to peripherals except TBT.

2. The data memory, CPU registers, program status word and port output latches are all held in the

status in effect before IDLE0 and SLEEP0 modes were entered.

3. The program counter holds the address 2 ahead of the instruction which starts IDLE0 and

SLEEP0 modes.

Note: Before starting IDLE0 or SLEEP0 mode, be sure to stop (Disable) peripherals.

Stopping peripherals

by instruction

Starting IDLE0 and SLEEP0

modes by instruction

CPU and WDT are halted

Reset input

Yes

Reset

No

No

TBT

source clock

falling

edge

Yes

No

TBTCR

= "1"

Yes

No

TBT interrupt

enable

Yes

(Normal release mode)

No

IMF = "1"

Yes (Interrupt release mode)

Interrupt processing

Execution of the

instruction which follows

the IDLE0 and SLEEP0

modes start instruction

Figure 2-12 IDLE0 and SLEEP0 Modes

(1)

Start the IDLE0 and SLEEP0 modes

Stop (Disable) peripherals such as a timer counter.

Page 24

�TENTATIVE

TMP86FS49FG

When IDLE0 and SLEEP0 modes start, set SYSCR2 to “1”.

(2)

Release the IDLE0 and SLEEP0 modes

IDLE0 and SLEEP0 modes include a normal release mode and an interrupt release mode.

These modes are selected by interrupt master flag (IMF), the individual interrupt enable flag of

TBT and TBTCR.

After releasing IDLE0 and SLEEP0 modes, the SYSCR2 is automatically cleared to

“0” and the operation mode is returned to the mode preceding IDLE0 and SLEEP0 modes. Before

starting the IDLE0 or SLEEP0 mode, when the TBTCR is set to “1”, INTTBT interrupt

latch is set to “1”.

IDLE0 and SLEEP0 modes can also be released by inputting low level on the RESET pin. After

releasing reset, the operation mode is started from NORMAL1 mode.

Note: IDLE0 and SLEEP0 modes start/release without reference to TBTCR setting.

(3)

Normal release mode (IMF・EF7・TBTCR = “0”)

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the

TBTCR without reference to individual interrupt enable flag (EF). After the falling edge

is detected, the program operation is resumed from the instruction following the IDLE0 and SLEEP0

modes start instruction.

(4)

Interrupt release mode (IMF・EF7・TBTCR = “1”)

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the

TBTCR at INTTBT interrupt source enabled with the individual interrupt enable flag (EF)

and INTTBT interrupt processing is started.

Note 1: Because returning from IDLE0, SLEEP0 to NORMAL1, SLOW1 is executed by the asynchronous internal clock, the period of IDLE0, SLEEP0 mode might be the shorter than the period setting by TBTCR.

Note 2: When a watchdog timer interrupt is generated immediately before IDLE0/SLEEP0 mode is

started, the watchdog timer interrupt will be processed but IDLE0/SLEEP0 mode will not be

started.

Page 25

�Page 26

Figure 2-13 IDLE0 and SLEEP0 Modes Start/Release

Watchdog

timer

Instruction

execution

Program

counter

TBT clock

Halt

Halt

Halt

Watchdog

timer

Main

system

clock

Halt

Instruction

execution

Program

counter

TBT clock

Main

system

clock

Watchdog

timer

Instruction

execution

Program

counter

Interrupt

request

M ain

system

clock

Operate

Operate

Acceptance of interrupt

Instruction address a + 2

a+4

a+3

Halt

TENTATIVE

(b) IDLE0 and SLEEP0 modes release

Interrupt release mode

a+3

Normal release mode

a+3

(a) IDLE0 and SLEEP0 modes start (Example: Starting with the SET instruction located at address a)

Operate

SET (SYSCR2). 2

a+2

2.2 System Clock Controller

2. Operational Description

TMP86FS49FG

�TENTATIVE

2.2.4.4

TMP86FS49FG

SLOW mode

SLOW mode is controlled by the system control register 2 (SYSCR2).

The following is the methods to switch the mode with the warm-up counter (TC4, TC3).

(1)

Switching from NORMAL2 mode to SLOW1 mode

First, set SYSCK (Bit5 in SYSCR2) to switch the main system clock to the low-frequency clock

for SLOW2 mode.

Next, clear XEN (Bit7 in SYSCR2) to turn off high-frequency oscillation.

Note: The high-frequency clock can be continued oscillation in order to return to NORMAL2 mode from

SLOW mode quickly. Always turn off oscillation of high-frequency clock when switching from

SLOW mode to stop mode.

When the low-frequency clock oscillation is unstable, wait until oscillation stabilizes before performing the above operations. The timer/counter 6, 5, 4, 3 (TC6, TC5, TC4, TC3) can conveniently

be used to confirm that low-frequency clock oscillation has stabilized.

Example 1 :Switching from NORMAL2 mode to SLOW1 mode.

SET

; SYSCR2 ← 1

(SYSCR2). 5

(Switches the main system clock to the low-frequency

clock for SLOW2)

CLR

; SYSCR2 ← 0

(SYSCR2). 7

(Turns off high-frequency oscillation)

Example 2 :Switching to the SLOW1 mode after low-frequency clock has stabilized.

(SYSCR2). 6

; SYSCR2 ← 1

LD

(TC3CR), 43H

; Sets mode for TC4, TC3 (16-bit TC, fs for source)

LD

(TC4CR), 05H

LDW

(TTREG3), 8000H

SET

; IMF ← 0

DI

SET

(EIRH). 1

; Enables INTTC4

; IMF ← 1

EI

SET

; Sets warm-up time (Depend on oscillator accompanied)

(TC4CR). 3

; Starts TC4, 3

CLR

(TC4CR). 3

; Stops TC4, 3

SET

(SYSCR2). 5

; SYSCR2 ← 1

:

PINTTC4:

(Switches the main system clock to the low-frequency clock)

CLR

; SYSCR2 ← 0

(SYSCR2). 7

(Turns off high-frequency oscillation)

RETI

:

VINTTC4:

(2)

DW

PINTTC4

; INTTC4 vector table

Switching from SLOW1 mode to NORMAL2 mode

First, set XEN (Bit7 in SYSCR2) to turn on the high-frequency oscillation. When time for stabilization (Warm up) has been taken by the timer/counter 4, 3 (TC4, TC3), clear SYSCK (Bit5 in

SYSCR2) to switch the main system clock to the high-frequency clock.

Page 27

�2. Operational Description

2.2 System Clock Controller

TENTATIVE

TMP86FS49FG

Note: After SYSCK is cleared to “0”, executing the instructions is continiued by the low-frequency clock

for the period synchronized with low-frequency and high-frequency clocks.

High-frequency clock

Low-frequency clock

Main system clock

SYSCK

Note: SLOW mode can also be released by inputting low level on the RESET pin, which immediately performs the reset operation. After reset, TMP86FS49FG are placed in NORMAL1 mode.

Example :Switching from the SLOW1 mode to the NORMAL2 mode (fc = 16 MHz, warm-up time is 4.0 ms).

(SYSCR2). 7

; SYSCR2 ← 1 (Starts high-frequency oscillation)

LD

(TC3CR), 63H

; Sets mode for TC4, TC3 (16-bit TC, fc for source)

LD

(TC4CR), 05H

LD

(TTREG4), 0F8H

SET

; Sets warm-up time

; IMF ← 0

DI

SET

(EIRH). 1

; Enables INTTC4

; IMF ← 1

EI

SET

(TC4CR). 3

; Starts TC4, 3

CLR

(TC4CR). 3

; Stops TC4, 3

CLR

(SYSCR2). 5

; SYSCR2 ← 0

:

PINTTC4:

(Switches the main system clock to the high-frequency clock)

RETI

:

VINTTC4:

DW

PINTTC4

; INTTC4 vector table

Page 28

�Page 29

Figure 2-14 Switching between the NORMAL2 and SLOW Modes

SET (SYSCR2). 7

SET (SYSCR2). 5

SLOW1 mode

Instruction

execution

XEN

SYSCK

Highfrequency

clock

Lowfrequency

clock

Main

system

clock

NORMAL2

mode

Instruction

execution

XEN

SYSCK

Highfrequency

clock

Lowfrequency

clock

Main

system

clock

(b) Switching to the NORMAL2 mode

Warm up during SLOW2 mode

CLR (SYSCR2). 5

(a) Switching to the SLOW mode

SLOW2 mode

CLR (SYSCR2). 7

NORMAL2

mode

SLOW1 mode

Turn off

TENTATIVE

TMP86FS49FG

�2. Operational Description

2.3 Reset Circuit

TMP86FS49FG

TENTATIVE

2.3 Reset Circuit

The TMP86FS49FG have four types of reset generation procedures: An external reset input, an address trap reset,

a watchdog timer reset and a system clock reset. Table 2-2 shows on-chip hardware initialization by reset action.

The malfunction reset circuit such as watchdog timer reset, address trap reset and system clock reset is not initialized when power is turned on. The RESET pin can reset state at the maximum 24/fc [s] (1.5 µs at 16.0 MHz) when

power is turned on.

Table 2-2 Initializing Internal Status by Reset Action

On-chip Hardware

Initial Value

Program counter

(PC)

(FFFEH)

Stack pointer

(SP)

Not initialized

General-purpose registers

(W, A, B, C, D, E, H, L, IX, IY)

(JF)

Not initialized

Zero flag

(ZF)

Not initialized

Carry flag

(CF)

Not initialized

Half carry flag

(HF)

Not initialized

Sign flag

(SF)

Not initialized

Overflow flag

(VF)

Not initialized

(IMF)

0

(EF)

0

Interrupt individual enable flags

Interrupt latches

2.3.1

Initial Value

Prescaler and divider of timing generator

0

Not initialized

Jump status flag

Interrupt master enable flag

On-chip Hardware

(IL)

Watchdog timer

Enable

Output latches of I/O ports

Refer to I/O port circuitry

Control registers

Refer to each of control

register

RAM

Not initialized

0

External Reset Input

The RESET pin contains a Schmitt trigger (Hysteresis) with an internal pull-up resistor.

When the RESET pin is held at “L” level for at least 3 machine cycles (12/fc [s]) with the power supply voltage within the operating voltage range and oscillation stable, a reset is applied and the internal state is initialized.

When the RESET pin input goes high, the reset operation is released and the program execution starts at the

vector address stored at addresses FFFEH to FFFFH.

VDD

RESET

Internal reset

Watchdog timer reset

Malfunction

reset output

circuit

Address trap reset

System clock reset

Figure 2-15 Reset Circuit

Page 30

�TMP86FS49FG

TENTATIVE

2.3.2

Address trap reset

If the CPU should start looping for some cause such as noise and an attempt be made to fetch an instruction

from the on-chip RAM (when WDTCR1 is set to “1”), DBR or the SFR area, address trap reset will

be generated. The reset time is about 8/fc to 24/fc [s] (0.5 to 1.5 µs at 16.0 MHz).

Note:The operating mode under address trapped is alternative of reset or interrupt. The address trap area is alternative.

Instruction

execution

JP

Reset release

a

Instruction at address r

Address trap is occurred

Internal reset

4/fc to 12/fc [s]

8/fc to 24/fc [s]

16/fc [s]

Note 1: Address “a” is in the SFR or on-chip RAM (WDTCR1 = “1”) space.

Note 2: During reset release, reset vector “r” is read out, and an instruction at address “r” is fetched and decoded.

Figure 2-16 Address Trap Reset

2.3.3

Watchdog timer reset

Refer to 2.4 “Watchdog Timer”.

2.3.4

System clock reset

Clearing both XEN and XTEN (Bits 7 and 6 in SYSCR2) to “0”, clearing XEN to “0” when SYSCK = “0”,

or clearing XTEN to “0” when SYSCK = “1” stops system clock, and causes the microcomputer to deadlock.

This can be prevented by automatically generating a reset signal whenever XEN = XTEN = “0”, XEN =

SYSCK = “0”, or XTEN = “0”/SYSCK = “1” is detected to continue the oscillation. The reset time is about 8/

fc to 24/fc [s] (0.5 to 1.5 µs at 16.0 MHz).

Page 31

�2. Operational Description

2.3 Reset Circuit

TENTATIVE

Page 32

TMP86FS49FG

�TMP86FS49FG

TENTATIVE

22. Electrical Characteristics

22.1 Absolute Maximum Ratings

The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant.

Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down

or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when

designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

(VSS = 0 V)

Parameter

Symbol

Pins

Ratings

Supply voltage

VDD

-0.3 to 6.5

Input voltage

VIN

-0.3 to VDD + 0.3

VOUT1

-0.3 to VDD + 0.3

Output voltage

Output current (Per 1 pin)

Output current (Total)

IOUT1

P0, P1, P4, P6, P7 ports

-1.8

IOUT2

P0, P1, P4, P6, P7 ports

3.2

IOUT3

P3, P5 ports

30

Σ IOUT1

P0, P1, P4, P6, P7 ports

60

Σ IOUT2

P3, P5 ports

V

mA

80

Power dissipation [Topr = 85 °C]

PD

250

Soldering temperature (time)

Tsld

260 (10 s)

Storage temperature

Tstg

-55 to 125

Operating temperature

Topr

-40 to 85

Page 255

Unit

mW

°C

�22. Electrical Characteristics

22.1 Absolute Maximum Ratings

TMP86FS49FG

TENTATIVE

22.2 Recommended Operating Conditions

The recommended operating conditions for a device are operating conditions under which it can be guaranteed that

the device will operate as specified. If the device is used under operating conditions other than the recommended

operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may

occur. Thus, when designing products which include this device, ensure that the recommended operating conditions

for the device are always adhered to.

22.2.1 MCU mode (Flash Programming or erasing)

(VSS = 0 V, Topr = -10 to 40°C)

Parameter

Symbol

Pins

Ratings

VDD

Supply voltage

Input high level

Input low level

Clock frequency

NORMAL1, 2 modes

VIH1

Except hysteresis input

VIH2

Hysteresis input

VIL1

Except hysteresis input

VIL2

Except hysteresis input

fc

VDD ≥ 4.5 V

VDD ≥ 4.5 V

XIN, XOUT

Min

Max

4.5

5.5

VDD × 0.70

Unit

VDD

VDD × 0.75

V

VDD × 0.30

0

VDD × 0.25

1.0

16.0

MHz

22.2.2 MCU mode (Except Flash Programming or erasing)

(VSS = 0 V, Topr = -40 to 85°C)

Parameter

Symbol

Pins

Supply voltage

(Condition 1)

Ratings

fc = 16 MHz

NORMAL1, 2 modes

IDLE0, 1, 2 modes

fs = 32.768 KHz

SLOW1, 2 modes

SLEEP0, 1, 2 modes

Min

Max

4.5

5.5

3.0

3.6

Unit

STOP mode

VDD

Supply voltage

(Condition 2)

fc = 8 MHz

NORMAL1, 2 modes

IDLE0, 1, 2 modes

fs = 32.768 KHz

SLOW1, 2 modes

SLEEP0, 1, 2 modes

V

STOP mode

Input high level

VIH1

Except hysteresis input

VIH2

Hysteresis input

VDD < 4.5 V

VIH3

Input low level

VIL1

Except hysteresis input

VIL2

Hysteresis input

VDD ≥ 4.5 V

VDD × 0.70

VDD × 0.75

VDD

VDD × 0.90

VDD × 0.30

0

VDD × 0.25

VDD × 0.10

VDD < 4.5 V

VIL3

XIN, XOUT

VDD = 3.0 to 3.6 V, 4.5 to 5.5V

1.0

8.0

fc

XIN, XOUT

VDD = 4.5 to 5.5 V

1.0

16.0

fs

XTIN, XTOUT

VDD = 3.0 to 3.6 V, 4.5 to 5.5V

30.0

34.0

fc

Clock frequency

VDD ≥ 4.5 V

MHz

Note 1: The Supply voltage (VDD) is divided into two different voltage areas. Do not change VDD from Condition 1 to Condition 2 and vice versa while the MCU is operationg. If you wish to use VDD in a continuous range of 3.0V to

5.5V without stopping the MCU, please contact your local Toshiba office.

Page 256

kHz

�TMP86FS49FG

TENTATIVE

22.2.3 Serial PROM mode

(VSS = 0 V, Topr = -10 to 40 °C)

Parameter

Supply voltage

Input high voltage

Input low voltage

Clock frequency

Symbol

Pins

VDD

VIH1

NORMAL1, 2 modes

Except hysteresis input

VIH2

Hysteresis input

VIL1

Except hysteresis input

VIL2

Hysteresis input

fc

Condition

VDD ≥ 4.5 V

VDD ≥ 4.5 V

XIN, XOUT

Min

Max

4.5

5.5

VDD × 0.70

VDD × 0.75

0

2.0

Page 257

VDD

Unit

V

VDD × 0.30

VDD × 0.25

16.0

MHz

�22. Electrical Characteristics

22.1 Absolute Maximum Ratings

TMP86FS49FG

TENTATIVE

22.3 DC Characteristics

(VSS = 0 V, Topr = -40 to 85 °C)

Parameter

Symbol

Pins

Condition

Min

Typ.

Max

Unit

–

0.9

–

V

–

–

±2

µA

100

220

450

kΩ

VHS

Hysteresis input

IIN1

TEST

IIN2

Sink open drain, tri–state port

IIN3

RESET, STOP

RIN

RESET pull–up

ILO1

Sink open drain port

VDD = 5.5 V, VOUT = 5.5 V

–

–

2

ILO2

Tri–state port

VDD = 5.5 V, VOUT = 5.5 V/0 V

–

–

±2

Output high voltage

VOH

Tri–state port

VDD = 4.5 V, IOH = -0.7 mA

4.1

–

–

Output low voltage

VOL

Except XOUT, P3, P5

VDD = 4.5 V, IOL = 1.6 mA

–

–

0.4

Output low curren

IOL

High current port

(P3, P5 Port)

VDD = 4.5 V, VOL = 1.0 V

–

20

–

–

12.6

20

–

6.3

7.5

–

7.6

10

When a program

operates on flash

memory

–

0.9

3

When a program

operates on RAM

–

10

21

–

4.5

16

–

3.5

12

–

0.5

10

Hysteresis voltage

Input current

Input resistance

Output leakage current

Supply current in

NORMAL1, 2 modes

VDD = 5.5 V

When a program

operates on flash

memory

VIN = 5.3 V/0.2 V

Supply current in

IDLE0 mode

fc = 16 MHz

fs = 32.768 kHz

Supply current in IDLE

1, 2 modes

Supply current in

SLOW1 mode

VDD = 5.5 V, VIN = 5.5 V/0 V

IDD

VDD = 3.0 V

VIN = 2.8 V/0.2 V

Supply current in

SLEEP1 mode

fs = 32.768 kHz

V

mA

µA

Supply current in

SLEEP0 mode

Supply current in

STOP mode

µA

VDD = 5.5 V

VIN = 5.3 V/0.2 V

Note 1: Typical values show those at Topr = 25°C and VDD = 5 V.

Note 2: Input current (IIN1, IIN3): The current through pull-up or pull-down resistor is not included.

Note 3: IDD does not include IREF.

Note 4: The supply currents of SLOW2 and SLEEP2 modes are equivalent to those of IDLE1 and IDLE2 modes.

Page 258

�TMP86FS49FG

TENTATIVE

22.4 AD Characteristics

(VSS = 0.0 V, 4.5 V ≤ VDD ≤ 5.5 V, Topr = -40 to 85 °C)

Paramete

Symbol

Analog reference voltage

VAREF

Power supply voltage of analog control

circuit

AVDD

Condition

Min

Typ.

Max

AVDD - 1.0

–

AVDD

VDD

V

∆ VAREF

3.5

–

–

Analog input voltage

VAIN

VSS

–

VAREF

Power supply current of analog reference voltage

IREF

–

0.6

1.0

–

–

±2

–

–

±2

–

–

±2

–

–

±2

Analog reference voltage range (Note 4)

VDD = AVDD = VAREF = 5.5 V

VSS = AVSS = 0.0 V

Non linearity error

VDD = AVDD = 5.0 V,

Zero point error

VSS = AVSS = 0.0 V

Full scale error

VAREF = 5.0 V

Total error

Unit

mA

LSB

(VSS = 0 V, 3.0 V ≤ VDD ≤ 3.6 V, Topr = -40 to 85°C)

Parameter

Symbol

Analog reference voltage

VAREF

Power supply voltage of analog control

circuit

AVDD

Condition

Min

Typ.

Max

AVDD - 1.0

–

AVDD

VDD

V

∆ VAREF

2.5

–

–

Analog input voltage

VAIN

VSS

–

VAREF

Power supply current of analog reference voltage

IREF

–

0.5

0.8

–

–

±2

–

–

±2

–

–

±2

–

–

±2

Analog reference voltage range (Note 4)

VDD = AVDD = VAREF =3.6 V

VSS = AVSS = 0.0 V

Non linearity error

Zero point error

Full scale error

VDD = AVDD = 3.0 V

VSS = AVSS = 0.0 V

VAREF = 3.0 V

Total error

Unit

mA

LSB

Note 1: The total error includes all errors except a quanitization error, and is defined as a maximum deviation from the ideal conversion line.

Note 2: Conversion time is defferent in recommended value by power supply voltage.

Note 3: The voltage to be input on the AIN input pin must not exceed the range between VAREF and VSS. If a voltage outside this

range is input, conversion values will become unstable and conversion values of other channels will also be affected.

Note 4: Analog reference voltage range: ∆VAREF = VAREF - VSS

Note 5: When AD converter is not used, fix the AVDD and VAREF pin on the VDD level.

Page 259

�22. Electrical Characteristics

22.6 Flash Characteristics

TMP86FS49FG

TENTATIVE

22.5 AC Characteristics

(VSS = 0 V, VDD = 4.5 V to 5.5 V, Topr = -40 to 85°C)

Parameter

Symbol

Condition

Min

Typ.

Max

0.25

–

4

117.6

–

133.3

For external clock operation (XIN input)

fc = 16 MHz

–

31.25

–

ns

For external clock operation (XTIN input)

fs = 32.768 kHz

–

15.26

–

µs

NORMAL1, 2 modes

Machine cycle time

tcy

IDLE0, 1, 2 modes

SLOW1, 2 modes

SLEEP0, 1, 2 modes

High-level clock pulse width

tWCH

Low-level clock pulse width

tWCL

High-level clock pulse width

tWSH

Low-level clock pulse width

tWSL

Unit

µs

(VSS = 0 V, VDD = 3.0 V to 3.6 V, Topr = -40 to 85°C)

Paramete

Symbol

Condition

Min

Typ.

Max

0.5

–

4

117.6

–

133.3

For external clock operation (XIN input)

fc = 8 MHz

–

62.5

–

ns

For external clock operation (XTIN input)

fs = 32.768 kHz

–

15.26

–

µs

NORMAL1, 2 modes

tcy

Machine cycle time

IDLE0, 1, 2 modes

SLOW1, 2 modes

SLEEP0, 1, 2 modes

High-level clock pulse width

tWCH

Low-level clock pulse width

tWCL

High-level clock pulse width

tWSH

Low-level clock pulse width

tWSL

Unit

µs

22.6 Flash Characteristics

22.6.1 Write/Retention Characteristics

(VSS = 0 V)

Paramete

Number of guaranteed writes to flash memory

Condition

VSS = 0 V, Topr = -10 to 40°C

Page 260

Min

Typ.

Max.

Unit

–

–

100

Times

�TMP86FS49FG

TENTATIVE

22.7 Recommended Oscillating Conditions

XIN

XOUT

XTIN

C2

C1

(1) High-frequency Oscillation

XTOUT

C1

C2

(2) Low-frequency Oscillation

Note 1: To ensure stable oscillation, the resonator position, load capacitance, etc. must be appropriate. Because these factors are

greatly affected by board patterns, please be sure to evaluate operation on the board on which the device will actually be

mounted.

Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For

up-to-date information, please refer to the following URL:

http://www.murata.co.jp/search/index.html

22.8 Handling Precaution

- The solderability test conditions for lead-free products (indicated by the suffix G in product name) are shown

below.

1. When using the Sn-63Pb solder bath

Solder bath temperature = 230 °C

Dipping time = 5 seconds

Number of times = once

R-type flux used

2. When using the Sn-3.0Ag-0.5Cu solder bath

Solder bath temperature = 245 °C

Dipping time = 5 seconds

Number of times = once

R-type flux used

Note: The pass criteron of the above test is as follows:

Solderability rate until forming ≥ 95 %

- When using the device (oscillator) in places exposed to high electric fields such as cathode-ray tubes, we recommend electrically shielding the package in order to maintain normal operating condition.

Page 261

�22. Electrical Characteristics

22.8 Handling Precaution

TENTATIVE

Page 262

TMP86FS49FG

�