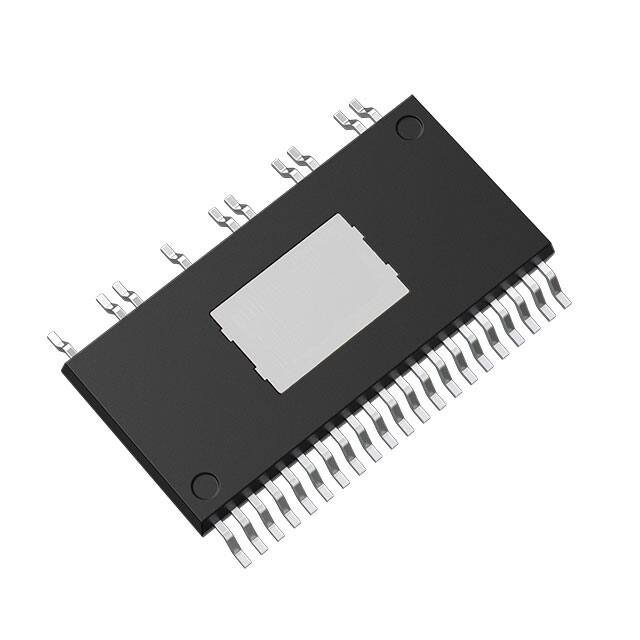

TPD4162F

Intelligent Power Device

TPD4162F

High Voltage Monolithic Silicon Power IC

1. Description

The TPD4162F is a DC brushless motor driver using high-voltage PWM

control. It is fabricated using a high-voltage SOI process. The device

contains PWM circuit, 3-phase decode circuit, level shift high-side

driver, low-side driver, IGBT outputs, FRDs, over-current, and current

limit and under-voltage protection circuits, and a thermal shutdown

circuit. It is easy to control a DC brushless motor by applying a signal

from a motor controller and a Hall element / Hall IC to the TPD4162F.

P-HSSOP31-0918-0.80-002

TPD4162F

2. Applications

DC brushless motor driver IC

3. Features

●

●

●

●

●

●

High voltage power side and low voltage signal side terminal are separated.

Bootstrap circuits give simple high-side supply.

Bootstrap diodes are built in.

PWM and 3-phase decode circuit are built in.

Pulses-per-revolution output:

FGC = High: 3 pulse/electrical angle: 360°

FGC = Low : 1 pulse/electrical angle: 360°

Included over-current and current limit and under-voltage protection, and thermal shutdown.

Start of commercial production

2019-10

© 2020

Toshiba Electronic Devices & Storage Corporation

1

2020-02-20

�TPD4162F

4. Block Diagram

Figure 4.1 Block Diagram

5. Pin Assignments

Figure 5.1 Pin Assignments

© 2020

Toshiba Electronic Devices & Storage Corporation

2

2020-02-20

�TPD4162F

6. Pin Description

Table 6.1

Pin Description

Pin No.

Symbol

Pin Description

1

VBB

High-voltage power supply input pin.

2

BSU

U-phase bootstrap capacitor connecting pin.

3

U

4

IS1

IGBT emitter/FRD anode pin.

5

BSV

V-phase bootstrap capacitor connecting pin.

U-phase output pin.

6

V

7

BSW

V-phase output pin.

8

W

W-phase output pin.

9

NC

Unused pin, which is not connected to the chip internally.

10

IS2

IGBT emitter/FRD anode pin.

11

GND

12

NC

Unused pin, which is not connected to the chip internally.

13

NC

Unused pin, which is not connected to the chip internally.

14

HW-

W-phase Hall element signal input pin. (Hall IC can be used.)

15

HW+

W-phase Hall element signal input pin. (Hall IC can be used.)

16

HV-

V-phase Hall element signal input pin. (Hall IC can be used.)

17

HV+

V-phase Hall element signal input pin. (Hall IC can be used.)

18

HU-

U-phase Hall element signal input pin. (Hall IC can be used.)

19

HU+

U-phase Hall element signal input pin. (Hall IC can be used.)

20

VREG

5 V regulator output pin.

21

CS

W-phase bootstrap capacitor connecting pin.

Ground pin.

Over-current protection detection pin

22

OS

23

RREF

24

NC

PWM triangular wave oscillation frequency setup pin.

(Connect a capacitor to this pin.)

PWM triangular wave oscillation frequency setup pin.

(Connect a resistor to this pin.)

Unused pin, which is not connected to the chip internally.

25

RS

Input for current limit and over-current protection detection pin

26

FGC

27

VS

Speed control signal input pin. (PWM reference voltage input pin.)

28

FG

Revolution pulse output pin.

29

VCC

Control power supply pin.

30

NC

Unused pin, which is not connected to the chip internally.

31

GND

FG pulse count select (High or open = 3 ppr; Low = 1 ppr).

Ground pin.

© 2020

Toshiba Electronic Devices & Storage Corporation

3

2020-02-20

�TPD4162F

7. Functional Description

7.1.1. Timing Chart

HU

HV

Hall amp

input

HW

VU

Output voltage

VV

VW

Revolution pulse

(FGC=H)

FG

Revolution pulse

(FGC=L)

FG

Figure7.1.1 Timing Chart

Note: Hall amp input logic high (H) refers to H*+>H*-. (*: U/V/W)

© 2020

Toshiba Electronic Devices & Storage Corporation

4

2020-02-20

�TPD4162F

7.1.2. Truth Table

Table 7.1.2 Truth Table

FGC

Hall amp Input

U Phase

V Phase

W Phase

FG

HU

HV

HW

High side

Low side

High side

Low side

High side

Low side

H

H

L

H

OFF

ON

ON

OFF

OFF

OFF

H

H

H

L

L

OFF

ON

OFF

OFF

ON

OFF

L

H

H

H

L

OFF

OFF

OFF

ON

ON

OFF

H

H

L

H

L

ON

OFF

OFF

ON

OFF

OFF

L

H

L

H

H

ON

OFF

OFF

OFF

OFF

ON

H

H

L

L

H

OFF

OFF

ON

OFF

OFF

ON

L

H

L

L

L

OFF

OFF

OFF

OFF

OFF

OFF

L

H

H

H

H

OFF

OFF

OFF

OFF

OFF

OFF

L

L

H

L

H

OFF

ON

ON

OFF

OFF

OFF

H

L

H

L

L

OFF

ON

OFF

OFF

ON

OFF

H

L

H

H

L

OFF

OFF

OFF

ON

ON

OFF

H

L

L

H

L

ON

OFF

OFF

ON

OFF

OFF

L

L

L

H

H

ON

OFF

OFF

OFF

OFF

ON

L

L

L

L

H

OFF

OFF

ON

OFF

OFF

ON

L

L

L

L

L

OFF

OFF

OFF

OFF

OFF

OFF

L

L

H

H

H

OFF

OFF

OFF

OFF

OFF

OFF

H

Note: Hall amp input logic high (H) refers to H*+>H*-. (*: U/V/W)

7.2. Handling precautions

(1) When switching the power supply to the circuit on/off, ensure that VS < VVSOFF (all IGBT outputs off). At

that time, either the VCC or the VBB can be turned on/off first. Note that if the power supply is switched off

as described above, the IC may be destroyed if the current regeneration route to the VBB power supply is

blocked when the VBB line is disconnected by a relay or similar while the motor is still running.

(2) The triangular wave oscillator circuit, with externally connected C5 and R3, charges and discharges minute

amounts of current. Therefore, subjecting the IC to noise when mounting it on the board may distort the

triangular wave or cause malfunction. To avoid this, attach external parts to the base of the IC leads or

isolate them from any tracks or wiring which carries large current.

(3) The PWM of this IC is controlled by the on/off state of the high-side IGBT.

(4) If a motor is locked where VBB voltage is low and duty is 100 %, it may not be possible to reboot after the

load is released as a result of the high side being ON immediately prior to the motor being locked. This is

because, over time, the bootstrap voltage falls, the high-side voltage decrease protection operates and the

high-side output becomes OFF. In this case, since the level shift pulse necessary to turn the high side ON

cannot be generated, reboot is not possible. A level shift pulse is generated by either the edge of a Hall

sensor output or the edge of an internal PWM signal, but neither edge is available due to the motor lock

and duty 100 % command. In order to reboot after a lock, the high-side power voltage must return to a

level 0.5 V (typ.) higher than the voltage decrease protection level, and a high-side input signal must be

introduced. As a high-side input signal is created by the aforementioned level shift pulse, it is possible to

reboot by reducing PWM duty to less than 100 % or by forcing the motor to turn externally and creating an

edge at a Hall sensor output. In order to ensure reboot after a system lock, the maximum duty of motor

operation must be less than 100 %.

© 2020

Toshiba Electronic Devices & Storage Corporation

5

2020-02-20

�TPD4162F

7.3. Description of Protection Function

(1)

Current limit protection

The IC incorporates a current limit protection circuit to protect itself against over current at startup or

when a motor is locked. This protection function detects voltage generated in the current-detection

resistor connected to the RS pin. When this voltage exceeds VR = 0.5 V (typ.), the high-side IGBT output,

which is on, temporarily shuts down after a delay time, preventing any additional current from flowing to

the IC. The next PWM ON signal releases the shutdown state.

Duty ON

PWM reference voltage

Duty OFF

Triangle wave

Delay time

toff

ton

ton

Current limit setting value

Output current

Retry

Over-current shutdown

Figure7.3.1 Description of Current limit protection

(2) Over-current protection

This protection function detects voltage generated in the current-detection resistor connected to the RS

pin. When this voltage exceeds VR = 0.7 V (typ.), the all high-side and low-side IGBT outputs are shut down.

Over-current protection recovery time can be adjusted with the capacitor and resistance connected to CS

terminal. The CS terminal voltage is carried out by the damping time constant decided by this capacitor

and resistance. The low side IGBT of the phase which a high side turns on by a timing chart will be made

to turn on, a bootstrap capacitor will be charged, if the threshold value 1(VRON) is exceeded (refreshment

operation), and the threshold value 2(VROFF) is exceeded after that, IGBT turns on according to an input

signal.

CS terminal Voltage

Threshold value 2(VROFF)

Threshold value 1(VRON)

Refreshment operation

tcs

tcsr

Over-current setting value

Output current

Retry

Over-current shutdown

Figure7.3.2 Description of Over-current protection

© 2020

Toshiba Electronic Devices & Storage Corporation

6

2020-02-20

�TPD4162F

(3) Under-voltage protection

The IC incorporates under-voltage protection circuits to prevent the IGBT from operating in unsaturated

mode when the VCC voltage or the VBS voltage drops.

When the VCC power supply falls to the IC internal setting VCCUVD = 11 V (typ.), all IGBT outputs are shut

down regardless of the input. This protection function has hysteresis. When the VCC power supply reaches

0.5 V higher than the shutdown voltage VCCUVR = 11.5 V (typ.), the IC is automatically restored and the

IGBT is turned on/off again by the input.

When the VBS supply voltage drops VBSUVD = 3.0 V (typ.), the high-side IGBT output shuts down. When

he VBS supply voltage reaches 0.5 V higher than the shutdown voltage VBSUVR = 3.5 V (typ.) VBS supply

voltage reaches 0.5 V higher than the shutdown voltage VBSUVR = 3.5 V (typ.), the IGBT is turned on/off

again by the input signal.

(4) Thermal shutdown

The IC incorporates a thermal shutdown circuit to protect itself against excessive rise in temperature.

When the temperature of this chip rises to the internal setting TSD due to external causes or internal heat

generation, all IGBT outputs are shut down regardless of the input. This protection function has hysteresis

∆TSD = 50 °C (typ.). When the chip temperature falls to TSD − ∆TSD, the chip is automatically restored

and the IGBT is turned on/off again by the input.

Because the chip contains just one temperature-detection location, when the chip heats up due to the IGBT

for example, the distance between the detection location and the IGBT (the source of the heat) can cause

differences in the time taken for shutdown to occur. Therefore, the temperature of the chip may rise higher

than the thermal shutdown temperature.

7.4. Description of Bootstrap Capacitor Charging and Its Capacitance

The IC uses bootstrapping for the power supply for high-side drivers.

The bootstrap capacitor is charged by turning on the low-side IGBT of the same arm (approximately 1/5 of

PWM cycle) while the high-side IGBT controlled by PWM is off. For example, to drive at 20 kHz, it takes

approximately 10 μs per cycle to charge the capacitor. When the VS voltage exceeds 3.8 V (55 % duty),

the low-side IGBT is continuously in the off state. This is because when the PWM on-duty becomes larger,

the arm is short-circuited while the low-side IGBT is on. Even in this state, because PWM control is being

performed on the high-side IGBT, the regenerative current of the diode flows to the low-side FRD of the

same arm, and the bootstrap capacitor is charged. Note that when the on-duty is 100 %, diode regenerative

current does not flow; thus, the bootstrap capacitor is not charged.

When driving a motor at 100 % duty cycle, take the voltage drop at 100 % duty (see the figure below) into

consideration to determine the capacitance of the bootstrap capacitor.

Capacitance of the bootstrap capacitor = Current dissipation (max) of the high-side driver × Maximum drive

time /(VCC − VF (BSD) + VF (FRD) − 13.5) [F]

VF (BSD) : Bootstrap diode forward voltage

VF (FRD) : Fast recovery diode forward voltage

Consideration must be made for aging and temperature change of the capacitor.

Duty cycle 100 % (VS: 5.4 V)

Duty cycle 80 %

C

Triangular wave

Duty cycle 55 % (VS: 3.8 V)

PWM reference voltage

B

Duty cycle 0 % (VS: 2.1 V)

VVsOFF (VS: 1.3 V)

Low-side ON

High-side duty ON

A

GND

VS Range

IGBT Operation

A

Both high and low-side OFF.

B

Charging range. Low-side IGBT refreshing on the phase the high-side IGBT in PWM.

C

No charging range. High-side at PWM according to the timing chart. Low-side no refreshing.

© 2020

Toshiba Electronic Devices & Storage Corporation

7

2020-02-20

�TPD4162F

8. Absolute Maximum Ratings

Table 8.1

Absolute Maximum Ratings

(Ta = 25°C unless otherwise specified)

Characteristics

Symbol

Rating

Unit

VBB

600

V

VCC

20

V

Output current (DC)

Iout

0.7

A

Output current (pulse)

Ioutp

1.2

A

Input voltage (except VS)

VIN

-0.5 to VREG + 0.5

V

Input voltage (only VS)

VVS

8.2

V

VREG current

IREG

50

mA

FG voltage

VFG

6

V

FG current

IFG

20

mA

Power dissipation (Tc = 25°C)

PC

20

W

Operating junction temperature

Power supply voltage

Tjopr

-40 to 135

°C

Junction temperature

Tj

150

°C

Storage temperature

Tstg

-55 to 150

°C

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant

change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating

conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the

operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook

(“Handling Precautions”/“Derating Concept and Methods“) and individual reliability data (i.e. reliability test report

and estimated failure rate, etc).

8.1. Safe Operating Area

Peak winding current

(A)

0.7

0

0

450

Power supply voltage VBB (V)

Figure8.1 SOA at Tj = 135 °C

© 2020

Toshiba Electronic Devices & Storage Corporation

8

2020-02-20

�TPD4162F

9. Operating Ranges

Table 9.1 Operating Ranges(Ta=25 ℃)

Characteristics

Operating power supply voltage

Symbol

Test Condition

Min

Typ.

Max

VBB

50

280

450

VCC

13.5

15

17.5

Unit

V

10. Electrical Characteristics

Electrical Characteristics(Ta=25 ℃)

Table 10.1

Characteristics

Current dissipation

Symbol

Test Condition

Min

Typ.

Max

IBB

VBB = 450 V, Duty cycle = 0 %

0.5

ICC

VCC = 15 V, Duty cycle = 0 %

0.9

1.5

IBS (ON)

VBS = 15 V, high side ON

85

150

IBS (OFF)

VBS = 15 V, high side OFF

75

130

Unit

mA

µA

VHSENS(HA)

―

50

―

―

mVp-p

IHB(HA)

―

-2

0

2

µA

CMVIN(HA)

―

0.7

VREG-1.3

V

Hall amp hysteresis width

∆VIN(HA)

―

8

30

62

Hall amp input voltage L→H

VLH(HA)

―

4

15

31

Hall amp input voltage H→L

VHL(HA)

―

-31

-15

-4

Hall amp input sensitivity

Hall amp input current

Hall amp common input voltage

Output saturation voltage

VCEsat

FRD forward voltage

PWM ON-duty cycle

PWM ON-duty cycle, 0 %

VF

2.0

3.0

V

IF = 0.5 A

1.5

3.0

V

―

0

PWMMAX

―

100

PWM = 0 %

1.7

2.1

2.5

V

PWM = 100 %

4.9

5.4

6.1

V

VVS100 % − VVS0 %

2.8

3.3

3.8

V

Output all OFF

1.1

1.3

1.5

V

VCC = 15 V, IREG = 30 mA

4.5

5.0

5.5

V

VVS0 %

VVS100 %

PWM ON-duty voltage range

VVSW

Regulator voltage

VCC = 15 V, Ioutp = 0.5 A

PWMMIN

PWM ON-duty cycle, 100 %

Output all-OFF voltage

mV

VVSOFF

VREG

Speed control voltage range

VS

FG output saturation voltage

VFGsat

―

VCC = 15 V, IFG = 5 mA

%

0

6.5

V

0.5

V

Current limit voltage

VR

―

0.46

0.5

0.54

V

Current limit delay time

DtR

3

4.5

µs

Over-current protection voltage

VCS

0.64

0.7

0.76

V

Over-current protection delay time

tCS

2.2

3.5

µs

Over-current protection recovery time

tcsr

1.0

2.0

ms

Thermal shutdown temperature

TSD

135

185

°C

C4=470 pF , R2=2 MΩ

Thermal shutdown hysteresis

∆TSD

―

50

°C

VCC under-voltage protection

VCCUVD

―

10

11

12

V

VCC under-voltage protection

recovery

VCCUVR

―

10.5

11.5

12.5

V

© 2020

Toshiba Electronic Devices & Storage Corporation

9

2020-02-20

�TPD4162F

VBS under-voltage protection

VBSUVD

―

2.0

3.0

4.0

V

VBS under-voltage protection

recovery

VBSUVR

―

2.5

3.5

4.5

V

Refresh operating ON voltage

VRFON

Refresh operation ON

1.1

1.3

1.5

V

Refresh operating OFF voltage

VRFOFF

Refresh operation OFF

3.1

3.8

4.6

V

16.5

20

25

kHz

Triangular wave frequency

fc

R3 = 27 kΩ, C5 = 1000 pF

Output-on delay time

ton

VBB = 280 V, VCC = 15 V, Ioutp = 0.5 A

2.5

3.5

µs

Output-off delay time

toff

VBB = 280 V, VCC = 15 V, Ioutp = 0.5 A

2.0

3.0

µs

FRD reverse recovery time

trr

VBB = 280 V, VCC = 15 V, Ioutp = 0.5 A

200

ns

11. Application Circuit Example

Figure 11.1

© 2020

Toshiba Electronic Devices & Storage Corporation

Application Circuit Example

10

2020-02-20

�TPD4162F

Typical external parts are shown in the following table.

Table 11.1 Typical external parts

Part

Typical

C1, C2, C3

25 V/2.2 μF

R1

1 Ω ± 1 % (1 W)

R2

Purpose

Remarks

Bootstrap capacitor

(Note 1)

Current detection

(Note 2)

2 MΩ± 5 %

Over-current

protection recovery setup

(Note 3)

C4

25 V / 470 pF

Over-current

protection recovery setup

(Note 3)

C5

25 V/1000 pF ± 5 %

PWM frequency setup

(Note 4)

R3

27 kΩ ± 5 %

PWM frequency setup

(Note 4)

C6

25 V/10 μF

C7

25 V/0.1 μF

Control power supply stability

(Note 5)

C8

25 V/10 μF

C9

25 V/0.1 μF

VREG power supply stability

(Note 5)

R4

5.1 kΩ± 5 %

FG pin pull-up resistor

(Note 6)

Note 1: The required bootstrap capacitance value varies according to the motor drive conditions.

Although the IC can operate at above the VBS undervoltage level, it is however recommended that

the capacitor voltage be greater than or equal to 3.5 V to keep the power dissipation small.

Note 2: The following formula shows the detection current: IO = VR ÷ R1 (at VR = 0.5 V (typ.))

Do not exceed a detection current of 0.7 A when using the IC.

Note 3: A setup of over-current protection recovery and the refreshment operating time at the time of a

return are set up in the combination of C4 and R2 which were shown in the formula.

And recommends a setup of C4 and R2 from which refreshment operating time is set to 190 μs or

more. If the CS pin is not used, connect to the VREG pin.

Over-current protection recovery time =1.06×C4×R2 [s]

Refreshment operating time =0.21×C4×R2 [s]

Note 4: With the combination of C5 and R3 shown in the table, the PWM frequency is around 20 kHz. The

IC intrinsic error factor is around 10 %.

The PWM frequency is broadly expressed by the following formula. (In this case, the stray

capacitance of the printed circuit board needs to be considered.)

fc = 0.65 ÷ { C5 × (R3 + 4.25 kΩ)} [Hz]

R3 creates the reference current of the PWM triangular wave charge/discharge circuit. If R3 is set

too small it exceeds the current capacity of the IC internal circuits and the triangular wave distorts.

Set R3 to at least 9 kΩ.

Note 5: When using the IC, adjustment is required in accordance with the use environment. When

mounting, place as close to the base of the IC leads as possible to improve noise elimination.

Note 6: The FG pin is open drain. If the FG pin is not used, connect to the GND.

Note 7: If noise is detected on the Input signal pin, add a capacitor between inputs.

Note 8: A Hall device should be an indium antimony system. It is recommend that the peak Hall device

voltage be set more than 300 mV

© 2020

Toshiba Electronic Devices & Storage Corporation

11

2020-02-20

�TPD4162F

12. Internal circuit diagrams

Internal circuit diagram of HU+, HU-, HV+, HV-, HW+, HW- input pins

Internal circuit diagram of VS pin

Internal circuit diagram of FG pin

Internal circuit diagram of FGC pin

Internal circuit diagram of RS pin

© 2020

Toshiba Electronic Devices & Storage Corporation

12

2020-02-20

�TPD4162F

13. Package Information

13.1. Package Dimensions

P-HSSOP31-0918-0.80-002

Unit:mm

Detailed illustration of Part F.

Note)

1. *1, *2: Does not include leftover resin.

2. *3: Does not include leftover tiebar.

Weight: 0.7 g (typ.)

Figure 13.1 Package Dimensions

© 2020

Toshiba Electronic Devices & Storage Corporation

13

2020-02-20

�TPD4162F

13.2. Marking

Figure 13.2 Marking

© 2020

Toshiba Electronic Devices & Storage Corporation

14

2020-02-20

�TPD4162F

RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as “TOSHIBA”.

Hardware, software and systems described in this document are collectively referred to as “Product”.

• TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

• This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's

written permission, reproduction is permissible only if reproduction is without alteration/omission.

• Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for

complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which

minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to

property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the

Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information,

including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and

conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product

will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited

to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the

applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any

other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO

LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

• PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY

CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation,

equipment used in nuclear facilities, equipment used in the aerospace industry, and lifesaving and/or life supporting medical equipment. IF

YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your

TOSHIBA sales representative or contact us via our website.

• Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

• Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

• The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any

infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any

intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

• ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR

PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER,

INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING

WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2)

DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR

INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE,

ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

• Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for

the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass

destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations

including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export

and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and

regulations.

• Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please

use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including

without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT

OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

https://toshiba.semicon-storage.com/

© 2020

Toshiba Electronic Devices & Storage Corporation

15

2020-02-20

�