Not Recommended for New Designs

BCM48BH120T120A00

BCM48BH120M120A00

(Formerly VIB0101THJ)

BCM

Bus Converter

TM

S

C

FEATURES

NRTL

US

DESCRIPTION

The V•I ChipTM Bus Converter is a high efficiency (>95%) Sine

Amplitude ConverterTM (SACTM) operating from a 38 to 55 Vdc

primary bus to deliver an isolated 12 V nominal, unregulated

secondary. The SAC offers a low AC impedance beyond the

bandwidth of most downstream regulators, meaning that

input capacitance normally located at the input of a 12 V

regulator can be located at the input to the SAC. Since the

K factor of the BCM48BH120T120A00 is 1/4, that capacitance

value can be reduced by a factor of 16x, resulting in savings of

board area, materials and total system cost.

• 48 Vdc – 12 Vdc 120 W Bus Converter

• High efficiency (>95%) reduces system power

consumption

• High power density (801 W/in3) reduces power system

footprint by >50%

• “Half Chip” V•I Chip package enables surface mount,

low impedance interconnect to system board

• Contains built-in protection features: undervoltage,

The BCM48BH120T120A00 is provided in a V•I Chip package

compatible with standard pick-and-place and surface mount

assembly processes. The V•I Chip package provides flexible

thermal management through its low junction-to-case and

junction-to-board thermal resistance. With high conversion

efficiency the BCM48BH120T120A00 increases overall system

efficiency and lowers operating costs compared to

conventional approaches.

overvoltage lockout, over current protection, short

circuit protection, overtemperature protection.

• Provides enable/disable control, internal temperature

monitoring

• ZVS/ZCS Resonant Sine Amplitude Converter topology

• Less than 50°C temperature rise at full load in typical

applications

TYPICAL APPLICATION

VIN = 38 – 55 V

POUT = 120 W(NOM)

• High End Computing Systems

• Automated Test Equipment

• Telecom Base Stations

• High Density Power Supplies

• Communication Systems

VOUT = 9.5 – 13.75 V (NO LOAD)

K = 1/4

PART NUMBER

DESCRIPTION

BCM48BH120T120A00

-40°C – 125°C TJ, J lead

TYPICAL APPLICATION

POL

enable / disable

switch

TM

PC

POL

SW1

F1

+In

VIN

3.15 A

C1

BCM +Out

POL

VOUT

10 µF

-In

POL

-Out

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 1 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

ABSOLUTE MAXIMUM RATINGS

CONTROL PIN SPECIFICATIONS

+IN to –IN . . . . . . . . . . . . . . . . . . . . . . . . . -1.0 Vdc – +60 Vdc

PC to –IN . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 Vdc – +20 Vdc

TM to –IN . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 Vdc – +7.0 Vdc

+IN/-IN to +OUT/-OUT . . . . . . . . . . . . . . . . . . . 2250 V (Hi Pot)

+IN/-IN to +OUT/-OUT . . . . . . . . . . . . . . . . . . . . 60 V (working)

+OUT to –OUT . . . . . . . . . . . . . . . . . . . . . . -1.0 Vdc - +16 Vdc

Temperature during reflow . . . . . . . . . . . . . . . . 245°C (MSL 6)

See section 5.0 for further application details and guidelines.

PACKAGE ORDERING INFORMATION

4

3

2

1

A

+Out

+In

B

C

D

E

F

G

H

J

K

-Out

L

M

NC

TM

NC

PC

-In

PC (V•I Chip BCM Primary Control)

The PC pin can enable and disable the BCM. When held below

VPC-DIS the BCM shall be disabled. When allowed to float with

an impedance to –IN of greater than 60 kΩ the module will

start. When connected to another BCM PC pin (either directly,

or isolated through a diode), the BCMs will start simultaneously when enabled. The PC pin is capable of being either

driven high by an external logic signal or internal pull up to 5 V

(operating).

TM (V•I Chip BCM Temperature Monitor)

The TM pin monitors the internal temperature of the BCM

within an accuracy of +5/-5 °C. It has a room temperature

setpoint of ~3.0 V and an approximate gain of 10 mV/°C. It

can source up to 100 uA and may also be used as a “Power

Good” flag to verify that the BCM is operating.

Bottom View

Signal

Name

+In

–In

NC

TM

NC

PC

+Out

–Out

Designation

A1-B1, A2-B2

L1-M1, L2-M2

E1

F2

G1

H2

A3-D3, A4-D4

J3-M3, J4-M4

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 2 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

1.0 ELECTRICAL CHARACTERISTICS

Specifications apply over all line and load conditions unless otherwise noted; Boldface specifications apply over the

temperature range of -40°C < TJ < 125°C (T-Grade); All other specifications are at TJ = 25º unless otherwise noted

ATTRIBUTE

SYMBOL

VIN

dVIN /dt

PQ

Voltage range

dV/dt

Quiescent power

No load power dissipation

PNL

Inrush current peak

IINR-P

DC input current

IIN-DC

K factor

( )

VOUT

CONDITIONS / NOTES

MIN

TYP

MAX

UNIT

38

48

55

1

150

3.0

3.5

Vdc

V/µs

mW

12

A

3.5

A

VIN = 38 – 55 Vdc; See Figure 14

VIN = 46 – 55 Vdc; See Figure 14

97

120

W

VIN = 46 – 55 Vdc

Average POUT < = 120 W, Tpeak < 10 ms

150

W

14

11.3

V

A

PC connected to -IN

VIN = 48 V

VIN = 38 to 55 V

VIN = 48 V COUT = 500 µF,

IOUT = 10.55 A

68

1.7

5.5

K

VIN

Output power (average)

POUT

Output power (peak)

POUT-P

Output voltage

Output current (average)

VOUT

IOUT

1/4

Efficiency (ambient)

η

Efficiency (hot)

Minimum efficiency

(over load range)

Output resistance (ambient)

Output resistance (hot)

Output resistance (cold)

Load capacitance

Switching frequency

Ripple frequency

η

Section 3.0

Pout < =120 W

VIN = 48 V, POUT = 120 W

VIN = 38 V to 55 V, POUT = 100 W

VIN = 48 V, TJ = 100°C, POUT = 120 W

η

24 W < POUT < POUT Max

ROUT

ROUT

ROUT

COUT

FSW

FSW-RP

Output voltage ripple

VOUT-PP

VIN to VOUT (application of VIN)

TON1

PC

PC voltage (operating)

PC voltage (enable)

PC voltage (disable)

PC source current (startup)

PC source current (operating)

PC internal resistance

PC capacitance (internal)

PC capacitance (external)

External PC resistance

PC external toggle rate

PC to VOUT with PC released

PC to VOUT, disable PC

VPC

VPC-EN

VPC-DIS

IPC-EN

IPC-OP

RPC-SNK

CPC_INT

CPC_EXT

RPC

FPC-TOG

Ton2

TPC-DIS

W

TJ = 25°C

TJ = 125°C

TJ = -40°C

8.5

93

90.5

92.6

VIN = 48 V, Pre-applied; See Figure 16

VIN = 48 V, Pre-applied; See Figure 16

%

93.7

%

89

%

35.4

46.1

27.2

44.1

56.1

35.0

1.75

3.50

55.8

69.1

45.7

500

1.90

3.80

mΩ

mΩ

mΩ

uF

MHz

MHz

1.60

3.20

140

355

mV

570

800

ms

4.7

2.0

5.0

2.5

50

100

50

150

5.3

3.0

1.95

300

2

400

588

1000

V

V

V

uA

mA

kΩ

pF

pF

kΩ

Hz

µs

µs

COUT = 0 µF, IOUT = 10.55 A, VIN = 48 V,

Section 8.0

VIN = 48 V, CPC = 0; See Figure 16

Internal pull down resistor

Section 5.0

External capacitance delays PC enable time

Connected to –VIN

94.6

60

60

4

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

1

100

10

Rev. 2.0

12/10

Page 3 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

1.0 ELECTRICAL CHARACTERISTICS (CONT.)

Specifications apply over all line and load conditions unless otherwise noted; Boldface specifications apply over the

temperature range of -40°C < TJ < 125°C (T-Grade); All other specifications are at TJ = 25º unless otherwise noted

ATTRIBUTE

SYMBOL

TM

TM accuracy

TM gain

TM source current

TM internal resistance

External TM capacitance

TM voltage ripple

Actm

ATM

ITM

RTM-SNK

CTM

VTM-PP

PROTECTION

Negative going OVLO

Positive going OVLO

Negative going UVLO

Positive going UVLO

Output overcurrent trip

Short circuit protection

trip current

Short circuit protection

response time

Thermal shutdown

junction setpoint

VIN OVLOVIN OVLO+

VIN UVLOVIN UVLO+

IOCP

GENERAL SPECIFICATION

Isolation voltage (Hi-Pot)

Working voltage (IN – OUT)

Isolation vapacitance

Isolation resistance

MTBF

Agency approvals / standards

CONDITIONS / NOTES

MIN

TYP

-5

MAX

UNIT

+5

ºC

mV/°C

uA

kΩ

pF

mV

10

CTM = 0 uF, VIN = 55 V, POUT = 120 W

VIN = 48 V, 25°C

25

40

75

180

100

50

50

250

55.1

55.5

29.1

30.7

12

57.8

58.1

30.8

32.6

20

59.4

59.4

35.4

37.3

25

V

V

V

V

A

40

A

ISSP

15

TSSP

0.8

1.0

1.2

us

TJ-OTP

125

130

135

°C

VHIPOT

Vworking

CIN-OUT

RIN-OUT

2250

1750

60

2150

Unpowered unit

MIL HDBK 217F, 25°C, GB

cTUVus

CE Mark

1350

10

7.1

V

V

pF

MΩ

Mhrs

ROHS 6 of 6

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 4 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

1.1 APPLICATION CHARACTERISTICS

All specifications are at TJ = 25ºC unless otherwise noted. See associated figures for general trend data.

ATTRIBUTE

SYMBOL

No load power

Inrush current peak

PNL

INR-P

Efficiency (ambient)

η

Efficiency (hot – 100°C)

η

Output resistance (-40°C)

Output resistance (25°C)

Output resistance (100°C)

ROUT_C

ROUT_R

ROUT_H

Output voltage ripple

VOUT-PP

VOUT transient (positive)

VOUT-TRAN+

VOUT transient (negative)

VOUT-TRAN-

Undervoltage lockout

response time

Output Overcurrent

Response Time

Overvoltage Lockout

Response Time

CONDITIONS / NOTES

TYP

UNIT

VIN = 48 V, PC enabled; See Figure 1

COUT = 500 µF, POUT = 120 W

VIN = 48 V, POUT = 120 W

COUT = 500 µF

VIN = 48 V, POUT = 120 W

COUT = 500 µF

VIN = 48 V

VIN = 48 V

VIN= 48 V

COUT = 0uF, POUT = 120 W @ VIN = 48,

VIN = 48 V

IOUT_STEP = 0 TO 10.55 A,

ISLEW >10 A/us; See Figure 12

IOUT_STEP = 10.55 A to 0 A,

ISLEW > 10 A/us; See Figure 11

1.75

6

W

A

95

%

94

%

35

44

56

mΩ

mΩ

mΩ

160

mV

1.4

V

1.3

V

2.4

us

4.4

ms

2.4

µs

TUVLO

TOCP

12 < IOCP < 25 A

TOVLO

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 5 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

Full Load Efficiency vs. Case Temperature

96

95

2.5

Efficiency (%)

2

1.5

94

93

92

91

1

-40

38

40

42

44

46

47

49

51

53

-40ºC

25ºC

96

94

14

94

92

12

10

8

PD

6

84

4

82

2

80

0

4

6

8

Output Load (A)

38 V

VIN :

48 V

55 V

10

38 V

48 V

55 V

84

4

82

2

0

2

4

6

88

8

6

4

82

2

80

0

8

10

48 V

38 V

48 V

55 V

10

12

55 V

38 V

48 V

55 V

ROUT vs. CaseTemperature

12

50

45

40

35

30

25

20

-40

-20

0

20

40

60

80

100

Temperature (°C)

Output Load (A)

VIN :

8

55

ROUT (m )

12

PD

38 V

VIN:

60

Power Dissipation (W)

Efficiency (%)

14

6

6

PD

Figure 4 – Efficiency and power dissipation at 25°C (case); VIN

10

4

12

8

86

0

90

2

14

Output Load (A)

η

0

η

88

16

84

55 V

10

Efficiency & Power Dissipation 100°C Case

86

48 V

90

12

96

92

100

80

Figure 3 – Efficiency and power dissipation at -40°C (case); VIN

94

80

16

92

Efficiency (%)

Efficiency (%)

90

Power Dissipation (W)

16

2

60

Efficiency & Power Dissipation 25°C Case

Efficiency & Power Dissipation -40°C Case

0

40

Figure 2 – Full load efficiency vs. temperature; VIN

96

86

20

38 V

VIN :

100ºC

Figure 1 – No load power dissipation vs. VIN; TCASE

88

0

Case Temperature (C)

Input Voltage (V)

TCASE:

-20

55

Power Dissipation (W)

No Load Power Dissipation (W)

No Load Power Dissipation vs. Line

3

38 V

48 V

55 V

Figure 5 – Efficiency and power dissipation at 100°C (case); VIN

I OUT :

1.05 A

10.55 A

Figure 6 – ROUT vs. temperature vs. IOUT

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 6 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

Output Voltage Ripple 25°C vs. IOUT

180

160

Vripple (mV)

140

120

100

80

60

40

20

0

0

2

4

6

8

10

IOUT (A)

Figure 7 – Vripple vs. IOUT ; 48 Vin, no external capacitance

Figure 8 – PC to VOUT startup waveform

Figure 9 – VIN to VOUT startup waveform

Figure 10 – Output voltage and input current ripple, 48 Vin, 120 W

no cOUT

Figure 11 – Positive load transient (0 – 11.3 A)

Figure 12 – Negative load transient (11.3 A – 0 A)

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 7 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

POUT (W)

�

120

�

97

38

Figure 13 – PC disable waveform, 48 VIN, 500 µF COUT full load

46

VIN (VDC)

55

Figure 14 – POUT derating vs. VIN

2.0 PACKAGE/MECHANICAL SPECIFICATIONS

All specifications are at TJ = 25ºC unless otherwise noted. See associated figures for general trend data.

ATTRIBUTE

SYMBOL

L

W

H

Vol

F

No Heatsink

No Heatsink

Power Density

PD

No Heatsink

Weight

W

Operating Temperature

Storage Temperature

Thermal Impedance

Thermal Capacity

Peak Compressive Force

Applied to Case (Z-axis)

TJ

TST

ØJC

TYP

MAX

-40

-40

UNIT

Junction to Case

125

125

2.7

°C

°C

°C/W

Ws/°C

3.0

lbs

225

245

150

3

6

VDC

VDC

°C

°C

s

°C/s

°C/s

5

Supported by J-leads only

ESDHBM

ESDMM

ESD Rating

Peak Temperature During Reflow

Peak Time Above 183°C

Peak Heating Rate During Reflow

Peak Cooling Rate Post Reflow

[b]

MIN

21.7 / 0.854 22.0 / 0.866 22.3 / 0.878 mm/in

16.37 / 0.644 16.50 / 0.650 16.63 / 0.655 mm/in

6.48 / 0.255 6.73 / 0.265 6.98 / 0.275 mm/in

2.44 / 0.150

cm3/in3

3.6 / 0.56

cm2/in2

801

W/in3

3

W/cm

49

0.28/8

oz/g

Nickel (0.51-2.03 µm)

Palladium (0.02-0.15 µm)

Gold (0.003-0.05 µm)

Lead Finish

[a]

CONDITIONS / NOTES

Length

Width

Height

Volume

Footprint

Human Body Model[a]

Machine Model[b]

MSL 5

MSL 6

2.5

1500

400

1.5

1.5

JEDEC JESD 22-A114C.01

JEDED JESD 22-A115-A

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 8 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

2.1 MECHANICAL DRAWING

mm

(inch)

BOTTOM VIEW

TOP VIEW ( COMPONENT SIDE )

NOTES:

mm

2. DIMENSIONS ARE inch .

UNLESS OTHERWISE SPECIFIED, TOLERANCES ARE:

3. .X / [.XX] = +/-0.25 / [.01]; .XX / [.XXX] = +/-0.13 / [.005]

4. PRODUCT MARKING ON TOP SURFACE

DXF and PDF files are available on vicorpower.com

2.2 RECOMMENDED LAND PATTERN

4

RECOMMENDED LAND PATTERN

( COMPONENT SIDE SH OWN )

3

2

1

A

+Out

+In

B

C

NC

TM

NC

PC

-In

D

E

F

G

H

J

K

-Out

L

M

Bottom View

NOTES:

3. .X / [.XX] = +/-0.25 / [.01]; .XX / [.XXX] = +/-0.13 / [.005]

mm

2. DIMENSIONS ARE inch .

UNLESS OTHERWISE SPECIFIED, TOLERANCES ARE:

4. PRODUCT MARKING ON TOP SURFACE

DXF and PDF files are available on vicorpower.com

Signal

Name

+In

–In

NC

TM

NC

PC

+Out

–Out

Designation

A1-B1, A2-B2

L1-M1, L2-M2

E1

F2

G1

H2

A3-D3, A4-D4

J3-M3, J4-M4

2.3 RECOMMENDED LAND PATTERN FOR PUSH PIN HEATSINK

Notes:

1. Maintain 3.50 (0.138) Dia. keep-out zone

free of copper, all PCB layers.

2. (A) minimum recommended pitch is 24.00 (0.945)

this provides 7.50 (0.295) component

edge–to–edge spacing, and 0.50 (0.020)

clearance between Vicor heat sinks.

(B) Minimum recommended pith is 25.50 (1.004).

This provides 9.00 (0.354) component

edge–to–edge spacing, and 2.00 (0.079)

clearance between Vicor heat sinks.

3. V•I Chip land pattern shown for reference

only, actual land pattern may differ.

Dimensions from edges of land pattern

to push–pin holes will be the same for

all half size V•I Chip Products.

4. RoHS compliant per CST–0001 latest revision.

5. Unless otherwise specified:

Dimensions are mm (inches)

tolerances are:

x.x (x.xx) = ±0.3 (0.01)

x.xx (x.xxx) = ±0.13 (0.005)

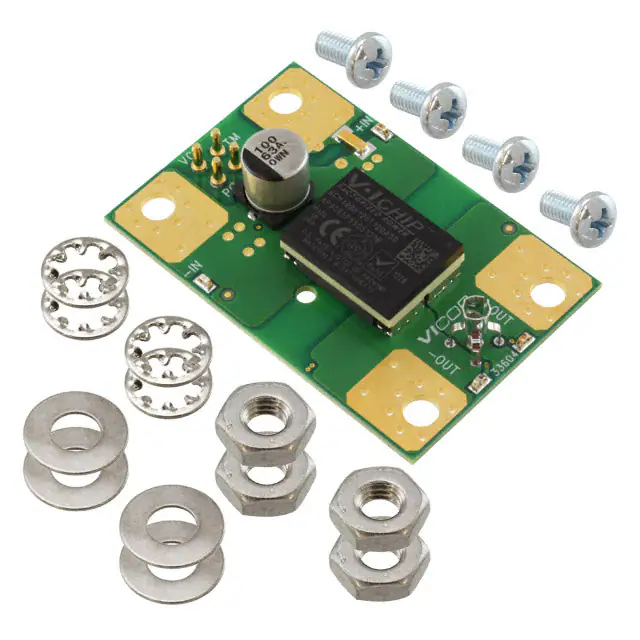

6. Plated through holes for grounding clips (33855)

shown for reference, Heatsink orientation and

device pitch will dictate final grounding solution.

(NO GROUNDING CLIPS)

(WITH GROUNDING CLIPS)

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 9 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

3.0 POWER, VOLTAGE, EFFICIENCY RELATIONSHIPS

Because of the high frequency, fully resonant SAC topology,

power dissipation and overall conversion efficiency of BCM

converters can be estimated as shown below.

OUTPUT

POWER

INPUT

POWER

Key relationships to be considered are the following:

1. Transfer Function

P R OUT

a. No load condition

P NL

VOUT = VIN • K

Eq. 1

Figure 15 – Power transfer diagram

Where K (transformer turns ratio) is constant

for each part number

b. Loaded condition

VOUT = Vin • K – IOUT • ROUT

Eq. 2

2. Dissipated Power

The two main terms of power losses in the

BCM module are:

- No load power dissipation (PNL) defined as the power

used to power up the module with an enabled power

train at no load.

- Resistive loss (ROUT) refers to the power loss across

the BCM modeled as pure resistive impedance.

PDISSIPATED ~

~ PNL + PROUT

Eq. 3

Therefore, with reference to the diagram shown in Figure 15

POUT = PIN – PDISSIPATED = PIN – PNL – PROUT

Eq. 4

Notice that ROUT is temperature and input voltage dependent

and PNL is temperature dependent (See Figure 15).

The above relations can be combined to calculate the overall module efficiency:

η =

POUT

PIN

=

PIN – PNL – PROUT

PIN

=

VIN • IIN – PNL – (IOUT)2 • ROUT

VIN • IIN

=1–

(

PNL + (IOUT)2 • ROUT

VIN • IIN

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

)

Eq. 5

Rev. 2.0

12/10

Page 10 of 16

v i c o r p o w e r. c o m

�v i c o r p o w e r. c o m

NL

5V

2.5 V

5V

3V

PC

VUVLO+

VUVLO–

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

1

A

E: TON2

F: TOCP

G: TPC–DIS

H: TSSP**

B

D

1: Controller start

2: Controller turn off

3: PC release

C

*Min value switching off

**From detection of error to power train shutdown

A: TON1

B: TOVLO*

C: Max recovery time

D:TUVLO

0.4 V

3 V @ 27°C

TM

LL • K

Vout

C

500mS

before retrial

3V

VIN

VOVLO+

VOVLO–

2

F

4: PC pulled low

5: PC released on output SC

6: SC removed

IOCP

ISSP

IOUT

E

3

G

4

Notes:

H

5

– Timing and voltage is not to scale

– Error pulse width is load dependent

6

Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

4.0 OPERATING

Figure 16 – Timing diagram

Rev. 2.0

12/10

Page 11 of 16

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

5.0 USING THE CONTROL SIGNALS TM AND PC

The PC control pin can be used to accomplish the following

functions:

• Delayed start: At start-up, PC pin will source a constant

100 uA current to the internal RC network. Adding an

external capacitor will allow further delay in reaching the

2.5 V threshold for module start.

• Synchronized start up: In a parallel module array, PC pins

shall be connected in order to ensure synchronous start of all

the units. While every controller has a calibrated 2.5 V

reference on PC comparator, many factors might cause

different timing in turning on the 100 uA current source on

each module, i.e.:

– Different VIN slew rate

– Statistical component value distribution

By connecting all PC pins, the charging transient will be

shared and all the modules will be enabled synchronously.

• Auxiliary voltage source: Once enabled in regular

operational conditions (no fault), each BCM PC provides a

regulated 5 V, 2 mA voltage source.

• Output disable: PC pin can be actively pulled down in order

to disable module operations. Pull down impedance shall be

lower than 1 kΩ and toggle rate lower than 1 Hz.

• Fault detection flag: The PC 5 V voltage source is internally

turned off as soon as a fault is detected. After a minimum

disable time, the module tries to re-start, and PC voltage is

re-enabled. For system monitoring purposes (microcontroller

interface) faults are detected on falling edges of PC signal.

It is important to notice that PC doesn’t have current sink

capability (only 150 kΩ typical pull down is present),

therefore, in an array, PC line will not be capable of disabling

all the modules if a fault occurs on one of them.

6.0 FUSE SELECTION

V•I Chips are not internally fused in order to provide flexibility

in configuring power systems. Input line fusing of V•I Chips is

recommended at system level, in order to provide thermal

protection in case of catastrophic failure.

The fuse shall be selected by closely matching system

requirements with the following characteristics:

• Current rating (usually greater than maximum BCM current)

• Maximum voltage rating (usually greater than the maximum

possible input voltage)

• Ambient temperature

• Nominal melting I2t

• Recommended fuse: 3.15 A Little Fuse Nano2 Fuse

The temperature monitor (TM) pin provides a voltage proportional to the absolute temperature of the converter control IC.

It can be used to accomplish the following functions:

• Monitor the control IC temperature: The temperature in

Kelvin is equal to the voltage on the TM pin scaled

by x100. (i.e. 3.0 V = 300 K = 27ºC). It is important to

remember that V•I chips are multi-chip modules, whose

temperature distribution greatly vary for each part number as

well with input/output conditions, thermal management and

environmental conditions. Therefore, TM cannot be used to

thermally protect the system.

• Fault detection flag: The TM voltage source is internally

turned off as soon as a fault is detected. After a minimum

disable time, the module tries to re-start, and TM voltage is

re-enabled.

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 12 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00 - BCM48BH120M120A00

7.0 CURRENT SHARING

The SAC topology bases its performance on efficient transfer

of energy through a transformer, without the need of closed

loop control. For this reason, the transfer characteristic can be

approximated by an ideal transformer with some resistive drop

and positive temperature coefficient.

This type of characteristic is close to the impedance characteristic

of a DC power distribution system, both in behavior

(AC dynamic) and absolute value (DC dynamic).

When connected in an array (with same K factor), the BCM

module will inherently share the load current with parallel

units, according to the equivalent impedance divider that the

system implements from the power source to the point of load.

It is important to notice that, when successfully started, BCMs

are capable of bidirectional operations (reverse power transfer

is enabled if the BCM input falls within its operating range and

the BCM is otherwise enabled). In parallel arrays, because of

the resistive behavior, circulating currents are never experienced,

because of energy conservation law.

General recommendations to achieve matched array impedances

are (see also AN016 for further details):

• to dedicate common copper planes within the PCB to

deliver and return the current to the modules

• to make the PCB layout as symmetric as possible

• to apply same input/output filters (if present) to each unit

Figure 17 – BCM Array

V•I CHIP INC. (A VICOR COMPANY) 25 FRONTAGE RD. ANDOVER, MA 01810 800-735-6200

Rev. 2.0

12/10

Page 13 of 16

v i c o r p o w e r. c o m

�Not Recommended for New Designs

BCM48BH120T120A00

- BCM48BH120M120A00

PRELIMINARY

DATASHEET

8.0 INPUT AND OUTPUT FILTER DESIGN

A major advantage of SAC systems versus conventional PWM

converters is that the transformers do not require large

functional filters. The resonant LC tank, operated at extreme

high frequency, is amplitude modulated as a function of input

voltage and output current, and efficiently transfers charge

through the isolation transformer. A small amount of

capacitance, embedded in the input and output stages of the

module, is sufficient for full functionality and is key to achieve

power density.

This paradigm shift requires system design to carefully evaluate

external filters in order to:

1.Guarantee low source impedance:

To take full advantage of the BCM dynamic response, the

impedance presented to its input terminals must be low

from DC to approximately 5 MHz. The connection of the

V•I Chip to its power source should be implemented with

minimal distribution inductance. If the interconnect

inductance exceeds 100 nH, the input should be bypassed

with a RC damper to retain low source impedance and

stable operation. With an interconnect inductance of

200 nH, the RC damper may be as high as 47 µF in series

with 0.3 Ω. A single electrolytic or equivalent low-Q

capacitor may be used in place of the series RC bypass.

Total load capacitance at the output of the BCM shall not

exceed the specified maximum. Owing to the wide bandwidth

and low output impedance of the BCM, low frequency bypass

capacitance and significant energy storage may be more

densely and efficiently provided by adding capacitance at the

input of the BCM. At frequencies