W25M512JV

Featuring

3V 512M-BIT (2 x 256M-BIT)

SERIAL MCP FLASH MEMORY

With Multi I/O SPI & Concurrent Operations

Publication Release Date: January 06, 2017

- Revision C

�W25M512JV

Table of Contents

1.

2.

3.

4.

5.

6.

GENERAL DESCRIPTIONS ............................................................................................................. 6

FEATURES ....................................................................................................................................... 6

PACKAGE TYPES AND PIN CONFIGURATIONS .......................................................................... 7

3.1

Pad Configuration WSON 8x6-mm ...................................................................................... 7

3.2

Pad Description WSON 8x6-mm .......................................................................................... 7

3.3

Pin Configuration SOIC 300-mil ........................................................................................... 8

3.4

Pin Description SOIC 300-mil ............................................................................................... 8

3.5

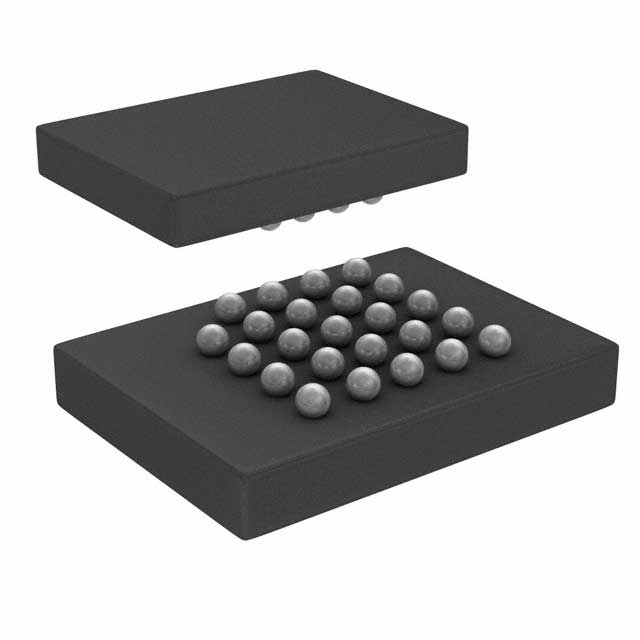

Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array) ................................................. 9

3.6

Ball Description TFBGA 8x6-mm ......................................................................................... 9

DEVICE CONFIGURATION & PIN DESCRIPTIONS..................................................................... 10

4.1

Serial MCP (SpiStack® ) Device Configuration ................................................................... 10

4.2

Chip Select (/CS) ................................................................................................................ 10

4.3

Serial Input & Output (DI, DO and IO0, IO1, IO2, IO3) ...................................................... 10

4.4

Serial Clock (CLK) .............................................................................................................. 10

4.5

Reset (/RESET) .................................................................................................................. 10

SINGLE DIE (W25Q256JV) BLOCK DIAGRAM ............................................................................. 11

FUNCTIONAL DESCRIPTIONS ..................................................................................................... 12

6.1

Device Operations .............................................................................................................. 12

6.1.1

6.1.2

6.1.3

6.1.4

6.1.5

7.

Stacked Die Operations ........................................................................................................ 12

Standard SPI Instructions ..................................................................................................... 12

Dual & Quad SPI Instructions ............................................................................................... 13

3-Byte / 4-Byte Address Modes ............................................................................................ 13

Software Reset & Hardware /RESET pin .............................................................................. 13

6.2

Write Protection .................................................................................................................. 14

STATUS AND CONFIGURATION REGISTERS ............................................................................ 15

7.1

Status Registers ................................................................................................................. 15

7.1.1

7.1.2

7.1.3

7.1.4

7.1.5

7.1.6

7.1.7

7.1.8

7.1.9

7.1.10

7.1.11

7.1.12

7.1.13

7.1.14

7.1.15

7.1.16

Program/Erase/Write In Progress (BUSY) – Status Only...................................................... 15

Write Enable Latch (WEL) – Status Only .............................................................................. 15

Block Protect Bits (BP3, BP2, BP1, BP0) – Volatile/Non-Volatile Writable ........................... 16

Top/Bottom Block Protect (TB) – Volatile/Non-Volatile Writable ........................................... 16

Complement Protect (CMP) – Volatile/Non-Volatile Writable................................................ 16

Status Register Lock (SRL) – Volatile/Non-Volatile OTP Writable ........................................ 16

Erase/Program Suspend Status (SUS) – Status Only .......................................................... 17

Security Register Lock Bits (LB3, LB2, LB1) – Volatile/Non-Volatile OTP Writable .............. 17

Current Address Mode (ADS) – Status Only......................................................................... 17

Power-Up Address Mode (ADP) – Non-Volatile Writable.................................................... 17

Write Protect Selection (WPS) – Volatile/Non-Volatile Writable .......................................... 17

Output Driver Strength (DRV1, DRV0) – Volatile/Non-Volatile Writable ............................. 18

Reserved Bits – Non Functional ......................................................................................... 18

Single Die W25Q256JV Status Register Memory Protection (WPS = 0, CMP = 0) ............ 19

Single Die W25Q256JV Status Register Memory Protection (WPS = 0, CMP = 1) ............ 20

Single Die W25Q256JV Individual Block Memory Protection (WPS=1) .............................. 21

-1-

�W25M512JV

8.

7.2

Extended Address Register – Volatile Writable Only ......................................................... 22

INSTRUCTIONS ............................................................................................................................. 23

8.1

Device ID and Instruction Set Tables ................................................................................. 23

8.1.1

8.1.2

8.1.3

8.1.4

8.1.5

8.2

Manufacturer and Device Identification ................................................................................. 23

Instruction Set Table 1 (Standard Single SPI, 3-Byte Address Mode ADS=0)(1) ................... 24

Instruction Set Table 2 (Dual/Quad SPI Instructions, 3-Byte Address Mode ADS=0) ........... 25

Instruction Set Table 3 (Standard Single SPI, 4-Byte Address Mode ADS=1)(1) ................... 26

Instruction Set Table 4 (Dual/Quad SPI Instructions, 4-Byte Address Mode ADS=1) ........... 27

Instruction Descriptions ...................................................................................................... 29

8.2.1

8.2.2

8.2.3

8.2.4

8.2.5

8.2.6

8.2.7

8.2.8

8.2.9

8.2.10

8.2.11

8.2.12

8.2.13

8.2.14

8.2.16

8.2.17

8.2.18

8.2.19

8.2.20

8.2.21

8.2.22

8.2.23

8.2.25

8.2.26

8.2.27

8.2.28

8.2.29

8.2.30

8.2.31

8.2.32

8.2.33

8.2.34

8.2.35

8.2.36

8.2.37

8.2.38

Software Die Select (C2h) .................................................................................................... 29

Write Enable (06h) ................................................................................................................ 30

Write Enable for Volatile Status Register (50h)..................................................................... 30

Write Disable (04h) ............................................................................................................... 31

Read Status Register-1 (05h), Status Register-2 (35h) & Status Register-3 (15h) ............... 31

Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h) ............... 32

Read Extended Address Register (C8h) ............................................................................... 34

Write Extended Address Register (C5h) ............................................................................... 35

Enter 4-Byte Address Mode (B7h) ........................................................................................ 36

Exit 4-Byte Address Mode (E9h) ......................................................................................... 36

Read Data (03h) ................................................................................................................. 37

Read Data with 4-Byte Address (13h)................................................................................. 38

Fast Read (0Bh) ................................................................................................................. 39

Fast Read with 4-Byte Address (0Ch)................................................................................. 40

Fast Read Dual Output (3Bh) ............................................................................................. 41

Fast Read Dual Output with 4-Byte Address (3Ch) ............................................................ 42

Fast Read Quad Output (6Bh) ............................................................................................ 43

Fast Read Quad Output with 4-Byte Address (6Ch) ........................................................... 44

Fast Read Dual I/O (BBh) ................................................................................................... 45

Fast Read Dual I/O with 4-Byte Address (BCh) .................................................................. 46

Fast Read Quad I/O (EBh).................................................................................................. 47

Fast Read Quad I/O with 4-Byte Address (ECh) ................................................................. 48

Set Burst with Wrap (77h) ................................................................................................... 49

Page Program (02h) ........................................................................................................... 50

Page Program with 4-Byte Address (12h)........................................................................... 51

Quad Input Page Program (32h)......................................................................................... 52

Quad Input Page Program with 4-Byte Address (34h) ........................................................ 53

Sector Erase (20h) .............................................................................................................. 54

Sector Erase with 4-Byte Address (21h) ............................................................................. 55

32KB Block Erase (52h)...................................................................................................... 56

64KB Block Erase (D8h) ..................................................................................................... 57

64KB Block Erase with 4-Byte Address (DCh).................................................................... 58

Single Die Chip Erase (C7h / 60h) ...................................................................................... 59

Erase / Program Suspend (75h) ......................................................................................... 60

Erase / Program Resume (7Ah) .......................................................................................... 61

Read Device ID (ABh)......................................................................................................... 62

-2-

Publication Release Date: January 06, 2017

- Revision C

�W25M512JV

8.2.39

8.2.40

8.2.41

8.2.42

8.2.43

8.2.44

8.2.45

8.2.46

8.2.47

8.2.48

8.2.49

8.2.50

8.2.51

8.2.52

8.2.53

9.

10.

11.

12.

Read Manufacturer / Device ID (90h) ................................................................................. 63

Read Manufacturer / Device ID Dual I/O (92h) ................................................................... 64

Read Manufacturer / Device ID Quad I/O (94h) .................................................................. 65

Read Unique ID Number (4Bh) ........................................................................................... 66

Read JEDEC ID (9Fh) ........................................................................................................ 67

Read SFDP Register (5Ah)................................................................................................. 68

Erase Security Registers (44h) ........................................................................................... 69

Program Security Registers (42h) ....................................................................................... 70

Read Security Registers (48h) ............................................................................................ 71

Individual Block/Sector Lock (36h) ...................................................................................... 72

Individual Block/Sector Unlock (39h) .................................................................................. 73

Read Block/Sector Lock (3Dh)............................................................................................ 74

Global Block/Sector Lock (7Eh) .......................................................................................... 75

Global Block/Sector Unlock (98h) ....................................................................................... 75

Enable Reset (66h) and Reset Device (99h) ...................................................................... 76

ELECTRICAL CHARACTERISTICS(1) ............................................................................................ 77

9.1

Absolute Maximum Ratings (2) .......................................................................................... 77

9.2

Operating Ranges .............................................................................................................. 77

9.3

Power-up Power-down Timing and Requirements ............................................................. 78

9.4

DC Electrical Characteristics(1) ........................................................................................... 79

9.5

AC Measurement Conditions ............................................................................................. 80

9.6

AC Electrical Characteristics(5) ........................................................................................... 81

9.7

Serial Output Timing ........................................................................................................... 83

9.8

Serial Input Timing.............................................................................................................. 83

9.9

/HOLD Timing ....................................................................... Error! Bookmark not defined.

9.10 /WP Timing ........................................................................... Error! Bookmark not defined.

PACKAGE SPECIFICATIONS ....................................................................................................... 84

10.1 8-Pad WSON 8x6-mm (Package Code E) ......................................................................... 84

10.2 16-Pin SOIC 300-mil (Package Code F) ............................................................................ 85

10.3 24-Ball TFBGA 8x6-mm (Package Code B, 5x5-1 Ball Array) ........................................... 86

10.4 24-Ball TFBGA 8x6-mm (Package Code C, 6x4 Ball Array) .............................................. 87

ORDERING INFORMATION .......................................................................................................... 88

11.1 Valid Part Numbers and Top Side Marking ........................................................................ 89

REVISION HISTORY ...................................................................................................................... 90

-3-

�W25M512JV

Table of Figures

Figure 1a. W25M512JV Pad Assignments, 8-pad WSON 8x6-mm (Package Code E) ............................... 7

Figure 1b. W25M512JV Pin Assignments, 16-pin SOIC 300-mil (Package Code F) ................................... 8

Figure 1c. W25M512JV Ball Assignments, 24-ball TFBGA 8x6-mm (Package Code B & C) ...................... 9

Figure 2a. W25M512JV Device Configuration ............................................................................................ 10

Figure 2b. Single Die W25Q256JV Serial Flash Memory Block Diagram .................................................. 11

Figure 2c. W25M512JV Serial Flash Memory Operation Diagram ............................................................. 12

Figure 3a. Status Register-1 ....................................................................................................................... 15

Figure 3b. Status Register-2 ....................................................................................................................... 17

Figure 3c. Status Register-3 ....................................................................................................................... 18

Figure 3d. Individual Block/Sector Locks (Single Die W25Q256JV) .......................................................... 21

Figure 3e. Extended Address Register (Single Die W25Q256JV).............................................................. 22

Figure 4. Software Die Select Instruction .................................................................................................... 29

Figure 5. Write Enable Instruction ............................................................................................................... 30

Figure 6. Write Enable for Volatile Status Register Instruction ................................................................... 30

Figure 7. Write Disable Instruction .............................................................................................................. 31

Figure 8. Read Status Register Instruction ................................................................................................. 31

Figure 9a. Write Status Register-1/2/3 Instruction ...................................................................................... 32

Figure 9b. Write Status Register-1/2 Instruction ......................................................................................... 33

Figure 10. Read Extended Address Register Instruction ............................................................................ 34

Figure 11. Write Extended Address Register Instruction ............................................................................ 35

Figure 12. Enter 4-Byte Address Mode instruction ..................................................................................... 36

Figure 13. Exit 4-Byte Address Mode instruction ........................................................................................ 36

Figure 14. Read Data Instruction ................................................................................................................ 37

Figure 15. Read Data with 4-Byte Address Instruction ............................................................................... 38

Figure 16. Fast Read Instruction ................................................................................................................. 39

Figure 17. Fast Read with 4-Byte Address Instruction ............................................................................... 40

Figure 19. Fast Read Dual Output Instruction ............................................................................................ 41

Figure 20. Fast Read Dual Output with 4-Byte Address Instruction ........................................................... 42

Figure 21. Fast Read Quad Output Instruction ........................................................................................... 43

Figure 22. Fast Read Quad Output with 4-Byte Address Instruction .......................................................... 44

Figure 23. Fast Read Dual I/O Instruction .................................................................................................. 45

Figure 24. Fast Read Dual I/O w/ 4-Byte Address Instruction .................................................................... 46

Figure 26. Fast Read Quad I/O Instruction ................................................................................................. 47

Figure 27. Fast Read Quad I/O w/ 4-Byte Address Instruction ................................................................... 48

Figure 29. Set Burst with Wrap Instruction ................................................................................................. 49

Figure 30. Page Program Instruction .......................................................................................................... 50

Figure 31. Page Program with 4-Byte Address Instruction ......................................................................... 51

Figure 32. Quad Input Page Program Instruction ....................................................................................... 52

Figure 33. Quad Input Page Program with 4-Byte Address Instruction ...................................................... 53

Figure 34. Sector Erase Instruction ............................................................................................................ 54

Figure 35. Sector Erase with 4-Byte Address Instruction ........................................................................... 55

Figure 36. 32KB Block Erase Instruction .................................................................................................... 56

-4-

Publication Release Date: January 06, 2017

- Revision C

�W25M512JV

Figure 37. 64KB Block Erase Instruction .................................................................................................... 57

Figure 38. 64KB Block Erase with 4-Byte Address Instruction ................................................................... 58

Figure 39. Single Die Chip Erase Instruction .............................................................................................. 59

Figure 40. Erase/Program Suspend Instruction .......................................................................................... 60

Figure 41. Erase/Program Resume Instruction........................................................................................... 61

Figure 42. Read Device ID Instruction ........................................................................................................ 62

Figure 43. Read Manufacturer / Device ID Instruction ................................................................................ 63

Figure 44. Read Manufacturer / Device ID Dual I/O Instruction ................................................................. 64

Figure 45. Read Manufacturer / Device ID Quad I/O Instruction ................................................................ 65

Figure 46. Read Unique ID Number Instruction .......................................................................................... 66

Figure 47. Read JEDEC ID Instruction ....................................................................................................... 67

Figure 48. Read SFDP Register Instruction ................................................................................................ 68

Figure 49. Erase Security Registers Instruction.......................................................................................... 69

Figure 50. Program Security Registers Instruction ..................................................................................... 70

Figure 51. Read Security Registers Instruction .......................................................................................... 71

Figure 52. Individual Block/Sector Lock Instruction .................................................................................... 72

Figure 53. Individual Block Unlock Instruction ............................................................................................ 73

Figure 54. Read Block Lock Instruction ...................................................................................................... 74

Figure 55. Global Block Lock Instruction .................................................................................................... 75

Figure 56. Global Block Unlock Instruction ................................................................................................. 75

Figure 57. Enable Reset and Reset Instruction Sequence ......................................................................... 76

Figure 58a. Power-up Timing and Voltage Levels ...................................................................................... 78

Figure 58b. Power-up, Power-Down Requirement ..................................................................................... 78

Figure 59. AC Measurement I/O Waveform ................................................................................................ 80

-5-

�W25M512JV

1. GENERAL DESCRIPTIONS

The W25M512JV (2 x 256M-bit) Serial MCP (Multi Chip Package) Flash memory is based on the popular

W25Q SpiFlash® series by stacking two individual W25Q256JV die into a standard 8-pin package. It offers

the highest memory density for the low pin-count package, as well as Concurrent Operations in Serial Flash

memory for the first time. The W25M SpiStack® series is ideal for small form factor system designs, and

applications that demand high Program/Erase data throughput.

The SpiStack® product series introduces a new “Software Die Select (C2h)” instruction, and a factory

assigned “Die ID#” for each stacked die. Each W25Q256JV die can be accessed independently even

though the interface is shared. The SpiStack® feature only allows a single die to be Active and have control

of the SPI interface at any given time to avoid bus contention.

The W25M512JV maintains all the SpiFlash® features and functions, with the support for standard SPI

(Serial Peripheral Interface), Dual I/O SPI, and Quad I/O SPI read operations through the shared SPI

interface: Serial Clock, Chip Select, Serial Data I/O0 (DI), I/O1 (DO), I/O2, and I/O3.

Each W25Q256JV memory array is organized into 131,072 programmable pages of 256-Byte each. Up to

256 bytes can be programmed at a time. Pages can be erased in groups of 16 (4KB sector erase), groups

of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The small 4KB

sectors allow for greater flexibility in applications that require data and parameter storage.

2. FEATURES

New Family of SpiFlash® Memories

– W25M512JV: 2 x 256M-bit (2 x 32M-Byte)

– Standard SPI: CLK, /CS, DI, DO

– Dual SPI: CLK, /CS, IO0, IO1

– Quad SPI: CLK, /CS, IO0, IO1, IO2, IO3

– 3 or 4-Byte Addressing Mode

– Software Die Select (C2h)

– Software & Hardware Reset(1)

Low Power, Wide Temperature Range

– Single 2.7 to 3.6V power supply

– 4mA active current,